Материалы по тегу: ускоритель

|

02.04.2026 [11:50], Руслан Авдеев

Китайские ИИ-ускорители заняли почти половину местного рынка на фоне снижения доли NVIDIAКитайские производители видеокарт и ИИ-чипов заняли около 41 % локального рынка ИИ-ускорителей в 2025 году. Это сказалась на позициях NVIDIA, некогда занимавшей на этом, одном из ключевых рынков за пределами США, доминирующее положение, сообщает Reuters со ссылкой на аналитику IDC. Местные производители наращивают свою долю по мере того, как Пекин всё больше внимания уделяет вопросу обеспечения независимости от иностранных чипов. Власти стимулируют использование государственными ведомствами и компаниями китайских альтернатив после того, как США несколько раз инициировали ужесточение экспортного контроля в Поднебесную. Общие поставки ИИ-ускорителей NVIDIA, AMD и китайских производителей в 2025 году достигли в КНР приблизительно 4 млн единиц. NVIDIA сохранила позицию лидера рынка, поставив около 2,2 млн ускорителей, доля компании на рынке составляет 55 %. Тем не менее назвать это успехом американского вендора нельзя, поскольку раньше компания тотально доминировала на рынке. AMD поставила скромные 160 тыс. ускорителей (доля 4 %).

Источник изображения: James Lo/unsplash.com Китайские вендоры в совокупности поставили 1,65 млн ускорителей — 41 % рынка. Это свидетельствует о том, насколько агрессивно местные игроки действуют для компенсации дефицита ускорителей, ужесточившегося из-за американского экспортного контроля. Среди китайских производителей особенно выделяется Huawei Technologies, поставившая около 812 тыс. чипов, приблизительно половину от общих объёмов местной продукции. Второе место занимает T-Head — занимающееся разработкой чипов подразделение Alibaba, поставившее приблизительно 265 тыс. ускорителей. Kunlunxin (Baidu) и Cambricon поставили приблизительно по 116 тыс. чипов каждая, поделив третье место среди китайских вендоров. На Hygon, MetaX и Iluvatar CoreX пришлось 5 %, 4 % и 3 % соответственно. В 2025 году китайские власти инициировали новый раунд расходов на ИИ-инфраструктуру, руководство в провинциях ускорило развёртывание вычислительных центров. Многие их таких кампусов ЦОД, по данным Reuters, получили негласное указание «покупать китайское». Тем не менее, в начале 2026 года США одобрили поставки относительно современных ускорителей NVIDIA H200 в КНР, после чего поставки были официально одобрены и Пекином. В марте глава NVIDIA Дженсен Хуанг (Jensen Huang) объявил, что начат выпуск H200 для китайского рынка — это может изменить позиции NVIDIA уже в обозримом будущем.

22.03.2026 [13:10], Сергей Карасёв

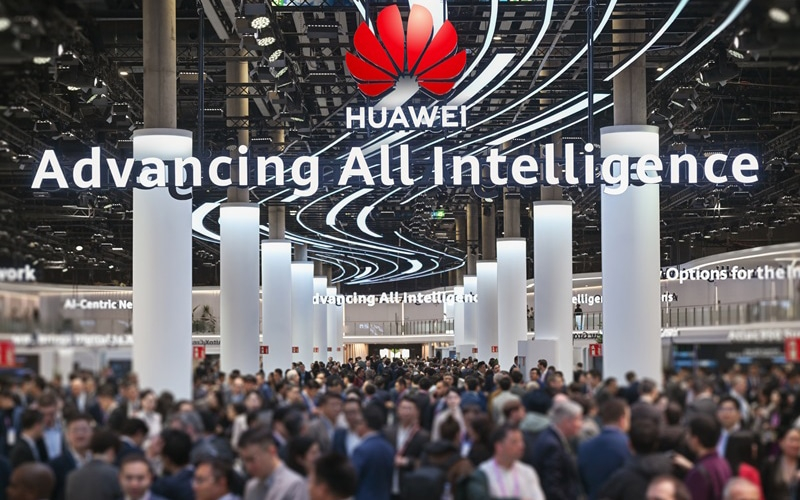

Почти втрое быстрее NVIDIA H20: Huawei представила ИИ-ускоритель Atlas 350 для инференсаКомпания Huawei Technologies, по сообщению газеты South China Morning Post (SCMP), представила ускоритель Atlas 350, предназначенный для ИИ-инференса. Утверждается, что в таких задачах новинка обеспечивает прирост производительности до 2,8 раза по сравнению с NVIDIA H20. Известно, что решение Atlas 350 выполнено на чипе Ascend 950PR. Заявленная ИИ-производительность в формате FP4 достигает 1,56 Пфлопс. Показатели быстродействия в других режимах пока не раскрываются, но ранее говорилось об 1 Пфлопс в FP8. Как отмечается, Huawei использует собственную память HBM. Её объём в зависимости от конфигурации ускорителя составляет до 128 Гбайт, пропускная способность — 1,6 Тбайт/с. Прочие технические характеристики не приводятся. Ускоритель Atlas 350 оптимизирован для предварительного заполнения (Prefill) в ходе инференса — это наиболее ресурсоёмкая фаза работы больших языковых моделей (LLM) в рамках процесса генерации контента: на данном этапе производится обработка входного запроса пользователя. Скорость выполнения предварительного заполнения напрямую влияет на показатель TTFT (Time To First Token), то есть, на время, прошедшее с момента ввода запроса до начала ответа. Таким образом, решение Atlas 350 подходит для ИИ-приложений реального времени и агентных систем.

Источник изображения: Huawei Huawei также заявила о планах масштабного обновления своих СХД, включая решения OceanStor Dorado и Pacific 9926 класса All-Flash. Кроме того, компания готовит платформу FusionCube A1000, которая поможет малым и средним предприятиям быстро разворачивать ИИ-системы. «Если первая половина эпохи ИИ была сосредоточена на вычислительной мощности, то вторая половина будет определяться данными. В 2026 году Huawei продолжит модернизацию своих СХД и будет активно участвовать в крупных национальных проектах по формированию соответствующей инфраструктуры», — говорит Юань Юань (Yuan Yuan), президент подразделения по хранению данных Huawei.

18.03.2026 [08:44], Сергей Карасёв

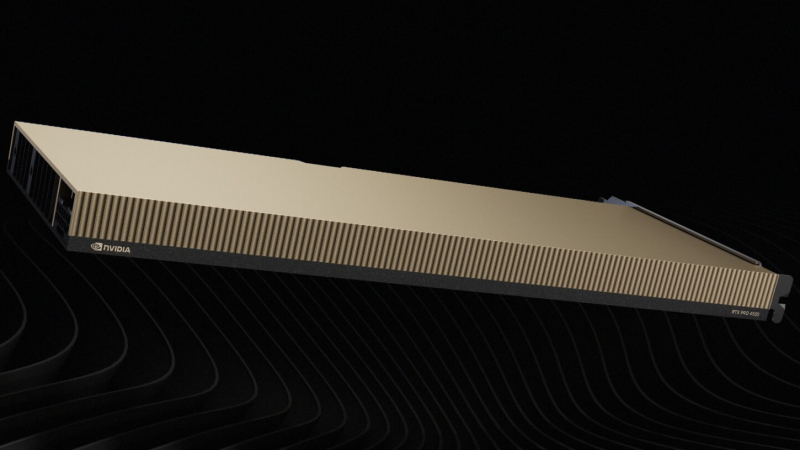

NVIDIA выпустила однослотовый ускоритель RTX Pro 4500 Blackwell Server Edition с 32 Гбайт памяти GDDR7Компания NVIDIA анонсировала ускоритель RTX Pro 4500 Blackwell Server Edition, подходящий для решения таких задач, как ИИ-инференс, анализ данных, обработка видеоматериалов и пр. Новинка ориентирована на дата-центры, облачные платформы и периферийные инфраструктуры. Решение выполнено на архитектуре Blackwell. Конфигурация включает 10 496 ядер CUDA, 82 ядра RT четвёртого поколения, а также 32 Гбайт GDDR7 с 256-бит шиной и пропускной способностью 800 Гбайт/с. Задействованы тензорные ядра пятого поколения, которые обеспечивают до трёх раз более высокую производительность по сравнению с более ранними изделиями и предлагают поддержку режима FP4. Карта получила однослотовое исполнение FHFL и пассивное охлаждение. Заявленное энергопотребление составляет 165 Вт. Для подключения служит интерфейс PCIe 5.0 x16. ИИ-быстродействие на операциях FP4 (Tensor Core) достигает 1,6 Пфлопс, FP8 (Tensor Core) — 811 Тфлопс, FP16/BF16 (Tensor Core) — 406 Тфлопс, TF32 (Tensor Core) — 203 Тфлопс. Как отмечает NVIDIA, по сравнению с системами, работающими только на основе CPU, ускоритель RTX Pro 4500 Blackwell Server Edition обеспечивает до 100 раз более высокую производительность при анализе видеоматериалов с помощью алгоритмов ИИ. Благодаря этому компании могут извлекать данные из видеопотока в режиме реального времени, ускоряя работу приложений компьютерного зрения — как в ЦОД, так и на периферии. Предусмотрены три аппаратных движка NVIDIA NVENC девятого поколения. Они имеют поддержку кодирования 4:2:2 H.264 и HEVC, а также улучшают качество при работе с HEVC и AV1. Вместе с тем три движка NVIDIA NVDEC шестого поколения демонстрируют вдвое более высокую пропускную способность при декодировании материалов H.264, а также поддерживают 4:2:2 H.264 и HEVC.

17.03.2026 [10:32], Руслан Авдеев

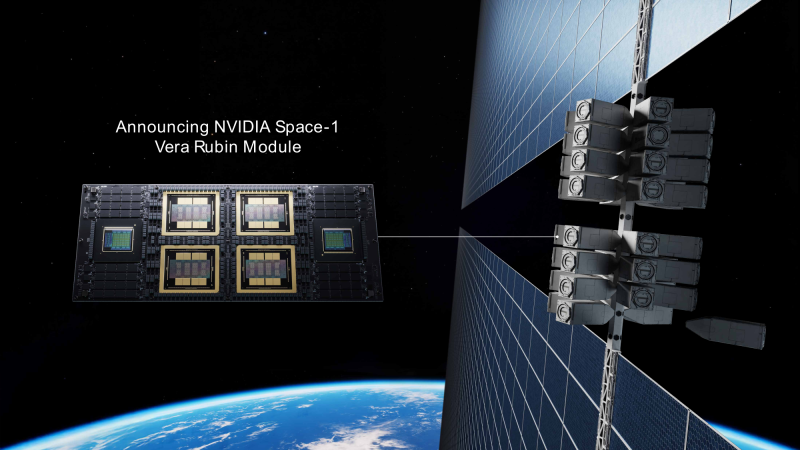

NVIDIA анонсировала Space-1 Vera Rubin Module — ИИ-ускоритель для орбитальных ЦОД, который в 25 раз быстрее H100Глава NVIDIA Дженсен Хуанг (Jensen Huang) представил космический вычислительный модуль на архитектуре Vera Rubin. По его словам, модуль до 25 раз производительнее, чем NVIDIA H100, и шесть коммерческих космических компаний уже внедрили платформу, сообщает Tom’s Hardware. Space-1 Vera Rubin Module предназначен для орбитальных дата-центров, работающих с ИИ-моделями непосредственно в космосе. Он имеет тесно интегрированную архитектуру CPU–GPU и высокоскоростной интерконнект для работы с большими потоками данных от космических инструментов в режиме реального времени. Также предлагается вариант NVIDIA IGX Thor для критически важных периферийных сред с поддержкой выполнения ИИ-задач в режиме реального времени, безопасной загрузки, автономных операций и др. Наиболее компактный вариант NVIDIA Jetson Orin рассчитан на использование в спутниках с ограниченными размерами, весом и энергопотреблением — для систем бортового «зрения», навигации и обработки данных с датчиков. По данным NVIDIA, сейчас её новые платформы на Земле и в космосе используют компании Aetherflux, Axiom Space, Kepler Communications, Planet Labs PBC, Sophia Space и Starcloud. Kepler внедряет Jetson Orin в своей спутниковой группировке для управления данными и их маршрутизацией с помощью ИИ-инструментов. Jetson Orin применяется непосредственно в спутниках. В октябре 2025 года основатель Amazon и Blue Origin Джефф Безос (Jeff Bezos) прогнозировал, что через 10–20 лет на орбите появятся ЦОД гигаваттного масштаба. Основными преимуществами таких решений назывались возможность непрерывного электроснабжения группировки с помощью солнечной энергии, а также упрощённая система охлаждения в космосе. Starcloud уже строит специальные орбитальные ИИ-ЦОД, предназначенные для обучения моделей и инференса непосредственно на орбите. Космические ЦОД — весьма перспективное направление в сфере ИИ. Одним из наиболее громких событий стала заявка SpaceX, попросившей у американских властей разрешение на вывод на орбиту миллиона микро-ЦОД. Инициатива подверглась критике Amazon как «спекулятивная», но компания столкнулась с критикой Федеральной комиссии по связи с США, потребовавшей навести порядок в собственном космическом бизнесе.

15.03.2026 [11:15], Сергей Карасёв

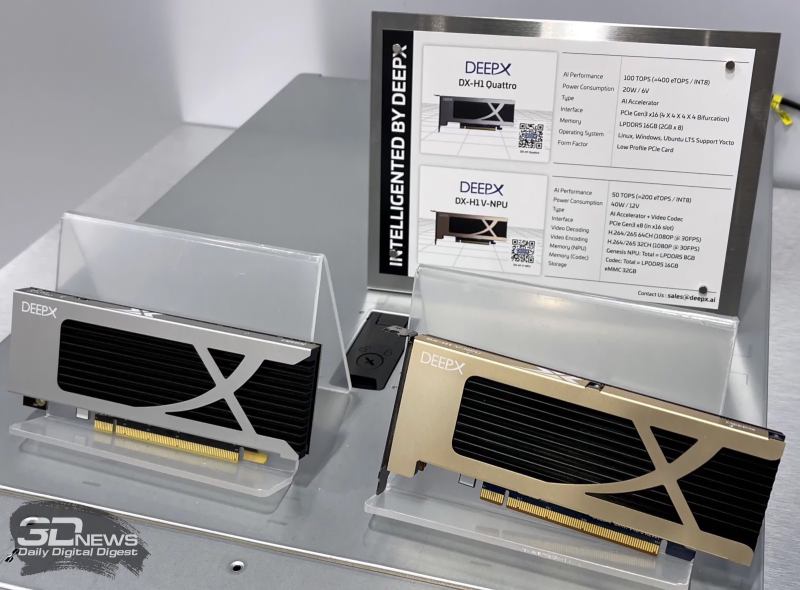

Выпуск ИИ-чипов DeepX DX-M2 отложен из-за проблем у TeslaИзменение графика разработки ИИ-ускорителя Tesla следующего поколения, по сообщению ресурса DigiTimes, привело к тому, что южнокорейская компания DeepX вынуждена отложить выпуск своих чипов DX-M2, массовое производство которых изначально было запланировано на II квартал 2027 года. Отмечается, что задержки возникли с разработкой изделия Tesla AI6. Предполагается, что это решение будет применяться для поддержания разнообразных нагрузок в инфраструктуре Tesla, включая платформы автономного вождения, системы человекоподобного робота Optimus и дата-центры для ИИ-задач. В 2025 году Tesla подписала контракт с Samsung на изготовление AI6 вплоть до декабря 2033-го: стоимость соглашения составляет $16 млрд. Первоначальный договор предусматривал производство около 16 тыс. пластин в месяц, однако затем Tesla запросила дополнительно 24 тыс. пластин, что в сумме предполагает объем до 40 тыс. пластин ежемесячно. Для Tesla AI6 планируется применение 2-нм техпроцесса Samsung. По такой же методике будут выпускаться чипы DeepX DX-M2. Для обоих этих изделий оговорено использование услуги Multi-Project Wafer (MPW), при которой на одной кремниевой пластине в рамках получения прототипов размещаются изделия нескольких разных заказчиков. Такой подход позволяет снизить затраты на разработку перед организацией массового производства. Однако, по информации DigiTimes, с выходом Tesla AI6 на этап MPW возникли задержки. С чем именно связаны сложности, не уточняется. Отраслевые эксперты полагают, что пересмотр графика может быть обусловлен изменением сроков инвестиций в автономные транспортные средства, роботизированные платформы и суперкомпьютеры с ИИ. Компания Samsung отказалась от комментариев, сославшись на конфиденциальность проектов заказчиков. Между тем из-за задержек Tesla выпуск чипов DeepX DX-M2 по программе MPW, который планировалось начать в апреле, переносится на более поздний срок. В соответствии с новым графиком, тестирование качества этих решений будет организовано не ранее III квартала текущего года. Ожидается, что DX-M2 обеспечит ИИ-производительность на уровне 80 TOPS при максимальном энергопотреблении примерно 5 Вт. Чип поддерживает память LPDDR5X. Утверждается, что процессор способен работать с ИИ-моделями, насчитывающими до 100 млрд параметров.

12.03.2026 [11:23], Владимир Мироненко

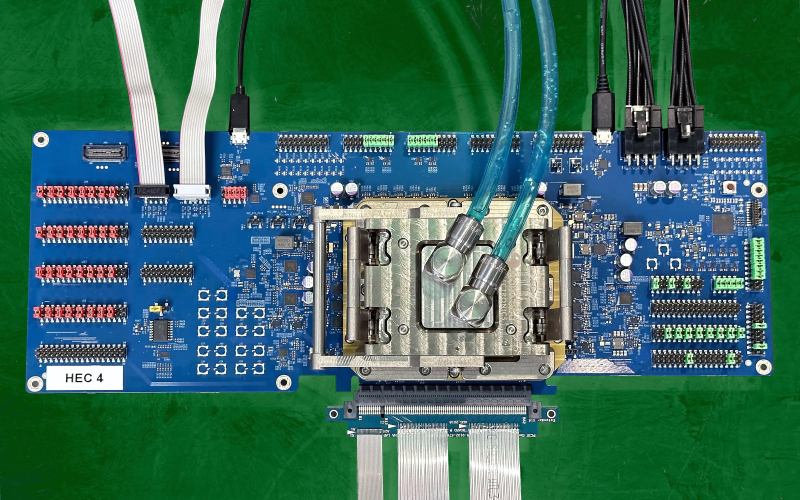

Intel представила чип Heracles, который в 5000 раз быстрее серверных процессоров в вычислениях с FHEКомпания Intel представила на конференции ISSCC чип Heracles с поддержкой полностью гомоморфного шифрования (FHE), который превосходит топовый серверный процессор Intel по скорости вычислений с FHE в 5 тыс. раз, сообщил ресурс IEEE Spectrum. FHE позволяет выполнять вычисления над данными в зашифрованном виде без их расшифровки, но на стандартных процессорах и видеокартах оно работает крайне медленно. Heracles построен на основе 3-нм технологии FinFET и примерно в 20 раз больше большинства исследовательских чипов FHE, имеющих размеры 10 мм2 или менее. В основе Heracles лежат 64 вычислительных ядра — так называемые пары тайлов, — расположенные в сетке восемь на восемь и служащие в качестве SIMD-движков для полиномиальных вычислений, манипуляций и других операций, составляющих вычисления в FHE, а также для их параллельного выполнения. Встроенная в кристалл сеть 2D-mesh соединяет тайлы друг с другом широкими шинами по 512 байт. На чипе данные размещаются в 64 Мбайт кеша, откуда они могут передаваться по массиву со скоростью 9,6 Тбайт/с, переходя от одной пары тайлов к другой. Чтобы предотвратить взаимное влияние перемещения данных и математических вычислений, Heracles использует три синхронизированных потока инструкций: один для перемещения вне чипа, один для перемещения внутри чипа и один для арифметических операций. Чип размещён в корпусе с жидкостным охлаждением вместе с двумя стеками памяти HBM по 24 Гбайт (суммарно 48 Гбайт с ПСП 819 Гбайт/с). Данная конструкция позволяет Heracles, работающему на частоте 1,2 ГГц, выполнять критически важные математические преобразования FHE всего за 39 мс, что в 2355 раз быстрее, чем может предложить Intel Xeon, работающий на частоте 3,5 ГГц. По семи ключевым операциям Heracles быстрее него в 1074–5547 раз в зависимости от объёма необходимых операций перераспределения (shuffling). Компания продемонстрировала на ISSCC возможности Heracles на примере простого частного запроса к защищённому серверу. Он имитировал запрос избирателя на проверку правильности регистрации его бюллетеня. В данном случае у штата есть зашифрованная база данных избирателей и их голосов: избиратель шифрует свой идентификационный номер и голос, а сервер проверяет совпадение без расшифровки и возвращает зашифрованный ответ, который пользователь затем расшифровывает на своей стороне. На Xeon этот процесс занял 15 мс, а Heracles справился с задачей за 14 мкс. Казалось бы, эта разница незаметна для отдельного человека, но проверка 100 млн бюллетеней занимает более 17 дней работы Xeon против всего 23 минут на Heracles. Проект Heracles был запущен пять лет назад в рамках программы DARPA по ускорению FHE с помощью специализированного оборудования. Разработкой подобных чипов также занимается ряд стартапов, включая Fabric Cryptography, Cornami и Optalysys. Сану Мэтью (Sanu Mathew), руководитель исследований в области защищённых схем в Intel, считает, что у компании есть большое преимущество, поскольку её чип может выполнять больше вычислений, чем любой другой ускоритель FHE, созданный до сих пор. «Heracles — это первое оборудование, работающее в масштабе», — говорит он. В дальнейшем компания планирует повышать скорость вычислений чипа за счёт тонкой настройки ПО. Она также будет испытывать более масштабные задачи FHE и изучать улучшения аппаратного обеспечения для потенциального следующего поколения. «Это как первый микропроцессор… начало целого пути», — отмечает Мэтью.

12.03.2026 [09:13], Сергей Карасёв

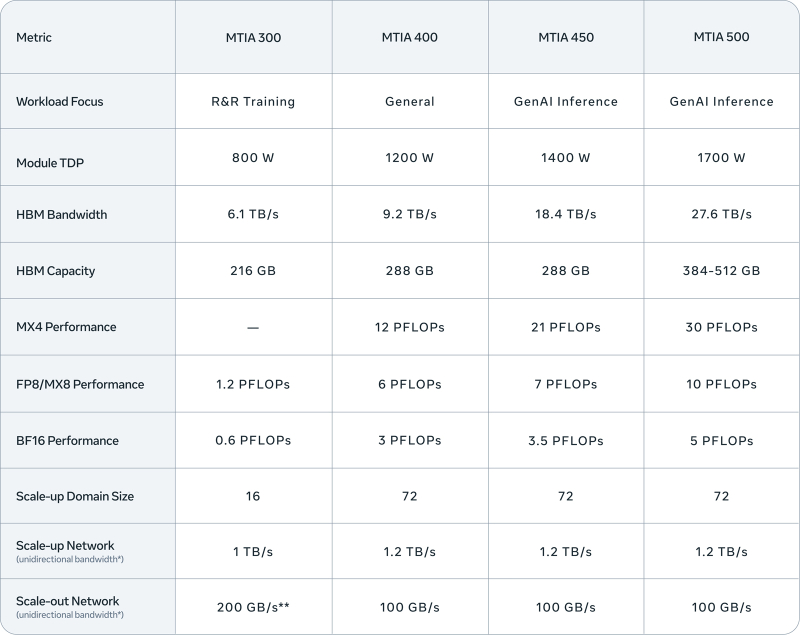

Meta✴ представила четыре новых ИИ-ускорителя MTIA — с FP8-производительностью до 10 ПфлопсКомпания Meta✴ анонсировала ИИ-ускорители MTIA (Meta✴ Training and Inference Accelerator) сразу четырёх новых поколений. Это решения MTIA 300, 400, 450 и 500: внедрение некоторых из них уже началось, тогда как развёртывание других запланировано на текущий и следующий годы. Устройства ориентированы на различные ИИ-нагрузки, включая инференс и генеративные сервисы. ИИ-процессор MTIA первого поколения (MTIA 100), напомним, дебютировал в 2023 году: изделие получило в общей сложности 128 ядер RISC-V и 128 Мбайт памяти SRAM. В 2024-м вышло решение второго поколения MTIA 200 с повышенной производительностью. В каждом из четырёх новых продуктов, по заявлениям Meta✴, упор сделан на улучшении вычислительных характеристик, пропускной способности памяти и эффективности. Конструкция ускорителя MTIA 300 включает один вычислительный чиплет, два сетевых чиплета (NIC) и несколько стеков HBM. Каждый вычислительный чиплет состоит из матрицы процессорных элементов (PE), содержащих по два векторных ядра RISC-V. Объём памяти HBM составляет 216 Гбайт, её пропускная способность — 6,1 Тбайт/с. Заявленная ИИ-производительность в режимах FP8/МХ8 достигает 1,2 Пфлопс. Показатель TDP равен 800 Вт. Реализован движок DMA для взаимодействия с локальной памятью. Ускоритель, уже применяющийся в дата-центрах Meta✴, оптимизирован для задач обучения по принципу Rephrase and Respond (R&R).

Источник изображений: Meta✴ Ступенью выше располагается решение MTIA 400 общего назначения. Оно объединяет два вычислительных чиплета, а объём памяти HBM увеличен до 288 Гбайт (пропускная способность — 9,2 Тбайт/с). У этого ускорителя быстродействие на операциях FP8/МХ8 составляет до 6 Пфлопс. Величина TDP равна 1200 Вт. 72 ускорителя MTIA 400, «провязанные» в одной стойке, образуют единый масштабируемый домен. При этом может использоваться жидкостное охлаждение с воздушной поддержкой или полностью жидкостное охлаждение. На сегодняшний день Meta✴ завершила тестирование MTIA 400 и находится на этапе внедрения изделий. Вариант MTIA 450, в свою очередь, ориентирован на задачи инференса в сфере генеративного ИИ. Этот ускоритель также использует 288 Гбайт памяти HBM, но её пропускная способность достигает 18,4 Тбайт/с. Значение TDP подросло до 1400 Вт. Решение обеспечивает ИИ-производительность в режимах FP8/МХ8 до 7 Пфлопс, в режиме МХ4 — 21 Пфлопс. MTIA 450 также поддерживает смешанные вычисления с низкой точностью без дополнительного программного преобразования данных. Внедрение этой модели в ЦОД Meta✴ намечено на начало 2027 года. Наконец, самый мощный из готовящихся ускорителей — MTIA 500 — также рассчитан на инференс в сфере генеративного ИИ. Используется конфигурация вычислительных чиплетов 2 × 2, окруженных несколькими стеками HBM и двумя сетевыми чиплетами. Это устройство может использовать от 384 до 512 Гбайт памяти HBM с пропускной способностью до 27,6 Тбайт/с. Показатель TDP достигает 1700 Вт. Заявленная производительность FP8/МХ8 — до 10 Пфлопс, МХ4 — до 30 Пфлопс. Массовое внедрение MTIA 500 запланировано на 2027 год. На системном уровне MTIA 400, 450 и 500 используют одно и то же шасси, стойку и сетевую инфраструктуру. Это обеспечивает возможность модернизации с минимальными затратами при переходе на изделия следующего поколения.

05.03.2026 [17:00], Владимир Мироненко

В ближайшие годы Broadcom не ожидает конкуренции от ИИ-компаний в разработке чиповBroadcom утверждает, что компании в сфере ИИ не смогут в ближайшем будущем создавать и развёртывать собственные чипы, отметив, что у неё имеются заказы на разработку и поставку чипов на годы вперёд, пишет The Register. В своём выступлении по итогам I квартала 2026 финансового года, завершившегося 1 февраля, президент и генеральный директор Broadcom Хок Тан (Hock Tan) отметил 106-% рост продаж чипов для ИИ-инфраструктуры в годовом исчислении, что превысило собственный прогноз и принесло $8,4 млрд за квартал. «Рост обусловлен высоким спросом на кастомные ИИ-ускорители и сетевые решения для ИИ, — заявил Хок Тан, — Рост выручки от ИИ ускоряется, и мы ожидаем, что выручка от полупроводниковых решений для ИИ во II квартале составит $10,7 млрд». Как сообщает The Register, Тан отметил успешную работу по разработке ускорителей с пятью клиентами, добавив, что он ожидает, что Google продемонстрирует «ещё больший спрос» на микросхемы Broadcom по мере развёртывания TPU следующего поколения. Anthropic вскоре внедрит TPU на 1 ГВт, разработанные Broadcom, и по словам Тана, она планирует запустить оборудование на 3 ГВт в 2027 году. Meta✴ установит «несколько гигаватт» XPU от Broadcom «в 2027 году и позже». Также ожидается, что OpenAI развернёт «более 1 ГВт вычислительных мощностей» на основе кастомных XPU в 2027 году. Тан заявил, что Broadcom уже обеспечила себе заказы на поставки всего оборудования, включая высокоскоростную память, и удовлетворения спроса до 2028 года. И он предсказал, что Broadcom будет и дальше заключать аналогичные сделки в течение многих лет, поскольку крупные облачные провайдеры и стартапы в области ИИ не могут сравниться с ней в способности проектировать и поставлять кастомные чипы. «Они сталкиваются с огромными проблемами», — сообщил Хок Тан, имея в виду привлечение талантливых разработчиков микросхем, способных создавать чипы, оптимизированные для конкретных рабочих нагрузок, управлять производственным процессом, развивать опыт в области упаковки, а затем создавать сетевые решения для своих чипов. По словам Тана, процесс создания собственных чипов должен привести к разработке микросхем, конкурентоспособных не только с NVIDIA, но и со «всеми другими игроками». Но он не видит, чтобы это стало возможным в какой-либо крупной компании или ИИ-стартапе, «в течение многих лет». Бизнес Broadcom в сфере сетевых решений, ориентированных на ИИ, также переживает бум, увеличив выручку на 60 % год к году. Тан заявил, что в следующем году компания представит чип-коммутатор Tomahawk 7, который вдвое превысит по производительности текущую модель, и сделает то же самое для своих медных интерконнектов, а это значит, что у клиентов не будет необходимости в рассмотрении перехода на оптические сети. Общий доход группы полупроводниковых решений Semiconductor Solutions за квартал составил $12,52 млрд, что на 52 % больше, чем годом ранее и выше прогнозируемых аналитиками StreetAccount $12,25 млрд (по данным CNBC). Выручка от чипов, не связанных с ИИ, осталась на уровне $4,1 млрд. Во II финансовом квартале компания прогнозирует выручку на этом же уровне, что на 4 % больше год к году. Бизнес Broadcom по разработке инфраструктурного ПО, объединяющий CA, Symantec Enterprise и VMware, показал рост выручки на 1 %, достигнув $6,8 млрд, что ниже консенсус-прогноза StreetAccount в $7,02 млрд. При этом выручка VMware выросла на 13 %. «Наше инфраструктурное ПО не подвержено влиянию ИИ», — подчеркнул Тан, комментируя падение акций некоторых компаний из-за появления новых разработок ИИ-стартапов в сфере программирования. В отчётном квартале выручка Broadcom выросла на 29 % год к году до $19,31 млрд при консенсус-прогнозе аналитиков, опрошенных LSEG, в размере $19,18 млрд. Скорректированная прибыль на акцию (Non-GAAP) составила $2,05 при консенсус-прогнозе от LSEG в $2,03. Чистая прибыль (GAAP) выросла до $7,35 млрд, или $1,50 на акцию, по сравнению с $5,50 млрд, или $1,14 на акцию годом ранее. Во II квартале 2026 финансового года Broadcom прогнозирует выручку в размере $22,0 млрд (рост год к году на 47 %), что превышает средний прогноз в $20,56 млрд, согласно данным LSEG. Также компания прогнозирует скорректированную EBITDA в 68 %. Кроме того, согласно прогнозу Broadcom выручка группы полупроводниковых решений Semiconductor Solutions составит $14,8 млрд (рост год к году на 76 %), выручка подразделения по разработке инфраструктурного ПО — $7,2 млрд (рост — 9 %), согласно данным MarketBeat.

24.02.2026 [23:00], Владимир Мироненко

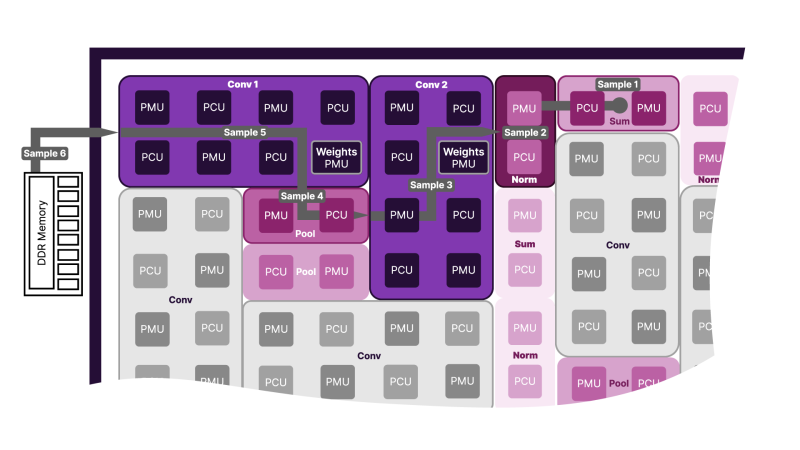

SambaNova представила ИИ-ускоритель SN50 и объявила о расширении партнёрства с IntelSambaNova представила ИИ-ускорители пятого поколения SN50 на основе фирменных RDU (Reconfigurable Dataflow Unit), которые, по словам компании, «обеспечивает непревзойденное сочетание сверхнизкой задержки, высокой пропускной способности и энергоэффективной производительности для рабочих нагрузок ИИ-инференса, коренным образом меняя экономику генерации токенов». Кроме того, объявлено об инвестициях и сотрудничестве с Intel, которая передумала покупать SambaNova целиком. Как отметил The Register, новый чип представляет собой значительное улучшение по сравнению с SN40L 2023 года. По данным компании, SN50 обеспечивает в 2,5 раза более высокую производительность при 16-бит вычислениях (1,6 Пфлопс) и в 5 раз более высокую производительность в режиме FP8 (3,2 Пфлопс). В основе SN50 лежит архитектура потоковой обработки данных (SambaNova DataFlow). Как и в предшественнике, в SN50 используется трёхуровневая иерархия памяти, которая сочетает в себе DDR5, HBM и SRAM, что позволяет платформам на основе новинки поддерживать ИИ-модели с 10 трлн параметров и длиной контекста до 10 млн токенов. Каждый RDU оснащен 432 Мбайт SRAM, 64 Гбайт HBM2E с пропускной способностью 1,8 Тбайт/с и от 256 Гбайт до 2 Тбайт памяти DDR5. Доступность HBM2E и конфигурируемый объём DDR5 позволят повысить привлекательность и доступность SN50 на фоне дефицита памяти. Каждый ускоритель получил интерконнект со скоростью 2,2 Тбайт/с (в каждую сторону) для связи с другими чипами через коммутируемую фабрику. Как утверждает SambaNova, по сравнению с ускорителем NVIDIA B200, SN50 обеспечивает в 5 раз большую максимальную скорость генерации токенов на пользователя и более чем в 3 раза большую пропускную способность для агентного инференса, что было продемонстрировано на примере ряда моделей, таких как Meta✴ Llama 3.3 70B. Архитектура позволяет эффективно разгружать KV-кеш и переключаться между моделям в HBM и SRAM в режиме «горячей замены» за миллисекунды, что крайне важно для агентных рабочих нагрузок, часто переключающихся между несколькими ИИ-моделями. Также в SN50 входные токены могут кешироваться в памяти, сокращая время предварительной обработки и время ожидания первого токена (TTFT) для запросов. Такое сочетание производительности, эффективности и масштабируемости обеспечивает преимущество в совокупной стоимости владения (TCO), по словам компании, не имеющее аналогов на рынке, для поставщиков сервисов инференса, использующих такие модели, как OpenAI GPT-OSS, с восьмикратной экономией по сравнению с NVIDIA B200. SN50 ориентирован и на такие приложения, как голосовые помощники на основе ИИ, требующие сверхнизкой задержки для работы в режиме реального времени. По заявлению компании, он сможет обеспечить работу тысяч одновременных сессий. Также была представлена 20-кВт система SambaRack SN50, которая объединяет 16 чипов SN50. SambaRack могут масштабироваться до кластера из 256 ускорителей с пропускной способностью интерконнекта в несколько Тбайт/с, что сокращает время обработки запросов и поддерживает большие размеры пакетов. В результате можно развёртывать модели с более высокой пропускной способностью и быстродействием. Поставки SN50 клиентам начнутся во II половине 2026 года. Раннее SambaNova сообщила о привлечении более $350 млн в рамках переподписанного раунда финансирования серии E, возглавляемого частной инвестиционной компанией Vista Equity Partners при партнёрстве с Cambium Capital. В нём также приняло «активное участие» инвестиционное подразделение Intel — Intel Capital, сообщил SiliconANGLE. Также SambaNova заявила о сотрудничестве с Intel в разработке новых высокопроизводительных и экономически эффективных систем для выполнения ИИ-задач. Цель — предоставить предприятиям альтернативу GPU, которые сегодня используются в большинстве рабочих нагрузок. Intel инвестирует в стартап, чтобы ускорить развёртывание нового «облачного решения для ИИ» на базе существующей платформы SambaNova Cloud. Обновлённая платформа, оптимизированная для многомодальных LLM, получит процессоры Xeon, а также GPU, сетевые и иные решения Intel, в том числе в области СХД. Идёт ли речь о создании специализированных моделей Xeon, как это было в случае NVIDIA, не уточняется. В дальнейшем Intel и SambaNova планируют совместно продвигать и продавать новую платформу, используя существующие связи Intel с предприятиями и партнёрские каналы. Партнёрство несёт выгоду обеим компаниям. SambaNova сможет воспользоваться глобальным охватом и производственной базой Intel для масштабирования своих ИИ-ускорителей, а Intel получит шанс наконец-то заявить о себе на ИИ-рынке. До сих пор Intel не могла конкурировать с NVIDIA и другими производителями чипов, такими как AMD, в ИИ-сфере. Чипы SN50 от SambaNova в сочетании с процессорами Intel Xeon потенциально могут изменить эту ситуацию. Стоит отметить, что у Intel, которая сама чувствует себя не лучшим образом, есть довольно крупная сделка с NVIDIA. Компания также предлагает собственные GPU для инференса, пусть и значительно более простые в сравнении с SN50, и даже странные гибриды из ускорителей Habana Gaudi 3 и NVIDIA B200. Наконец, имеется и сделка с AWS по выпуску кастомных Xeon 6 и неких ИИ-ускорителей. Что касается старых «коллег» SambaNova в деле борьбы с NVIDIA, то Groq в итоге была поглощена последней, а Cerebras, наконец, подписала заметную сделку с действительно крупным игроком на рынке ИИ — OpenAI.

23.02.2026 [22:57], Владимир Мироненко

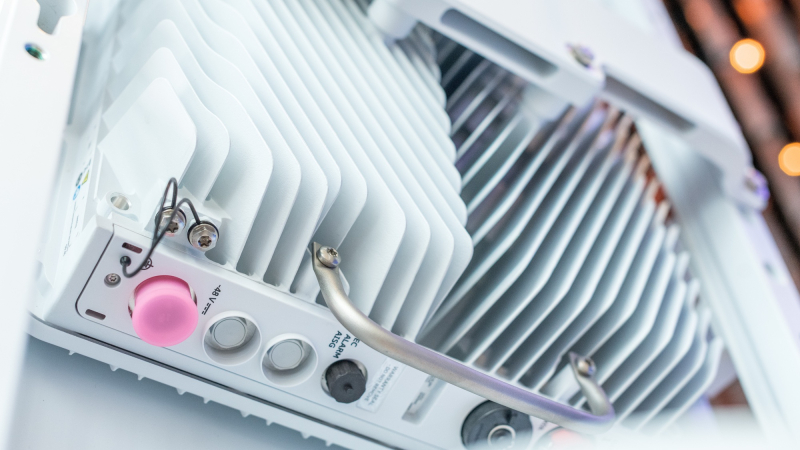

Чипы AMD прожорливы, NVIDIA — дороги, а Intel — ненадёжны: Ericsson остаётся верна кастомным ASICEricsson представила свой первый набор продуктов AI-RAN, подчеркнув приверженность стратегии, основанной на собственных ASIC для повышения производительности сетей радиодоступа (RAN). В то время как беспроводная индустрия всё чаще обращается к виртуализированным/облачным RAN с использованием универсальных процессоров (GPP) Intel, Ericsson защищает свои продолжающиеся инвестиции в кастомные чипы для высокопроизводительных задач, отметил ресурс IEEE ComSoc Technology Blog. Впрочем, Intel остаётся ключевым партнёром Ericsson, а вот с AMD и NVIDIA у компании не заладилось. Портфель решений Ericsson для RAN базируется на двух основных архитектурах. Большая часть основана на ASIC, разработанных как собственными силами, так и в партнёрстве с Intel. Также портфель включает Cloud RAN, которая объединяет программный стек Ericsson с процессорами Intel Xeon EE. Несмотря на надежды отрасли, что виртуализация позволит отделить аппаратное обеспечение от программного, Intel остаётся единственным партнером Ericsson по поставке микросхем для массового развёртывания, что создаёт некоторые риски. Фактически Ericsson подтвердила «коммерческую поддержку» исключительно решений Intel, в то время как в случае AMD, Arm и NVIDIA всё по-прежнему ограничивается «поддержкой прототипов». Несмотря на многолетние заявления отрасли о необходимости разнообразия микросхем в экосистеме vRAN, прогресс, похоже, застопорился. Кроме того, интеграция ИИ в ПО RAN добавляет новые уровни сложности, которые могут ещё больше укрепить зависимость компании от «железа» одного вендора. Отраслевые наблюдатели по-прежнему скептически относятся к стремлению Ericsson к «единому программному стеку» для гетерогенных аппаратных платформ. Хотя аппаратная и программная дезагрегация достижима на более высоких уровнях (L2/L3), PHY-уровень L1 — наиболее ресурсоёмкая часть стека — остаётся сильно оптимизированным для конкретного «кремния». Первоначально Ericsson рассчитывала на переносимость L1-кода между x86 (в т.ч. AMD) и Arm SVE2 (NVIDIA Grace) для соответствия возможностям Intel AVX-512. Однако достижение высокой производительности на этих платформах без существенного рефакторинга остается серьёзной инженерной проблемой. Критическим узким местом в обработке L1-трафика является коррекция ошибок (Forward Error Correction), которая традиционно требует выделенного аппаратного ускорения. Ericsson первоначально полагалась на разгрузку с переносом задач FEC на дискретные PCIe-ускорители Intel. Затем Intel внедрила ускорение FEC в Xeon EE в рамках vRAN Boost. Попытки использовать FPGA AMD показали их невысокую энергоэффективность, а GPU NVIDIA оказались слишком дороги для такой задачи. Однако развитие AI-RAN изменило экономику, поскольку теперь ускорители можно использовать как для RAN, так и для ИИ-задач. Так, Ericsson заинтересовали тензорные процессоры Google (TPU). Тем не менее, несмотря на стремление к созданию «единого ПО», планы Ericsson подтверждают существование проблем в реализации этой идеи. В то время как уровни L2 и выше используют универсальную кодовую базу для всех аппаратных платформ, уровень L1 требует адаптации под конкретные чипы. Чтобы избежать зависимости от одного поставщика чипов, компания уделяет приоритетное внимание развитию HAL (Hardware Abstraction Layers), что позволит портировать ПО на разные аппаратные платформы с минимальными изменениями. Основные инициативы включают внедрение интерфейса BBDev (Baseband Device) для отделения ПО RAN от базового аппаратного обеспечения. Рассматривается даже возможность интеграции с NVIDIA CUDA, но здесь многое зависит от более широкой отраслевой стандартизации. Что касается радиосвязи, менее подверженной полной виртуализации, Ericsson встраивает процессоры Neural Network Accelerators (NNA) непосредственно в радиомодули. Эти программируемые матричные ядра оптимизированы для обработки данных в системах Massive MIMO, обеспечивая формирование луча и оценку канала за доли миллисекунды при соблюдении строгих ограничений по мощности. Новые AI-радиомодули оснащены ASIC Ericsson с NNA. Утверждается, что они расширяют возможности локального инференса в радиосистемах Massive MIMO, обеспечивая оптимизацию в реальном времени. |

|