Материалы по тегу: risc-v

|

29.04.2026 [01:23], Владимир Мироненко

Tenstorrent представила ИИ-серверы Galaxy Blackhole для быстрой генерации токенов и без дезагрегацииTenstorrent представила вычислительную систему Galaxy Blackhole на базе ускорителей Blackhole с архитектурой RISC-V, которая позиционируется как системная ИИ-платформа, способная конкурировать с другими решениями за счёт стабильной производительности инференса, высокоскоростного доступа к памяти и масштабируемой сети — трёх факторов, которые всё чаще определяют эффективность развёртывания ИИ в реальных условиях, пишет Forbes. 6U-сервер Tensorrent Galaxy Blackhole с воздушным охлаждением основан на 32 ИИ-ускорителях Blackhole суммарной производительностью 23 Пфлопс в режиме FP8. Система включает 6,2 Гбайт SRAM (суммарно 2,9 Пбайт/с) и 1 Тбайт GDDR6 (суммарно 16 Тбайт/с). Высокоскоростную связь между узлами при горизонтальном масштабировании обеспечивают 800GbE-порты — до 56 портов на систему с общей пропускной способностью 11,2 Тбайт/с (в дуплексе). Стоимость системы Tensorrent Galaxy Blackhole составляет $110 тыс. Восьмичиповые системы NVIDIA DGX будут производительнее, но и обойдутся в три-пять раз дороже, сообщил The Register. Базовый суперкластер Galaxy Supercluster стоимостью в $440 тыс. включает четыре системы Blackhole. При этом архитектура Tenstorrent поддерживает масштабирование до 32 узлов с 1024 ускорителями. Mesh-сеть Tenstorrent не ограничивается одним узлом. Подобно кластерам TPU от Google или Trainium2 от Amazon, её можно расширить для поддержки более крупных моделей, более высокой пропускной способности или большей интерактивности, добавив больше узлов и отрегулировав параллелизм тензоров и конвейеров. Как сообщает Tenstorrent, для DeepSeek V3 её четырёхузловые суперкластеры Blackhole Galaxy Supercluster могут обрабатывать запрос на 100 тыс. токенов — эквивалент 166 страниц текста — менее чем за четыре секунды. Tenstorrent заявила, что кластеры Galaxy Blackhole могут генерировать видео быстрее, чем в реальном времени, а также очень быстро генерировать токены LLM. Демонстрационные версии систем Tenstorrent настроены на обычный режим с генерацией текста с удобочитаемой скоростью, и режим Blitz, обеспечивающий максимально быструю обработку данных, подходящую для таких приложений, как генерация кода и агентный ИИ. В режиме Blitz MoE-модель DeepSeek-671B обеспечивает «до 350 т/с на пользователя со временем получения первого токена менее 4 с», сообщила компания. Ресурс EE Times протестировал этот режим за несколько дней до официального запуска, получив 255 т/с на пользователя для коротких запросов в стиле чат-бота. Этот режим поддерживает пакетную обработку от 8 до 64 и длину контекста до 128 тыс токенов. Он работает на 16 серверах Galaxy (512 чипов) с использованием конвейерного параллелизма на этапе декодирования. Компания отметила, что её системы не нуждаются в дезагрегации. «Мы можем выполнять и [предварительное заполнение, и декодирование] на одном узле, — сообщил генеральный директор Tenstorrent Джим Келлер (Jim Keller) изданию EE Times. — Мы создаём большой кластер, на котором можно запускать предварительное заполнение и декодирование LLM, генерацию видео, агентный ИИ… мы не специализируемся на чём-то одном. У нас много чипов, большой объём SRAM, но все чипы имеют DRAM, и все они тесно связаны между собой, поэтому наша платформа гораздо более универсальна».

27.04.2026 [12:54], Сергей Карасёв

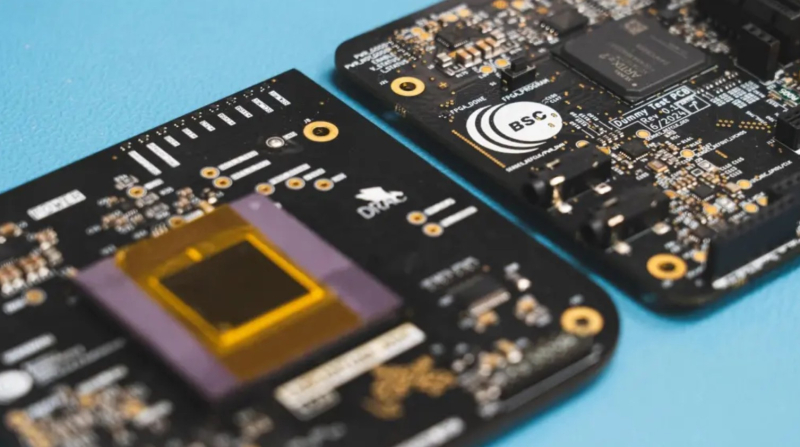

Одноплатный компьютер Banana Pi BPI-SM10 получил чип RISC-V с ИИ-производительностью 60 TOPSКоманда Banana Pi анонсировала мини-компьютер BPI-SM10, подходящий для проектирования устройств с ИИ-функциями. В основу новинки, состоящей из вычислительного модуля и сопутствующей интерфейсной платы, положен процессор с архитектурой RISC-V. CPU-модуль построен на чипе SpacemiT K3. Он содержит восемь 64-бит ядер RISC-V X100 с тактовой частотой до 2,4 ГГц и восемь ИИ-ядер RISC-V A100 с общей производительностью до 60 TOPS на операциях INT4. Есть интегрированный графический контроллер Imagination Technologies BXM4-64-MC1 с поддержкой Vulkan 1.3, OpenGL 3.0 и OpenGL ES 1.1/2.0/3.2. Возможно декодирование материалов 4K120 (H.264/H.265/VP9), а также кодирование 4K60 (H.264/H.265). Объём оперативной памяти LPDDR5-6400 может достигать 32 Гбайт.

Источник изображения: Banana Pi Интерфейсная плата располагает коннекторами M.2 Key M (PCIe 3.0 x4) и M.2 Key M (PCIe 3.0 x1) для SSD, слотом M.2 Key E для адаптера Wi-Fi, а также сетевым портом 1GbE. Есть четыре разъёма USB 3.0 Type-A, порт USB Type-C и интерфейс DisplayPort 1.2. Среди прочего упомянуты 40-контактная колодка (UART, SPI, I2S, I2C, GPIO), два интерфейса MIPI CSI и один интерфейс MIPI DSI. Питание подаётся через DC-разъём. Размеры составляют 103 × 90,5 × 35 мм. Допускается монтаж активного кулера с радиатором и вентилятором. Утверждается, что новинка способна поддерживать работу ИИ-моделей, насчитывающих до 30 млрд параметров, обеспечивая при этом производительность на уровне 10 токенов в секунду. Banana Pi BPI-SM10 может стать основой ИИ-терминалов, систем промышленной автоматизации и машинного зрения, шлюзов AIoT, робототехнических платформ и пр.

21.04.2026 [08:49], Руслан Авдеев

Испанцы разрабатывают аппаратный «стоп-кран» для защиты от бэкдоров в зарубежных чипахНа фоне изменчивой геополитической обстановки и сопутствующих проблем Национальный центр суперкомпьютерных вычислений Барселоны (Barcelona Supercomputing Center, BSC) совместно с Политехническим университетом Каталонии (Politècnica de Catalunya, UPC) запустили проект Safe and Secure Technologies, сообщает EE Times. Он предназначен для разработки безопасных чипов для критической инфраструктуры и экстренных служб. Проект обеспечит разработки для сфер, в которых сбои в работе оборудования и угрозы безопасности могут иметь серьёзные последствия. В числе прочего это касается энергосетей, автомобильной промышленности, железнодорожного транспорта, телеком-сектора, гражданской обороны и др. ЕС стремится снизить зависимость от внешних технологий, поэтому Safe and Secure Technologies должен поспособствовать достижению технологического суверенитета. В компании заявляют, что уязвимость часто заключается не в доступности оборудования, а в его происхождении. Проблема в том, что Европа в контексте чипов для критически важных систем во многом зависит от технологий из США, Тайваня и Юго-Восточной Азии в целом. Предполагается, что при определённых условиях сторонние игроки могут, например, использовать недокументированный бэкдор для полного отключения энергосистемы и др.

Источник изображения: Barcelona Supercomputer Center Акцент в проекте сделан не на создании собственных уникальных решений, а на прозрачности, позволяющей полностью проверить безопасность продуктов. Основным аппаратным компонентом проекта станет т.н. «остров безопасности» (Safety Island), созданный на основе наработок европейских программ De-RISC, SELENE, ISOLDE и FRACTAL — интегрированный модуль обеспечения безопасности. Этот компонент будет устанавливаться в непосредственной близости от процессора и гарантирует, что устройство будет работать в соответствии со спецификации, необходимыми пользователю. Фактически модуль контролирует работу основного процессора, отслеживает выполнение им задач в режиме реального времени и распределение ресурсов. Если эти условия не соблюдаются, модуль способен или сам принять меры, или инициировать прерывание, чтобы ПО или операционная система отреагировали на него в соответствии с пользовательскими запросами. Заявлено, что разработанное «железо» может выйти из строят только в исключительных обстоятельствах. В этому случае оно распознаёт ситуацию и контролируемым образом прерывает исполнение до того, как остальная система получит ошибочные инструкции.

Источник изображения: Barcelona Supercomputer Center Разработка Safe and Secure Technologies ориентирована в первую очередь на интеграцию с продуктами на базе RISC-V, но в целом «ядро», предназначенное для размещения в хост-процессоре, можно интегрировать и с чипами Intel, Arm и AMD. Учитывая будущие нормативные требования и требования к безопасности продуктов, компания намерена поддерживать передовые стандарты криптографии. Строго говоря, продукт не является «криптографическим чипом как таковым», поскольку в его задачи входит контроль над функциями безопасности, но в будущем по запросу клиентов можно добавить даже поддержку «квантовой криптографии». У компании не будет собственных производственных мощностей, основное внимание она будет уделять проектированию, а собственно выпуск поручат контрактным производителям. Сейчас проект работает над привлечением капитала, чтобы поменьше зависеть от государственных субсидий. Хотя возможности для государственного финансирования открыты, они не являются основным драйвером разработок. Переговоры с инвесторами продолжаются, ожидается, что в конечном итоге численность персонала составит несколько десятков человек. Выход на рынок будет зависеть от капитализации, начать работы планируется через 6-12 месяцев, после чего возможно значительное ускорение. Safe and Secure Technologies — уже пятнадцатый проект, «отпочковавшийся» от BSC. Ранее коммерческие предприятия центра уже привлекли €44 млн частного капитала и наняли более 600 специалистов. В феврале сообщалось, что BSC уже активно участвует в гонке за обретением Европой технологического суверенитета. Первый европейский суверенный RISC-V-процессор Cinco Ranch изготовлен по техпроцессу Intel 3. В этом приняла непосредственное участие Лаборатория суперкомпьютерных вычислений (BZL) центра BSC-CNS, а в апреле появилась информация, что процессор готов к началу массового производства.

10.04.2026 [09:26], Сергей Карасёв

Разработчик RISC-V-ядер SiFive привлёк на развитие $400 млнКомпания SiFive, специализирующаяся на разработке процессорных ядер с архитектурой RISC-V, объявила о проведении переподписанного раунда финансирования Series G, в ходе которого на дальнейшее развитие привлечено $400 млн. При этом SiFive получила оценку на уровне $3,65 млрд. Отмечается, что традиционные CPU играют важную роль в инфраструктурах агентного ИИ, где берут на себя сложные задачи координации на системном уровне. Дело в том, что GPU и специализированные ИИ-ускорители для таких операций не предназначены. Поэтому по мере развития ИИ-агентов возрастает спрос на высокоэффективные CPU. Компания SiFive стремится удовлетворить потребность в таких изделиях, заменяя энергоёмкие устаревшие архитектуры современными решениями на базе RISC-V.

Источник изображения: SiFive Раунд финансирования Series G проведён под руководством Atreides Management. В число инвесторов вошли Apollo Global Management, NVIDIA, Point72 Turion, T. Rowe Price Investment Management, Prosperity7 Ventures и Sutter Hill Ventures. Полученные деньги SiFive намерена направить на увеличение штата специалистов с целью ускорения разработки передовых RISC-V-решений для дата-центров следующего поколения, ориентированных на агентный ИИ. Одним из ключевых направлений деятельности названо расширение научно-исследовательских работ по созданию высокопроизводительных скалярных, векторных и матричных RISC-V-изделий. Кроме того, будет ускорено развитие сопутствующей программной экосистемы с использованием CUDA, а также инструментов RedHat и Ubuntu. Планируется тесное сотрудничество с клиентами и участниками отрасли. В целом, как отмечается, архитектура RISC-V имеет хорошие перспективы в сегменте дата-центров, предназначенных для работы с ИИ.

24.03.2026 [23:10], Владимир Мироненко

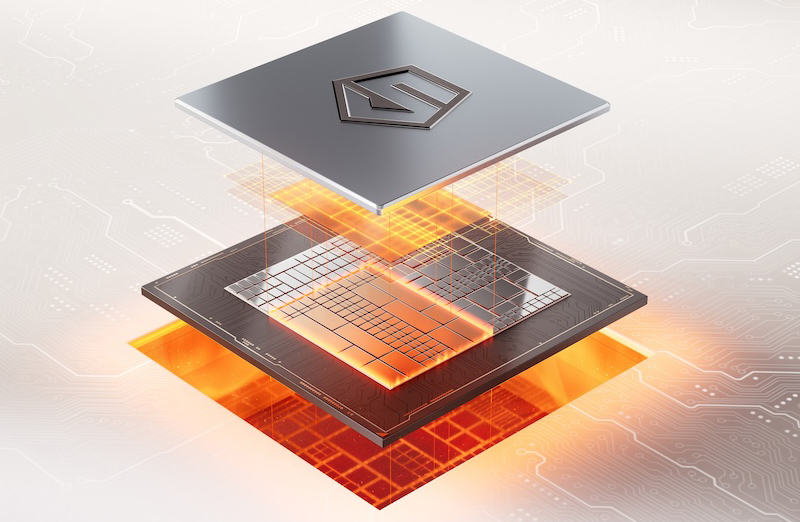

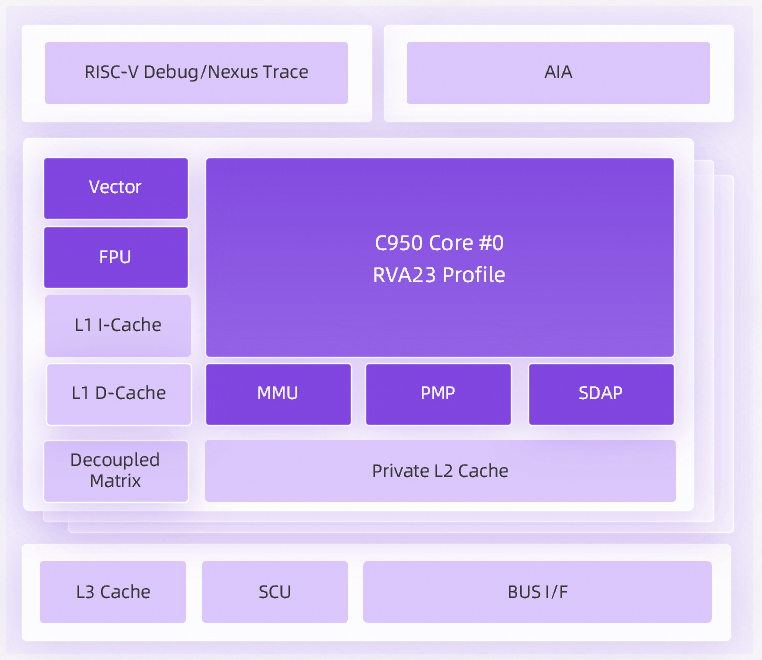

Alibaba представила самый производительный в мире процессор на базе RISC-V — XuanTie C950Alibaba представила серверный процессор XuanTie C950 с частотой 3,2 ГГц, созданный на основе открытой архитектуры RISC-V и изготовленный по 5-нм техпроцессу, сообщил ресурс SCMP. Как заявила компания, процессор оптимизирован для облачных вычислений и ИИ-нагрузок, и сможет обрабатывать многоэтапные задачи, выполняемые ИИ-агентами. По словам компании, это «самый высокопроизводительный процессор с архитектурой RISC-V в мире». Мэн Цзяньи (Meng Jianyi), главный научный сотрудник DAMO Academy, исследовательского подразделения Alibaba, заявил, что производительность C950 более чем в три раза больше, чем у C920 прошлого поколения. «Открытая природа RISC-V позволяет разработчикам микросхем настраивать наборы инструкций и ускорять выполнение конкретных задач ИИ без или с низкими лицензионными сборами. Это особенно важно для разработки ИИ-агентов», — приводит Reuters сообщение компании.

Источник изображения: Alibaba Подразделение DAMO Academy, разработавшее дизайн чипа, сообщило, что XuanTie «могут быть настроены под конкретные шаблоны инференса, помогая клиентам адаптировать чипы под свои нужды». Alibaba добавила, что по сравнению с некоторыми массовыми продуктами её процессор обеспечивает более чем 30 % «улучшение производительности благодаря гибкости в настройке для конкретных сценариев использования». На разработку C950 потребовалось два года, и это первый чип в линейке XuanTie, разработанный с нуля с учётом выполнения инференса LLM как базовой рабочей нагрузки. Предыдущий серверный чип, C930, был представен в феврале 2025 года, его поставки стартовали спустя месяц. Его предшественник, C920, поставляется с 2024 года. XuanTie C950 — это 64-бит процессор с декодером шириной 8 инструкций и 16-стадийным конвейером, предсказателем ветвлений TAGE и настраиваемым механизмом предвыборки, соответствующий профилю RVA23 и дополненный некоторыми другими инструкциями. Заявленная производительность в SPECint2006 составляет 22/ГГц. Чип включает 256-бит векторные регистры и поддержку FP16/BF16/FP32/FP64/INT8/INT16/INT32/INT64. Типовой объём кеша инструкций составляет 64 Кбайт с опциональной проверкой чётности, кеша данных — тоже 64 Кбайт, ECC опционально. L2-кеш собственный у каждого ядра — типовой объём составляет 1 Мбайт, ECC опционально. Типовой кластер состоит из 8 ядер. Для внутренней связи используется шина CHI.E/CHI.F, для внешней — AMBA ACE4.0/AXI4.0. Благодаря совместной оптимизации программного и аппаратного обеспечения, C950 обеспечивает высокую производительность в облачных вычислениях, включая запуск MySQL, Redis, Nginx и OpenSSL, инференс больших языковых моделей, включая Qwen и DeepSeek, а также при использовании вместе с разработанными компанией интегрированными ИИ-движками — Alibaba Vector Acceleration Engine и Matrix Acceleration Engine. Оба движка разработаны совместно с CPU-ядрами, а не «прилеплены» к ним. C950 — первый процессор RISC-V, который изначально поддерживает инференс LLM с миллиардом параметров на аппаратном уровне, утверждает компания. Расширения набора инструкций и аппаратные блоки разработаны для выполнения основных операций таких моделей, как Qwen3 и DeepSeek V3, без накладных расходов. C950 является флагманом портфолио чипов Alibaba.

13.03.2026 [11:29], Сергей Карасёв

Tenstorrent представила настольную ИИ-систему TT-QuietBox 2 с СЖО на базе RISC-VКанадский стартап Tenstorrent анонсировал настольную рабочую станцию TT-QuietBox 2, предназначенную для решения ресурсоёмких задач в области ИИ. Утверждается, что новинка способна поддерживать большие языковые модели, насчитывающие до 120 млрд параметров. Ключевой составляющей TT-QuietBox 2 являются четыре фирменных ускорителя Blackhole. Каждый из них содержит 16 «больших» ядер RISC-V, 120 ядер Tensix, 210 Мбайт памяти SRAM и 32 Гбайт памяти GDDR6 с пропускной способностью 512 Гбайт/с. Таким образом, в общей сложности задействованы 64 ядра RISC-V, 480 ядер Tensix и 128 Гбайт памяти GDDR6. Рабочая станция также несёт на борту 256 Гбайт памяти DDR5. Реализована система жидкостного охлаждения. Питание осуществляется от обычной розетки: производитель подчеркивает, что станции не требуется специально оборудованное помещение или серверная стойка. На устройстве применяется платформа Ubuntu 24.04; используется полностью открытый программный стек. Заявлена поддержка популярных фреймворков, таких как PyTorch, ONNX и TensorFlow. Суммарная пиковая производительность на операциях ИИ достигает 2654 Тфлопс (BlockFP8). В качестве примера приводится работа с моделью Llama 3.1 70B (70 млрд параметров): быстродействие составляет 476,5 токена/с. А модель Boltz-2 формирует структуру белка из 686 аминокислот за 49 с (на одном чипе Blackhole). Для сравнения, современному процессору для выполнения такой задачи, как утверждается, требуется около 45 мин. Благодаря наличию сразу четырёх ускорителей Blackhole система способна параллельно моделировать структуры нескольких белков. В продажу станция TT-QuietBox 2 поступит во II квартале нынешнего года по ориентировочной цене $10 тыс.

12.03.2026 [09:13], Сергей Карасёв

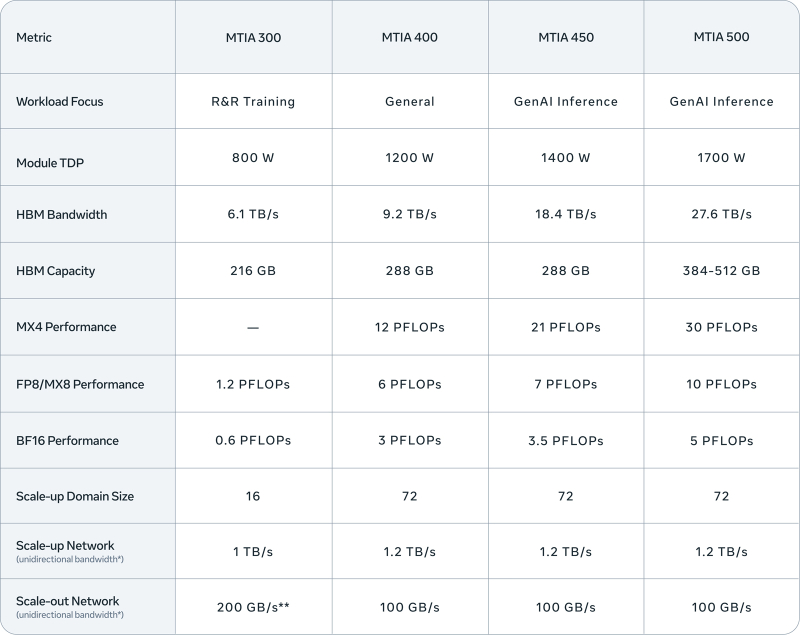

Meta✴ представила четыре новых ИИ-ускорителя MTIA — с FP8-производительностью до 10 ПфлопсКомпания Meta✴ анонсировала ИИ-ускорители MTIA (Meta✴ Training and Inference Accelerator) сразу четырёх новых поколений. Это решения MTIA 300, 400, 450 и 500: внедрение некоторых из них уже началось, тогда как развёртывание других запланировано на текущий и следующий годы. Устройства ориентированы на различные ИИ-нагрузки, включая инференс и генеративные сервисы. ИИ-процессор MTIA первого поколения (MTIA 100), напомним, дебютировал в 2023 году: изделие получило в общей сложности 128 ядер RISC-V и 128 Мбайт памяти SRAM. В 2024-м вышло решение второго поколения MTIA 200 с повышенной производительностью. В каждом из четырёх новых продуктов, по заявлениям Meta✴, упор сделан на улучшении вычислительных характеристик, пропускной способности памяти и эффективности. Конструкция ускорителя MTIA 300 включает один вычислительный чиплет, два сетевых чиплета (NIC) и несколько стеков HBM. Каждый вычислительный чиплет состоит из матрицы процессорных элементов (PE), содержащих по два векторных ядра RISC-V. Объём памяти HBM составляет 216 Гбайт, её пропускная способность — 6,1 Тбайт/с. Заявленная ИИ-производительность в режимах FP8/МХ8 достигает 1,2 Пфлопс. Показатель TDP равен 800 Вт. Реализован движок DMA для взаимодействия с локальной памятью. Ускоритель, уже применяющийся в дата-центрах Meta✴, оптимизирован для задач обучения по принципу Rephrase and Respond (R&R).

Источник изображений: Meta✴ Ступенью выше располагается решение MTIA 400 общего назначения. Оно объединяет два вычислительных чиплета, а объём памяти HBM увеличен до 288 Гбайт (пропускная способность — 9,2 Тбайт/с). У этого ускорителя быстродействие на операциях FP8/МХ8 составляет до 6 Пфлопс. Величина TDP равна 1200 Вт. 72 ускорителя MTIA 400, «провязанные» в одной стойке, образуют единый масштабируемый домен. При этом может использоваться жидкостное охлаждение с воздушной поддержкой или полностью жидкостное охлаждение. На сегодняшний день Meta✴ завершила тестирование MTIA 400 и находится на этапе внедрения изделий. Вариант MTIA 450, в свою очередь, ориентирован на задачи инференса в сфере генеративного ИИ. Этот ускоритель также использует 288 Гбайт памяти HBM, но её пропускная способность достигает 18,4 Тбайт/с. Значение TDP подросло до 1400 Вт. Решение обеспечивает ИИ-производительность в режимах FP8/МХ8 до 7 Пфлопс, в режиме МХ4 — 21 Пфлопс. MTIA 450 также поддерживает смешанные вычисления с низкой точностью без дополнительного программного преобразования данных. Внедрение этой модели в ЦОД Meta✴ намечено на начало 2027 года. Наконец, самый мощный из готовящихся ускорителей — MTIA 500 — также рассчитан на инференс в сфере генеративного ИИ. Используется конфигурация вычислительных чиплетов 2 × 2, окруженных несколькими стеками HBM и двумя сетевыми чиплетами. Это устройство может использовать от 384 до 512 Гбайт памяти HBM с пропускной способностью до 27,6 Тбайт/с. Показатель TDP достигает 1700 Вт. Заявленная производительность FP8/МХ8 — до 10 Пфлопс, МХ4 — до 30 Пфлопс. Массовое внедрение MTIA 500 запланировано на 2027 год. На системном уровне MTIA 400, 450 и 500 используют одно и то же шасси, стойку и сетевую инфраструктуру. Это обеспечивает возможность модернизации с минимальными затратами при переходе на изделия следующего поколения.

09.03.2026 [16:39], Владимир Мироненко

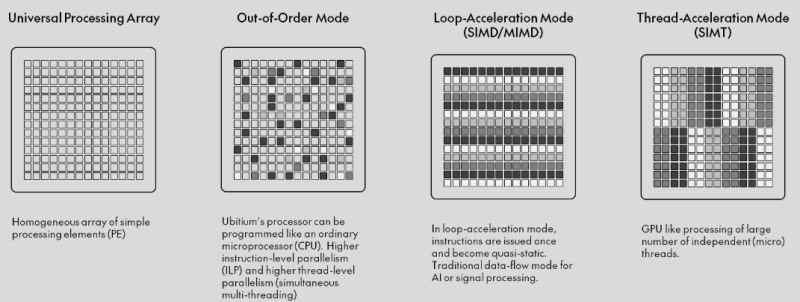

Ubitium стала на шаг ближе к выпуску универсального RISC-V процессора, заменяющего CPU, GPU, DSP и FPGAНемецкий стартап Ubitium объявил о завершении стадии tape-out (финальный этап проектирования) универсального RISC-V-процессора, изготовленного по 8-нм техпроцессу Samsung Foundry и предназначенного для рынка встроенных вычислительных систем автомобилей, промышленного оборудования и бытовой электроники, включая радарные и многосенсорные сигнальные цепи, аудио и голосовую связь в реальном времени, компьютерное зрение, периферийный ИИ, промышленный человеко-машинный интерфейс (HMI) и т.д. В основе процессора Ubitium лежит «универсальный процессорный массив» (Universal Processing Array) — программно-определяемая система с 256 элементами, объединяющая функции CPU, GPU, DSP и FPGA и способная мгновенно менять режимы выполнения во время работы. Такая унификация позволяет чипу переключаться между режимом работы в качестве CPU общего назначения для обслуживания ОС и режимом работы в качестве ИИ-ускорителя, избегая задержек при передаче данных между отдельными чипами.

Источник изображения: Ubitium Завершение tape-out на 8-нм техпроцессе Samsung подтверждает работоспособность основного процессорного массива и интерфейса LPDDR5. Для Ubitium доказательство того, что один процессор может обрабатывать общие вычислительные задачи, задачи обработки в реальном времени и задачи ИИ на одном кристалле, является важным шагом на пути к коммерческой жизнеспособности, отметил EE Times. «Это решение претворяет давно существующую концепцию в жизнь», — заявил Мартин Форбах (Martin Vorbach), технический директор Ubitium. «Встроенные системы переросли архитектуры, на которые сегодня опирается отрасль. Консолидация больше не является необязательной. Она неизбежна», — добавил он. Технология, лежащая в основе этого проекта, совершенствовалась более 15 лет. Для её воплощения в жизнь Форбахом совместно с рядом специалистов была создана в 2024 году компания Ubitium. Ускорить разработку позволило привлечение $3,7 млн в рамках посевного раунда в конце прошлого года, который совместно возглавили Runa Capital, Inflection и KBC Focus Fund. Инвестиции позволили Ubitium проверить архитектуру и подготовить наборы для разработки (IDK) для первых клиентов. «Индустрия процессоров объёмом $500 млрд построена на жёстких границах между вычислительными задачами», — сказал Хён Шин Чо (Hyun Shin Cho), генеральный директор Ubitium и соучредитель. — Мы стираем эти границы. Наш универсальный процессор делает всё — CPU, GPU, DSP, FPGA — на одном чипе, в одной архитектуре. Это не просто постепенное улучшение. Это смена парадигмы. Это архитектура процессора, которую требует эпоха ИИ». Как отметил EE Times, завершение tape-out продукта — это не просто большая победа для Ubitium. Это также поворотный момент для экосистемы RISC-V. Открытая архитектура RISC-V используется большей частью для создания обычных ядер, которые полагаются на внешние ускорители для сложных рабочих нагрузок. Ubitium расширяет границы использования архитектуры, сохраняя полную совместимость с RISC-V. Процессор поддерживает стандартные наборы инструментов RISC-V для разработки ПО и может работать под управлением Linux и RTOS. Кроме того, унифицированный программный стек устраняет необходимость в компиляторах для конкретного поставщика или проприетарных языках, что позволяет быстро внедрять инновации и сократить время разработки. Компания сотрудничает с Samsung Foundry и ADTechnology для завершения проектирования и с Siemens Digital Industries Software — для проверки микросхемы (pre-silicon validation). Вторая стадия tape-out запланирована на конец этого года, а серийное производство начнётся в 2027 году, сообщила компания.

17.02.2026 [13:57], Владимир Мироненко

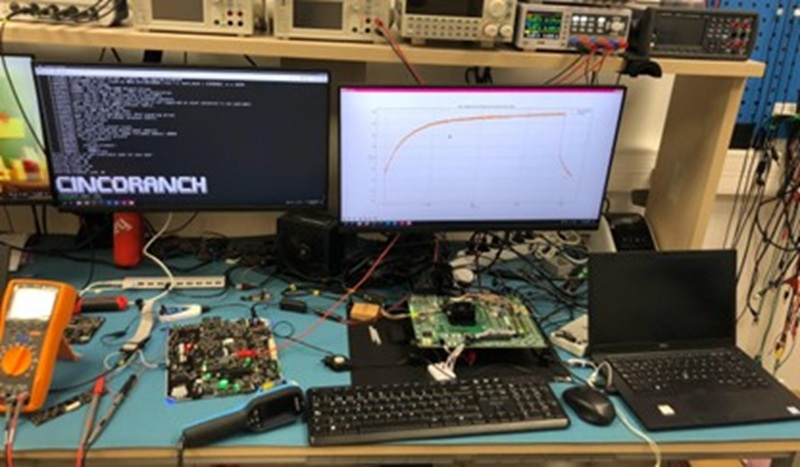

Первый европейский суверенный RISC-V-процессор Cinco Ranch изготовлен по техпроцессу Intel 3Лаборатория суперкомпьютерных вычислений (BZL) Национального центра суперкомпьютерных вычислений Барселоны (BSC-CNS) сообщила об успешном запуске тестового чипа Cinco Ranch TC1 на архитектуре RISC-V, изготовленного по передовому техпроцессу Intel 3. В заявлении отмечено, что результаты подтверждают надёжность конструкции и жизнеспособность вычислительной архитектуры на базе открытой платформы RISC-V. «Это достижение является ключевым этапом в процессе разработки чипа и качественным скачком на пути к суверенным суперкомпьютерным технологиям в Европе», — подчеркнула BZL, отметив, что готовый чип предлагает открытую, гибкую альтернативу, свободную от зависимости от проприетарных архитектур крупных транснациональных корпораций. Проект связан с Европейской инициативой по процессорам (EPI), целью которой является разработка отечественных процессоров для будущих европейских суперкомпьютеров и промышленных систем. «Успешная стабильная загрузка Linux и проверка достижения чипом ожидаемых частот подтверждают зрелость конструкции и качество работы, проделанной командами BZL», — говорит исследователь BSC и координатор аппаратной части лаборатории Zettascale в Барселоне. Cinco Ranch TC1 — это первый чип, произведенный в академической среде с использованием 3-нм техпроцесса Intel 3. На этапе проектирования, из-за невозможности прямого доступа к этой технологии, BZL провела внутренние оценки на сопоставимом техпроцессе TSMC N7, что позволило оценить конструкцию перед окончательной реализацией. Сообщается, что структура Cinco Ranch TC1 основана на трёх взаимодополняющих процессорных блоках, предназначенных для совместной работы и охвата различных вычислительных профилей. В чипе используются три блока RISC-V на одном кристалле, каждый из которых ориентировано на специализированные рабочие нагрузки. Три ядра используют микроархитектуры Sargantana, Lagarto Ka и Lagarto Ox, с основным упором на эффективность, векторные нагрузки и скалярную обработку соответственно. Подсистема CPU занимает всего 3,2 мм² на крошечном кристалле площадью 15,2 мм², который также включает высокоскоростные интерфейсы, такие как PCIe 5.0 и DDR5. Для сравнения, площадь CCD восьмиядерного процессора AMD Zen 5 составляет около 71 мм², и для этого чиплета также требуется отдельный кристалл I/O, отметил ресурс HotHardware.com.  Cinco Ranch TC1 был протестирован на оценочной плате Hawk Canyon V2, разработанной Intel для первоначальной проверки чипа после его производства. Следующим этапом станет функциональное тестирование и тестирование производительности, оптимизация ПО и полная проверка системы. В мае 2025 года на Cinco Ranch TC1 (Test Chip 1) была успешно загружена ОС Linux, а в июле 2025 года, после получения партии из 500 чипов, начались работы по характеризации и проверке. Вся партия продемонстрировала высокую функциональную производительность, при этом большинство устройств успешно запустили все три интегрированных процессора чипа. Также результаты тестов подтверждают, что Cinco Ranch TC1 работает на частоте до 1,25 ГГц, что превышает консервативные оценки, сделанные на этапе проектирования. Для BZL и её партнёров это достижение является важной вехой и доказательством того, что разработанные в Европе процессоры с открытой ISA могут быть реализованы на передовых технологиях производства и воплощены в реальных кремниевых решениях. Для Европы — это значимый шаг к технологической автономии в HPC. А для Intel это демонстрация того, что её бизнес может оказывать всестороннюю поддержку передовым внешним клиентам в сложных гетерогенных проектах.

10.02.2026 [12:09], Сергей Карасёв

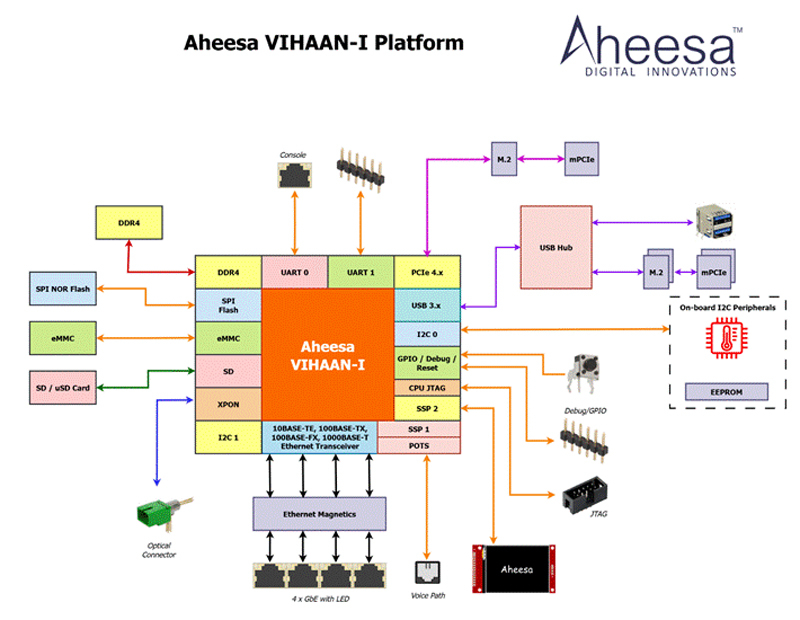

Стартап Aheesa создал первый в Индии чип RISC-V для PON-сетейИндийский безфабричный стартап Aheesa Digital Innovations, по сообщению EE Times, завершил разработку первой в стране «системы на чипе» (SoC) с архитектурой RISC-V, ориентированной на волоконно-оптические сети широкополосного доступа в интернет. Изделие получило обозначение VIHAAN-I. Новинка предназначена для инфраструктур GPON (Gigabit Passive Optical Network) и EPON (Ethernet Passive Optical Network). Решение объединяет на одном кристалле вычислительные ресурсы, средства управления и широкополосного доступа. VIHAAN-I является частью платформы Aheesa Seshnag. В состав новинки входит RISC-V-ядро C-DAC Vega. Реализована поддержка памяти DDR4 и SPI NOR, флеш-карт SD и microSD, а также интерфейса xPON. Заявлена совместимость с Ethernet-стандартами 10BASE-TE, 100BASE-TX, 100BASE-FX и 1000BASE-T. Изделие объединяет многопортовый гигабитный Ethernet и прямое оптоволоконное соединение. Среди прочего упомянуты интерфейсы USB и PCIe (четыре линии) с возможностью использование модулей M.2 и mini-PCIe. Кроме того, предусмотрена интегрированная поддержка голосовой связи. SoC будет производиться на предприятии UMC с применением 28-нм технологии.

Источник изображения: Aheesa Digital Innovations / EE Times Выбор архитектуры RISC-V, как заявляет Aheesa Digital Innovations, обусловлен прежде всего соображениями безопасности. Поддерживаются стандартные сетевые функции, такие как коммутация Ethernet, маршрутизация, службы межсетевого экрана, VPN, протокол динамической конфигурации хоста и пр. Примерно на 60% решение состоит из стандартных лицензированных компонентов, таких как контроллеры памяти и интерфейсные блоки. Заявлена совместимость с последними версиями ядра Linux. Aheesa Digital Innovations основана в 2021 году Шридхараном Мани (Sridharan Mani), который занимает пост генерального директора. Компания получила поддержку в рамках индийской программы стимулирования разработок. Стартап сотрудничает с рядом государственных учреждений, включая Министерство электроники и информационных технологий (MEITy) и Центр развития передовых вычислительных технологий (C-DAC). Aheesa Digital Innovations намерена предлагать свои решения OEM- и ODM-производителям, системным интеграторам и дистрибьюторам, которые поставляют устройства телекоммуникационным операторам. В дальнейшем стартап планирует активно развивать семейство собственных SoC. В частности, готовятся решения с поддержкой 10GbE и Wi-Fi 7. |

|