Материалы по тегу: cxl

|

15.04.2026 [11:48], Сергей Карасёв

Анонсированы китайские SSD для дата-центров PetaIO: PCIe 6.0, CXL 3.0 и 28 Гбайт/сКитайская компания PetaIO, по сообщениям сетевых источников, разработала высокопроизводительные SSD нового поколения с интерфейсом PCIe 6.0, предназначенные для использования в дата-центрах, ориентированных на ресурсоёмкие ИИ-нагрузки. Полностью характеристики устройств не раскрываются. Известно, что в их основу положен передовой контроллер Titanium Himalaya, при изготовлении которого применяется 6-нм техпроцесс. Говорится о поддержке CXL 3.0, а также о возможности формирования пулов памяти объёмом до 256 Тбайт. Заявленная скорость передачи данных при последовательном чтении превышает 28 Гбайт/с. Накопители специально оптимизированы для выполнения задач в области ИИ. Показатель IOPS при произвольном чтении информации блоками по 512 байт составляет до 50 млн. При этом обеспечивается задержка на уровне 2,7 мкс.

Источник изображения: PetaIO Предполагается, что новые SSD помогут решить проблему «стены памяти» в масштабных инфраструктурах ИИ. О ёмкости накопителей и их форм-факторе пока ничего не сообщается. При этом подчёркивается, что устройства совместимы с современными высокопроизводительными сетевыми экосистемами. Нужно отметить, что в настоящее время на сайте PetaIO упомянуты SSD нескольких семейств. Это, в частности, решения PETA8118 формата U.2 (PCIe 4.0 x4) вместимостью до 8 Тбайт, PETA8118 типоразмера M.2 2280 (PCIe 4.0 x4) ёмкостью до 4 Тбайт, PETA8118 стандарта E1.S (PCIe 4.0 x4) на 2–8 Тбайт и изделия PETA8118 в виде карт расширения PCIe 4.0 x4 ёмкостью до 4 Тбайт.

14.04.2026 [12:44], Владимир Мироненко

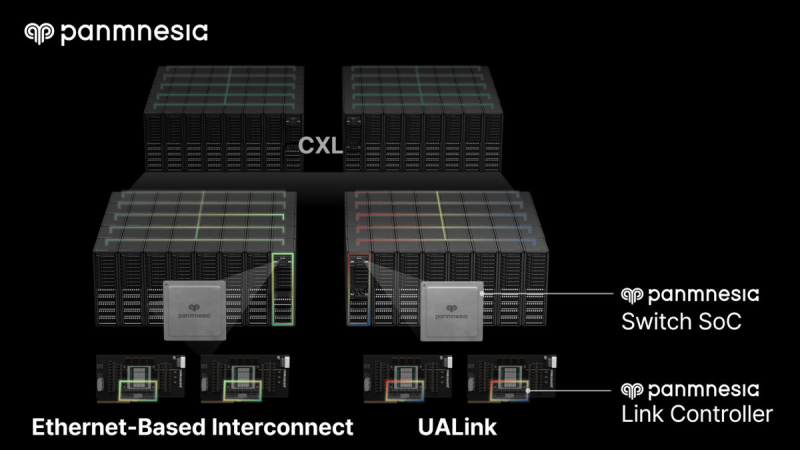

Panmnesia привлёк $10 млн на разработку интерконнекта следующего поколения для ИИ ЦОДЮжнокорейский стартап Panmnesia, специализирующийся на разработке интерконнекта для ИИ-инфраструктур, сообщил о получении финансирования в размере около $10 млн на разработку интерконнекта следующего поколения для ИИ ЦОД. Проект включает разработку контроллеров и коммутаторов на основе открытых стандартов, таких как UALink и протоколов интерконнекта на основе Ethernet. Уже имея обширный портфель продуктов CXL, Panmnesia теперь расширяет свою деятельность в области интерконнекта, ориентированного на ускорители. Компания отметила, что по мере распространения крупномасштабных ИИ-моделей в различных отраслях, ИИ ЦОД всё чаще полагаются на ИИ-ускорители разных вендоров. В этом контексте технологии интерконнекта, обеспечивающие высокоскоростную передачу данных между ускорителями, стали критически важным фактором, определяющим общую производительность ИИ-системы. Также Panmnesia планирует оптимизировать топологию разработанных устройств для ускорения обмена данными между ними и провести валидацию на уровне стойки. Ожидается, что чип-коммутатор с поддержкой интерконнекта, ориентированного на ускорители, такого как UALink, станет доступен во II половине 2027 года. Портфолио продуктов CXL компании включает комплексные решения, в том числе контроллеры и IP-блоки PCIe/CXL, аппаратные SoC, такие, как коммутаторы PCIe/CXL, и специализированные кремниевые решения. В прошлом году Panmnesia представила архитектуру CXL-over-XLink, которая интегрирует специализированные каналы связи для ускорителей (известные как XLink), включая UALink, с CXL для обеспечения расширенной связи в крупных ИИ ЦОД.

24.03.2026 [08:50], Сергей Карасёв

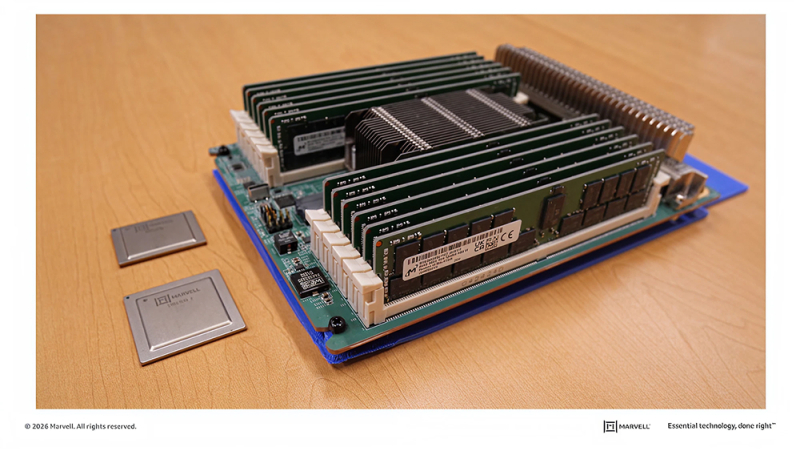

Marvell представила коммутатор Structera S 60260 с поддержкой 260 линий PCIe 6.0Компания Marvell Technology анонсировала коммутатор Structera S 60260 — это, как утверждается, первое в отрасли решение с поддержкой 260 линий PCIe 6.0. Новинка предназначена для использования в дата-центрах, ориентированных на ресурсоёмкие задачи ИИ. Одновременно компания представила и коммутатор Structera S 30260 с поддержкой 260 линий CXL 3.0. Marvell отмечает, что современные ИИ ЦОД оперируют серверами с большим количеством GPU и ускорителей других типов. На этом фоне критически важным элементом становятся коммутационные системы на основе PCIe, способные обеспечить высокую плотность вычислений и максимально эффективное использование доступных ресурсов. В традиционных инфраструктурах применяется множество коммутаторов, что приводит к увеличению энергопотребления, задержек и общей стоимости владения. Изделие Structera S 60260 позволяет решить эти проблемы. Новинка базируется на разработках компании XConn Technologies, которую Marvell приобрела в начале текущего года за $540 млн. XConn специализируется на разработке передовых коммутаторов PCIe и CXL: в частности, с 2022 года она поставляет коммутаторы с 256 линиями PCIe 5.0. В случае решения Structera S 60260 количество линий PCIe 6.0 практически в два раза больше, чем у сопоставимых по классу продуктов конкурентов. «Коммутатор Structera S PCIe оптимизирован для обеспечения лучших в отрасли показателей производительности, гибкости, задержки и энергоэффективности при работе с ресурсоёмкими приложениями, включая ИИ, задачи машинного обучения следующего поколения и НРС», — говорит Джерри Фан (Gerry Fan), старший вице-президент Marvell. Благодаря объединению коммутаторов Structera S PCIe с ретаймерами Marvell Alaska P PCIe гиперскейлеры и операторы ИИ ЦОД получают комплексную платформу интерконнекта на основе PCIe. При использовании активных электрических кабелей (AEC) протяжённость соединений PCIe 6.0 может достигать 7 м, а при использовании активных оптических кабелей — превышать 7 м. Изделия Structera S PCIe совместимы по выводам с новыми коммутаторами Marvell Structera S CXL 3.0. Поставки тестовых образцов Structera S PCIe 6.0 уже начались. Отгрузки коммерческих коммутаторов Structera S PCIe 60260 клиентам будут организованы в III квартале 2026 года.

21.03.2026 [12:53], Сергей Карасёв

11 Тбайт памяти для ИИ: Penguin Solutions представила кеширующий сервер MemoryAI KV на основе CXL-модулейКомпания Penguin Solutions анонсировала систему MemoryAI KV Cache Server призванную решить проблему «стены памяти» в современных инфраструктурах, ориентированных на ресурсоёмкие задачи ИИ-инференса. Устройство предоставляет до 11 Тбайт CXL-памяти, что позволяет максимально эффективно использовать доступные вычислительные мощности. Сервер (модель Altus XE4318GT-KVC) выполнен в форм-факторе 4U. Он несёт на борту два процессора AMD EPYC 9005 Turin в исполнении Socket SP5 (LGA 6096) с показателем TDP до 500 Вт. В оснащение входят контроллер ASpeed AST2600 и сетевой адаптер Intel I350-AM2. Реализованы два коннектора для SSD формата M.2 2280/22110 с интерфейсом PCIe 3.0, восемь слотов для карт PCIe 5.0 x16 FHFL и два слота для карт PCIe 5.0 x16 LP, два сетевых порта 400GbE (RJ45), два порта USB 3.0 (5 Гбит/с), а также аналоговый интерфейс D-Sub. Устройство поддерживает до 3 Тбайт памяти DDR5-6400. Кроме того, установлены восемь карт CXL, каждая из которых содержит 1 Тбайт памяти. Благодаря этому расширяются возможности применяемых в инфраструктуре ИИ-ускорителей с ограниченным объёмом HBM. Говорится о совместимости с программной средой NVIDIA Dynamo, предназначенной в том числе для ускорения инференса. В целом, как отмечает Penguin Solutions, новый сервер позволяет компаниям максимально эффективно использовать GPU-ускорители благодаря добавлению больших пулов памяти.

Источник изображения: Penguin Solutions Устройство оборудовано четырьмя блоками питания мощностью 3000 Вт с сертификатом 80 Plus Titanium. Диапазон рабочих температур — от +10 до +35 °C. Заявлена совместимость с Red Hat Enterprise Linux (RHEL) и Rocky Linux. На систему предоставляется трёхлетняя гарантия.

05.03.2026 [14:21], Владимир Мироненко

Дефицит памяти поможет Broadcom подзаработать, но не так, как вы подумалиВ связи с ростом цен на оперативную память на фоне её дефицита, который, по прогнозам экспертов, сохранится и в 2027 году, VMware (подразделение Broadcom) предложила частное облако VMware Cloud Foundation (VCF) 9.0 в качестве решения, необходимого для работы в новых условиях. VMware заявила, что «традиционный подход, заключающийся в увеличении количества оборудования для решения проблем производительности и масштабируемости, больше не является жизнеспособным». «Broadcom разработала VCF 9.0 специально для решения этой экономической задачи, предложив три различных подхода: снижение совокупной стоимости владения за счёт многоуровневого хранения памяти, отсрочка капитальных затрат за счёт передовых технологий повышения эффективности и обеспечение немедленного внедрения в существующий парк оборудования», — сообщила она. Как отметил The Register, VMware всегда продвигала многоуровневую организацию памяти VCF 9 как возможность снизить затраты на инфраструктуру за счёт уменьшения установленного объёма DRAM путём прозрачного переноса части данных на NVMe. Вместе с тем, не следует забывать, что стоимость SSD также выросла. VMware также признаёт, что её архитектура памяти подходит не для всех рабочих нагрузок и не предназначена для виртуальных машин, чувствительных к задержкам, или очень больших инстансов. Но VMware всё равно утверждает, что «наиболее прямое решение проблемы стремительного роста цен на DRAM — это просто использовать её меньше», а VCF 9.0 позволяет «заменить дорогостоящую DRAM значительно более дешёвым хранилищем NVMe». Многоуровневое распределение памяти VMware в настоящее время превосходит альтернативу в виде CXL, пишет The Register. Кроме того, новые поколения серверных процессоров AMD и Intel создали возможность очередного этапа консолидации нагрузок. Dell утверждает, что её клиенты заменяют семь серверов одной новой машиной; Intel говорит о консолидации 5:1. Новые серверы позволяют запускать огромное количество ВМ, что концентрирует риски и требует огромного количества дорогостоящей памяти. Но VMware и не требует, чтобы в каждом хосте в кластере использовалось многоуровневое распределение памяти. Так что VCF 9 в текущей ситуации действительно может оказаться эффективным средством снижения затрат. В то же время The Register отметил, что многие пользователей vSphere считают VCF 9 очень дорогим продуктом, несмотря на уверения Broadcom в обратном. При этом Broadcom, похоже, в принципе не готова идти на ценовые уступки — или бери, или уходи.

07.02.2026 [13:53], Сергей Карасёв

Montage Technology представила активные кабели PCIe 6.x/CXL 3.xКомпания Montage Technology объявила о разработке активных электрических кабелей (AEC) PCIe 6.x/CXL 3.x, предназначенных для организации высокоскоростного интерконнекта с низкой задержкой в дата-центрах, ориентированных на ресурсоёмкие задачи ИИ и НРС. Отмечается, что на фоне стремительного внедрения ИИ и продолжающегося развития облачных вычислений быстро растёт нагрузка на ЦОД. При этом PCIe остаётся основным стандартом для обмена данными между CPU, GPU, сетевыми картами и высокопроизводительными хранилищами. Интерконнект на базе PCIe применяется как в рамках серверных стоек, так и в составе суперузлов, в связи с чем требуется увеличивать протяжённость соединений. В таких условиях, подчёркивает Montage Technology, медные линии на базе AEC имеют решающее значение для обеспечения целостности сигнала на больших расстояниях.

Источник изображения: Montage Technology Кабели Montage Technology PCIe 6.x/CXL 3.x с ретаймером используют фирменные блоки SerDes и передовую архитектуру DSP. Применён высокоплотный форм-фактор OSFP-XD. Говорится о развитых функциях мониторинга и диагностики каналов связи, что упрощает обслуживание систем и повышает их эффективность. Возможно использование в инфраструктурах с различными топологиями. В разработке решения, как утверждается, принимали участие ведущие китайские производители кабелей. Проведены успешные тесты на совместимость с CPU, xPU, коммутаторами PCIe, сетевыми адаптерами и другими устройствами. В дальнейшем компания Montage Technology намерена развивать направление высокоскоростного интерконнекта, включая выпуск ретаймеров PCIe 7.0.

06.02.2026 [10:53], Владимир Мироненко

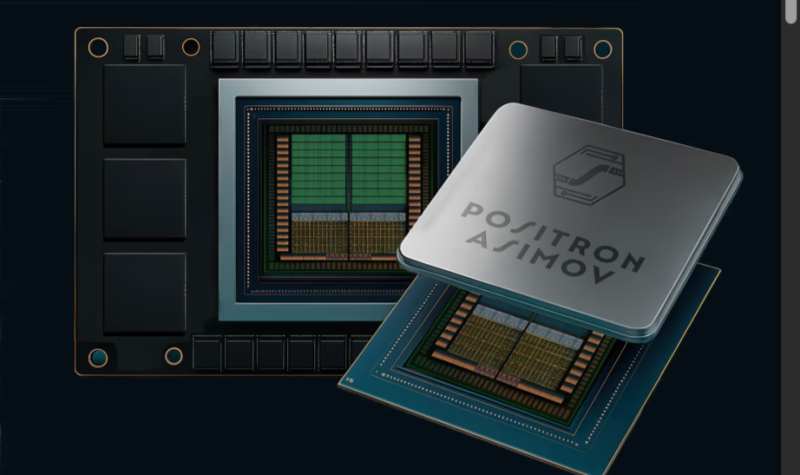

Без дефицитной HBM: Positron AI готовит ИИ-ускоритель Asimov с терабайтами LPDDR5xКомпания Positron AI сообщила о привлечении $230 млн инвестиций в рамках переподписанного раунда финансирования серии B, в результате которого оценка её рыночной стоимости превысила $1 млрд. Раунд возглавили ARENA Private Wealth, Jump Trading и Unless при участии новых инвесторов Qatar Investment Authority (QIA), Arm и Helena, а также существующих инвесторов Valor Equity Partners, Atreides Management, DFJ Growth, Resilience Reserve, Flume Ventures и 1517. Объявление было сделано на мероприятии Web Summit Qatar, что подчеркивает растущий международный авторитет компании, отметил ресурс eWeek. На то, чтобы перейти в категорию единорогов, Positron AI потребовалось 34 месяца. Positron AI отметила решение Jump Trading стать одним из лидеров раунда после того, как эта компания стала её клиентом. «Для рабочих нагрузок, которые нас интересуют, узкими местами всё чаще становятся память и энергопотребление, а не теоретические вычисления», — сказал технический директор Jump Trading. — В ходе наших тестов Positron Atlas показал примерно в три раза меньшую сквозную задержку, чем сопоставимая система на базе NVIDIA H100, при оценке рабочих нагрузок инференса, в готовом к производству корпусе с воздушным охлаждением и цепочкой поставок, которую мы можем спланировать». Полученные инвестиции позволят ускорить выход платформы следующего поколения Asimov, разработанной на заказ. Компания планирует завершить тестирование Asimov к концу III квартала, а пробные версии появятся в конце I квартала 2027 года. В Asimov будет использоваться память LPDDR (без HBM), но возможность приблизиться к теоретической пиковой пропускной способности памяти означает, что компании и не нужно полагаться на HBM для быстрой генерации токенов, сообщил ресурсу EE Times технический директор Positron. Вычислительные элементы Asimov — это эволюция блоков Atlas с добавлением ядер Arm и улучшенным интерконнектом. Расширить память LPDDR5x в Asimov можно с помощью CXL — с 864 Гбайт до 2,3 Тбайт на чип. Чип позволяет создать два независимых домена памяти, чтобы лучше утилизировать её. Хосит-интерфейс чипа — PCI 6.0 x32. Хотя LPDDR5x дешевле и ёмче HBM, она значительно уступает ей по пропускной способности. Если ускорители Rubin от NVIDIA оснащены 288 Гбайт памяти HBM4 с пиковой пропускной способностью 22 Тбайт/с, то для Asimov, по-видимому, потолок составляет около 3 Тбайт/с, пишет The Register (в спецификациях указано 2,76 Тбайт/с). По словам Positron, разница в том, что её чипы действительно могут использовать 90 % этой пропускной способности, в то время как GPU на базе HBM в реальных условиях едва достигают 30 % пиковой пропускной способности, хотя память Rubin даже в этом случае примерно в 2,4 раза быстрее, чем у Asimov. Компания сообщила, что 400-Вт чип оснащён систолической матрицей 512×512, работающей на частоте 2 ГГц и поддерживающей типы данных TF32, FP16/BF16, FP8, NVFP4 и INT4. Эта матрица управляется рядом ядер Armv9 и может быть переконфигурирована, например, в 128×512 (GEMV) или 512×128 (GEMM), в зависимости от того, какой вариант более выгоден для решения конкретной задачи. Четыре чипа Asimov образуют 4U-платформу Titan с воздушным охлаждением и пропускной способностью между чипами 16 Тбит/с. Компания отметила, что Asimov рассчитан на поддержку 2 Тбайт памяти на ускоритель и 8 Тбайт памяти на систему Titan с аналогичной пропускной способностью памяти, как у ускорителя NVIDIA Rubin. В масштабе стойки это означает объём памяти более 100 Тбайт. До 4096 систем Titan (16384 ускорителя) могут быть объединены в единый масштабируемый домен с более чем 32 Пбайт памяти. Это достигается с помощью чистого межчипового интерконнекта, а не коммутируемых масштабируемых сетей, как в стоечных архитектурах NVIDIA или AMD. Positron подчеркнула, что её архитектура, ориентированная на память, открывает доступ к высокоэффективным задачам инференса, включая большие языковые модели с длинным контекстом, агентные рабочие процессы и модели медиа и видео следующего поколения.

19.01.2026 [09:03], Сергей Карасёв

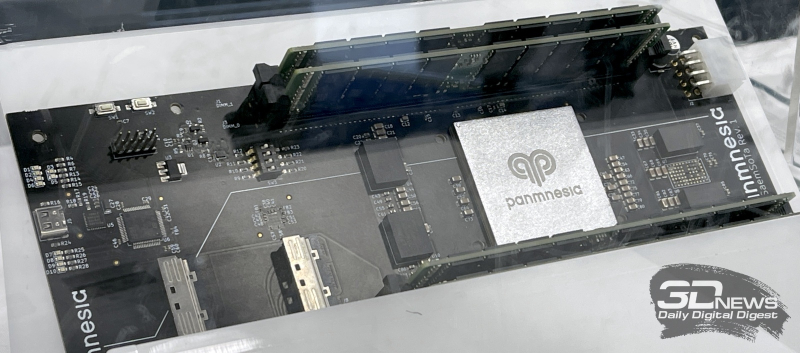

Panmnesia представила чип-коммутатор Panswitch с поддержкой PCIe 6.4 и CXL 3.2Южнокорейский стартап Panmnesia анонсировал чип-коммутатор Panswitch (модель H1SW06245ACFAA), предназначенный для использования в составе масштабных HPC-платформ и дата-центров, ориентированных на задачи ИИ. Кроме того, представлена сопутствующая плата для разработчиков PanRDK. Как утверждается, Panswitch — это первое в мире изделие в своём классе, полностью поддерживающее ключевые функции, описанные в спецификации CXL 3.2, включая Port-based Routing (PBR). Это позволяет соединять тысячи устройств в единой вычислительной среде посредством CXL. Отмечается, что Panswitch даёт возможность формировать сети с различными топологиями — от простых древовидных структур до ячеистых (mesh) конфигураций, систем Dragonfly и пр. Это позволяет оптимизировать пути передачи данных в зависимости от конкретных рабочих нагрузок. В состав Panswitch входит проприетарный CXL-контроллер Panmnesia со сверхнизкой задержкой. Говорится о поддержке интерфейса PCIe 6.4. В целом, как подчёркивает разработчик, Panswitch обеспечивает повышенную производительность и эффективность при крупномасштабных развёртываниях ИИ. В свою очередь, плата PanRDK предназначена для тестирования чипа-коммутатора в реальных условиях. Это решение оснащено FPGA, благодаря чему может быть настроено для работы в качестве различных устройств, в том числе CXL CPU, CXL GPU и пула памяти CXL. Предусмотрены слоты MCIO и CEM, что позволяет сформировать полноценную систему с поддержкой CXL. Плата совместима не только с изделиями Panmnesia, но и с широким спектром решений сторонних производителей, соответствующих стандарту CXL. Поставки чипов Panswitch и пилотных систем уже начались.

07.01.2026 [16:47], Владимир Мироненко

В попытке догнать Broadcom: Marvell купила за $540 млн XConn, разработчика коммутаторов PCIe и CXLПосле объявления о заключении окончательного соглашения о приобретении XConn Technologies, поставщика передовых коммутаторов PCIe и CXL, акции Marvell Technology пошли в гору — их цена выросла на 4 %, сообщил ресурс SiliconANGLE. Сумма сделки составляет около $540 млн. Примерно 60 % будет выплачено наличными и 40 % — акциями Marvell, при этом стоимость последних будет определяться на основе средневзвешенной цены за 20 дней. По словам Marvell, приобретение позволит ей расширить портфель коммутационных решений продуктами XConn PCIe и CXL, а также укрепить команду по разработке решений UALink высококвалифицированными инженерами XConn с глубокими знаниями в области высокопроизводительной коммутации. Коммутация необходима для соединения большого количества ИИ-микросхем в гигантские кластеры для запуска мощных больших языковых моделей. Компания XConn, основанная в 2020 году и финансируемая частными инвесторами, выпустила в марте 2024 года первый в отрасли коммутатор Apollo с поддержкой CXL 2.0 и PCIe 5.0, обеспечивающий 256 линий. Его выпускает TSMC с использованием техпроцессов N16 и N5, сообщил ресурс Data Center Dynamics. Затем она выпустила в марте 2025 года гибридный коммутатор Apollo 2, объединяющий CXL 3.1 и PCIe 6.2 на одном чипе в конфигурациях от 64 до 260 линий. Когда-то Marvell считалась одной из самых перспективных компаний после NVIDIA, и многие эксперты полагали, что она станет одним из главных бенефициаров бума ИИ. Однако она по-прежнему уступает по темпам развития NVIDIA, а заодно и своему основному конкуренту Broadcom, который разрабатывает чипы как минимум для четырёх гиперскейлеров. Покупка XConn призвана исправить ситуацию, дополняя недавнее приобретение Celestial AI. По словам Marvell, приобретение XConn добавит проверенные коммутационные продукты PCIe и CXL, IP-решения и инженерные кадры для расширения команды по масштабируемым коммутаторам UALink. «В сочетании с предстоящим приобретением Celestial AI мы будем иметь все возможности для предоставления клиентам производительности, гибкости и архитектурного выбора, необходимых им по мере роста размеров и сложности ИИ-систем», — отметил он. Сделка позволит Marvell расширить свой общий целевой рынок (Total Addressable Market, TAM) за счёт освоения растущих возможностей коммутаторов PCIe и CXL. PCIe-коммутаторы становятся критически важным строительным блоком для ИИ-инфраструктуры. В то же время CXL необходим для дезагрегации памяти в современных ЦОД. Сочетание контроллеров памяти Marvell CXL с коммутаторами XConn CXL позволит создать самый обширный в отрасли портфель коммутаторов для поддержки ресурсоёмких ИИ-задач. На данный момент у XConn насчитывается более чем 20 клиентов. Marvell ожидает, что продукты XConn CXL и PCIe начнут приносить доход во II половине 2027 финансового года. Также ожидается, что в результате сделки Marvell получит около $100 млн дополнительного дохода в 2028 финансовом году.

28.11.2025 [12:50], Сергей Карасёв

Сервер Giga Computing R284-A91 получил 16 отсеков для CXL-модулей формата E3.S 2TКомпания Giga Computing (дочерняя структура Gigabyte) анонсировала сервер R284-A91-AAL3 для задач НРС. Новинка, выполненная в форм-факторе 2U, использует аппаратную платформу Intel с двумя процессорами Xeon 6900 семейства Granite Rapids-AP с показателем TDP до 500 Вт. Система располагает 24 слотами для модулей оперативной памяти DDR5: могут использоваться изделия RDIMM-6400 и MRDIMM-8800. В оснащение входят контроллер ASPEED AST2600, два сетевых порта 1GbE на основе Intel I350-AM2, выделенный сетевой порт управления 1GbE, два разъёма USB 3.0 Type-A и интерфейс Mini-DP. Предусмотрено по одному слоту PCIe 5.0 x16 для карты FHHL и OCP NIC 3.0 (PCIe 5.0 x16). Особенностью сервера является наличие 16 фронтальных отсеков для CXL-модулей формата E3.S 2T (PCIe 5.0 x8). Такие изделия, в частности, ранее представила компания Innodisk. Модули CXL дают возможность масштабировать ресурсы памяти системы для выполнения сложных задач. Кроме того, там же предусмотрены четыре посадочных места для E3.S NVMe SSD (PCIe 5.0). Есть два тыльных отсека для SFF-устройств SATA/SAS-4 с возможностью горячей замены и два внутренних коннектора M.2 для SSD формата 2280/22110 с интерфейсом PCIe 5.0 x4. Габариты сервера составляют 438 × 87,5 × 815 мм, масса — 21,2 кг. Питание обеспечивают два блока с резервированием мощностью 2700 Вт с сертификатом 80 PLUS Titanium. Применено воздушное охлаждение с четырьмя системными вентиляторами диаметром 80 мм. Диапазон рабочих температур — от +10 до +35 °C. Гарантирована совместимость с Windows Server 2025. Опционально может быть установлен модуль TPM 2.0. |

|