Материалы по тегу: 800gbe

|

13.04.2026 [13:05], Сергей Карасёв

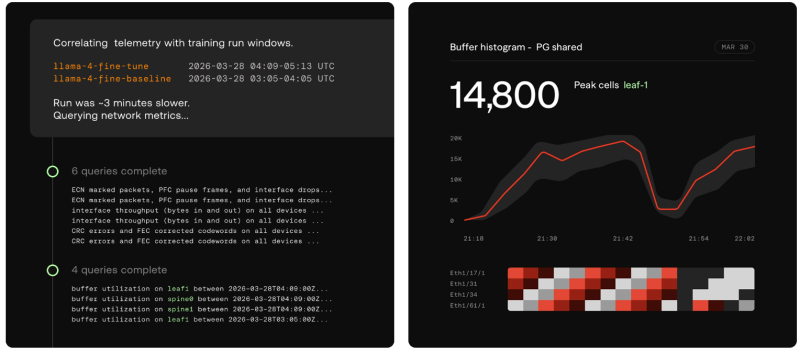

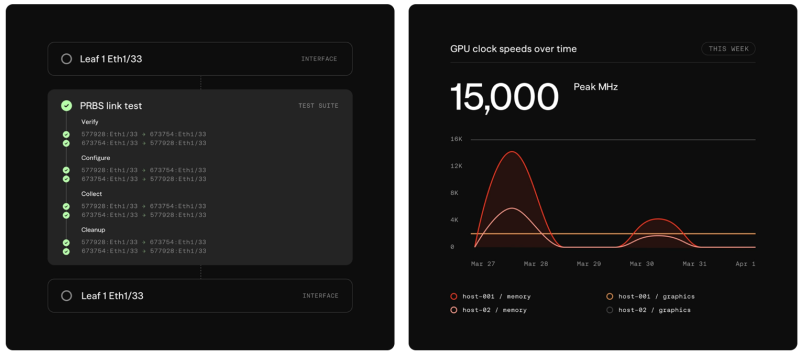

Aria Networks представила «думающую» сетевую платформу Deep Networking для высокоэффективных ИИ-инфраструктурКомпания Aria Networks анонсировала сетевую платформу Deep Networking, призванную повысить эффективность работы ИИ-систем. Предложенное решение объединяет специализированное коммутационное оборудование, сетевую ОС SONiC, высокоточную телеметрию на коммутаторах, трансиверах и сетевых картах, а также ИИ-алгоритмы на разных уровнях вычислительной инфраструктуры. Стартап Aria Networks основан в январе 2025 года Мансуром Карамом (Mansour Karam), учредителем фирмы Apstra, которую в 2019-м приобрёл американский производитель сетевого оборудования Juniper Networks. Aria Networks занимается разработкой высокопроизводительных решений, сочетающих возможности стандартного Ethernet со специализированным ПО для управления большим количеством модульных коммутаторов как единой системой. На сегодняшний день стартап привлёк в общей сложности $125 млн инвестиций от Sutter Hill Ventures, Atreides Management, Valor Equity Partners и Eclipse Ventures. Идея Deep Networking заключается в том, чтобы рассматривать сеть в качестве активного участника кластера ИИ, а не в роли пассивного слоя. Это достигается путём сбора детальной телеметрии с коммутационных ASIC, внедрения интеллектуальных агентов на каждом уровне и постоянного распространения обновлений ПО через облако. В качестве ключевых показателей быстродействия Aria Networks рассматривает MFU (уровень утилизации оборудования при обучении) и Token Efficiency (эффективность токенов). Первый параметр отражает, какой процент от теоретической максимальной производительности ИИ-ускорителя (пиковых FLOPS) реально тратится на полезные вычисления для обучения или инференса. В свою очередь, эффективность токенов показывает, уровень MFU или время на обработку одного токена. Основное техническое преимущество Deep Networking заключается в получении детализированной телеметрии. Традиционные инструменты мониторинга сети собирают данные постфактум — с относительно невысокой точностью. Решение Aria Networks обрабатывает телеметрию в реальном времени непосредственно с ASIC. Благодаря этому обеспечивается адаптивная настройка параметров DLB (динамическая балансировка нагрузки) и DCQCN (механизм управления перегрузками). Сама платформа Deep Networking имеет многоуровневую архитектуру. На самых нижних уровнях ИИ-агенты в течение микросекунд реагируют на такие события, как сбои в работе трансиверов, перенаправляя трафик между коммутаторами. На более высоких уровнях принимаются стратегические решения о перераспределении потоков в кластере. Кроме того, внешние системы, например, планировщики заданий и маршрутизаторы, могут напрямую запрашивать сведения о состояние сети и интегрировать их в процесс принятия собственных решений. С аппаратной точки зрения инфраструктура Deep Networking базируется на коммутаторах Aria Switch 800G, Aria Switch 1.6T High Radix и Aria Switch 1.6T, оснащённых чипами Broadcom. Платформа непрерывно настраивает каждый аспект сетевой инфраструктуры для конкретного обслуживаемого ИИ-кластера без ручного вмешательства, что сводит к минимуму задержки и устраняет ошибки, обусловленные человеческим фактором. Администраторам достаточно указать свои потребности, после чего платформа соответствующим образом оптимизирует сеть. При этом система постоянно оценивает состояние сети и в режиме реального времени принимает меры для обеспечения наилучшей производительности и бесперебойной работы. Aria Networks утверждает, что один неисправный сетевой адаптер в кластере из 10 тыс. XPU может снизить показатель MFU на 1,7 %. А сбой трансивера способен спровоцировать некорректную переадресацию трафика, что приведёт к существенным финансовым потерям. Архитектура Deep Networking позволяет эффективно решать подобные проблемы, одновременно улучшая производительность. Так, повышение MFU на 3 % в кластере из 10 тыс. XPU, по оценкам стартапа, приводит к увеличению годовой выручки на $49,8 млн.

23.03.2026 [09:31], Сергей Карасёв

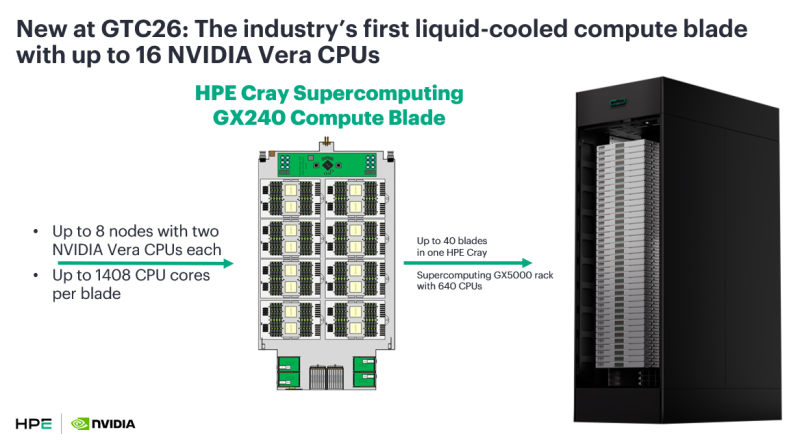

HPE представила узлы на базе NVIDIA Vera для платформы Cray Supercomputing GX5000Компания HPE анонсировала новые решения семейства NVIDIA AI Computing by HPE, ориентированные на крупномасштабные ИИ-платформы и суперкомпьютерные системы. О намерении использовать такие инфраструктурные продукты в числе прочих сообщили Аргоннская национальная лаборатория (ANL) Министерства энергетики США (DOE), Hudson River Trading (HRT), Корейский институт научно-технической информации (KISTI) и Центр высокопроизводительных вычислений HLRS при Штутгартском университете в Германии. В частности, представлены новые узлы для суперкомпьютерной платформы HPE Cray Supercomputing GX5000 — blade-серверы HPE Cray Supercomputing GX240. Эти устройства могут нести на борту до 16 процессоров NVIDIA Vera (88C/176T). В одной стойке могут быть размещены до 40 узлов, что в сумме даёт 640 чипов Vera и 56 320 ядер Olympus. Реализовано жидкостное охлаждение. Система предназначена для решения наиболее ресурсоёмких вычислительных задач в области ИИ. Новые серверы появятся на рынке в следующем году. Для платформы HPE Cray Supercomputing GX5000 также будут доступны коммутаторы NVIDIA Quantum-X800 InfiniBand, предоставляющие 144 порта с пропускной способностью до 800 Гбит/с. В этих устройствах реализованы развитые функции снижения энергопотребления. Кроме того, HPE готовит OCP-серверы высокой плотности Compute XD700 для обучения LLM и инференса. В основу данной системы положена платформа NVIDIA HGX Rubin NVL8, а одна стойка может насчитывать до 128 ускорителей Rubin. Данное решение появится в начале 2027-го. Помимо этого, анонсирована стоечная система нового поколения NVIDIA Vera Rubin NVL72 by HPE — это флагманская ИИ-платформа, разработанная для моделей с более чем 1 трлн параметров. Конфигурация включает 36 процессоров Vera, 72 чипа Rubin, интерконнект NVIDIA NVLink шестого поколения, сетевые адаптеры NVIDIA ConnectX-9 SuperNIC и DPU NVIDIA BlueField-4. Система поступит в продажу в декабре 2026 года.

19.03.2026 [15:32], Руслан Авдеев

16 тыс. км без регенерации сигнала: Ciena и Meta✴ установили рекорд дальности и скорости передачи данных по подводному кабелю BifrotstКомпании Ciena и Meta✴ установили мировой рекорд дальности высокоскоростной передачи данных без регенерации сигнала по действующему подводному кабелю на одной несущей — 800 Гбит/с. Речь идёт о системе Bifrost длиной 16 608 км, объединяющей Сингапур, Индонезию, Филиппины, Гуам и США. Тесты проводились на паре волокон, принадлежащих Meta✴. Испытания увенчались успехом благодаря технологии GeoMesh Extreme компании Ciena, она включает когерентную оптическую систему WaveLogic 6 Extreme (WL6e) и компактную реконфигурируемую систему 6500 Reconfigurable Line System (RLS). Ciena заявляет, что установление мирового рекорда дальности передачи с подобными характеристиками связи подтверждает ценность WL6e в качестве технологии, способной обеспечить «800G повсюду». Опыты доказывают, что сверхвысокоскоростную передачу данных можно обеспечить на самых длинных и сложных подводных маршрутах. Компания подчёркивает, что общая пропускная способность оптоволоконных пар составила в ходе испытаний 18 Тбит/с с избыточным эксплуатационным резервом. Использовался компактный SLTE (submarine line terminal equipment) высотой всего 10U, который оказался вдвое энергоэффективнее в сравнении с решением Ciena предыдущего поколения. Партнёры подчеркнули, что результаты имеют исключительное значение с точки зрения эффективности использования пространства и электроэнергии. Это критически важно для посадочных станций. Для Meta✴ проект имеет особое значение, поскольку должен помочь в управлении совместимой с ИИ-оборудованием инфраструктурой на больших расстояниях с уменьшением углеродных выбросов благодаря сниженному энергопотреблению и компактному объёму. Не так давно Ciena сообщала о рекордной для компании выручке $1,43 млрд в I квартале финансового года, на 33 % больше год к году. Компания назвала результата «беспрецедентным». В июне 2025 года сообщалось, что Telxius и Ciena установили рекорд скорости передачи данных между США и Европой по трансатлантическому кабелю Marea.

06.02.2026 [11:30], Сергей Карасёв

102,4 Тбит/с и СЖО: Aria Networks представила коммутаторы на платформе Broadcom Tomahawk 6 для ИИ-инфраструктурСтартап Aria Networks, базирующийся в Санта-Кларе (Калифорния, США), вышел из скрытого режима, анонсировав высокопроизводительные коммутаторы для крупномасштабных кластеров ИИ. В основу устройств положена аппаратная платформа Broadcom Tomahawk 6 (TH6). В новое семейство вошли три модели: Aria Tomahawk 6 (High Radix), Aria Tomahawk 6 (Liquid) и Aria Tomahawk 6 (Air). Все они обеспечивают суммарную коммутационную способность до 102,4 Тбит/с. Разработчик заявляет, что устройства могут применяться в составе ИИ-платформ с любыми типами ускорителей, будь то GPU NVIDIA и AMD, тензорные чипы или специализированные решения вроде Cerebras.

Источник изображения: Aria Networks Модель Aria Tomahawk 6 (Air) выполнена в форм-факторе 4U и оборудована воздушным охлаждением. Задействованы 512 блоков SerDes 200G. Коммутатор располагает 64 портами с пропускной способностью 1,6 Тбит/с каждый. Модификация Aria Tomahawk 6 (Liquid) имеет аналогичные технические характеристики, но заключена в 2U-корпус с жидкостным охлаждением. Наконец, вариант Aria Tomahawk 6 (High Radix) типоразмера 4U использует 1024 блока SerDes 100G. Устройство оборудовано 128 портами 800GbE; применяется воздушное охлаждение. На базе этого коммутатора могут формироваться кластеры с простой двухуровневой топологией, насчитывающие до 32 тыс. ИИ-ускорителей. Компания Aria Networks основана Мансуром Карамом (Mansour Karam), учредителем фирмы Apstra, которую в 2019 году приобрёл американский производитель сетевого оборудования Juniper Networks. Стартап Aria Networks фокусируется на разработке высокопроизводительных решений, сочетающих возможности стандартного Ethernet со специализированным программным уровнем, позволяющим управлять большим количеством модульных коммутаторов как единой системой. Утверждается, что этот унифицированный программный слой оптимизирует производительность и гарантирует надёжность инфраструктуры. Для эффективного управления коммутаторами применяются ИИ-алгоритмы.

15.12.2025 [12:11], Сергей Карасёв

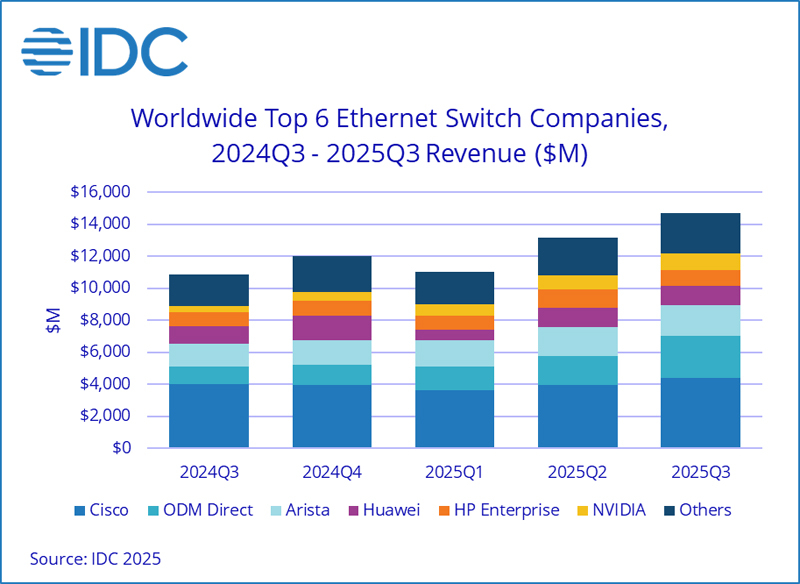

Квартальные продажи Ethernet-коммутаторов подскочили на треть благодаря спросу со стороны ЦОДКомпания International Data Corporation (IDC) подсчитала, что в III квартале уходящего года объём мирового рынка Ethernet-коммутаторов корпоративного класса достиг $14,7 млрд: это на 35,2 % больше по сравнению с аналогичным периодом 2024-го. Вместе с тем продажи маршрутизаторов для предприятий и поставщиков услуг увеличились на 15,8 % в годовом исчислении — до $3,6 млрд. Значительная положительная динамика обусловлена прежде всего развитием сегмента дата-центров. Гиперскейлеры и крупные облачные провайдеры активно закупают сетевое оборудование на фоне стремительного внедрения ИИ, которое сопровождается расширением инфраструктуры ЦОД. Поставки Ethernet-коммутаторов для дата-центров в денежном выражении выросли на 62,0 % по отношению к III четверти 2024 года. Выручка от устройств стандарта 800GbE подскочила на 91,6 % в квартальном исчислении, а их доля в общем объёме ЦОД-рынка составила 18,3 %. Продажи решений 200/400GbE взлетели на 97,8 % в годовом исчислении: на них приходится 43,9 % от общей выручки в сегменте дата-центров. В категории Ethernet-коммутаторов, не связанных с ЦОД, продажи за год поднялись на 8,2 %. Выручка от поставок решений 1GbE выросла на 1,2 %, 10GbE — на 14,3 %, 25/50GbE — на 20,9 % по сравнению с III кварталом 2024-го.

Источник изображения: IDC С географической точки зрения в Северной и Южной Америке рынок коммутаторов Ethernet в целом расширился на 41,6 %, чему способствовал активный рост в дата-центрах США. В регионе EMEA (Европа, Ближний Восток и Африка) продажи поднялись на 24,7 % в годовом исчислении, в Азиатско-Тихоокеанском регионе — на 32,7 %. В рейтинг крупнейших поставщиков коммутаторов Ethernet в глобальном масштабе входят Cisco, Arista Networks, HPE, NVIDIA и Huawei с долями соответственно 29,8 %, 12,8 %, 12,5 %, 11,6 % и 8,2 %. Отмечается, что выручка NVIDIA на рынке Ethernet-коммутаторов за год взлетела на 167,7 %. В секторе маршрутизаторов на поставщиков услуг пришлось 74,0 % от общего объёма выручки с ростом на 20,2 % в годовом исчислении. Корпоративное направление принесло 26,0 % продаж, показав прибавку на уровне 4,7 %. В региональном плане поставки маршрутизаторов в Северной и Южной Америке поднялись на 31,5 % в годовом исчислении, в Азиатско-Тихоокеанском регионе — на 7,7 %, а в регионе EMEA — на 3,5 %.

09.12.2025 [22:15], Владимир Мироненко

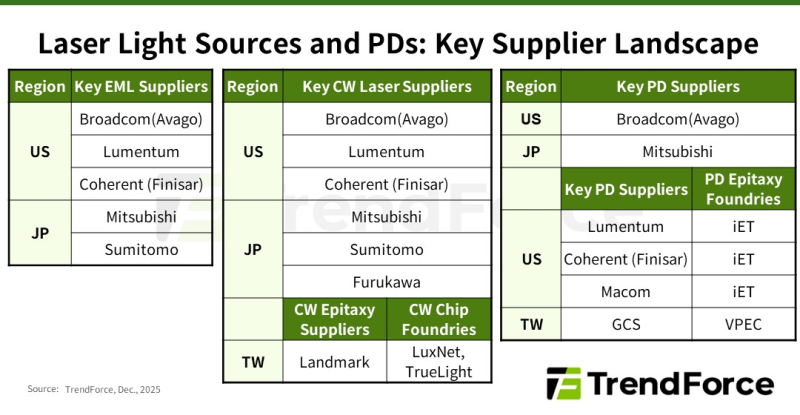

Дефицит добрался и до лазеров: NVIDIA зарезервировала чуть ли не всю продукцию ключевых поставщиковВ настоящее время высокоскоростные оптические соединения играют ключевую роль в обеспечении производительности и масштабируемости ИИ ЦОД, особенно по мере того, как они превращаются в крупные кластеры, сообщается в исследовании TrendForce. Согласно её прогнозу, в 2025 году мировые поставки оптических трансиверов с поддержкой скорости 800 Гбит/с и выше составят 24 млн шт. с последующим ростом в 2,6 раза почти до 63 млн шт. в 2026 году. Аналитики отметили, что резкий рост спроса на оптические трансиверы привёл к значительному дефициту в сфере производства источников лазерного излучения на глобальном рынке. NVIDIA в рамках стратегии развития зарезервировала крупные объёмы продукции у ключевых поставщиков EML-лазеров, что привело к увеличению сроков поставки — не ранее 2027 года. В связи с этим производители оптических модулей и провайдеры облачных услуг (CSP) вынуждены заниматься поиском вторичных поставщиков и альтернативных решений, что ведёт к изменениям в отрасли, отметили в TrendForce. Помимо лазеров VCSEL, используемых в линиях связи малой и средней дальности, оптические модули для линий средней и большой дальности в основном включают два типа лазеров: EML, отличающиеся большой дальностью действия и целостностью сигнала, и лазеры непрерывного излучения (CW). В EML-лазерах все ключевые функции объединены на одном кристалле, что делает их чрезвычайно сложными и трудоёмкими в изготовлении. Их производством занимается всего лишь несколько поставщиков, таких как Lumentum, Coherent (Finisar), Mitsubishi, Sumitomo и Broadcom. Впрочем, о дефиците Mitsubishi предупреждала более года назад. А Broadcom, вероятно, будет отдавать приоритет собственным продуктам. EML-лазеры играют важную роль в масштабировании вычислительных кластеров с увеличением расстояния между ЦОД. Планы NVIDIA по развитию кремниевой фотоники и интегрированной оптики (CPO) реализуются медленнее, чем предполагалось, что приводит к постоянной зависимости от подключаемых модулей для расширения кластеров. Чтобы обеспечить стабильную работу в этом направлении, NVIDIA заранее зарезервировала значительную часть мощностей по производству EML-лазеров, что отразилось на доступности компонента для остальных компаний. CW-лазеры, используемые в паре с кремниевыми фотонными чипами, отличаются более простой конструкцией, обусловленной отсутствием встроенной возможности модуляции, что упрощает производство и расширяет круг поставщиков. В результате CW-лазеры в сочетании с кремниевой фотоникой стали основным альтернативным решением для провайдеров облачных услуг в связи с дефицитом EML-лазеров. Впрочем, здесь тоже наблюдаются проблемы. Производство CW-лазеров сталкивается с растущими ограничениями, обусловленными рядом факторов: длительные сроки поставки оборудования ограничивают расширение производства, а строгие стандарты надёжности требуют трудоемких тестов. В результате многие поставщики передают эти этапы на аутсорсинг, что создает дополнительные узкие места в производственной цепочке. Ввиду того, что экосистема производства CW-лазеров приближается к дефициту мощностей, поставщики вынуждены форсировать усилия по расширению производства. Помимо лазерных передатчиков, для изготовления оптических модулей требуются высокоскоростные фотодиоды (PD) для приёма сигналов. Ведущие поставщики, такие как Coherent, MACOM, Broadcom и Lumentum, выпускают фотодиоды PD 200G с поддержкой скорости передачи данных 200 Гбит/с на канал. Фотодиоды производятся на эпитаксиальных пластинах из фосфида индия (InP), аналогично EML- и CW-лазерам. Поскольку производители лазеров стремятся расширить мощности для эпитаксии, многие из них передают заказы на InP-эпитаксию (процесс выращивания эпитаксиальных листов из фосфида индия на подложке) специализированным заводам, таким как IntelliEPI и VPEC, сообщили в TrendForce. TrendForce прогнозирует, что спрос, обусловленный ИИ, приведёт не только к сокращению предложения модулей памяти, но и отразится на экосистеме производства лазеров в целом. Стремление NVIDIA обеспечить необходимые объёмы поставок EML-лазеров привело к ускорению перехода к CW-решениям и кремниевой фотоники среди других производителей. В то же время общеотраслевая гонка за производственными мощностями меняет роли в цепочке поставок и стимулирует рост производства у поставщиков технологий эпитаксии и обработки полупроводниковых соединений, говорят аналитики.

24.11.2025 [08:45], Сергей Карасёв

Cornelis анонсировала 800G-адаптер CN6000 SuperNIC с поддержкой Omni-Path, RoCEv2 и Ultra Ethernet для ИИ и НРСКомпания Cornelis Networks анонсировала сетевой адаптер CN6000 SuperNIC со скоростью передачи данных до 800 Гбит/с, разработанный для систем ИИ и НРС. О намерении использовать решение объявили многие отраслевые игроки, включая Lenovo, Synopsys и Atipa Technologies. В устройстве реализована архитектура Omni-Path. Говорится о полной совместимости со стандартами Ultra Ethernet и RoCEv2. Таким образом, адаптер может применяться в высоконагруженных средах, где требуются максимальная пропускная способность при низких задержках. Адаптер CN6000 SuperNIC обеспечивает быстродействие до 1,6 млрд сообщений в секунду. Утверждается, что новинка поможет организациям ускорить обучение крупных ИИ-моделей при одновременном снижении расходов на электроэнергию и эксплуатацию дата-центров. Cornelis заявляет, что традиционные архитектуры RoCEv2 испытывают трудности при масштабировании в рамках масштабных GPU-кластеров из-за требований к ресурсам памяти при управлении парами связанных очередей (Queue Pair, QP) для отправки и приёма данных. CN6000 SuperNIC позволяет решить проблему благодаря принципиально иной конструкции: задействованы «облегчённые» алгоритмы QP и аппаратно-ускоренные таблицы RoCEv2 In-Flight (RiF), что даёт возможность отслеживать миллионы одновременных операций с минимальными требованиями к ресурсам. Это гарантирует предсказуемую задержку при максимальной пропускной способности в системах любого масштаба. Пробные поставки CN6000 SuperNIC планируется начать к середине 2026 года, после чего будет организовано массовое производство.

17.11.2025 [12:14], Сергей Карасёв

Nokia представила коммутаторы с пропускной способностью до 102,4 Тбит/сКомпания Nokia анонсировала высокопроизводительные коммутаторы семейства 7220 IXR-H6 для дата-центров, ориентированных на ресурсоёмкие нагрузки ИИ. Новинки соответствуют спецификациям Ultra Ethernet Consortium (UEC), поддерживая расширенные функции для оптимизации и управления потоками данных, предотвращения перегрузок и повышения эффективности в крупномасштабных средах. Коммутаторы обеспечивают пропускную способность до 102,4 Тбит/с благодаря интерфейсам 800GbE и 1.6TbE, что вдвое больше по сравнению с решениями предыдущего поколения. В серию 7220 IXR-H6 вошли две модели с 64 портами (1.6TbE), оборудованные воздушным и жидкостным охлаждением. В первом случае допускается горячая замена блоков вентиляторов. Кроме того, дебютировала модификация со 128 портами (800GbE). О типе применённого чипсета пока ничего не сообщается.

Источник изображения: Nokia Устройства комплектуются блоками питания с резервированием и возможностью горячей замены. Предусмотрены сетевой порт управления RJ45, разъём USB 3.0 и консольный порт. Коммутаторы могут поставляться с сетевой операционной системой SR Linux NOS или SONiC (Software for Open Networking in the Cloud). По заявлениям Nokia, решения семейства 7220 IXR-H6 могут применяться в составе платформ облачных провайдеров и гиперскейлеров, а также в ИИ-кластерах, насчитывающих более 1 млн ускорителей разных типов (XPU). Говорится о совместимости с серверными стойками различных конфигураций. В продажу коммутаторы поступят в I квартале следующего года.

05.11.2025 [14:30], Сергей Карасёв

Arista представила 800G-коммутаторы серии R4 для ИИ и облачных платформКомпания Arista анонсировала высокопроизводительные коммутаторы семейства R4 для крупномасштабных кластеров ИИ, дата-центров и облачных платформ. В серию вошли модели 7800R4, 7280R4 и 7020R4 для различных вариантов развёртывания. В основу новинок положен чип Broadcom Jericho3 Qumran3D. Для устройств заявлена поддержка современных архитектур, таких как EVPN, VXLAN, MPLS, SR/SRv6 и Segment Routing-TE. В некоторых моделях реализована технология HyperPort, которая объединяет четыре порта 800GbE в один канал с пропускной способность 3,2 Тбит/с. Модульная система Arista 7800R4 обеспечивает ёмкость до 460 Тбит/с, или до 920 Тбит/с в полнодуплексном режиме. Возможны конфигурации с 576 портами 800GbE, 1152 портами 400GbE или 4608 портами 100GbE. Пропускная способность достигает 173 млрд пакетов в секунду. Задержка — менее 4 мкс. Предусмотрены варианты исполнения 10U, 16U, 23U и 32U. Энергопотребление варьируется от 6,8 до 28 кВт. Упомянута поддержка HyperPort.

Источник изображения: Arista Коммутатор 7280R4, в свою очередь, предлагается в конфигурациях с 32 портами 800GbE (OSFP/QSFP-DD) или с 64 портами 100GbE + 10 портов 800GbE. Ёмкость достигает 25,6 Тбит/с (51,2 Тбит/с в полнодуплексном режиме), пропускная способность — 9,6 млрд пакетов в секунду. Устройство укомплектовано 8-ядерным процессором с архитектурой x86, 64 Гбайт DRAM и SSD вместимостью 480 Гбайт. Версия Arista 7020R4 может оснащаться 48 портами 1/10/25GbE SFP или RJ45 (плюс 4 или 8 восходящих каналов 100GbE). Ёмкость составляет до 2 Тбит/с, пропускная способность — до 1 млрд пакетов в секунду. Коммутатор несёт на борту 4-ядерный чип x86, 32 Гбайт DRAM и SSD на 120 Гбайт. Заявленная задержка находится на уровне 3,8 мкс.

01.11.2025 [14:52], Сергей Карасёв

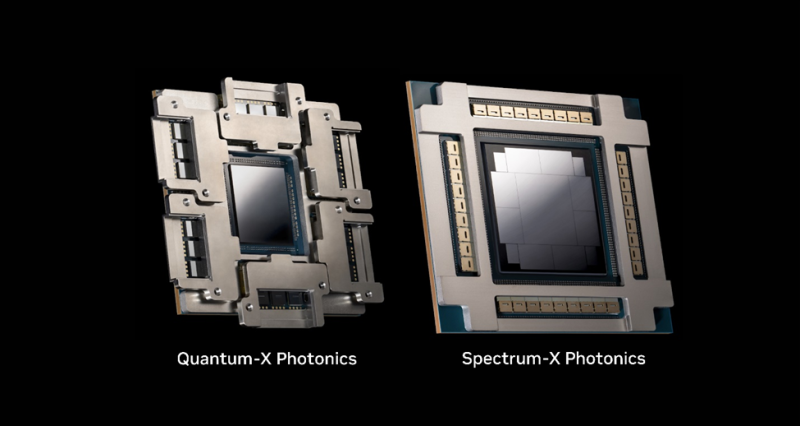

Cisco представила свои первые коммутаторы на чипах NVIDIA — N9100 с пропускной способностью 51,2 Тбит/сКомпания Cisco анонсировала высокопроизводительный коммутатор серии N9100, предназначенный для использования в ИИ ЦОД. Устройство, выполненное на платформе NVIDIA Spectrum-X Ethernet, создано в рамках инициативы NVIDIA Cloud Partner (NCP). Речь идёт о предоставлении эталонной архитектуры, ориентированной в том числе на провайдеров суверенного облака. Представленный коммутатор (модель Cisco N9164E-NS4-O) оснащён ASIC NVIDIA Spectrum-4. Устройство наделено 64 портами 800G OSFP, что в сумме обеспечивает пропускную способность до 51,2 Тбит/с. Возможно использование Cisco NX-OS (Nexus Operating System) и SONiC. Новинка несёт на борту процессор Intel Xeon D-1734NT (Ice Lake-D; 8C/16T, до 3,1 ГГц). Объём системной памяти составляет 64 Гбайт. Предусмотрен встроенный SSD вместимостью 240 Гбайт. Питание обеспечивают два блока мощностью 3000 Вт. За охлаждение отвечают четыре вентилятора с возможностью горячей замены. Диапазон рабочих температур — от 0 до +40 °C. Устройство, выполненное в форм-факторе 2RU, имеет размеры 439,2 × 705 × 87,9 мм. В целом, коммутаторы N9100 объединяют программный и сетевой стек Cisco с высокопроизводительным чипом NVIDIA, обеспечивая гибкость и масштабируемость при формировании крупных инфраструктур ИИ. При этом система управления и автоматизации Cisco Nexus Dashboard упрощает эксплуатацию дата-центра благодаря всестороннему мониторингу и гибким инструментам устранения неполадок. |

|