Материалы по тегу: cpu

|

13.05.2025 [22:15], Алексей Степин

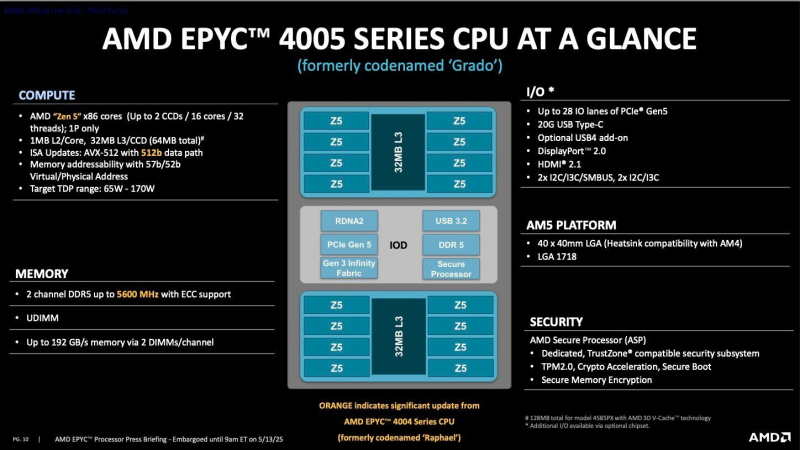

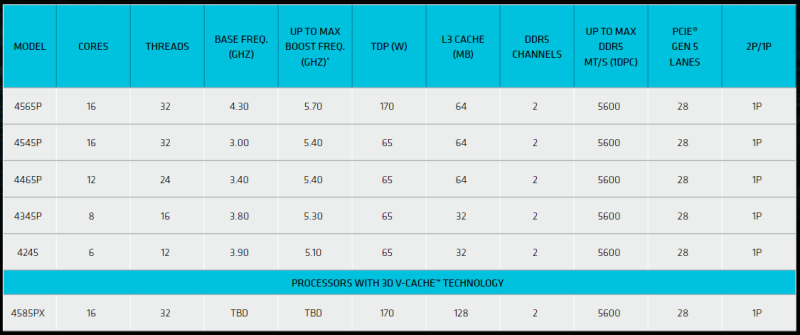

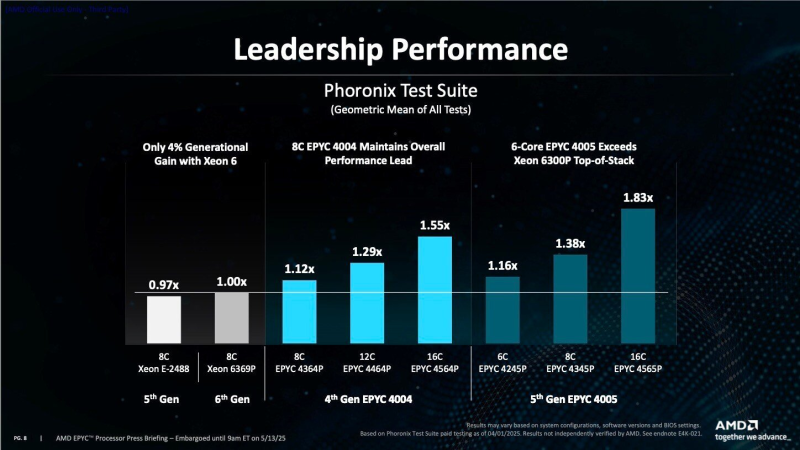

AMD представила процессоры EPYC 4005 Grado для сокета AM5Спустя год после анонса серверных процессоров начального уровня EPYC 4004 компания AMD обновила данный модельный ряд улучшенными чипами EPYC 4005 Grado. Как и прежде, процессоры ориентированы на применение в серверах для периферийных вычислений, хостинга, а также в решениях для малого и среднего бизнеса. В основе Grado лежат ядра Zen 5, что позволило повысить удельную производительность, получить поддержку более скоростной памяти DDR5 и расширенные возможностями ввода-вывода. Процессоры EPYC 4005 могут иметь до 16 ядер с поддержкой SMT и полноценной реализации AVX-512. Объём кеша L2 составляет 1 Мбайт на ядро, L3 — 32 Мбайт на восьмиядерный кристалл CCD; некоторые модели оснащаются дополнительным объёмом 3D V-Cache. Контроллер памяти в блоке IOD двухканальный, поддерживаются модули DDR5-5600 ECC суммарным объёмом до 192 Гбайт. Стоит, однако, отметить, что с памятью без коррекции ошибок EPYC 4005 не совместимы. Как и предки новинки в лице настольных Ryzen, EPYC 4005 предоставляют 28 линий PCI Express 5.0, а также интерфейсы USB 3.2 и USB 4 (опционально). Интегрированное видеоядро предлагает поддержку Display Port 2.0 и HDMI 2.1. В плане подсистемы накопителей процессоры могут обеспечивать работу до 14 устройств в различных конфигурациях, включая SATA и NVMe. Поддерживаются массивы RAID 0/1/5/10 с возможностью миграции. Наличие встроенного сопроцессора безопасности AMD Secure Processor вкупе с поддержкой TPM 2.0, шифрованием памяти и поддержкой доверенных зон (TrustZone) гарантирует высокий уровень безопасности. Процессоры полностью совместимы с инфраструктурой AM5 (LGA 1718), что облегчит жизнь системным интеграторам. Даже AMD EPYC 4004 имели лучшее соотношение возможностей к цене, нежели могли предложить аналогичные по классу Intel Xeon E-2400. Сохраняется это положение дел и для EPYC 4005: у Intel Xeon 6300 максимум восемь ядер, в то время как решение AMD может предложить 16 полновесных ядер Zen 5. Впрочем, у Intel есть ещё серия Granite Rapids-D, самые младшие модели которой гипотетически могут составить конкуренцию EPYC 4005. Всего в новую серию на момент анонса вошло шесть моделей. Венчает список 16-ядерный EPYC 4565P с теплопакетом 170 Вт (4,3–5,7 ГГц) стоимостью $589. Несколько особняком стоит модель EPYC 4585PX с расширенным до 128 Мбайт кешем L3, в остальном повторяющая характеристики модели 4565P. За кеш придётся доплатить — обойдётся такой EPYC в $699. Остальные представители модельного ряда EPYC 4005 имеют теплопакет 65 Вт, а их турбо-частоты ограничены 5,4–5,5 ГГц при базовых частотах менее 4 ГГц и количестве ядер от 6 до 16. Ресурс Phoronix уже провёл предварительное тестирование новинок, получив обнадёживающие результаты: EPYC 4565 в 1,83 раза превзошёл Intel Xeon 6369P, и даже шестиядерный EPYC 4245P опередил того же соперника на 16 %. Восьмиядерный EPYC 4345P оставил позади бывшего флагмана из серии Xeon E с 38-% отрывом. Все модели AMD EPYC 4005 поддерживают работу в среде Windows Server, RHEL, SLES и Ubuntu. Доступны новые процессоры AMD EPYC уже сейчас. Ряд ведущих производителей серверного оборудования, в том числе Altos, ASRock Rack, GIGABYTE, Mitac, MSI и Supermicro представили свои варианты решений на базе EPYC 4005.

07.05.2025 [11:28], Сергей Карасёв

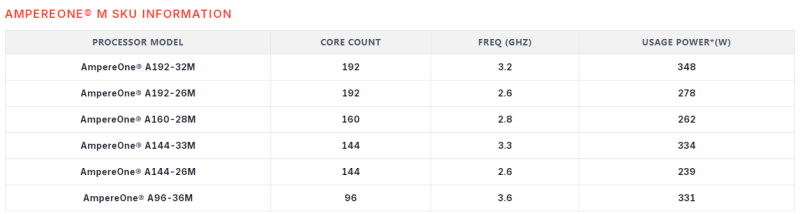

Ampere представила процессоры AmpereOne M для ИИ-задач: до 192 ядер Arm и 12 каналов памяти DDR5Компания Ampere Computing анонсировала процессоры семейства AmpereOne M, разработанные специально для поддержания ресурсоёмких ИИ-нагрузок в дата-центрах. Утверждается, что чипы подходят для задач инференса, работы с большими языковыми моделями (LLM), генеративным ИИ и пр. О подготовке новых изделий впервые сообщалось летом прошлого года. Конфигурация процессоров включает от 96 до 192 кастомизированных 64-бит ядер на базе Arm v8.6+. Имеется 16 Кбайт кеша инструкций и 64 Кбайт кеша данных L1 в расчёте на ядро, а также 2 Мбайт L2-кеша на ядро. Объём системного кеша составляет 64 Мбайт. Реализованы 12 каналов DDR5-5600 (поддерживается один модуль DIMM на канал) с возможностью адресации до 3 Тбайт памяти.

Источник изображений: Ampere Конструкция чипов включает 96 линий PCIe 5.0 с поддержкой бифуркации до режима x4 и возможностью использования до 24 дискретных подключённых устройств. Упомянуты средства виртуализации, шифрование памяти, поддержка прерываний I2C, GPIO, QSPI и GPI, системный и сторожевой таймеры. Предусмотрены развитые функции обеспечения безопасности, включая повышение производительности криптографических алгоритмов RNG, SHA512, SHA3. На сегодняшний день в серию AmpereOne M входят шесть моделей с тактовой частотой от 2,6 до 3,6 ГГц. Показатель TDP варьируется от 239 до 348 Вт. Благодаря интеллектуальной сети с высокой пропускной способностью и большому количеству однопоточных вычислительных ядер обеспечивается линейное масштабирование производительности в зависимости от текущей рабочей нагрузки. Возможна динамическая оптимизация мощности. Процессоры используют 7228-контактный разъём FCLGA. При производстве применяется 5-нм технология TSMC. По заявлениям Ampere, новые CPU подходят для применения в составе систем для серверных стоек высокой плотности. Благодаря этому достигается снижение эксплуатационных расходов по сравнению с ИИ-инфраструктурой на базе GPU.

01.05.2025 [00:15], Владимир Мироненко

«Байкал электроникс» поставила в Россию 85 тыс. процессоров Baikal

arm

baikal-l

baikal-m

baikal-s

cpu

hardware

risc-v

байкал электроникс

импортозамещение

микроконтроллер

россия

санкции

сделано в россии

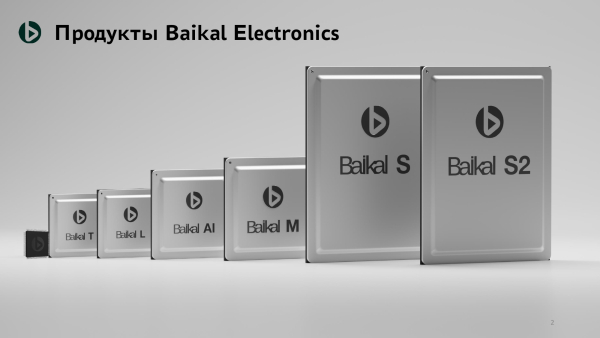

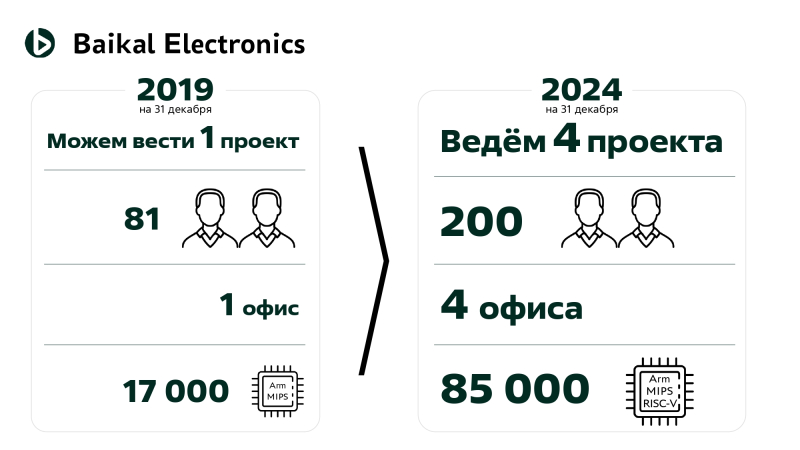

Компания «Байкал электроникс» за время работы ввезла в Россию 85 тыс. процессоров собственной разработки, включая модели Baikal-T, Baikal-M и Baikal-S. Из этого объёма компания поставила на российский рынок в 2019 году 17 тысяч процессоров. Об этом рассказал гендиректор «Байкал электроникс» Андрей Евдокимов на конференции «Планирование карьеры в электронной области», прошедшей в МИЭТ в апреле 2025 года. По словам Евдокимова, поставки должны были быть гораздо больше, но из-за санкций производство чипов было прекращено. Так, на Тайване была арестована партия из 150 тыс. процессоров Baikal-M. Кроме того, «Байкал электроникс» пришлось отменить из-за санкций заказ на изготовление 15 тыс. штук чипа Baikal-S, благо компания не успела его оплатить. В связи с отказом TSMC обслуживать российских заказчиков, выпуск Baikal-S был полностью отменён летом 2022-го года. Кроме того, санкциям подверглись и разработчики open source ПО. Вместе с тем «Байкал электроникс» продолжает работать и расширять свою деятельность. Если в 2019 году в ней работал 81 сотрудник и был один офис, то сейчас у компании четыре офиса и штат сотрудников составляет 205 человек. В настоящее время компания занимается четырьмя проектами. Евдокимов сообщил, что компания в апреле начала серийное производство собственного микроконтроллера Baikal-MCU, о разработке которого сообщалось два года назад, и вскоре будет направлен в серийное производство чип Baikal-L для ноутбуков и планшетов. Также в настоящее время в разработке компании находится следующее поколение серверных чипов Baikal-S2. Ранее компания также рассчитывала разработать Arm-процессоры Baikal-M2 и Baikal-M Lite, RISC-V чипы Baikal-NX, а также ИИ-ускорители Baikal AI SoC-C (для ЦОД) и AI SoC-E (для периферии). ИИ-ускорители, как ожидается, будут анонсированы в следующем году. По-видимому, в результате санкций компания пересмотрела развитие ряда проектов.

18.04.2025 [12:14], Сергей Карасёв

Массовый выпуск серверных процессоров на предприятиях в России начнётся не раньше 2030 годаСерийное производство российских высокопроизводительных процессоров для серверов на отечественных предприятиях будет освоено не ранее, чем через восемь лет. Об этом, как сообщает ComNews, заявил заместитель директора по развитию АО «МЦСТ» (разработчик чипов «Эльбрус») Константин Трушкин. По его словам, заводы, способные выпускать серверные чипы по 28-нм технологии, могут появиться в России «на горизонте 2028–2030 гг.». Ещё около трёх лет потребуется на получение массовой партии серверных процессоров с российскими кристаллами в соответствии с запросами участников рынка. Таким образом, в лучшем случае такие изделия в необходимых количествах станут доступны в 2031-м. Как отмечает Трушкин, организация подобного производства — это сложный технологический процесс. Для его отладки необходим партнёр, готовый «передать на завод дизайн сложной микросхемы» и совместными усилиями выявить возможные проблемы. Из-за высокой трудоёмкости такого проекта необходима поддержка, которую, по мнению Трушкина, могли бы оказать регуляторы. Переход на российские процессоры важен в связи со сформировавшейся геополитической обстановкой и санкциями, которые затрудняют закупки зарубежного оборудования.

Источник изображения: «МЦСТ» Трушкин считает, что «МЦСТ» станет первой отечественной компанией, которая сможет освоить массовый выпуск высокопроизводительных серверных процессоров на российском заводе. По его словам, изделия «Эльбрус» благодаря своей архитектуре позволяют получать значительную производительность с единицы площади кристалла. Вместе с тем участники рынка говорят, что, помимо создания российских серверных чипов, необходимо переписать ПО под новую архитектуру. При этом с портированием софта могут возникнуть серьёзные сложности из-за дефицита квалифицированных специалистов в соответствующей области.

15.04.2025 [23:38], Владимир Мироненко

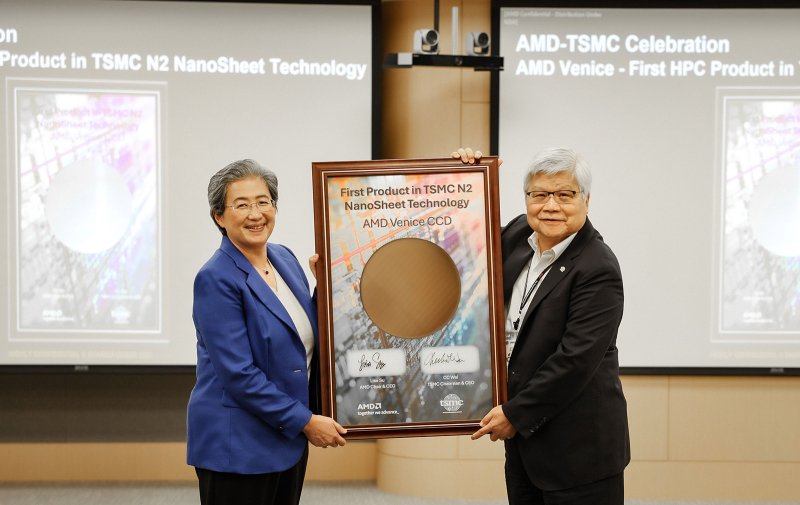

AMD начнёт размещать заказы на производство чипов в СШАAMD впервые в своей новейшей истории начнёт размещать заказы на производство своих чипов в США — на заводе TSMC в Аризоне. Об этом заявила 15 апреля генеральный директор AMD Лиза Су (Lisa Su) в ходе своего визита на Тайвань, где провела встречу с руководством TSMC, а также с другими партнёрами, пишет Reuters. Лиза Су сообщила, что совместно с TSMC был достигнут ряд важных вех, включая успешный пробный выпуск 2-нм чипа. Она также продемонстрировала совместно с генеральным директором TSMC Си-Си Вэем (C.C. Wei) кремниевую пластину с образцами чиплета CCD для серверных процессоров EPYC Venice на архитектуре Zen 6, который будет производиться с использованием 2-нм техпроцесса TSMC N2 — это первый в отрасли продукт для HPC-систем, который будет выпускаться по столь тонкой технологии со следующего года, говорит AMD. AMD также объявила об успешном запуске и валидации AMD EPYC Turin на новой фабрике TSMC в Аризоне. «Наш новый EPYC пятого поколения показал себя очень хорошо, поэтому мы готовы начать производство», — заявила журналистам в Тайбэе Лиза Су. Выпуск чипа начнётся в 2026 году. Правда, самые передовые техпроцессы, включая 2-нм, эта фабрика получит только через несколько лет. Как сообщают ресурсы Anue и TechNews, Лиза Су также заявила, что хотя Тайвань является ключевым регионом в цепочкк поставок AMD, компания наращивает своё присутствие в США. Су отметила, что приобретение ZT Systems за $4,9 млрд стало ключевым шагом для увеличения производства ИИ-серверов на чипах AMD в США: «Мы хотим иметь очень устойчивую цепочку поставок, поэтому Тайвань продолжает оставаться очень важной частью этой цепочки поставок, но Соединённые Штаты также будут важны, и мы расширяем нашу работу там, включая нашу работу с TSMC и другими ключевыми партнёрами». Впоследствии Су также подтвердила намерение «найти стратегического партнёра для [продажи] производственных активов компании ZT Systems». Она не стала вдаваться в подробности, но по данным Bloomberg, Compal Electronics, Wiwynn (Wistron) и Jabil собираются представить предложения по покупке производственных мощностей ZT Systems. Ранее демонстрировавшие интерес к покупке Inventec, которая в итоге продала AMD свою долю в ZT Systems, и Pegatron отказались от дальнейшего участия в борьбе за этот актив, сообщили источники Bloomberg. Сейчас самое подходящее время для AMD для продажи производственных мощностей в США, поскольку многие тайваньские OEM/ODM-вендоры спешат начать строительство заводов в США, чтобы избежать текущих или будущих пошлин, отметил Bloomberg. AMD намерена завершить продажу к концу II квартала. Стоимость сделки оценивается в $3–4 млрд. В свою очередь, NVIDIA объявила в понедельник о планах в течение четырёх следующих лет выпустить в США с помощью производственных партнёров ИИ-платформы на $500 млрд. Сейчас компания строит заводы совместно с Foxconn в Хьюстоне и с Wistron в Далласе. Тайваньские фирмы, включая Foxconn (Hon Hai Precision Industry Co.), полагаются на Мексику как на ключевой центр сборки и производства компонентов ИИ-серверов. После президентских выборов в США в прошлом году Foxconn приобрела землю под новое производствj и пообещала, что вскоре объявит о дополнительных инвестициях в экономику США. А тайваньская Quanta Computer одобрила увеличение уставного капитала своего американского подразделения на $230 млн.

05.04.2025 [10:35], Сергей Карасёв

Представлен первый в Китае высокопроизводительный процессор RISC-V для серверов — чип LingyuКитайская компания RiVAI Technologies, по сообщению ресурса Tom's Hardware, представила первый высокопроизводительный серверный процессор с открытой архитектурой RISC-V, полностью разработанный в КНР. Презентация изделия под названием Lingyu состоялась в Шэньчжэне: появление чипа отражает стремление страны к снижению зависимости от зарубежных изделий в условиях усиливающихся санкций со стороны США. Чип Lingyu насчитывает в общей сложности 40 ядер. Это 32 универсальных вычислительных ядра (CPU) и восемь специализированных ядер (LPU), предназначенных для нагрузок, связанных с ИИ, включая работу с большими языковыми моделями (LLM). Такая конфигурация ориентирована на достижение баланса между производительностью и энергоэффективностью, благодаря чему снижается общая стоимость владения (TCO). Прочие характеристики процессора пока не раскрываются. Основателем компании RiVAI Technologies является Чжанси Тан (Zhangxi Tan). Он получал образование под наставничеством Дэвида Паттерсона (David Patterson) — американского учёного в области информатики, профессора и лауреата премии Тьюринга 2017 года. Паттерсон, разработавший в 1990–2000 гг. несколько вариантов RISC-архитектур, выступает в качестве консультанта RiVAI Technologies. Отмечается, что RiVAI Technologies заключила партнёрские соглашения с более чем 50 компаниями, включая Lenovo и SenseTime, с целью развития экосистемы вокруг своих чипов RISC-V. Сотрудничество направлено на внедрение Lingyu в различных отраслях. Предполагается, что усилия будут способствовать дальнейшему развитию RISC-V в Китае. В целом, КНР ведёт активные исследования и разработки в области RISC-V. В частности, ранее ряд китайских компаний, включая T-Head (принадлежит гиганту Alibaba Group Holding), Shanghai Shiqing Technology, Juquan Optoelectronics, Xinsiyuan Microelectronics и StarFive, сформировали патентный альянс в сфере RISC-V. Кроме того, Пекин планирует запустить государственную программу с целью стимулирования широкого использования RISC-V по всей стране. Разработкой RISC-V-процессоров занимается Китайская академия наук.

01.04.2025 [14:53], Владимир Мироненко

Arm намерена занять 50 % рынка чипов для ЦОД к концу 2025 года — NVIDIA ей в этом поможетСогласно прогнозу Arm Holdings, к концу 2025 года доля процессоров с Arm-архитектурой на мировом рынке CPU для ЦОД вырастет до 50 % с 15 % в 2024 году. В интервью агентству Reuters Мохамед Авад (Mohamed Awad), руководитель подразделения инфраструктурных решений Arm, отметил, что благодаря более низкому энергопотреблению, чем у процессоров Intel и AMD, Arm-чипы становятся все более популярными среди компаний, занимающихся облачными вычислениями. Журналист ресурса The Register обратился в Arm Holdings с просьбой пояснить, благодаря чему компания рассчитывает добиться столь стремительного роста доли на рынке. Как сообщили в британской компании, принадлежащей японскому конгломерату Softbank, её прогноз в значительной степени основан на росте поставок ИИ-серверов. Мохамед Авад сообщил The Register, что в течение следующих нескольких лет, как ожидает компания, продажи ИИ-серверов вырастут на 300 %. «Для этого увеличения энергоэффективность больше не является конкурентным преимуществом — это базовое отраслевое требование. Именно здесь вычислительная платформа Arm Neoverse является явным лидером и предпочтительной платформой для ведущих партнёров отрасли, включая AWS, Google, Microsoft и NVIDIA», — заявил он. Как утверждает Arm Holdings, Arm-архитектура всё чаще используется гиперскейлерами AWS, Google, Microsoft в своих чипах. По оценкам Bernstein Research, в 2023 году почти 10 % серверов по всему миру содержат Arm-процессоры приложений в качестве «основных мозгов», и половина из них была развёрнута Amazon, сообщившей, что у нее в облаке используется более 2 млн чипов Graviton собственной разработки. В свою очередь, Google объявила в 2024 году о выпуске собственного процессора Axion на базе Neoverse V2 для своих ЦОД, а Microsoft сообщила в конце прошлого года об общедоступности в облаке Azure инстансов с использованием процессоров собственной разработки Cobalt 100. Расширение использования этими провайдерами облачных услуг Arm-процессоров может объяснить часть роста, который Авад прогнозирует на этот год, но продукты NVIDIA также, вероятно, составят значительную долю, полагает The Register. Например, система DGX GB200 NVL72 включает 36 процессора NVIDIA Grace и 72 ускорителя Blackwell B200, что составляет 2592 ядра Arm Neoverse V2, и они, вероятно, будут востребованы в этом году, отметил ресурс. Также не следует забывать о других решениях для ЦОД, которые имеют ядра на базе Arm-архитектуры, такие как SmartNIC и DPU — BlueField-3 от NVIDIA, а также карты Nitro в серверах AWS.

20.03.2025 [13:53], Руслан Авдеев

SoftBank решила купить производителя Arm-процессоров Ampere Computing за $6,5 млрдSoftBank Group подтвердила покупку производителя Arm-чипов Ampere Computing. Сделка оценивается в $6,5 млрд и, как ожидается, будет закрыта во II половине 2025 года, сообщает Silicon Angle. Оба главных акционера Ampere — Oracle и Carlyle Group — согласились продать свои доли в компании. После покупки Ampere будет действовать как независимое дочернее подразделение SoftBank, штаб-квартира компании по-прежнему останется в Санта-Кларе (Калифорния). Основанная в 2017 году бывшим вице-президентом Intel Рене Джеймс (Renee James) компания специализируется на выпуске серверных Arm-процессоров. Самой производительной моделью является AmpereOne M, поставки которого начались в декабре 2024 года. Процессор получил до 192 ядер и большую пропускную способность памяти, чем его предшественники. Также компания работает над разработкой ещё более производительного CPU Aurora который получит 512 ядер, HBM-память и выделенный ИИ-модуль.

Источник изображения: Ampere В SoftBank заявили, что покупают Ampere, в которой трудятся около 1 тыс. специалистов по полупроводникам, поскольку будущее «искусственного суперинтеллекта» требует прорывных вычислительных мощностей. Опыт Ampere в сфере чипов и HPC поможет ускорить соответствующие процессы и углубляет приверженность SoftBank к ИИ-инновациям в США. По имеющимся данным, Ampere впервые рассматривала продажу в сентябре 2024 года, позже компания наняла финансового консультанта для оценки перспектив. SoftBank выразила потенциальный интерес к покупке в январе 2025 года, а в прошлом месяце сообщалось, что переговоры о сделке идут весьма успешно. SoftBank уже является ключевым игроком на рынке чипов благодаря доле в Arm Holdings, купленной за $32 млрд в 2016 году. Arm вышла на IPO в 2023 году, но SoftBank всё ещё владеет крупнейшей долей компании. В прошлом июле SoftBank заключила сделку о покупке ещё одного производителя чипов — компании Graphcore, которая, как и Arm, базируется в Великобритании. Graphcore разрабатывает ИИ-ускорители. Сообщалось, что SoftBank может способствовать сотрудничеству Ampere и Graphcore в деле создания ИИ-серверов.

20.03.2025 [01:10], Владимир Мироненко

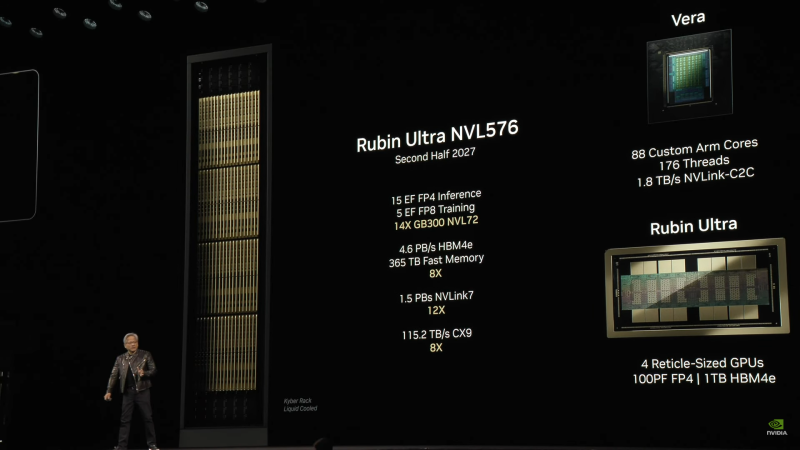

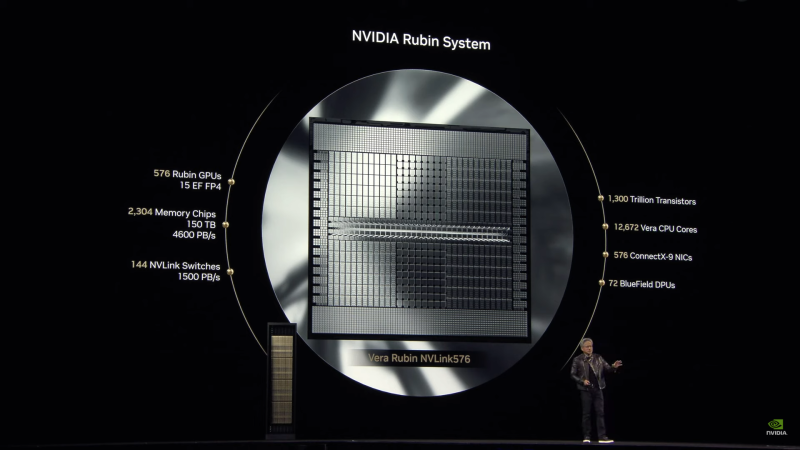

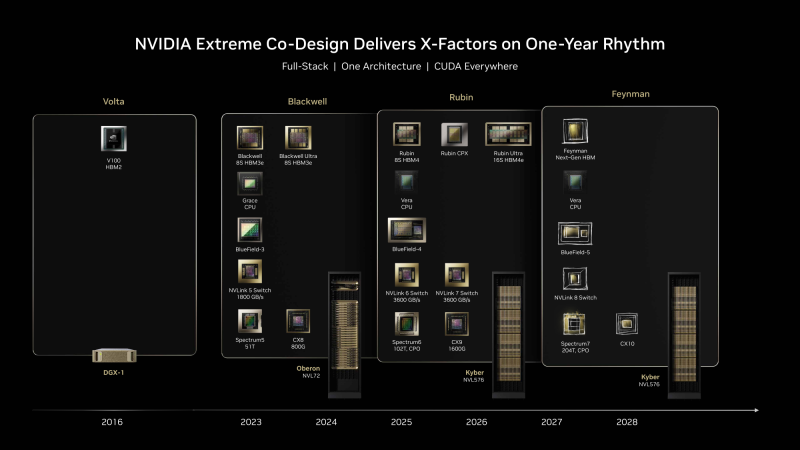

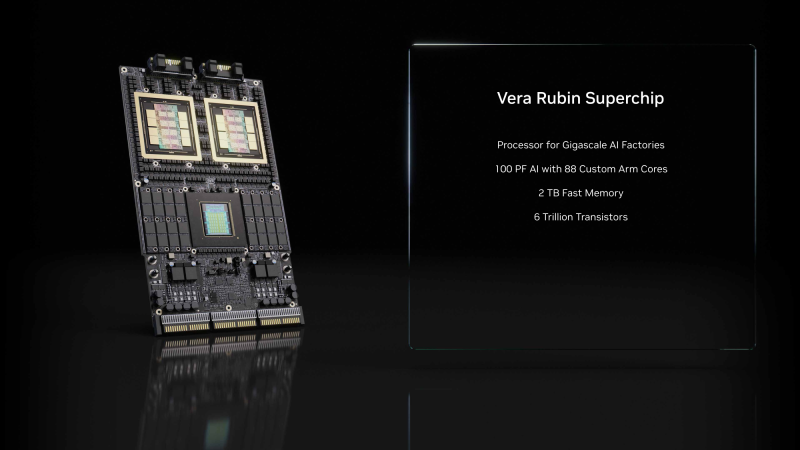

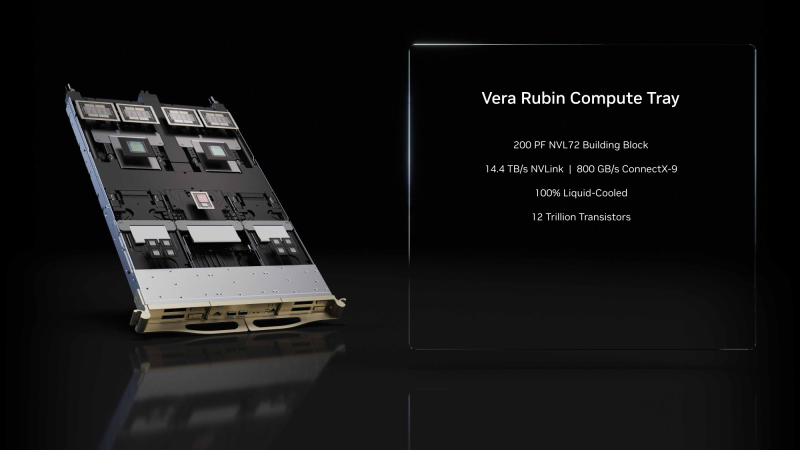

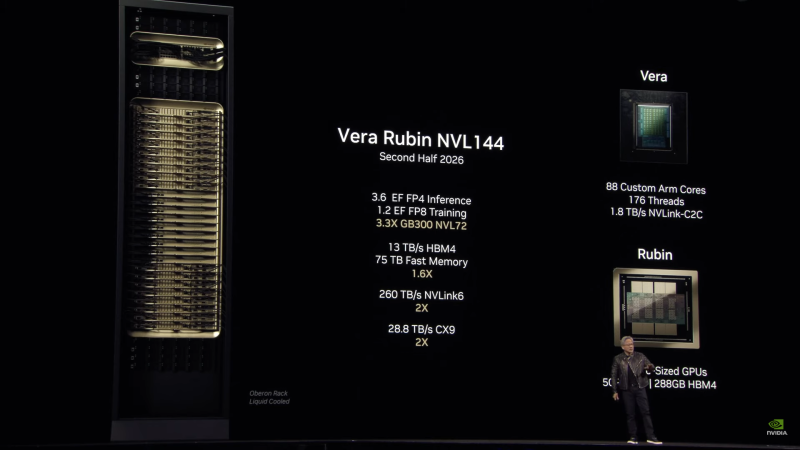

Анонсированы суперускорители на Rubin и Rubin Ultra, в которых NVIDIA не будет ошибаться в подсчётахNVIDIA анонсировала ИИ-ускорители следующего поколения Rubin, которые придут на смену Blackwell Ultra во II половине 2026 года. Выход Rubin Ultra запланирован на II половину 2027 года. Компанию им составят Arm-процессоры Vera. Серия названа в честь астронома Веры Купер Рубин (Vera Florence Cooper Rubin), известной своими исследованиями тёмной материи. NVIDIA отметила, что в названии предыдущих ускорителей была «допущена ошибка». В Blackwell каждый чип состоит из двух GPU, но, например, в названии GB200/GB300 NVL72 упоминается только 72 GPU, хотя речь фактически идёт о 144 GPU. Поэтому, начиная с Rubin компания будет использовать новую схему наименований, которая больше не учитывает количество чипов, а относится исключительно к количеству GPU. Таким образом, следующее поколение суперускорителей, упакованных в ту же стойку Oberon, что используется для Grace Blackwell, получило название Vera Rubin NVL144. Rubin во многом повторяет дизайн Blackwell, поскольку R200 всё так же включает два кристалла GPU (в составе SXM7), способных выдавать до 50 Пфлопс в вычислениях FP4 (без разреженности), и 288 Гбайт памяти в восьми стеках 12-Hi, но на этот раз уже HBM4 с общей пропускную способностью 13 Тбайт/с (2048-бит шина). Кристаллы GPU будут изготовлены по техпроцессу TSMC N3P, а компанию им составят два IO-чиплета, отвечающие за все внешние коммуникации, пишет SemiAnalysis. Всё вместе будет упаковано посредством CoWoS-L. TDP новинок не указывается.

Источник изображений: NVIDIA Чипы перейдут на интерконнект NVLink 6 со скоростью 1,8 Тбайт/с в каждую сторону (3,6 Тбайт/с в дуплексе), что вдвое выше, чем у текущего поколения NVLink 5. Аналогичным образом вырастет и коммутационная способность NVSwitch, а также NVLink C2C. Впрочем, при сохранении прежней схемы, когда один CPU обслуживает два модуля GPU, каждому из последних, по-видимому, достанется половина пропускной способности шины. Собственно процессор Vera получит 88 кастомных (а не Neoverse CSS в случае Grace) 3-нм Arm-ядра, причём с SMT, что даст 176 потоков. Каждый CPU получит порядка 1 Тбайт LPDDR-памяти и будет вдвое быстрее Grace при теплопакете в районе 50 Вт. По словам NVIDIA, VR200 NVL144 будет в 3,3 раза быстрее: 3,6 Эфлопс в FP4-вычислениях для инференса и 1,2 Эфлопс в FP8 для обучения. Суммарный объём HBM-памяти составит более 20,7 Тбайт, системной памяти — 75 Тбайт. Внешняя сеть будет представлена адаптерами ConnectX-9 SuperNIC со скоростью 1,6 Тбит/с на порт, что вдвое больше, чем у ConnectX-8, обслуживающих GB300. Во II половине 2027 года появится ускоритель Rubin Ultra (R300) с FP4-производительностью более 100 Пфлопс (без разреженности), объединяющий сразу четыре GPU, два IO-чиплета и 16 стеков HBM4e-памяти 16-Hi общим объёмом 1 Тбайт (32 Тбайт/с) в упаковке SXM8. Более того, ускорители, по-видимому, получат ещё и LPDDR-память. Процессор Vera перекочует в новую платформу без изменений, один CPU будет приходиться на четыре GPU. Внутренней шиной станет NVLink 7, которая сохранит скорость NVLink 6, зато получит вчетверо более производительные коммутатор NVSwitch. А вот внешнее подключение по-прежнему будут обслуживать адаптеры ConnectX-9. Новая стойка Kyber полностью поменяет компоновку. Узлы теперь напоминают вертикальные блейд-серверы, используемые в суперкомпьютерах. Каждый узел (VR300) будет включать один процессор Vera и один ускоритель Rubin Ultra. Всего таких узлов будет 144, что в сумме даёт 144 CPU, 576 GPU и 144 Тбайт HBM4e. Суперускоритель Rubin Ultra NVL576 будет потреблять 600 кВт и обеспечит быстродействие в 15 Эфлопс для инференса (FP4) и 5 Эфлопс для обучения (FP8). При этом упоминается, что объём быстрой (fast) памяти составит 365 Тбайт, но сколько из них достанется CPU, не уточняется. Дальнейшие планы NVIDIA включают выход во II половине 2028 года первого ускорителя на новой архитектуре Feynman, названной в честь физика-теоретика Ричарда Филлипса Фейнмана (Richard Phillips Feynman). Сообщается, что Feynman будет полагаться на память HBM «следующего поколения» и, вероятно, на CPU Vera. Это поколение также получит коммутаторы NVSwitch 8 (NVL-Next), сетевые коммутаторы Spectrum7 и адаптеры ConnectX-10. UPD: осенью компания представила соускорители Rubin CPX для масштабных задач ИИ-инференса, которые дополняют платформу Vera Rubin. Эти чипы будут доступны как в составе гибридной платформы NVIDIA Vera Rubin NVL144 CPX (144 × Rubin CPX + 144 × Rubin + 36 × Vera), так и в виде двухстоечного решения: Vera Rubin NVL144 CPX + Vera Rubin NVL144.

11.03.2025 [19:46], Алексей Степин

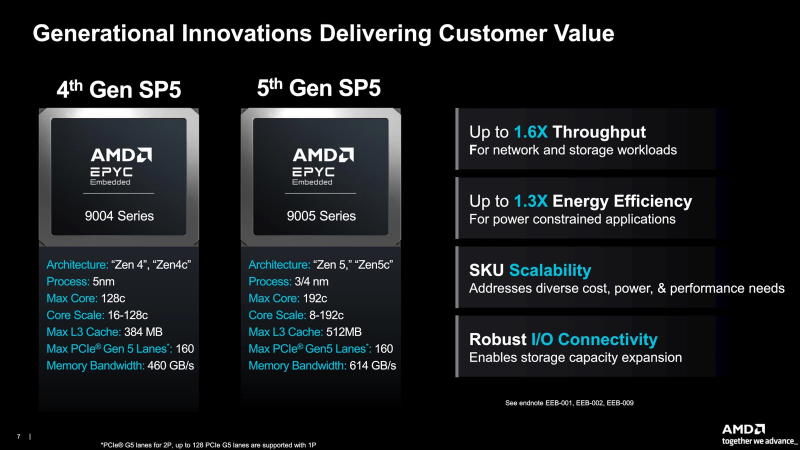

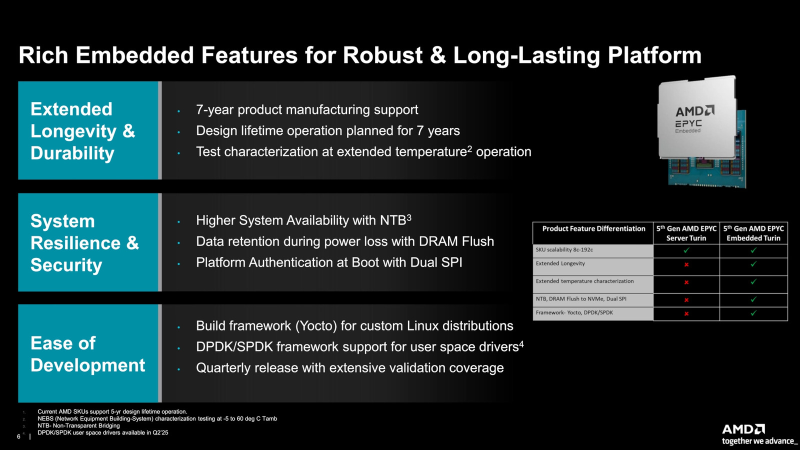

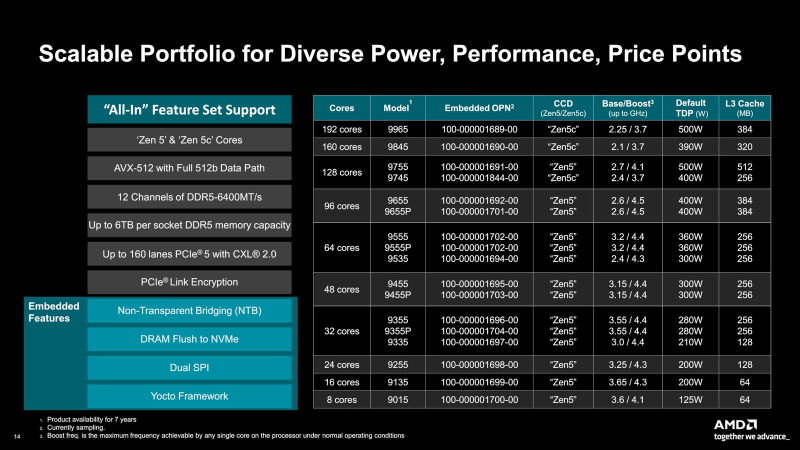

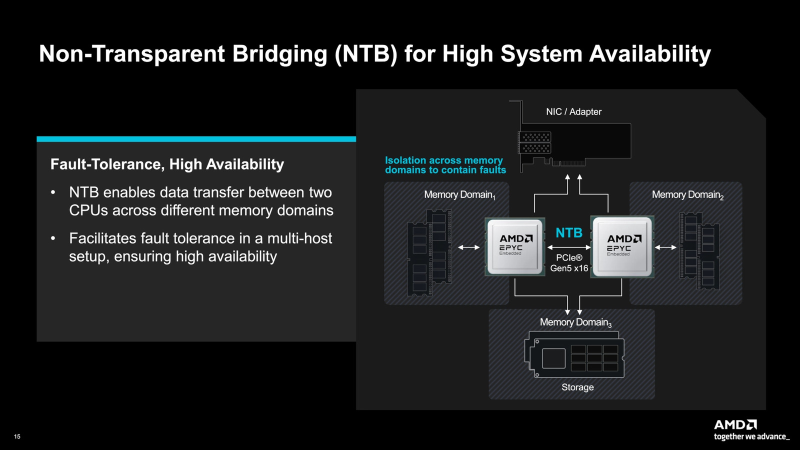

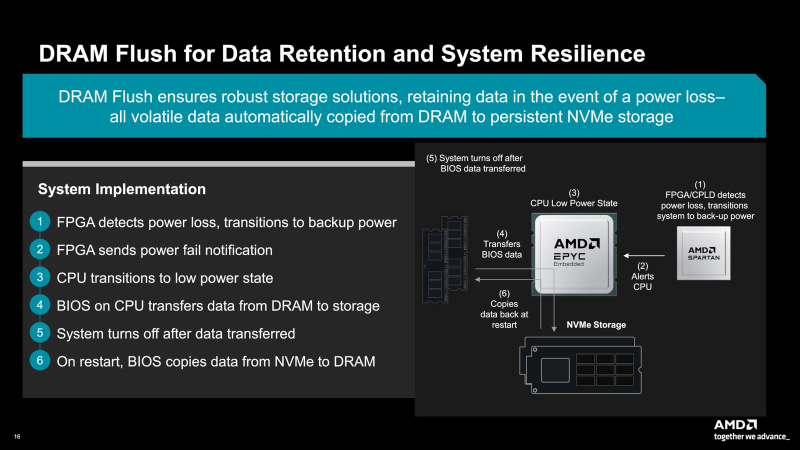

AMD представила EPYC Embedded 9005: до 192 ядер Zen 5(c), расширенная поддержка и высокая надёжностьAMD пополнила арсенал процессоров новыми моделями EPYC Embedded 9005, предназначенными для высоконагруженных встраиваемых решений, в том числе промышленных. Модельный ряд фактически повторяет ассортимент обычных EPYC 9005, но отличается некоторыми характерными для данного класса устройств особенностями, связанными с обеспечением повышенной надёжности и безопасности. Во-первых, конечно, следует отметить расширенный до 7 лет цикл поддержки данных решений. Во-вторых, сами процессоры EPYC Embedded 9005 рассчитаны на работу в более широком температурном диапазоне, так как встраиваемые платформы часто вынуждены функционировать отнюдь не в комфортных машинных залах ЦОД. Новые чипы поддерживают NTB (Non-Transparent Bridge), нужный для горячего резервирования в системах повышенной надежности, а также умеют безопасно сбрасывать содержимое оперативной памяти на NVMe-накопители при сбоях питания. Имеется поддержка CXL-модулей NV-CMM. Реализована аутентификация платформы при загрузке с использованием двух интерфейс SPI — один для образа BIOS, второй для кастомного загрузчика, которые проверяет целостность и корректность образа BIOS. Среди прочих особенностей отмечается наличие Secure I/O (SEV-TIO) и SDCI (Smart Data Cache Injection), а также расширенные функции мониторинга, в том числе OOB. Также реализованы расширенная коррекция ошибок DRAM и возможность переконфигурирования на лету сбойных DIMM. По сравнению c EPYC Embedded 9004 новые EPYC Embedded 9005 не только быстрее за счёт перехода на Zen 5, но и за счёт большего количества процессорных ядер — по этому параметру новый модельный ряд соответствует обычным серверным моделям и заканчивается на отметке 192 ядра. При этом в нём имеются как процессоры с классическими кристаллами Zen 5, так и с энергоэффективными Zen 5c. Новые процессоры AMD сертифицированы для работы с Yocto Linux и с DPDK/SPDK, что делает их пригодными в качестве основы для сетевого оборудования, в том числе маршрутизаторов и систем безопасности. Обновления ПО для разработчиков планируется выпускать на ежеквартальной основе. На данный момент AMD уже поставляет образцы новых процессоров, а полномасштабные отгрузки новинок начнутся во II квартале. |

|