Материалы по тегу: cpu

|

26.06.2025 [17:49], Алексей Степин

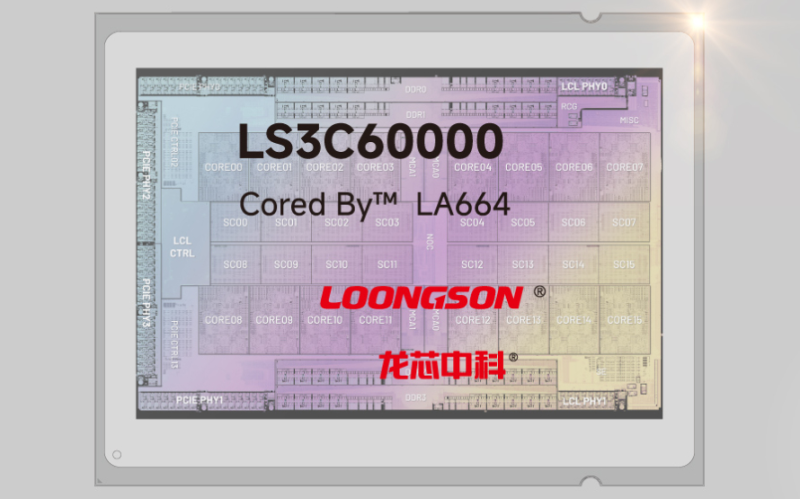

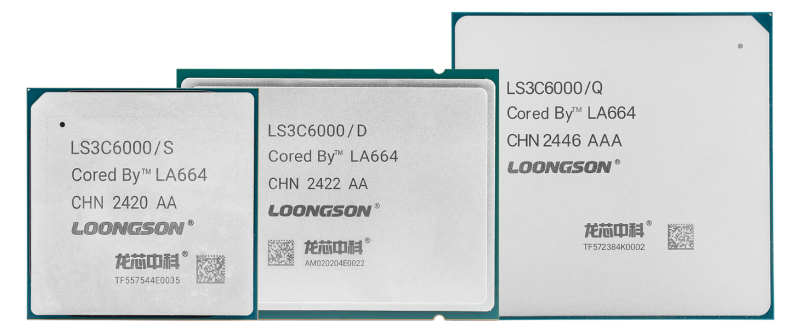

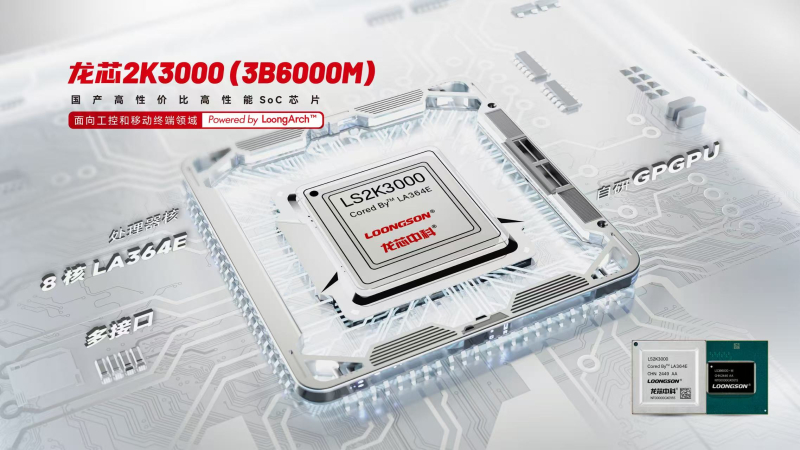

Loongson представила 64-ядерные серверные процессоры 3C6000 на базе LoongArchLoongson получила опытные образцы процессоров 3C6000 на базе архитектуры LoongArch ещё год назад, а сегодня китайская компания официально представила новинки. Эти процессоры, предназначенные для внутреннего рынка КНР, имеют чиплетную компоновку и содержат до 64 ядер LA664 с поддержкой SMT2. Это уже четвёртое поколение процессоров Longsoon с архитектурой LoongArch. Чиплетную компоновку сегодня используют все, и Loongson не исключение. Чиплетов в составе процессоров 3C6000 может быть от одного до четырёх. Чипы с литерой S имеют единственный чиплет, с D — два, а возглавляющие модельный ряд модели c индексом Q в названии несут на борту четыре 16-ядерных чиплета. Помимо стандартного набора инструкций LoongArch, имеется поддержка 126/256-бит векторных расширений. Дополнительно наличествует ядро LA264 (Loongson SE), выполняющее роль сопроцессора безопасности. Ядра LA664 имеют по 64 Кбайт кеша инструкций и данных, 256 Кбайт кеша L2, но кеш L3 общий, объёмом 32 Мбайт на чиплет. Дизайн ядер суперскалярный, с внеочередным исполнением с обработкой шести инструкций за такт. Каждое ядро содержит четыре целочисленных блока, четыре блока векторных операций и четыре модуля доступа к памяти. Подсистема памяти представлена четырёхканальным контроллером DDR4-3200, но многоядерные модели серий D и Q включают уже восемь каналов, а также могут работать в составе двух- и четырёхсокетных платформ. Базовые тактовые частоты ядер Loongson 3C6000 лежат в пределах 2,0–2,2 ГГц, но архитектура LA664 на частоте 2,2 ГГц показывает себя эффективнее в обработке целочисленных данных, нежели Xeon Scalable третьего поколения (Ice Lake-SP) на частоте 2,4 ГГц, хотя в вычислениях с плавающей запятой она, как было показано на презентации, несколько слабее. Речь о тестах SPEC CPU 2017, в ближайшее время ожидаются первые результаты новинок в других бенчмарках. На официальной сайте даны следующие показатели FP64-производительности: 844,8 Гфлопс на частоте 2,2 ГГц у S-модели, 1612,8 Гфлопс на частоте 2,1 ГГц у D-модели и 3072 Гфлопс на частоте 2,0 ГГц у Q-модели. Для связи между чиплетами применён фирменный интерконнект DragonChain. С внешним же миром процессоры общаются посредством интерфейса PCI Express 4.0 — 64 линии имеется даже у младших S-моделей, а у D и Q их уже 128. Теплопакет у одночиплетных процессоров укладывается в диапазон от 100 до 120 Вт, для более мощных моделей этот показатель варьируется в пределах 180 — 200 Вт для чипов D, для наиболее мощных Q он составляет от 250 до 300 Вт. Вместе с 3C6000 компания анонсировала процессоры 2K3000 и 3B6000M. Это сравнительно маломощные решения на базе архитектуры LA364E, содержащие до 8 ядер с частотой до 2,5 ГГц, а также интегрированный видеоускоритель LG200 (в предыдущих моделях использовался LG100) с производительностью 256 Гфлопс в режиме FP32. Имеется и ИИ-сопроцессор мощностью 8 Топс (INT8). Эти решения нацелены на применение в индустриальных системах, умных киосках и мобильных терминалах. Анонс новых решений Loongson очень важен для китайского рынка и страны в целом, особенно на фоне санкций со стороны США, не позволяющих КНР использовать решения Intel и AMD в вычислительных системах государственного сектора. Начало массового производства новых многоядерных процессоров Loongson 3C6000 должно если не решить проблему полностью, то заметно сгладить её.

23.06.2025 [09:05], Сергей Карасёв

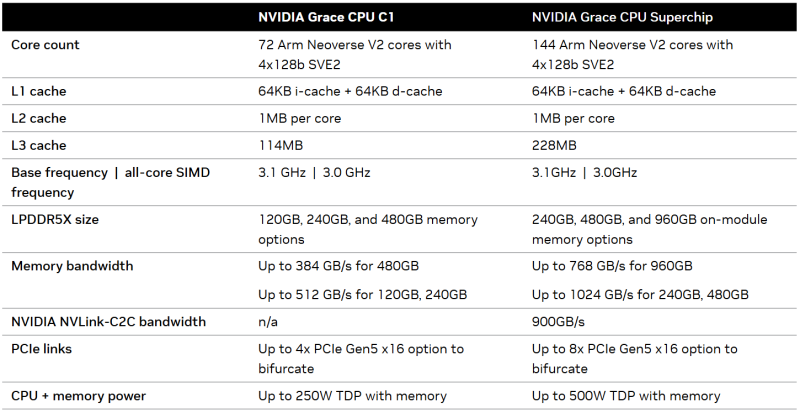

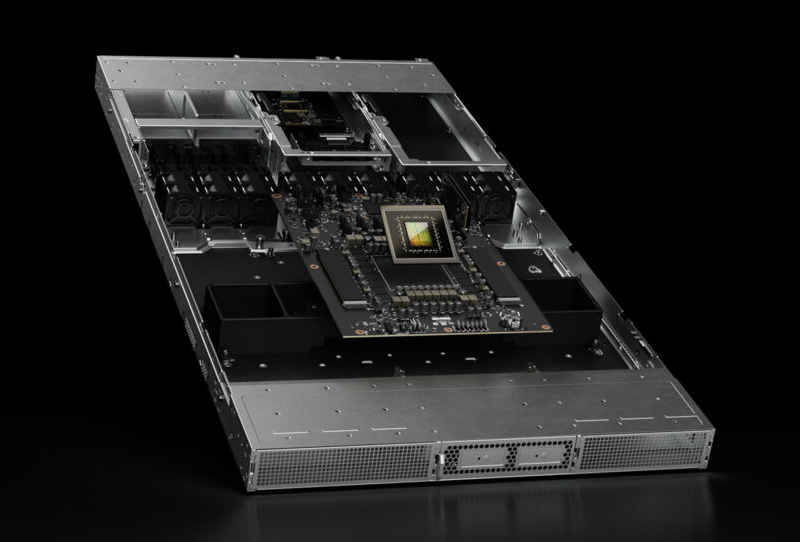

Половинка суперчипа: Arm-процессор NVIDIA Grace C1 набирает популярность в телеком-оборудовании, СХД и на периферииКомпания NVIDIA отметила рост популярности своего Arm-процессора Grace C1 среди ключевых ODM-партнёров. Изделие применяется в телекоммуникационном оборудовании, СХД, периферийных и облачных решениях, а также в других системах, где первостепенное значение имеет показатель производительности в расчёте на ватт затрачиваемой энергии. Архитектура NVIDIA Grace на сегодняшний день представлена в двух основных конфигурациях: это двухпроцессорный Grace Superchip и новый однопроцессорный Grace CPU C1. Последний содержит 72 ядра Arm Neoverse V2 (Armv9) с поддержкой векторных расширений SVE2. Объём кеша L2 составляет 1 Мбайт в расчёте на ядро. Кроме того, есть 114 Мбайт кеша L3. Тактовая частота достигает 3,1 ГГц.

Источник изображения: NVIDIA Процессор Grace CPU C1 функционирует в связке со 120, 240 или 480 Гбайт памяти LPDDR5X, пропускная способность которой достигает 512 Гбайт/с (384 Гбайт/с для варианта 480 Гбайт). Реализована поддержка четырёх массивов PCIe 5.0 x16, что даёт в общей сложности 64 линии (поддерживается бифуркация). Показатель TDP составляет до 250 Вт (вместе с памятью). По заявлениям NVIDIA, системы на базе Grace CPU C1 демонстрируют двукратное повышение производительности на ватт затрачиваемой энергии по сравнению с сопоставимыми по классу продуктами, построенными на чипах с архитектурой х86. Устройства на основе Grace CPU C1 проектируют такие компании, как Foxconn, Jabil, Lanner, MiTAC, Supermicro и QCT. В телекоммуникационной отрасли, как отмечается, востребован компьютер NVIDIA Compact Aerial RAN, объединяющий процессор Grace CPU C1 с ускорителем NVIDIA L4 и адаптером NVIDIA ConnectX-7 SmartNIC. Кроме того, Grace CPU C1 применяется в системах хранения WEKA и Supermicro.

19.06.2025 [11:21], Сергей Карасёв

AWS готовит чип Graviton и ускоритель Trainium следующего поколенияОблачная платформа Amazon Web Services (AWS), по сообщению ресурса CNBC, готовит обновлённую модификацию своего серверного процессора Graviton4, а также ускоритель Trainium следующего поколения, предназначенный для ресурсоёмких приложений ИИ. Оригинальная версия Graviton4 дебютировала в конце 2023 года. Изделие, разработанное подразделением Annapurna Labs в составе AWS, содержит 96 ядер Neoverse V2 Demeter с 2 Мбайт кеша L2 в расчёте на ядро. Используются 12 каналов памяти DDR5-5600. В общей сложности чип насчитывает 73 млрд транзисторов и изготавливается по 4-нм техпроцессу TSMC. По имеющейся информации, у инстансов на базе обновлённой версии Graviton4 пропускная способность сетевой подсистемы увеличится в 12 раз — с нынешних 50 Гбит/с до 600 Гбит/с. Прочие технические характеристики готовящегося изделия не раскрываются, но известно, что информацию о сроках его доступности AWS раскроет до конца текущего месяца. Сообщается также, что ускоритель Trainium следующего поколения выйдет до конца текущего года. Нынешнее решение Trainium2, основанное на ядрах NeuronCore-V3, было представлено в ноябре 2023-го. Его производительность достигает 1,29 Пфлопс в режиме FP8. Утверждается, что быстродействие Trainium3 увеличится в два раза, то есть будет составлять до 2,58 Пфлопс (FP8). Ранее появлялась информация, что энергопотребление Trainium3 может достигать 1000 Вт. Теперь говорится, что в плане энергетической эффективности ИИ-ускоритель нового поколения на 50 % превзойдёт предшественника. Возможно, имеется в виду быстродействие в расчёте на 1 Вт затрачиваемой энергии.

16.06.2025 [09:20], Владимир Мироненко

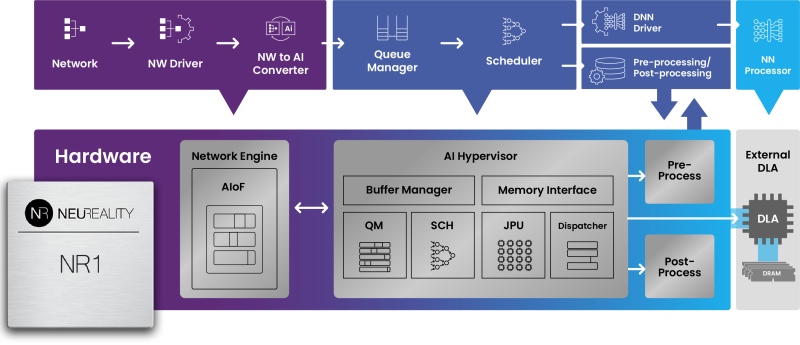

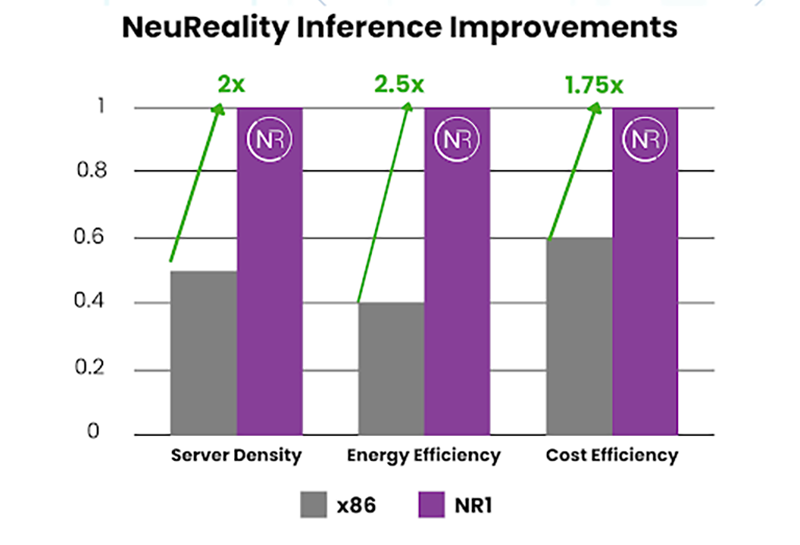

x86 не нужен: «недопроцессор» NeuReality NR1 кратно ускоряет инференс на любых GPUNeuReality объявила о выходе чипа NR1, специально созданного для оркестрации инференса, передаёт HPCwire. Он сочетается с любым GPU или ИИ-ускорителем, позволяя повысить эффективность использование GPU почти до 100 % по сравнению со средним показателем в 30–50 % при традиционном сочетании классического процессора и сетевого адаптера в современных серверах. Чип NR1 призван заменить традиционные CPU и NIC, которые являются узким местом для ИИ-нагрузок, предлагая вместе с тем шестикратное увеличение вычислительной мощности для обеспечения максимальной пропускной способности ускорителей и масштабного ИИ-инференса, утверждает разработчик. Как отметила компания, в течение многих лет разработчики развивали GPU, чтобы соответствовать требованиям ИИ, делая их быстрее и мощнее. Но традиционные CPU, разработанные для эпохи интернета, а не эпохи ИИ, в основном не менялись, становясь узким местом, поскольку ИИ-модели становятся всё более сложными, а запросы ИИ-нагрузок растут в объёме. NR1 включает все базовые функции CPU, необходимые для работы с ИИ-задачами, выделенные обработчики мультимедиа и данных, аппаратный гипервизор и комплексные сетевые IP-блоки, что обеспечивает значительно более высокую производительность, более низкое энергопотребление и окупаемость инвестиций. В тестах самой компании исполнение одной и той же модели на базе генеративного ИИ на одном и том же ИИ-ускорителе её чип NR1 позволяет получить в 6,5 раза больше токенов, чем x86-сервер при той же стоимости и энергопотреблении.  В соответствии с текущей тенденцией на разделение ресурсов хранения и вычислений, дезагрегация ИИ-ресурсов обеспечивает оптимизированную изоляцию ИИ-вычислений, отметила NeuReality. Такое разделение особенно важно в ЦОД и облаках. Традиционные программно-управляемые платформы, ориентированные на CPU, сталкиваются с такими проблемами, как высокая стоимость, энергопотребление и узкие места в системе при обработке задач ИИ-инференса. Сложность современной инфраструктуры и высокая стоимость часто ограничивают использование всех возможностей инференса, утверждает NeuReality. NR1 ориентирован на комплексную разгрузку ИИ-конвейера. Аппаратный ИИ-гипервизор отвечает за обработку путей данных и планирование заданий, охватывая механизмы пред- и постобработки данных, а также сетевой движок AI-over-Fabric. Благодаря этому достигнуто оптимальное соотношение цены и производительности и самые низкие эксплуатационные расходы, характеризующиеся низким энергопотреблением, минимальной задержкой и линейной масштабируемостью, говорит компания. Для DevOps и MLOps компания предоставляет полный SDK и сервисный слой на основе Kubernetes. Новый чип предлагается использовать для решения задач в сфере финансов и страхования, здравоохранении и фармацевтике, госуслугах и образовании, телекоммуникации, ретейле и электронной коммерции, для нагрузок генеративного и агентного ИИ, компьютерного зрения и т.д. NeuReality NR1 включает:

05.06.2025 [14:49], Сергей Карасёв

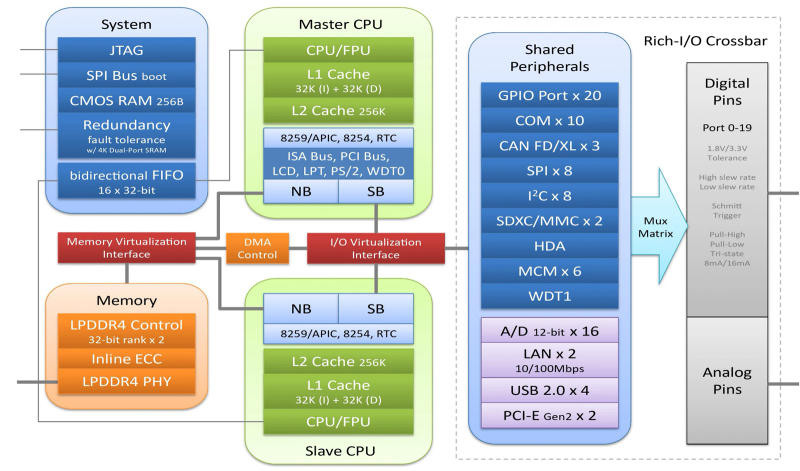

Два ядра, два BIOS, две ОС: DM&P представила x86-процессор Vortex86EX3Тайваньская компания DM&P Electronics, по сообщению ресурса CNX Software, подготовила к выпуску чип Vortex86EX3 — своё самое производительное решение с архитектурой x86. Процессор ориентирован на применение в индустриальной сфере, на что, в частности, указывает его широкий диапазон рабочих температур, который простирается от -40 до +85 °C. Изделие оснащено двумя вычислительными ядрами с тактовой частотой 1,2–1,6 ГГц. Они функционируют в конфигурации Master–Slave с двумя независимыми экземплярами BIOS и возможностью одновременного запуска двух ОС без применения гипервизора и средств виртуализации. Блок Master служит для поддержания работы пользовательского интерфейса и приложений, тогда как блок Slave отвечает за интерфейсы ввода-вывода в реальном времени. Каждое из ядер содержит 256 Кбайт кеша L2, а также по 32 Кбайт L1-кеша команд и данных. Процессор поддерживает работу с памятью LPDDR4 (ЕСС). Есть два интерфейса SD/eMMC, две линии PCIe 2.0, два сетевых интерфейса 10/100MbE и один параллельный порт. Прочие характеристики таковы: 4 × USB 2.0, 10 × COM, 20 × GPIO, 8 × SPI, 8 × I2C, 3 × CAN. Реализованы контроллеры HD-Audio и LCD. Чип выполнен в корпусе BGA (627 контактов) с размерами 17 × 17 мм.

Источник изображения: CNX Software Для новинки заявлена поддержка Windows 10, WinCE 5/6/7, Linux 2.x–6.6, QNX 7.0, RTOS-32, DOS и Yocto Project. Компания DM&P в партнёрстве с ICOP Technology продемонстрировала возможность одновременного запуска на Vortex86EX3 платформ Linux (Debian) и Windows Embedded Compact 7. Процессор может использоваться в том числе в системах автоматизации, функционирующих в реальном времени.

23.05.2025 [15:22], Владимир Мироненко

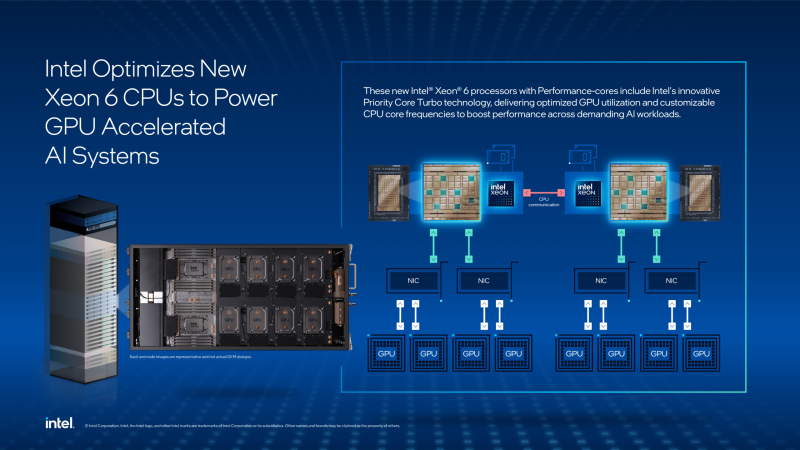

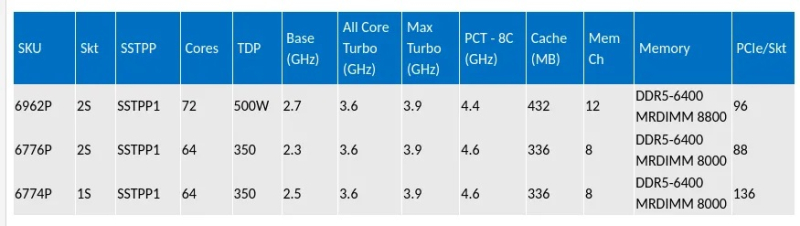

Специально для ИИ: Intel представила три оптимизированных процессора Intel Xeon Granite Rapids, один из которых используется в NVIDIA DGX B300Intel представила три новых процессора семейства Intel Xeon 6 Granite Rapids-SP/AP — 6962P, 6774P и 6776P, разработанные для управления «самыми передовыми ИИ-системами ускорителей». Новые процессоры с P-ядрами используют технологию Intel Priority Core Turbo (PCT), а также технологию Intel Speed Select Turbo Frequency (Intel SST-TF), которые позволяют настраивать частоты ядер процессора для повышения производительности ускорителя при обработке требовательных рабочих ИИ-нагрузок. Новые процессоры Xeon 6 уже доступны для заказчиков. В частности, Intel Xeon 6776P используется в ИИ-системе NVIDIA DGX B300, где «играет важную роль в управлении, оркестрации и поддержке ИИ-системы». «Новые чипы демонстрируют непревзойдённую производительность Xeon 6, что делает их идеальными процессорам для ИИ-систем с ускорением на GPU следующего поколения», — отметила Карин Айбшиц Сигал (Karin Eibschitz Segal), корпоративный вице-президент и временный генеральный директор Intel Data Center Group. Как сообщила Intel, внедрение PCT в сочетании с Intel SST-TF обеспечивает значительный скачок производительности ИИ-систем. PCT позволяет динамически формировать пул высокоприоритетных ядер, которые работают на более высоких турбочастотах, в то время как остальные ядра работают на базовой частоте, обеспечивая оптимальное распределение ресурсов процессора. Эта функция имеет решающее значение для рабочих ИИ-нагрузок, требующих последовательной и пакетной обработки, более быстрой отправки данных к ускорителям и повышения общей эффективности системы. Впрочем, в случае 6776P лишь до восьми ядер могут работать на повышенной турбочастоте. Процессоры Xeon 6 с P-ядрами, по словам Intel обеспечивают ведущие в отрасли характеристики для ИИ-систем, включая:

Новые процессоры отличаются высокой надёжности и удобством обслуживания, что сводит к минимуму перебои в работе. Как сообщается, новинки поддерживают AMX-вычисления с точностью FP16, что обеспечивает эффективную предобработку данных и выполнение критических задач ЦП в рабочих ИИ-нагрузках.

22.05.2025 [23:03], Владимир Мироненко

Qualcomm готовит 80-ядерный серверный Arm-процессор SD1 для ИИ-платформQualcomm провела в рамках выставки Computex 2025 мероприятие, на котором изложила свои планы на ближайшее будущее. Хотя немногим ранее компания подтвердила намерение вернуться на рынок серверных процессоров в подписанном с ИИ-стартапом Humain меморандуме о взаимопонимании, на нынешнем брифинге руководство Qualcomm лишь вскользь затронуло эту тему, уделив ей буквально считанные секунды, пишет ресурс ComputerBase. Вместе с тем на слайде, продемонстрированном в конце мероприятия, было сказано, что продвижение Qualcomm на рынке ЦОД станет следующим шагом по диверсификации компанией своей деятельности. Судя по всему, главным направлением, для которого Qualcomm займётся разработкой серверных чипов, станут ИИ-платформы. ComputerBase отметил, что генеральный директор Qualcomm Криштиану Амон (Cristiano Amon) неоднократно подчёркивал, что в ЦОД уже сейчас используется интеллектуальная собственность компании и её разработки. Лежащая в их основе технология считается «крайне революционной», предлагая высокую производительность чипа при низком энергопотреблении. Напомним, что Nuvia, которую приобрела Qualcomm, планировала выпустить «лучший в мире серверный процессор» с Arm-архитектурой и ядром Phoenix собственной разработки. Из-за этой сделки между Arm и Qualcomm начался серьёзный конфликт. Softbank же, контролирующая Arm, хочет купить производителя серверных Arm-процессоров Ampere Computing. Один из инсайдеров сообщил на платформе X о свежей публикации DigiTimes, согласно которой, Qualcomm «возвращается на рынок серверов на базе Arm-архитектуры», планируя выпустить 5-нм CPU под кодовым названием SD1. По данным издания, чип будет поддерживать память HBM и PCIe 5.0 и предназначен для интеграции со стоечными системами NVIDIA, закладывая основу для энергоэффективной экосистемы CPU+GPU. Новинка получит поддержку NVLink Fusion. Вместе с тем первая информация о процессорах SD1 появилась более года назад. Тогда говорилось, что процессор получит 80 ядер Oryon, работающих на частоте до 3,8 ГГц, 16 каналов DDR5-5600, 70 линий PCIe 5.0 с поддержкой CXL 1.1. Чип будет изготавливаться на TSMC по техпроцессу N5P и получит упаковку LGA9470 (98 × 95 мм). Возможно использование в двухсокетной конфигурации. Тогда же сообщалось, что Qualcomm сообщила своим партнёрам о готовящемся чипе на рубеже 2021-2022 гг., т.е. практически сразу после приобретения Nuvia.

21.05.2025 [09:25], Сергей Карасёв

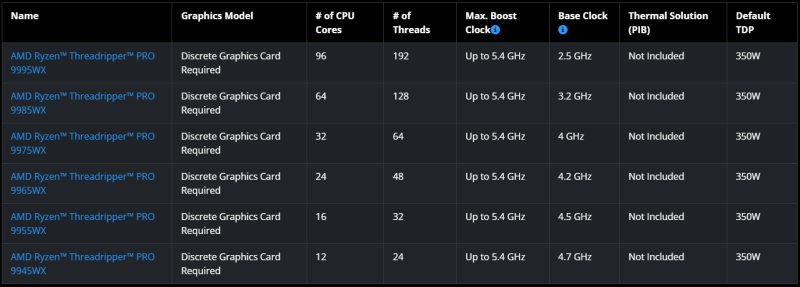

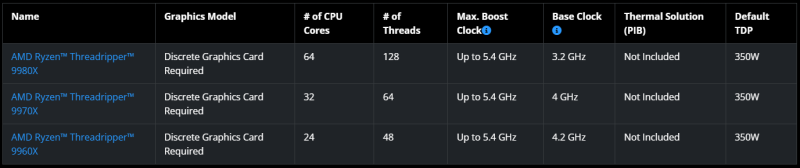

AMD представила процессоры Ryzen Threadripper PRO 9000 WX — до 96 ядер Zen 5 и 8 каналов DDR5-6400 ECCКомпания AMD анонсировала процессоры Ryzen Threadripper PRO 9000 WX и Ryzen Threadripper 9000 для высокопроизводительных рабочих станций, рассчитанных на создание и обучение ИИ-моделей, рендеринг графики, генерацию визуальных эффектов и другие ресурсоёмкие задачи. Новые чипы, известные под кодовым названием Shimada Peak, основаны на микроархитектуре Zen 5. Изделия обеспечивают поддержку до 128 линий PCIe 5.0 (без CXL), а также восьми каналов памяти DDR5-6400 ECC. Обеспечивается совместимость с материнскими платами, оборудованными процессорным разъёмом Socket TR5. Семейство Ryzen Threadripper PRO 9000 WX включает шесть моделей, насчитывающих от 12 до 96 вычислительных ядер с поддержкой SMT2. Максимальная тактовая частота в Boost-режиме у всех этих процессоров достигает 5,4 ГГц, а показатель TDP равен 350 Вт. На вершине серии располагается чип Ryzen Threadripper 9995WX с 96 ядрами (192 потока) и кешем L3 объемом 384 Мбайт. AMD заявляет, что этот процессор обеспечивает прирост производительности на 10–20 % по сравнению с решением предыдущего поколения Ryzen Threadripper PRO 7995WX на архитектуре Zen 4 и почти на 220 % по сравнению с чипом Intel Xeon W9-3595X. В свою очередь, семейство Ryzen Threadripper 9000 представлено тремя изделиями с 24, 32 и 64 ядрами (с поддержкой многопоточности), максимальной частотой 5,4 ГГц и TDP в 350 Вт. Объём кеша L3 равен 256 Мбайт у старшей версии и 128 Мбайт у двух других. Они предлагают лишь четыре канала памяти DDR5-6400 ECC и 88 линий PCIe 5.0. Новые процессоры станут доступны в июле. Системы на их основе будут предлагаться такими производителями, как Dell, HP, Lenovo и Supermicro.

16.05.2025 [17:20], Алексей Степин

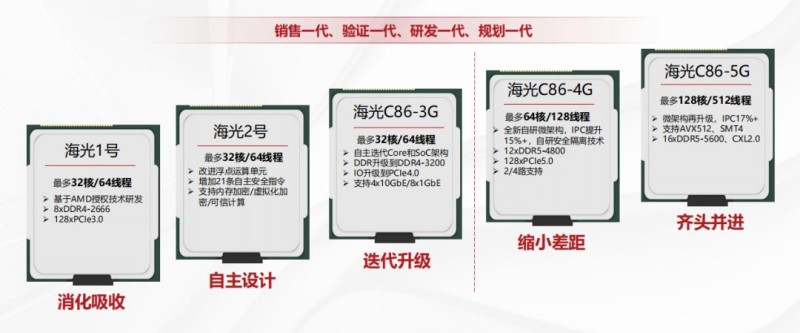

Hygon якобы готова к выпуску 128-ядерного конкурента AMD EPYC с SMT4 и AVX-512Имя Hygon вряд ли легко найти в списке лучших серверных процессоров, однако в своё время этот китайский разработчик смог выпустить в рамках соглашения с AMD серверные чипы Hygon Dhyana, совместимые с платформой Socket SP3. В 2024 году компания похвасталась уже 64-ядерными Hygon C86-7490 для платформы Socket SP5, которые, впрочем, всё равно базировались на архитектуре Zen 1. Но амбиции китайских разработчиков отнюдь не ограничиваются устаревшими архитектурами AMD, передаёт Tom's Hardware. Недавно в социальной сети Twitter (X) был замечен слайд, на котором якобы расписаны планы Hygon в области разработки новых процессоров, и они выглядят впечатляюще. В них фигурирует новый флагман под условным именем C86-5G, способный составить конкуренцию современным многоядерным серверным процессорам Intel и AMD. Этот процессор получит до 128 ядер, причём с поддержкой SMT4, а не привычного для x86-мира SMT2, что даст ему возможность исполнять одновременно до 512 потоков. Некогда аналогичная технология уже применялась Intel в процессорах Xeon Phi Knights Landing. Какая микроархитектура будет стоять за новыми ядрами, пока не разглашается. Заявляется лишь, что это новая фирменная разработка Hygon, а не очередное ответвление AMD EPYC. Заявлено о как минимум 17% прироста производительности в пересчете на такт (IPC). Известно также, что C86-5G получат поддержку AVX-512. 512 потоков нуждаются в быстрой памяти — новые процессоры получат 16-канальный контроллер DDR5-5600, что является серьезным шагом вперёд от 12 каналов DDR5-4800 в предыдущем поколении. Что касается IO-подсистемы, то уже в предыдущем поколении появилась поддержка 128 линий PCI Express 5.0. Вероятнее всего, это станет минимумом для C86-5G и, хотя точных цифр компания нет, отмечается, что в новых процессорах дебютирует полноценная поддержка CXL 2.0.

Hygon C86-7490. Источник: Twitter@YuuKi_AnS Четвёртое поколение серверных чипов Hygon доступно с прошлого года, так что можно предположить, что проектирование C86-5G находится в самом разгаре. Это один из проектов, критически важных для КНР в рамках «тарифной войны» с США и нацеленных на достижение статуса самодостаточности в сфере IT.

16.05.2025 [08:38], Владимир Мироненко

Qualcomm возвращается на рынок серверных процессоровQualcomm Technologies возвращается на рынок серверных процессоров. Это подтверждает меморандум о взаимопонимании, подписанный компанией и ИИ-стартапом Humain, принадлежащим Суверенному фонду Саудовской Аравии, с целью «запуска ИИ ЦОД, предложения гибридного ИИ на периферии и в облаке, а также сервисов “от облака до периферии” в Королевстве Саудовская Аравия и за его пределами». Меморандум о взаимопонимании был подписан в ходе Саудовско-американского инвестиционного форума в Эр-Рияде. Ранее о партнёрстве с Humain объявили NVIDIA, AMD и AWS, а также Cisco. В документе закреплено обязательство Qualcomm «разработать и поставлять современные ИИ-решения и CPU для ЦОД». Также стороны планируют интегрировать семейство арабских больших языковых моделей Humain (ALLaM, совместно разработанных с SDAIA) с широкой экосистемой периферийных ИИ-устройств на базе процессоров Qualcomm, предоставляя возможности гибридного ИИ-инференса от облака до периферии для широкого спектра устройств. В дальнейшем компании будут сотрудничать с Министерством связи и информационных технологий Саудовской Аравии (MCIT) с целью создания в Саудовской Аравии Центра проектирования полупроводниковых технологий мирового класса. Согласно документу, Qualcomm и Humain намерены «разработать и построить передовые ИИ ЦОД в Саудовской Аравии, предназначенные для предоставления высокоэффективных масштабируемых гибридных решений ИИ-инференса от облака до периферии (cloud-to-edge) для местных и международных клиентов на основе решений Qualcomm». Также партнёры планируют ускорить использование инфраструктуры за счет применения процессоров Snapdragon и Dragonwing. Ранее Qualcomm и Cerebras договорились об использовании ускорителей Cloud AI для инференса, в том числе в интересах заказчиков из Саудовской Аравии. Qualcomm и Humain заявили, что их ЦОД и экосистема предназначены для предоставления как государственным, так и корпоративным организациям доступа к высокопроизводительной и энергоэффективной облачной ИИ-инфраструктуре на основе CPU, а также cloud-to-edge сервисам. Согласно пресс-релизу, эти предложения позволят развёртывать ИИ-решения, которые могут делать прогнозы и принимать решения в реальном времени, а также значительно повышать доступность и ценность передовых приложений с поддержкой ИИ.

Источник изображения: Qualcomm Слухи о планируемом Qualcomm возврате к разработке серверных процессоров курсируют длительное время. В 2017 году компания выпустила 10-нм 48-ядерные чипы Centriq 2400, но затем отменила проект в 2019 году. Позже компания приобрела стартап Nuvia, который разрабатывал серверные Arm-процессоры. Qualcomm использовала наработки Nuvia в процессорах Snapdragon для компьютеров на базе Windows. Слухи разгорелись с новой силой, когда в начале года Qualcomm наняла Сайлеша Коттапалли (Sailesh Kottapalli) в качестве старшего вице-президента. Ранее он был главным архитектором серверных процессоров Xeon. Теперь Qualcomm не скрывает своих намерений. Она разместила на сайте вакансии, связанные с разработкой серверных процессоров, включая «архитектора управления питанием сервера», «архитектора ПО для управления питанием и температурой серверных SoC» и «архитектора серверной платформы». Причём, как отметил ресурс Computer Base, каждая вакансия сопровождается примечанием: «Команда Qualcomm Data Center разрабатывает высокопроизводительное и энергоэффективное серверное решение для ЦОД». На форуме JPMorgan финансовый директор и главный операционный директор Акаш Палхивала (Akash Palkhiwala) заявил, что у компании есть «ведущий в мире процессор» и NPU. «Изменения, которые происходят в ЦОД, очевидно, связаны с переходом к инференсу, который становится всё более важным, как и низкое энергопотребления, и именно здесь Qualcomm на высоте», — отметил Палхивала, добавив, что компания использует имеющиеся технологии в будущих серверных процессорах. |

|