Материалы по тегу: cpu

|

24.08.2025 [23:18], Сергей Карасёв

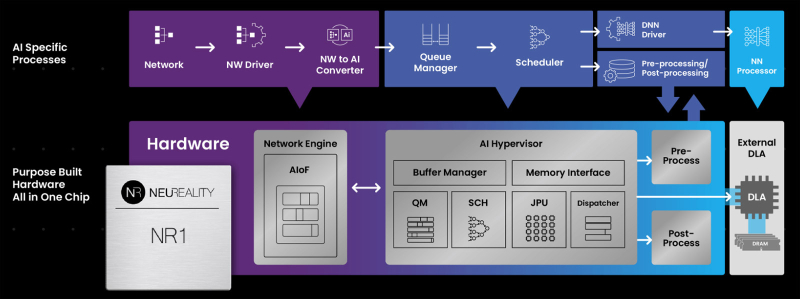

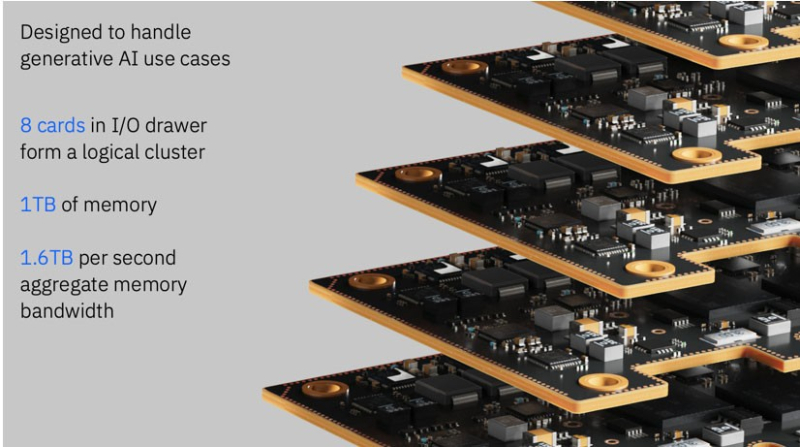

NeuReality готовит чип NR2 для оркестрации инференсаКомпания NeuReality раскрыла предварительную информацию об изделии NR2 — чипе второго поколения, предназначенном специально для оркестрации инференса. Изделие представляет собой более эффективную альтернативу связке CPU и NIC в высокопроизводительных системах ИИ. Чип первого поколения NR1 дебютировал в июне нынешнего года. Изделие может применяться в связке с любым GPU или ИИ-ускорителем. При этом, как утверждается, NR1 позволяет повысить эффективность использования GPU почти до 100 % по сравнению со средним показателем в 30–50 % при традиционном сочетании CPU и NIC в современных серверах. В состав NR1 входят четыре декодера видео/изображений, 16 DSP для аудио/речи, 16 векторных DSP общего назначения, два порта 10/25/50/100GbE и пр. Характеристики NR2 на данный момент полностью не раскрываются. Известно, что в основу решения положена платформа Arm Neoverse Compute Subsystems (CSS) V3. Чип может объединять до 128 ядер, оптимизированных для масштабных рабочих нагрузок обучения моделей ИИ и инференса. По сравнению с оригинальной версией в NR2 реализована более глубокая интеграция между CPU-блоком и NIC для координации ИИ-моделей в реальном времени, дезагрегации на основе микросервисов, потоковой передачи токенов, оптимизации KV-кеша и оркестровки. В целом, как отмечает NeuReality, чипы серии NR представляют собой качественно новый класс изделий, способных управлять рабочими нагрузками инференса с непревзойдённой эффективностью. Гипервизор ИИ в сочетании с ядрами Arm Neoverse обеспечивает оптимальную оркестровку и максимальную загрузку доступных ресурсов.

14.08.2025 [13:36], Сергей Карасёв

Китайский разработчик POWER-процессоров Hexin Technology обанкротилсяКитайская компания Hexin Technology, занимающаяся проектированием серверных процессоров, подала заявление о банкротстве. В документации Народного суда промежуточной инстанции Гуанчжоу провинции Гуандун говорится, что разработчик чипов столкнулся с неплатёжеспособностью: он не в состоянии погасить просроченные долги, а имеющихся активов недостаточно для покрытия обязательств. Hexin Technology, первоначально называвшаяся Zhongsheng Hongxin, основана в 2014 году ведущими специалистами Китайской академии наук (CAS) и IBM. Штаб-квартира компании находится в Гуанчжоу, а научно-исследовательские центры — в Сучжоу, Пекине, Шанхае и Шэньчжэне. Совместно с Университетом Цинхуа (Tsinghua University) фирма основала научно-исследовательский институт по производству серверных чипов. Кроме того, в районе Гуанчжоу была сформирована инновационная научно-исследовательская площадка.

Источник изображения: Jiwei.com Hexin Technology создаёт чипы на архитектуре набора команд (ISA) POWER корпорации IBM в рамках инициативы OpenPOWER. В частности, в конце 2023 года был представлен тестовый чип второго поколения (Test Chip 2, TC2) в рамках проекта по разработке серверного процессора HX-C2000. Отмечается, что в течение 2023-го компания получила 61 патент и подала в общей сложности 347 новых патентных заявок. Однако после этого у Hexin Technology возникли финансовые сложности. В июне 2024 года фирма проинформировала сотрудников о задержке выплаты зарплат за несколько месяцев. В сентябре того же года компания сообщила о сокращении жалования на 30 % и обратилась к сотрудникам с предложением «добровольного» отказа от социального страхования и накопительных выплат. А в ноябре появилась информация о том, что Hexin Technology близка к сворачиванию деятельности. Более 500 сотрудников предприятия подали коллективный иск в трудовой арбитраж для защиты своих прав, поскольку руководство компании не выходит на связь с работниками и не реагирует на их запросы.

05.08.2025 [11:16], Сергей Карасёв

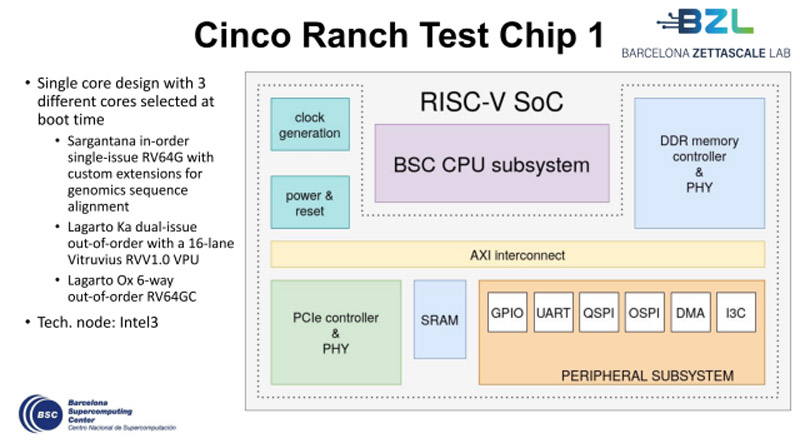

Европейские чипы Cinco Ranch на базе RISC-V близки к началу массового производстваУчастники проекта Barcelona Zettascale Laboratory (BZL), координируемого Барселонским суперкомпьютерным центром (BSC) в Испании, по сообщению ресурса EETimes, достигли фазы Tape-out в рамках разработки европейских процессоров Cinco Ranch на открытой архитектуре RISC-V. Tape-out — это финальная стадия проектирования интегральных схем или печатных плат перед их отправкой в производство. Данный процесс предполагает перенос цифрового макета чипа на фотошаблон для последующего изготовления. Производством изделий займётся предприятие Intel Foundry с применением техпроцесса Intel 3. Cinco Ranch представляет собой пятое поколение чипов серии Lagarto. По сути, это «система на кристалле» (SoC) промышленного класса с высокой энергетической эффективностью. Конструкция чипа включает три отдельных специализированных ядра, каждое из которых оптимизировано под определённые вычислительные задачи. В частности, присутствует ядро Sargantana (RV64G) с однопоточным выполнением инструкций по порядку. Кроме того, имеется двухпоточное ядро Lagarto Ka с внеочередным исполнением машинных инструкций. Довершает картину высокопроизводительное 6-поточное ядро Lagarto Ox (RV64GC) с внеочередным исполнением инструкций. Нужное ядро выбирается в момент загрузки системы.

Источник изображения: BSC Решение Cinco Ranch содержит 16-канальный векторный блок Vitruvius++ VPU и трёхуровневую систему кеша. Реализована поддержка памяти DDR5 и интерфейса PCIe 3.0. Площадь чипа составляет 16 мм2. Главной целью проекта BZL является разработка суверенных суперкомпьютерных технологий в Европе. Предполагается, что создаваемые чипы найдут применение в различных областях, включая НРС-платформы, автономные транспортные средства, системы ИИ и пр. После всестороннего тестирования чипов Cinco Ranch будет освоено их массовое производство.

30.07.2025 [13:26], Сергей Карасёв

Представлен китайский серверный процессор Zhaoxin KH-50000: до 96 ядер, 12 каналов DDR5 и 128 линий PCIe 5.0Китайская компания Zhaoxin анонсировала серверный x86-совместимый процессор нового поколения KH-50000. Изделие может применяться в том числе в ИИ-системах с высокой плотностью компоновки. Новинка, выполненная на основе чиплетной архитектуры, приходит на смену решению KH-40000. Чипы семейства KH-40000 насчитывают до 32 вычислительных ядер (без поддержки многопоточности), располагают 64 Мбайт кеша, 8 каналами памяти DDR4 и 128 линиями PCIe 4.0. Тактовая частота достигает 2,5 ГГц. Задействован интерконнект ZPI 3.0 Новый процессор KH-50000 содержит до 96 ядер (о поддержке многопоточности информации нет), а максимальная тактовая частота составляет 3 ГГц. Объём кеша достигает 384 Мбайт. Реализована поддержка 12 каналов DDR5 и 128 линий PCIe 5.0. Применяется интерконнект ZPI 5.0, который обеспечивает более высокую пропускную способность при одновременном снижении задержки и энергопотребления. Среди прочего упомянуты 16 линий PCIe 4.0 / SATA / USB. Новый серверный процессор продемонстрирован на Всемирной конференции по искусственному интеллекту (WAIC) в Шанхае (Китай). На базе KH-50000 могут создаваться четырёхсокетные системы, тогда как чип предыдущего поколения KH-40000 позволял формировать только одно- и двухсокетные машины. В целом, как отмечают наблюдатели, в конструктивном плане изделие KH-50000 схоже с процессорами AMD EPYC поколения Bergamo. Предполагается, что появление чипа поможет Китаю в сокращении зависимости от продукции зарубежных поставщиков.

19.07.2025 [13:39], Сергей Карасёв

Rockchip представила 10-ядерный Arm-процессор RK3668 с ИИ-модулемКомпания Rockchip, как сообщает ресурс CNX Software, процессор RK3668 на архитектуре Arm, предназначенный для создания одноплатных компьютеров и других устройств с ИИ-функциями. Изделие насчитывает 10 вычислительных ядер в конфигурации 4 × Arm Cortex-A730 и 6 × Arm Cortex-A530 (Armv9.3). Причём на сегодняшний день эти ядра официально не представлены. В состав чипа входят графический процессор Arm Magni с производительностью до 1–1,5 Тфлопс и блок VPU с возможностью декодирования материалов в формате 8K (60 к/с). Новинка располагает интегрированным нейропроцессорным модулем (NPU) с быстродействием до 16 TOPS для ускорения ИИ-операций. Процессор изображений (ISP) с ИИ-функциями поддерживает работу с видео 8K (30 к/с). Реализованы четыре канала оперативной памяти LPDDR5/5x/6 с пропускной способностью до 100 Гбайт/с. Возможно использование флеш-накопителей UFS 4.0. Поддерживаются интерфейсы HDMI 2.1 (до 8K / 60 к/с), MIPI DSI, PCIe, UCIe. Производственные нормы — 5–6 нм. Кроме того, Rockchip раскрыла дополнительную информацию о чипе RK3688, первые упоминания которого появились в октябре 2024 года. Это изделие объединяет 12 вычислительных ядер в конфигурации 8 × Arm Cortex-A730 и 4 × Arm Cortex-A530. Пропускная способность памяти LPDDR6 достигает 200 Гбайт/с. Возможно декодирование видеоматериалов 16Kp30 и кодирование 8Kp60. Производительность встроенного NPU-блока повышена до 32 TOPS. Этот процессор будет изготавливаться по технологии 4–5 нм. Одной из первых компаний, которая возьмёт на вооружение новые чипы, станет Radxa: она, в частности, готовит одноплатный компьютер Rock 6 на основе RK3668.

10.07.2025 [15:49], Владимир Мироненко

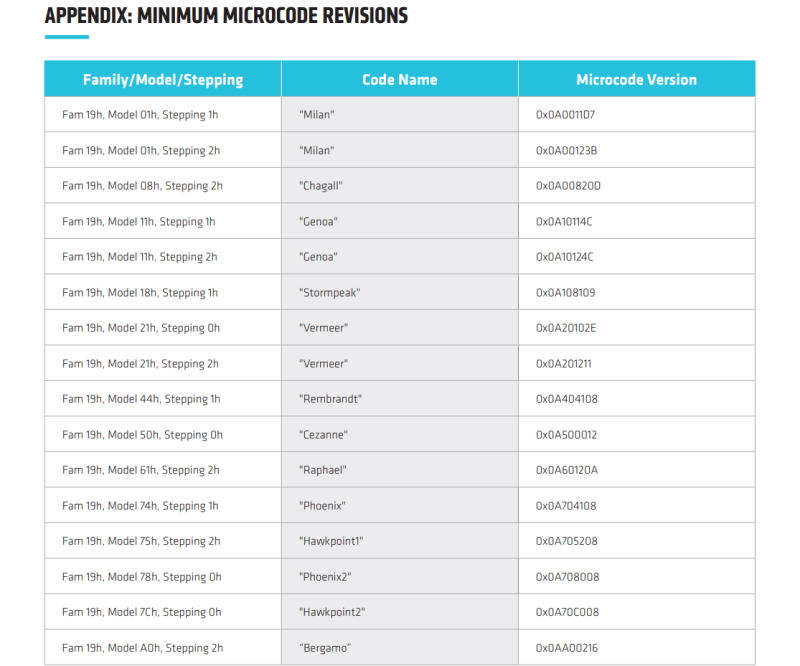

В процессорах AMD найдены уязвимости TSA, похожие на Meltdown и SpectreAMD сообщила об обнаружении нового класса микроархитектурных атак на свои процессоры — TSA (Transient Scheduler Attack). TSA подобны Meltdown и Spectre и затрагивают широкий спектр CPU AMD и способны привести к раскрытию информации. TSA включает сразу четыре уязвимости, которые были обнаружены исследователями Microsoft и Швейцарской высшей технической школы Цюриха (ETH Zurich). Две из них имеют средний уровень (medium severity) опасности, две — низкий уровень (Low severity). Несмотря на это Trend Micro и CrowdStrike оценили угрозу как «критическую», пишет ресурс The Register. Низкие оценки серьёзности объясняются высокой сложностью выполнения успешной атаки. AMD заявила, что её может осуществить только злоумышленник, способный запустить произвольный код на целевой машине, получив доступ через вредоносное ПО или вредоносную виртуальную машину, но для успешного выполнения атак требуются лишь низкие привилегии. Как утверждает AMD, TSA невозможно эксплуатировать через вредоносные веб-сайты, а для надёжного извлечения данных потребуется многократный запуск. Это связано с тем, что атака основана на использовании состояния «ложного завершения» (false completion), которое возникает, когда процессор ожидает быстрого завершения исполнения инструкций загрузки, но какое-либо условие препятствует их успешному завершению. В результате происходит повторная загрузка данных и выполнение зависимых операций, но из-за особенностей чипов «анализ времени выполнения может использоваться как источник утечки информации из микроархитектурных структур, оставшейся после спекулятивного выполнения других операций», — сообщил ресурс OpenNet. При использовании двух уязвимостей средней степени серьёзности успешные атаки на чипы AMD могут привести к утечке информации из ядра ОС. В других сценариях утечка данных может произойти также из приложений или виртуальных машин. Доступ к данным ядра потенциально может позволить злоумышленникам повысить привилегии, обойти механизмы безопасности, обеспечить персистентность и т.д. Баги низкого уровня могут привести к утечке внутренних данных о работе процессора, которые AMD не считает конфиденциальными.

Источник: AMD AMD заявила о двух различных вариантах TSA, которые могут быть реализованы на её чипах в зависимости от источника извлечения данных — TSA-SQ и TSA-L1.

Согласно технической документации AMD, уязвимости TSA-L1 вызваны ошибкой в использовании микротегов кешем L1 для поиска. Процессор может полагать, что данные находятся в кеше, хотя на самом деле это не так, что приводит к загрузке неверных данных, которые злоумышленник может затем вывести. Уязвимости TSA-SQ возникают, когда инструкция загрузки ошибочно извлекает данные из Store Queue, когда необходимые данные недоступны. В этом случае злоумышленник может обнаружить неверные данные и использовать их для извлечения информации, например, из ядра ОС, из ранее загруженных данных, даже если они выполнялись в другом контексте. Уязвимости проявляются в семействе процессоров AMD на базе микроархитектур Zen 3 и Zen 4, в том числе, в сериях Ryzen 5000/6000/7000/8000, EPYC Milan/Milan-X/Genoa/Genoa-X/Bergamo/Siena, Instinct MI300A, AMD Ryzen Threadripper PRO 7000 WX, EPYC Embedded 7003/8004/9004/97X4, Ryzen Embedded 5000/7000/V3000. В целом обновление микрокода и PI-прошивок (Platform Initialization) необходимо для чипов серий EPYC, Ryzen, Instinct.

09.07.2025 [14:35], Владимир Мироненко

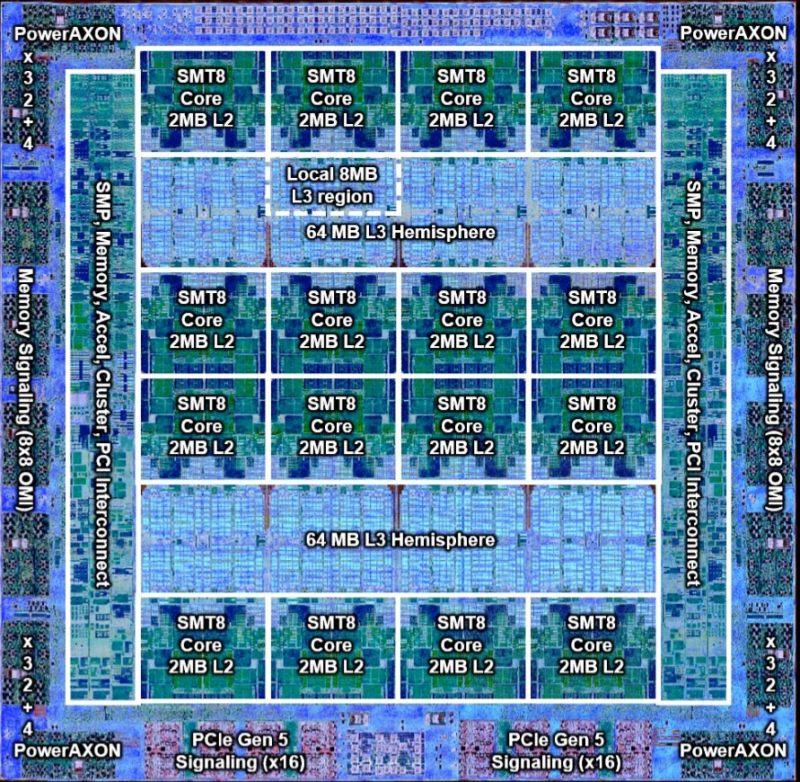

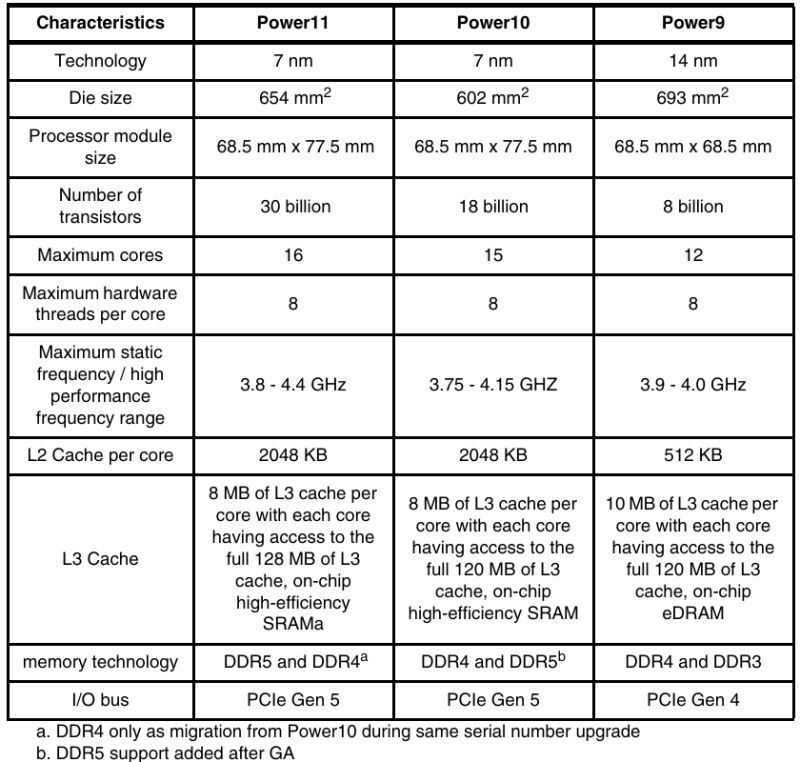

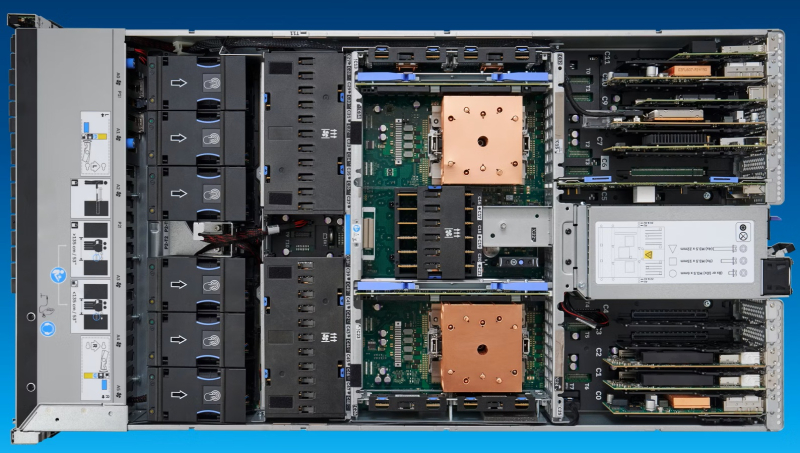

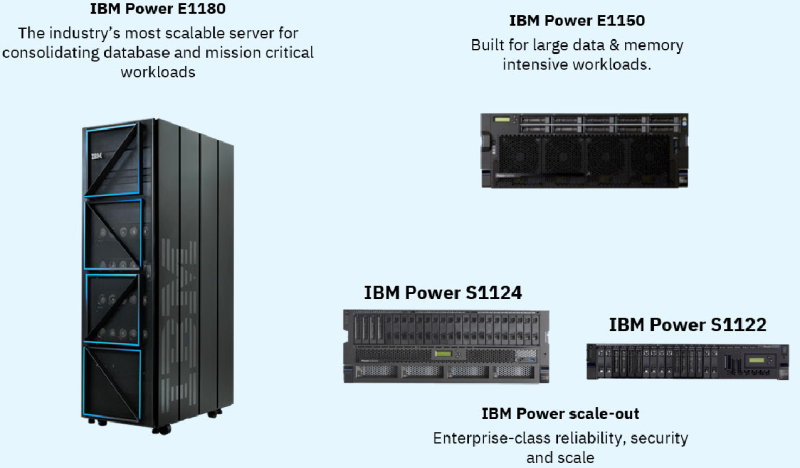

256 ядер, 2048 потоков и 64 Тбайт DDR5: IBM анонсировала «бесперебойные» серверы POWER11IBM представила серверы POWER11, получившие усовершенствованные процессоры, аппаратную архитектуру и программный стек виртуализации. Как заявила компания, POWER11 разработаны для обеспечения доступности, отказоустойчивости, производительности и масштабируемости, которые требуются предприятиям для бесшовного гибридного развёртывания on-premise или в облаке IBM Cloud. POWER11 представляет собой самый отказоустойчивый сервер в истории платформы IBM POWER с доступностью на уровне 99,9999 %, заявляет компания. Вместе с нулевым запланированным простоем для обслуживания системы и менее чем одной минутой гарантированного обнаружения угроз программ-вымогателей с помощью IBM POWER Cyber Vault, POWER11 устанавливает новую планку непрерывности ведения бизнеса, говорит IBM. Впервые общедоступная версия POWER11 будет одновременно включать высокопроизводительные серверы, модели среднего и начального уровня, а также решение IBM POWER Virtual Server (POWERVS) в IBM Cloud, обеспечивающее быстрый доступ в облако для рабочих нагрузок POWER и сертифицированное как гипермасштабируемая платформа для пакета RISE with SAP. POWER11 также является первым сервером семейства IBM POWER, поддерживающим 32-ядерные 5-нм ИИ-ускорители IBM Spyre Accelerator, которые будут доступны в IV квартале 2025 года. Они же используются в семействе мейнфреймов IBM z17. Процессор POWER11 изготавливается по 7-нм техпроцессу Samsung с использованием 18 слоёв металла и 2.5D-упаковки. Чип состоит из 30 млрд транзисторов, площадь кристалла, как и у предшественника, составляет 602 мм2. Процессор имеет 16 вычислительных ядер с поддержкой SMT8 15. Каждое ядро получило четыре блока MMA (Matrix Math Accelerator) для задач инференса. Как отмечает IT Jungle, в отличие от POWER10, 16-е ядро теперь является запасным, и может быть активировано в случае нештатной ситуации. Объём кеша L2 составляет 2 Мбайт на ядро, объём кеша L3 — 8 Мбайт на ядро, но суммарный объём L3 — до 120 Мбайт. Интерфейс POWERAXON/OMI обеспечивает пропускную способность до 2 Тбайт/с (32 ГТ/с). Возможна установка до 64 Тбайт DDR5 в модулях DDIMM, но в некоторых случаях осталась поддержка DDR4. Доступны 64 линии PCIe 5.0 и SMP-соединение для объединения до 16 сокетов. Для расширения доступны дисковые полки (24 × NVMe) и шасси с PCIe-слотами. Для обеспечения гибкости и масштабируемости POWER11 использует разные способы упаковки. Для высокопроизводительного сервера POWER E1180 задействован одночиповый вариант Single Chip Module (SCM), который обеспечивает один чип на сокет и до шестнадцати сокетов на систему. Для сервера среднего уровня POWER E1150 использовалась упаковка с двумя чипами на сокет Dual Chip Module (DCM) с поддержкой до четырёх сокетов на систему. Версия DCM также используется в линейке масштабируемых серверов POWER S1122/L1122 и POWER S1124/L1124 с двумя сокетами на систему. Также есть третий вариант упаковки — Single Core Module (eSCM), который используется для систем начального уровня POWER S1122 (4 или 10 ядер). POWER11 обеспечивает до 55 % более высокую производительность ядер по сравнению с POWER9 и до 45 % большую ёмкость с большим количеством ядер в системах начального и среднего уровня по сравнению с POWER10. Благодаря этому с POWER11 предприятия получат повышенную гибкость и безопасность, что повысит эффективность корпоративных процессов за счёт автоматизации, говорит IBM. Нулевой запланированный простой для обслуживания системы. POWER11 позволяет избежать дорогостоящего запланированного простоя и помочь снизить операционный риск. Благодаря использованию таких технологий, как автономное исправление и автоматизированное перемещение нагрузок, запланированные события по обслуживанию системы могут происходить без остановки критически важных приложений. Кроме того, IBM POWER будет взаимодействовать с IBM Concert, используя генеративный ИИ, чтобы помочь выявить операционные риски и автоматизировать их исправление, в том числе в области безопасности. Обнаружение угроз программ-вымогателей менее чем за минуту достигается с помощью IBM POWER Cyber Vault, интегрированного решения по обеспечению киберустойчивости, которое соответствует стандартам NIST. Cyber Vault умеет идентифицировать и автоматически реагировать на киберугрозы, защищая от кибератак, таких как повреждение данных и шифрование, с помощью проактивных неизменяемых снимков, которые автоматически создаются, сохраняются и тестируются по заданному пользователем расписанию. POWER 11 также использует одобренную NIST встроенную квантово-безопасную криптографию, предназначенную для защиты систем от атак с отложенной расшифровкой (HNDL) и атак на целостность встроенного ПО. IBM также отметила, что POWER11 обеспечивает значительный рост эффективности во всём ИТ-стеке. С точки зрения энергоэффективности POWER11 предлагает вдвое большую производительность на Вт (SPECint2017_rate) по сравнению с сопоставимыми x86-серверами — до двух раз в случае Intel Xeon Emerald Rapids. Кроме того, теперь разница в энергопотреблении между режимами максимальной производительности и режимом энергосбережения достигает 28 %, при этом пропускная способность падает всего на 6 %. Как утверждает ресурс StorageReview.com, этот режим будет полезен для сред разработки и тестирования с интенсивной загрузкой CPU. Вариант с прямым жидкостным охлаждением поддерживает 75 кВт на стойку (64 сокета в 42U), по сравнению с примерно 28 кВт для аналогичных x86-систем с воздушным охлаждением. Ожидается, что серверы IBM POWER11 — POWER E1180 (до 256 ядер, до 64 Тбайт DDR5), POWER E1150 (до 120 ядер, до 16 Тбайт DDR5), POWER S1124 (до 60 ядер, до 8 Тбайт DDR5) и POWER S1122 (до 60 ядер, до 4 Тбайт DDR5) поступят в продажу 25 июля.

04.07.2025 [19:50], Владимир Мироненко

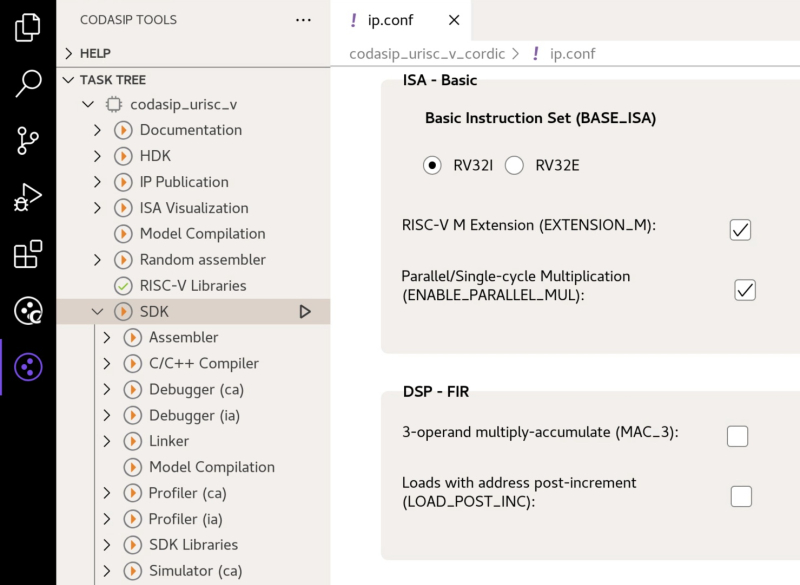

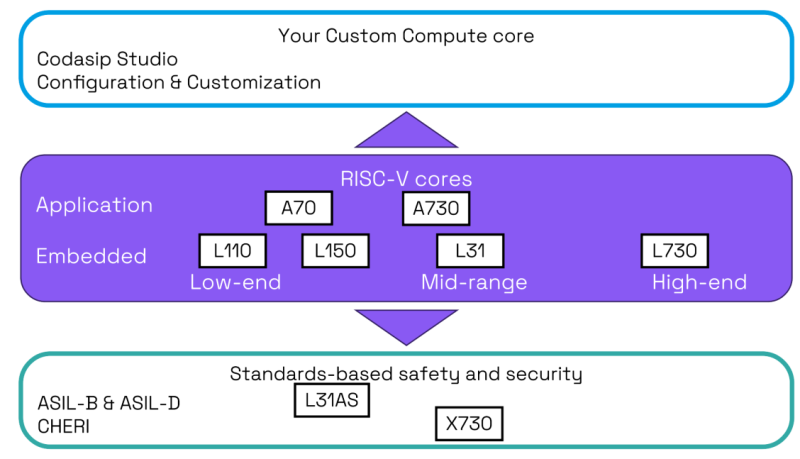

Разработчик RISC-V-чипов Codasip готов продаться — целиком или по частямРазработчик чипов с архитектурой RISC-V и инструментов проектирования из Мюнхена Codasip объявил о готовности продать свои активы, сославшись на проявление к ним интереса со стороны компаний во время недавнего раунда финансирования. Компания сообщила, что процесс приёма заявок на покупку, начавшийся 1 июля, продлится три месяца, что, по мнению ресурса The Register, может указывать на уже поступившие предложения. Ландшафт открытой архитектуры RISC-V превращается из экосистемы сотрудничества в высококонкурентную коммерческую среду, отметил ресурс EE Times. На фоне этого один из основных поставщиков EDA-инструментов Synopsys запустил полный набор основных IP-блоков RISC-V. Попутно крупные игроки рынка полупроводников, такие как Bosch, Infineon, NXP, Qualcomm и Nordic Semiconductor, сформировали консорциум Quintauris для разработки собственных процессорных решений для автомобильного сектора. В связи с этим Codasip попала в сложное положение, оказавшись между гигантами, предлагающими интегрированные решения, и крупными вертикальными игроками, разрабатывающими собственные продукты на базе RISC-V, что потенциально может сократить её целевой рынок. Codasip сообщила, что у неё есть несколько бизнес-подразделений, нацеленных на четыре ключевых направления продуктов, с «отделимыми» R&D-командами, намекая таким образом, что можно купить отдельные группы, а не компанию целиком.

Источник изображений: Codasip Как пишет The Register, у Codasip предполагаемая годовая выручка составляет $88,7 млн, что делает её одним из крупнейших разработчиков микросхем в экосистеме RISC-V. У Ventana Micro Systems предполагаемая выручка составляет $37,4 млн за год, а SiFive ожидала получить около $60 млн в прошлом году. Хотя RISC-V вызывает определённый интерес, предлагая открытый набор инструкций, лёгких путей для построения успешного бизнеса здесь не обещают — SiFive ранее уволила 20 % штата, Intel отказалась от программы Pathfinder for RISC-V, а Imagination Technologies отказалась от RISC-V, сосредоточившись на продуктах GPU и ИИ. У Codasip есть портфолио решений для прикладных и встраиваемых процессоров и портфолио процессоров с архитектурой безопасности CHERI с аппаратной защитой памяти, а также сопутствующее ПО. Отдельно разрабатываются высокопроизводительные прикладные процессоры в рамках проекта Евросоюза Digital Autonomy with RISC-V in Europe (DARE). Наконец, у компании есть и собственные EDA-инструменты для разработки и кастомизации чипов. Немалую часть средств компании приносят гранты от различных органов ЕС, многочисленных общеевропейских и национальных проектов, включая DARE, TRISTAN и NEUROKIT2E — более €119 млн ($140 млн). Однако большая часть этих денег пока не получена компанией. На следующих этапах грантовой поддержки компания может получить ещё €210 млн ($248 млн). Codasip также утверждает, что является частью новых консорциумов и проектов, которые могут принести ей финансирование в размере €51 млн ($60) или больше. По словам компании, эти средства могут быть переданы покупателю на разумных условиях. «В первую очередь, быть разработчиком CPU — это дорогостоящий бизнес, поэтому долгосрочное финансирование имеет важное значение — если рыночное признание низкое, доходы не появятся немедленно», — отметил Эндрю Басс (Andrew Buss), старший директор по исследованиям IDC в регионе EMEA. По оценкам EE Times, потенциальные приобретатели Codasip делятся на три категории. Первая включает гигантов в сфере EDA и интеллектуальной собственности (IP), таких как Synopsys, для которой приобретение Codasip означает возможность консолидации рынка благодаря получению уникального набора инструментов Codasip Studio, расширению портфеля интеллектуальной собственности и устранению значительного конкурента. Вторая категория состоит из вертикальных интеграторов, в основном американских технологических титанов, таких как Intel, Qualcomm и Broadcom. Intel уже предлагала в 2021 году более $2 млрд за SiFive, но сделка не состоялась. Приобретение Codasip даст Intel зрелый портфель интеллектуальной собственности для клиентов Intel Foundry Services (IFS), а также надёжную, отличающуюся от x86 архитектуру для собственных продуктов. Для Qualcomm, судящейся с Arm, сделка означала бы снижение зависимости от архитектуры Arm. Сертифицированные IP-блоки для автомобильных решений Codasip идеально соответствует роли Qualcomm в качестве соучредителя в Quintauris, пишет EE Times. Broadcom может быть интересен набор Codasip Custom Compute, который она могла бы использовать для внутренних ядер контроллеров в SoC. Хотя вероятность заявки от Broadcom довольно низкая. И, наконец, третья категория — организации ЕС, которые могли бы купить Codasip для потенциального европейского консорциума. Европейский союз сделал технологический суверенитет центральной политической целью, что очевидно на примере таких инициатив, как «Европейский закон о чипах» (European Chips Act). Для Евросоюза покупка является стратегической: не допустить приобретения неевропейской организацией критически важного европейского технологического актива, в значительной степени субсидируемого за счет средств ЕС. Покупатель из страны, не входящей в ЕС, должен будет предоставить твёрдые, юридически обязывающие обязательства по поддержанию и развитию европейских центров НИОКР Codasip, обеспечению постоянного участия в стратегических проектах ЕС и в целом соответствию технологической повестке ЕС, подчеркнул EE Times.

02.07.2025 [08:35], Руслан Авдеев

Arm-чипы захватывают рынок, но до доминирования в ЦОД им пока далекоСерверы на базе Arm-чипов стремительно набирают популярность — в 2025 году их поставки должны вырасти на 70 %. Тем не менее, этого не хвататит, чтобы к концу года добиться планируемого Arm Holdings охвата рынка в 50 %, сообщает The Register. Аналитики IDC утверждают, что Arm-серверы пользуются массовым спросом в основном благодаря стоечным системам вроде NVIDIA GB200 NVL72. В новейшем отчёте Worldwide Quarterly Server Tracker эксперты IDC подсчитали, что в текущем году на Arm-серверы придётся 21,1 % от общего объёма мировых поставок. Ожидается, что поставки серверов с хотя бы одним ИИ-ускорителем вырастут на 46,7 %, на них придётся в текущем году около половины рыночной стоимости. Всего за три года, по оценкам IDC, рынок серверов должен вырасти втрое благодаря гиперскейлерам и облачным провайдерам. В целом рынок серверов достиг в I квартале 2025 года $95,2 млрд, увеличившись год к году на 134,1 %. В результате IDC повысила прогноз на год до $366 млрд, на 44,6 % выше год к году — исторический максимум для данного сегмента. При этом поставки «стандартных» x86-серверов должны вырасти в 2025 году на 39,9 % до $283,9 млрд. При этом доля AMD непрерывно растёт. Сегмент альтернативных систем вырастет на 63,7 % год к году, а их общий прогнозируемый объём составит $82 млрд. По прогнозам IDC, наибольший рост, на 59,7 % год к году ожидается в США. К концу 2025 года на данный рынок будет приходиться почти 62 % общей выручки от продаж серверов. Ещё одной точкой роста является Китай. IDC прогнозирует рост на 39,5 % — более 21 % квартального дохода во всём мире. Регионы EMEA и Латинская Америка могут рассчитывать на 7 % и 0,7 % соответственно, а Канаду, вероятно, ожидает спад на 9,6 % из-за некой «очень крупной сделки» 2024 года. В IDC подчёркивают, что спрос на большие вычислительные мощности для ИИ, вероятно, сохранится — эволюция от старых чат-ботов к рассуждающим моделям и агентному ИИ потребует роста производительности на несколько порядков, особенно для инференса.

27.06.2025 [23:45], Владимир Мироненко

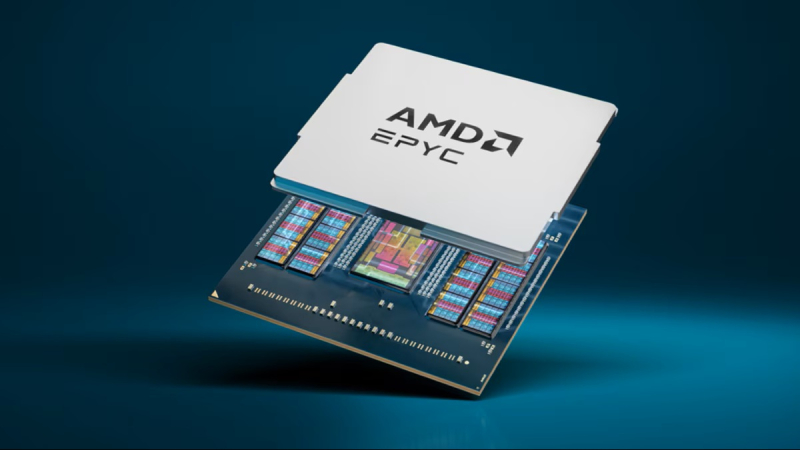

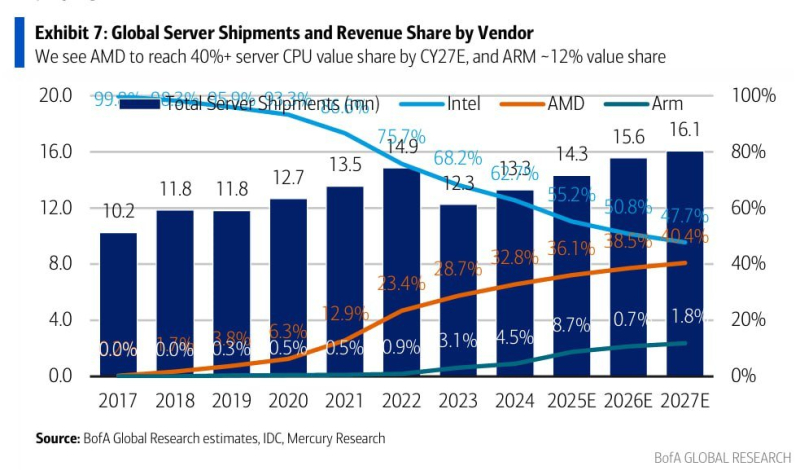

Intel скоро «догонит» AMD по доле рынка серверных процессоровУспехи AMD в разработке серверных процессоров EPYC на фоне проблем Intel с запуском некоторых поколений Xeon привели к постоянному росту в последние годы доли рынка серверных процессоров AMD, причём как по количеству единиц, так и по выручке, пишет ресурс HardwareLuxx. Впрочем, и AMD, и Intel уже угрожает Arm. В последнем отчёте Bank of America отмечается, что если в 2017 году доля рынка Intel составляла почти 100 %, в то время как процессоры AMD и Arm на нём практически, то в 2024 году доля AMD на рынке серверных процессоров составила около 33 % (и продолжает расти), а доля рынка Intel сократилась почти до 63 %. Переломный момент наступил после появления архитектуры AMD Zen и проблем Intel с переводом Xeon на более тонкие техпроцессы. К концу 2022 года доля рынка AMD превысила отметку в 20 %, в то время как доля Intel впервые упала ниже 75 %. Согласно оценкам Bank of America, основанным на данных IDC и Mercury Research, доля AMD на рынке серверных процессоров вырастет в 2025 году примерно до 36 %, в то время как доля Intel снизится примерно до 55 %. Также растёт конкуренция со стороны серверных процессоров с архитектурой Arm, поскольку поставщики облачных услуг ищут более энергоэффективные и экономичные варианты, а совокупная стоимость владения (TCO) в ЦОД становится все более важным фактором. Прогнозируется, что в следующем году на них будет приходиться примерно 9 % рынка серверных процессоров. В 2027 году, как ожидается доля рынка AMD может достичь 40 %, а доля Intel упадет ниже 50 %. Доля процессоров с Arm-архитектурой может составить от 10 до 12 %. Сама Arm Holdings намерена уже до конца этого занять половину рынка чипов для ЦОД, куда, впрочем, входят не только CPU. SoftBank, владеющая крупнейшей долей в Arm Holdings, решила приобрести разработчики серверных Arm-процессоров Ampere Computing. С 2028 года ожидается, что AMD и Intel будут в равных условиях. Следует отметить, что речь идёт о доле рынка исходя из выручки, то есть о продажах в денежном выражении, а не в количественном. Доход AMD в основном приносят высокопроизводительные многоядерные процессоры, в то время как Intel по-прежнему выпускает различные недорогие чипы. Как полагают аналитики, эта тенденция вряд ли изменится. AMD демонстрирует устойчивое развитие в серверном сегменте и готовит процессоры Venice, в то время как Intel пытается переломить ситуацию с помощью серии Xeon 6. |

|