Материалы по тегу: isa

|

25.10.2024 [13:24], Сергей Карасёв

От тостера до ЦОД: RISC-V International ратифицировала унифицированный профиль RVA23 для процессоров будущегоОрганизация RISC-V International объявила о ратификации профиля RVA23. Это значимое событие, которое, как ожидается, поможет открытой архитектуре RISC-V укрепить позиции по отношению к Arm и x86, избегая при этом потенциальных проблем, связанных с лицензированием. Профили RVA необходимы для обеспечения переносимости ПО между различными аппаратными реализациями. Таким образом, разработчики софта могут избежать привязки к конкретному поставщику аппаратных решений. Иными словами, одно и то же приложение сможет функционировать на любых устройствах, оснащённых процессорами с архитектурой RISC-V. Профиль RVA23 стандартизирует набор инструкций ISA (Instruction Set Architecture). Ключевой задачей является устранение фрагментации внутри экосистемы RISC-V. Отмечается, что в рамках ратификации профиль RVA23 прошёл длительный процесс разработки, рассмотрения и утверждения в многочисленных рабочих группах.

Источник изображения: pixabay.com RVA23 делает обязательными такие функции, как векторные операции, инструкции с плавающей запятой и атомарные инструкции, которые необходимы во многих сферах, включая НРС, машинное обучение и ИИ. В частности, векторные расширения ускоряют рабочие нагрузки с интенсивными математическими расчётами, включая криптографию, (де-)компрессию, обучение ИИ и пр. Важным компонентом RVA23 является поддержка гипервизоров. Это позволяет виртуализировать корпоративные рабочие нагрузки как на локальных серверах, так и в облаке. Таким образом, может быть ускорена разработка оборудования, ОС и прикладных программ для архитектуры RISC-V. Поддержка виртуализации также улучшит безопасность мобильных приложений путём разделения защищённых и незащищённых компонентов.

30.07.2021 [21:05], Алексей Степин

Конец эпохи: Intel окончательно прекратила поставки процессоров ItaniumПервая попытка Intel покорить рынок массовых 64-бит систем окончилась неудачей — любопытная сама по себе архитектура Itanium (IA64) была несовместима со сложившейся экосистемой x86. Однако лишь сегодня в истории можно окончательно поставить точку: компания прекратила последние отгрузки процессоров Itanium. Сейчас поддержка 64-бит вычислений привычна и является частью любого достаточно современного процессора. Но так было не всегда: в конце 90-х и начале 2000-х ограничения, накладываемые 32-бит разрядностью хотя и были очевидны, рынок высокопроизводительных 64-бит процессоров для серверов и рабочих станций принадлежал компаниям Sun, Silicon Graphics, DEC и IBM. Все они имели RISC-архитектуру и не имели совместимости с x86.

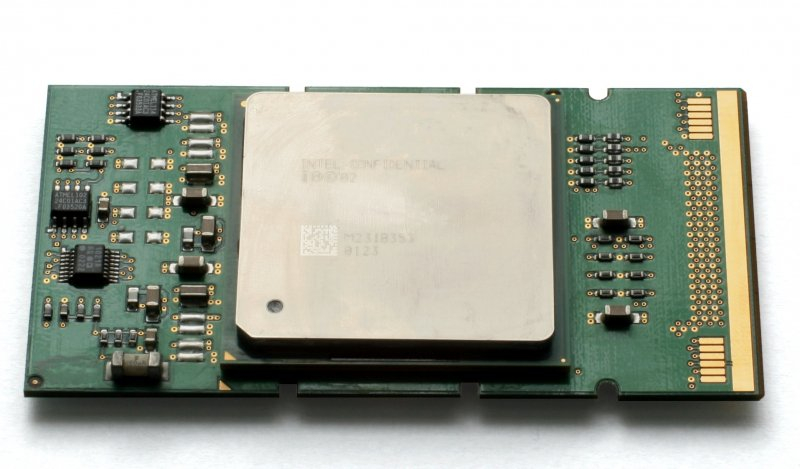

Форм-фактор Itanium: нечто среднее между слотовыми Pentium II/III и привычным PGA/LGA Itanium, или IA64, совместная разработка Intel и Hewlett-Packard, должна была вернуть этим компаниям первенство в сфере мощных CPU. И ставка была сделана на уникальную архитектуру EPIC (разновидность VLIW) с явным параллелизмом команд. Сама по себе IA64 обладала рядом преимуществ, однако требовала тонкой проработки ПО на уровне компилятора, поскольку процессоры EPIC во многом полагаются именно на него, а не на аппаратный планировщик.

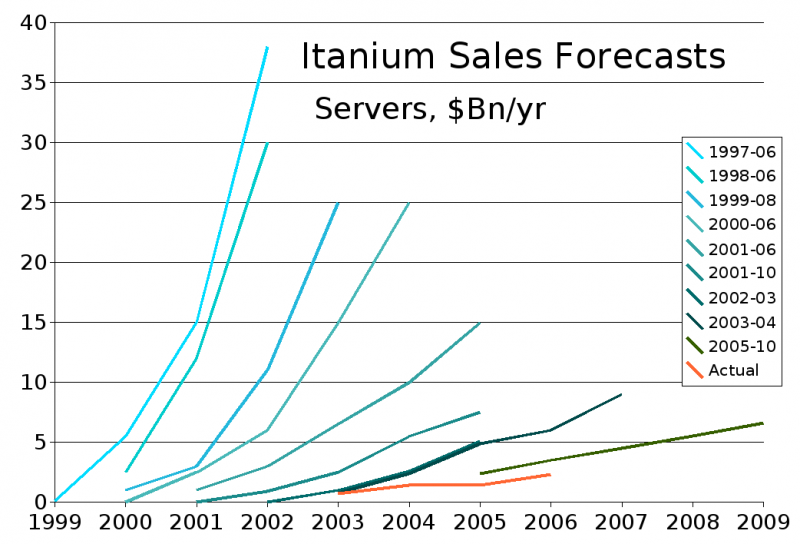

Itanium: радужные надежды и суровая реальность (красная линия) Отказ от последнего позволял потратить освободившийся транзисторный бюджет на более важные, по мнению Intel и HP, цели — например, на увеличение производительности вычислений с плавающей запятой. Но инфраструктура программного обеспечения к моменту анонса Itanium уже была весьма развитой. При этом новое, 64-бит ПО ещё надо было создать и, что гораздо важнее и сложнее, правильным образом оптимизировать, а уже имевшееся на новых CPU работало медленно из-за необходимости эмуляции x86. Компании пытались развивать IA64 до 2017 года, когда были представлены чипы Itanium Kittson с 8 ядрами и частотой до 2,66 ГГц, но то, что затея с новой архитектурой оказалась неудачной, было понятно уже после анонса первых процессоров AMD x86-64, полностью совместимых как с 32-бит, так и с 64-бит приложениями x86. В начале 2021 года Линус Торвальдс объявил о фактической смерти архитектуры и поддержка IA64 была исключена из новых ядер Linux. А сегодня можно говорить об окончательном завершении эры Itanium.

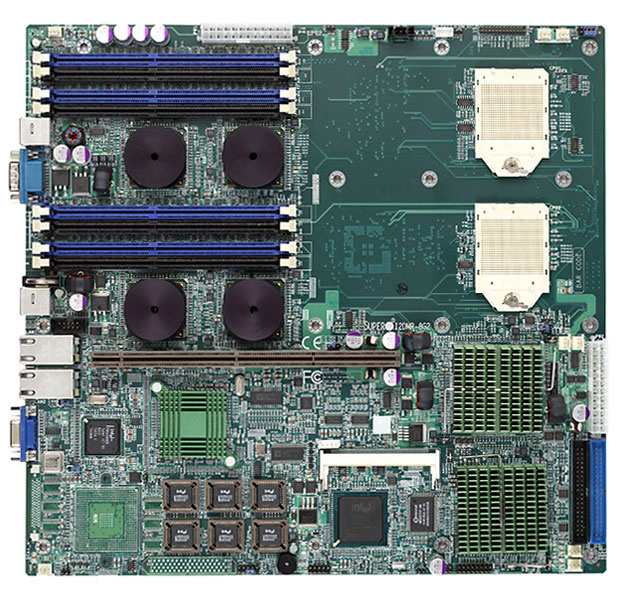

Раритет: Supermicro i2DML-iG2 в форм-факторе EATX с поддержкой Itanium 2. Найти такую плату почти невозможно Сама Intel ещё в 2019-ом официально поставила на Itanium крест, но из-за сложившейся экосистемы заказы на процессоры принимались вплоть до 30 января 2020 года. А вчера компания официально объявила о прекращении поставок последних партий Itanium. Теперь ещё одна процессорная архитектура стала достоянием истории, хотя HPE формально будет поддерживать её до 2025 года. Сами CPU нередко встречаются на онлайн-аукционах, например, на Ebay, но даже для энтузиастов они малоинтересны — найти подходящую системную плату невероятно сложно, а стоить она может намного дороже самих процессоров, да и форм-фактор имеет специфический.

24.08.2019 [06:14], Андрей Галадей

IBM передала наработки по архитектуре Power сообществуКорпорация IBM сообщила, что переводит архитектуру набора команд (ISA) Power в разряд открытых решений. То есть, за неё не нужно будет платить, как это было в последние 6 лет. Отмечается, что с 2013 года действовал консорциум OpenPOWER, который лицензировал связанную с Power интеллектуальную собственность. Но теперь все наработки и патенты будут переданы сообществу безвозмездно. Сама же организация OpenPOWER Foundation будет переподчинена Linux Foundation, что позволит создать площадку для развития архитектуры без привязки к чипмейкеру или иной компании. Как отмечается, OpenPOWER Foundation включает в себя более 350 компаний, а сообществу передали свыше 3 млн строк кода системных прошивок, спецификаций и схем. Всё это позволит создавать Power-совместимые чипы всем желающим.

pixabay.com Помимо собственно процессоров, компания передала сообществу и смежные технологии для разработки расширений на основе интерфейсов OpenCAPI (Open Coherent Accelerator Processor Interface) и OMI (Open Memory Interface). Первая технология должна устранить «узкие места» во взаимодействии CPU, GPU, ASIC, а также других чипов и контроллеров. Вторая же должна ускорить оперативную память. Это позволит создавать на базе архитектуры Power специализированные чипы для искусственного интеллекта. Важно отметить, что процессоры Power позволяют создавать современные серверы и суперкомпьютеры. К примеру, суперкомпьютеры Summit и Sierra работают как раз на таких чипах. А это, на минуточку, первый и второй номера в мировом рейтинге таких систем. Напомним, на процессорах с архитектурой Power (хотя и специализированных) работали в том числе и консоли Sony PlayStation 3, Xbox 360, а также старые ПК и ноутбуки Apple. |

|