Материалы по тегу: cpu

|

06.03.2025 [21:36], Владимир Мироненко

Google раскрыла детали уязвимости в процессорах AMD и опубликовала инструментарий для анализа и изменения их микрокодаСпециалисты Google Security Team сообщили детали уязвимости (CVE-2024-56161), позволяющей обойти механизм проверки цифровой подписи при обновлении микрокода в процессорах AMD на базе микроархитектуры от Zen1 до Zen4, о чём пишет ресурс OpenNet. Уязвимости присвоен рейтинг опасности CVSS 7,2 балла из 10, что говорит о серьёзности проблемы. «Неправильная проверка подписи в загрузчике исправлений микрокода CPU AMD может позволить злоумышленнику с привилегиями локального администратора загрузить вредоносный микрокод», — говорится в сообщении Google. Исследователи известили AMD об обнаруженной уязвимости 25 сентября 2024 года. Уязвимость, сделавшая возможной загрузку собственных патчей для микрокода процессоров AMD Zen 1-4, вызвана использованием для верификации вместо рекомендованных хеш-функций алгоритма CMAC, который не подходит для этого и не защищён от подбора коллизий. Компания AMD устранила уязвимость в декабрьском обновлении микрокода путём замены CMAC на криптографически стойкую хеш-функцию. Google также опубликовала под лицензией Apache 2.0 инструментарий Zentool, с помощью которого можно анализировать микрокод, манипулировать им и создавать патчи для изменения микрокода в процессорах AMD Zen. Zentool включает команды: zentool edit — редактирует параметры файлов с микрокодом, изменяет микрокод и заменяет отдельные инструкции; zentool print — выводит информацию о структурах и параметрах микрокода; zentool load — загружает микрокод в CPU; zentool resign — корректирует цифровую подпись с учётом добавленных в микрокод изменений. Также в состав Zentool входят утилиты mcas и mcop с реализациями ассемблера и дизассемблера для микрокода. Специалисты Google также подготовили руководство по микроархитектуре RISC86, применяемой в микрокоде AMD, и рекомендации по созданию собственного микрокода с пояснением, как создавать собственные процессорные инструкции, реализуемые на микрокоде RISC86, менять поведение существующих инструкций и загружать изменения микрокода в процессор.

06.03.2025 [18:45], Владимир Мироненко

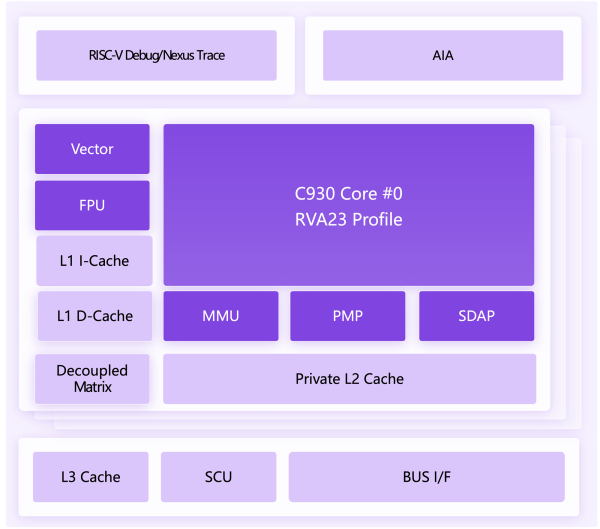

Китай запустит программу господдержки разработки и внедрения чипов RISC-VАрхитектура RISC-V с открытым исходным кодом, похоже, набирает значительную популярность в Китае, сделал вывод ресурс The Register, назвав в качестве свежего примера анонс процессора XuanTie C930, созданного НИИ Damo Academy (Alibaba Group Holding). Ядро C930 позиционируется как идеальное решение для серверов, ПК и автономных автомобилей. Особенно важно соответствие профилю RVA23, поскольку это краеугольный камень экосистемы RISC-V. В частности, профиль определяет расширения для гипервизора, которые являются практически необходимыми для серверных и облачных CPU. Как сообщает XuanTie, «C930 использует передовую микроархитектуру для достижения высокой производительности, включая алгоритм прогнозирования ветвлений на основе TAGE, индивидуальный кеш L2, регулируемый механизм предварительной выборки данных и т. д. Показатель производительности C930 в тесте Specint2006 превышает 15/ГГц». Сообщается, что «типичная конфигурация одного кластера поддерживает четыре ядра» с 64 Кбайт кеша инструкций и данных и L2-кешем на 1 Мбайт. Векторный блок поддерживает расширение RISC-V Vector 1.0, обрабатывает 256-бие векторные регистры и поддерживает вычисления в формате FP16/BF16/FP32/FP64/INT8/INT16/INT32/INT64. Также упомянут блок матричных вычислений. В ходе презентации чипа топ-менеджеры Alibaba Cloud спрогнозировали, что RISC-V станет основной облачной архитектурой в течение 5–8 лет. По данным Reuters, Пекин планирует запустить государственную программу с целью стимулирования широкого использования RISC-V по всей стране. В настоящее время восемь китайских правительственных агентств занимаются подготовкой постановления, которое будет способствовать распространению чипов на базе RISC-V в Китае. Ранее власти призвали китайские компании отказаться от американских чипов в пользу отечественных. Китайский разработчик процессоров Loongson получил возможность участия в пилотном проекте на поставку 10 тыс. ПК китайские школы и контракт на использование его чипов в вычислительной системе на орбитальной станции «Тяньгун», а Lenovo перенесла свой HCI-стек на архитектуру Loongson. Академия наук КНР пообещала в 2021 году выпускать новые проекты на основе RISC-V каждые полгода. Хотя эта цель не была достигнута, в феврале 2025 года академия намекнула на готовящийся мощный проект с использованием RISC-V. В 2023 году технологический гигант Baidu исследовал возможность использования чипов на базе RISC-V уровня ЦОД. В том же году Alibaba сообщила о намерении создать чипы RISC-V для различных сфер, от носимых устройств до облаков. Сейчас крупнейшими коммерческими производителями решений на базе RISC-V в Китае являются XuanTie и Nuclei System Technology, пишет Reuters. На недавнем мероприятии XuanTie было заявлено, что популярность DeepSeek также может стимулировать внедрение RISC-V, поскольку ИИ-модели китайского стартапа эффективно работают на менее мощных чипах. «Даже если решение RISC-V стоимостью ¥10 млн ($1,4 млн) может достичь лишь около 30 % уровня решений NVIDIA или Huawei, три таких комплекта будут всё равно дешевле», — сообщил представитель China Mobile System Integration. В США уже выразили беспокойство по поводу того, что открытая лицензия RISC-V, позволяющая разработчикам использовать архитектуру бесплатно, обеспечит китайским фирмам возможность применять интеллектуальную собственность, созданную в Америке, для разработки передовых технологий. Недавно господдержку запросил и российский альянс RISC-V.

01.03.2025 [14:17], Сергей Карасёв

Alibaba выпустила серверный процессор XuanTie C930 с архитектурой RISC-VНаучно-исследовательский институт Damo Academy, подразделение Alibaba Group Holding, по сообщению газеты South China Morning Post, выпустил свой первый процессор для серверов — изделие XuanTie C930, построенное на открытой архитектуре RISC-V. О подготовке названного чипа впервые стало известно в марте прошлого года. Тогда говорилось, что CPU будет использоваться в системах, предназначенных в том числе для работы с ИИ-приложениями. Характеристики XuanTie C930 полностью не раскрываются. Отмечается, что это суперскалярный процессор, который содержит 15-ступенчатый конвейер и поддерживает внеочередное исполнение команд. Заявлена поддержка унифицированного профиля RVA23. В рамках RVA23 предусмотрены такие функции, как векторные операции, обработка данных с плавающей запятой и атомарные инструкции, которые необходимы в том числе при решении ИИ-задач. Отгрузки XuanTie C930 заказчикам начнутся в текущем месяце.

Источник изображения: pconline.com.cn Ранее Damo Academy анонсировала несколько чипов XuanTie с архитектурой RISC-V для различных задач, включая C910 в 2019 году и C920 в 2024-м. В перспективе планируется выпуск процессоров XuanTie C908X, R908A и XL200, которые будут ориентированы соответственно на ИИ-системы, автомобильные приложения и коммуникационное оборудование. Нужно отметить, что Китай активно развивает собственную полупроводниковую промышленность, а одним из приоритетов является направление RISC-V. В 2023 году ведущие китайские RISC-V-разработчики сформировали патентный альянс — China RISC-V Industry Alliance. Разработкой RISC-V-изделий занимаются многие компании и организации из КНР, включая Китайскую академию наук. Создание собственных CPU имеет для страны большое значение в свете усиливающихся санкций со стороны США.

27.02.2025 [12:51], Сергей Карасёв

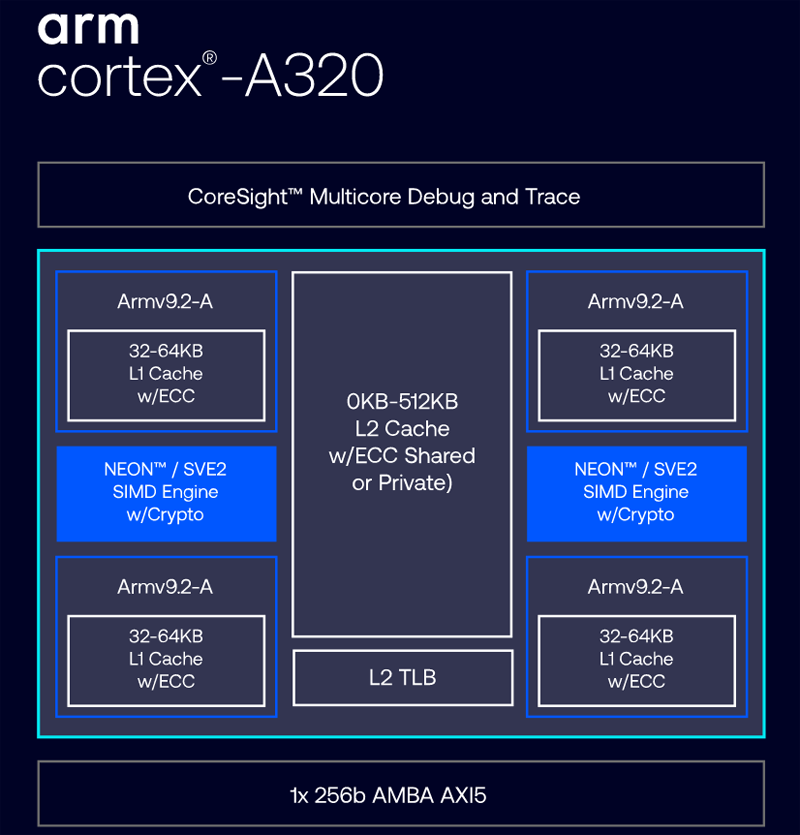

Представлен Armv9-процессор Cortex-A320 для IoT-устройств с ИИ-функциямиКомпания Arm анонсировала процессор Cortex-A320 — своё первое сверхэффективное изделие семейство Cortex-A, построенное на архитектуре Armv9. Чип ориентирован на периферийные устройства и IoT-оборудование с поддержкой ИИ-функций. В основу новинки положена архитектура версии Armv9.2-A (Harvard) с поддержкой расширений QARMA3, SVE2, MTE, RAS и криптографическими функциями. Объём кеша первого уровня может составлять 32 или 64 Кбайт. Опционально доступен кеш L2 ёмкостью от 128 до 512 Кбайт, тогда как кеш L3 не предусмотрен. Кроме того, существенно ускорена работа с оперативной памятью. Cortex-A320 — это одноядерный процессор с последовательной выборкой 32-битных инструкций. Благодаря многочисленным обновлениям микроархитектуры, таким как предсказание ветвлений и предварительные выборки, достигается повышение эффективности на 50 % по сравнению с Cortex-A520 и увеличение быстродействия на 30 % в SPECINT2K6 по сравнению с Cortex-A35.

Источник изображения: Arm По заявлениям Arm, процессор Cortex-A320 обеспечивает 10-кратное повышение производительности на операциях машинного обучения по сравнению с Cortex-A35 (на GEMM int8) и 6-кратное повышение по сравнению с Cortex-A53, самым популярным в мире изделием на архитектуре Armv8-A. На сегодняшний день Cortex-A320 — это наиболее эффективное решение серии Cortex-A для задач машинного обучения. На базе Cortex-A320 могут формироваться кластеры, насчитывающие до четырёх ядер. Блок векторной обработки с технологиями NEON и SVE2 может быть индивидуальным для каждого ядра или использоваться связкой из двух ядер, в том числе в четырёхъядерной конфигурации. Благодаря DSU-120T (оптимизированная версия DynamIQ Shared Unit) возможно формирование кластеров исключительно с ядрами Cortex-A320. Кроме того, новинки поддерживают NPU Ethos-U85, которые позволяют автоматически перекидывать обработку неподдерживаемых типов данных и инструкций на SIMD-блоки Cortex-A320. В целом говорится о возможности запуска на новых чипах моделей с более чем 1 млрд параметров. Процессор Cortex-A320 может применяться в самых разных сферах — от умных колонок и интеллектуальных камер наблюдения до автономных транспортных средств и контроллеров служебных роботов. Кроме того, новый процессор подходит для микроконтроллеров с батарейным питанием и устройств, работающих под управлением операционных систем реального времени (RTOS). Реализованы развитые средства обеспечения безопасности, включая Secure EL2 (Exception Level 2).

25.02.2025 [23:20], Владимир Мироненко

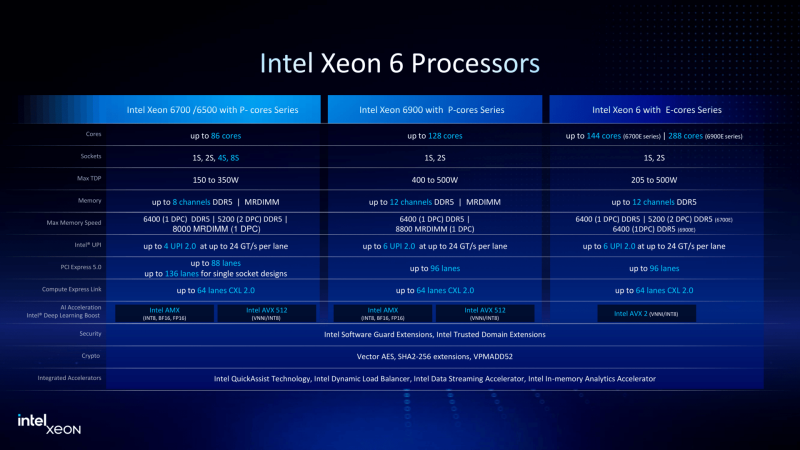

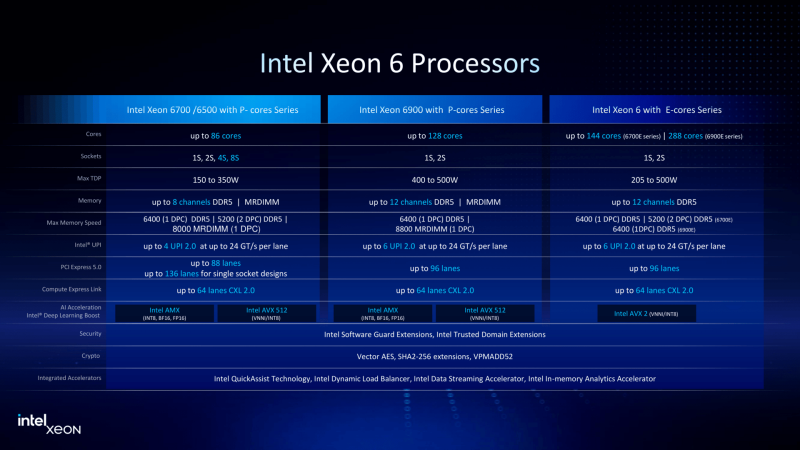

Intel: 288-ядерные процессоры Xeon 6900E — нишевый продуктКомпания Intel провела в понедельник презентацию ряда новых чипов, включая серию серверных процессоров Xeon 6700P и 6500P среднего класса, в ходе которой объявила, что представленный в прошлом году 288-ядерный серверный процессор Xeon 6900E (Sierra Forest-AP) не будет «широко распространяться» среди OEM-производителей, поскольку его главные потребители — пользователи облачных вычислений с индивидуальными потребностями в чипах, передаёт CRN. Intel добавила, что Xeon 6900E, являющийся флагманом семейства процессоров Xeon 6 Sierra Forest с энергоэффективными ядрами (E-cores), сейчас находится в производстве. Ронак Сингал (Ronak Singhal), старший научный сотрудник Intel и главный архитектор чипов Xeon рассказал, что Xeon 6900E предназначен для удовлетворения потребности облачных клиентов в кастомных чипах. По его словам, один из крупных клиентов уже запустил системы на базе Xeon 6900E. Ранее было объявлено, что компания будет выпускать для AWS кастомные Xeon 6 и ИИ-ускорители. По словам топ-менеджера Intel, те, кому действительно требуется очень большее количество ядер в процессорах обычно относятся к тем клиентам, с которыми компания обычно работает над индивидуальными решениями. За несколько недель до этого Мишель Джонстон Холтхаус (Michelle Johnston Holthaus), врио главы Intel и гендиректор Intel Products, заявила в ходе отчёта о квартальных результатах, что линейка Xeon 6 с E-ядрами не имеет той поддержки, на которую были надежды, также отметив, что это нишевый продукт. Несмотря на то, что это семейство Xeon 6 с E-ядрами пока не оправдывает ожиданий, Холтхаус заявила, что Intel по-прежнему возлагает большие надежды на процессоры Xeon следующего поколения с E-ядрами Clearwater Forest, хотя их выпуск пришлось отложить до I половины 2026 года из-за возникших сложностей с технологией упаковки, хотя до этого их планировалось выпустить уже в 2025 году. Clearwater Forest рассматривается компанией как стратегически важный продукт, поскольку он станет первым серверным процессором, использующим техпроцесс Intel 18A, который, как неоднократно заявляла компания, позволит ей превзойти возможности чипов, произведённых TSMC и Samsung. За несколько месяцев до того, как Гелсингер покинул компанию, он заявил, что чип позволит Intel «ускорить рост доли» на рынке.

25.02.2025 [18:30], Владимир Мироненко

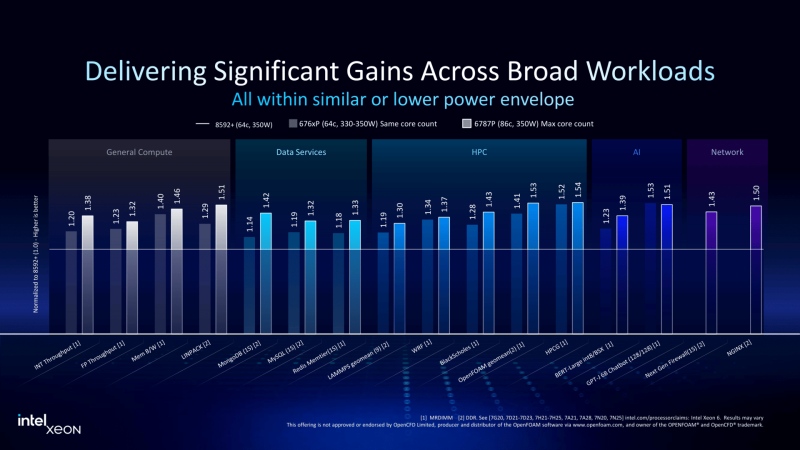

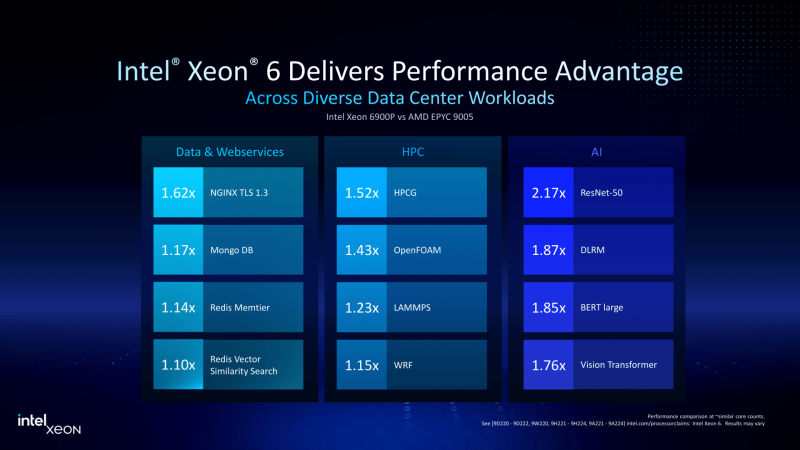

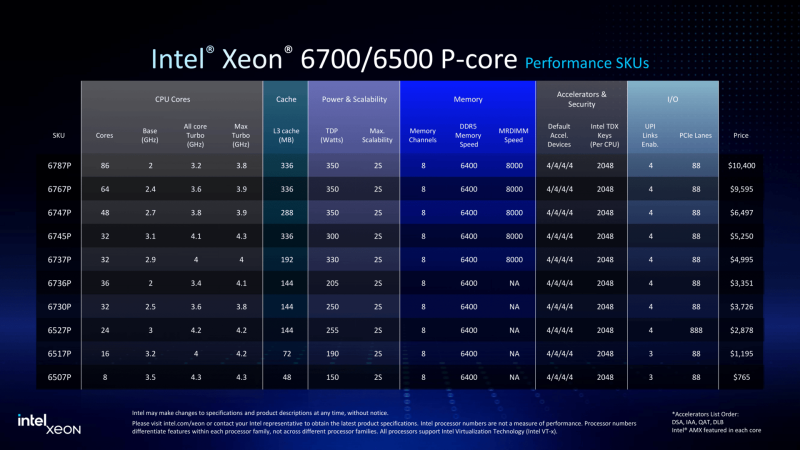

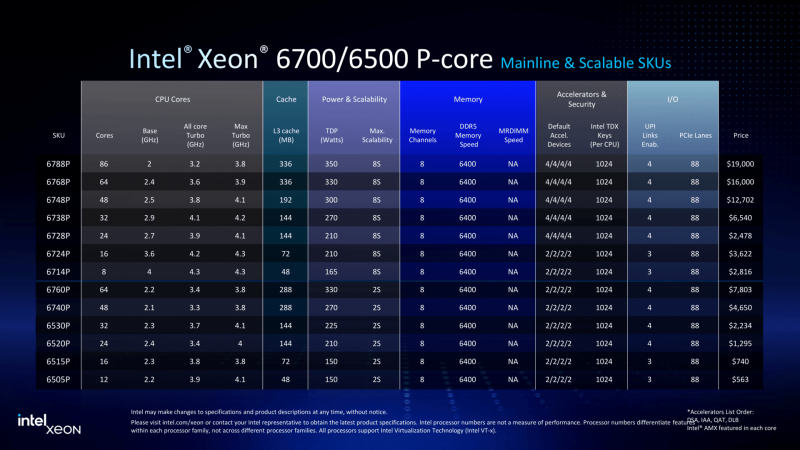

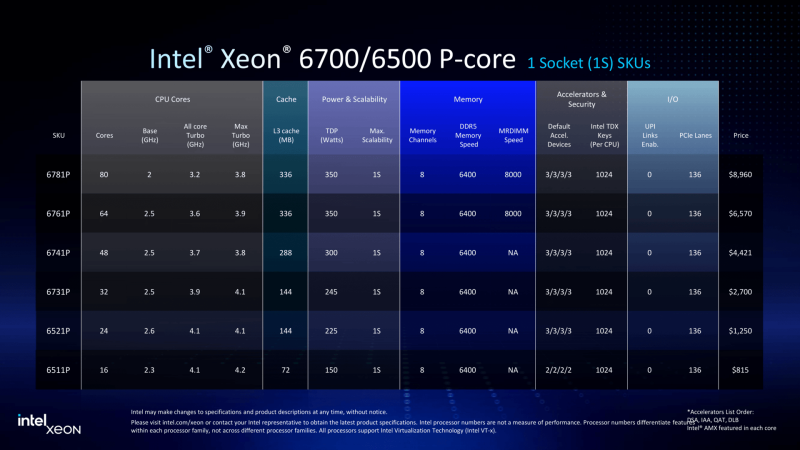

Granite Rapids в малом формате: Intel представила процессоры Xeon 6500P и 6700PIntel объявила о пополнении семейства процессоров Xeon 6 рядом новинок, включая чипы Granite Rapids-SP Xeon 6700P и 6500P, предназначенные для использования в ЦОД. Одновременно компания представила младшую серию Xeon 6300 для серверов начального уровня, а также Xeon 6 SoC поколения Granite Rapids-D с ускорителями vRAN Boost. Как отметил ресурс The Register, в отличие от Intel Xeon 6900P (Granite Rapids-AP), в новых чипах Xeon с P-ядрами компания не пыталась сравниться с AMD по количеству ядер или чистой вычислительной мощности. Успешно восстановив паритет по количеству ядер со своим конкурентом в сегменте чипов с архитектурой x86, Intel в значительной степени опирается на то, что осталось от её репутации на рынке — на свой набор ускорителей вычислений и более агрессивную ценовую политику — в попытке остановить снижение своей доли в секторе чипов для ЦОД. В Xeon 6 компания перешла на чиплетную компоновку, отделив I/O-тайлы (Intel 7) от вычислительных тайлов (Intel 3), но сохранив контроллеры памяти в составе последних. В случае 6700P и 6500P I/O-тайлы фактически те же, а вот блоки с ядрами отличаются. В старших 86-ядерных чипах используется пара XCC-чиплетов. В 48-ядерных и 16-ядерных чипах есть по одному вычислительному HCC- и LCC-тайлу соответственно. Это повышает выход годной продукции и позволяет гибко подходить к выбору количества ядер и тактовых частот — до +22 ядер при том же TDP (150–350 Вт) в сравнении с прошлым поколением. В то же время такой подход ограничивает количество доступных каждому процессору каналов памяти — их в 6500P/6700P всего восемь с возможностью установки до 4 Тбайт RAM. Поддерживается DDR5-6400 (1DPC) и DDR5-5200 (2DPC). С другой стороны, для двухсокетных серверов с 32 DIMM не придётся изощряться с размещением слотов памяти, сохранив традиционную архитектуру плат, охлаждения и шасси в целом. Кроме того, некоторые CPU помимо обычных модулей также поддерживают MRDIMM DDR5-8000 (1 DPC). Наконец, есть и поддержка до 64 линий CXL 2.0, что теоретически также позволит нарастит доступную память. В односокетных конфигурациях R1S-чипы поддерживают до 136 линий PCIe 5.0 (взамен ненужных UPI) против 88 линий у обычных многосокетных процессоров. В новых CPU также вернулась поддержка 4S- и 8S-конфигураций (до четырёх линий UPI 2.0 24 ГТ/с на CPU), которой были лишены и Emerald Rapids, и Xeon 6 6900P. Таким образом, Intel по-прежнему остаётся единственным поставщиком многосокетных x86-платформ для SAP HANA и аналогичных рабочих нагрузок, которым требуется одновременно много памяти и много ядер, а по сравнению с Sapphire Rapids новинки значительно быстрее. Объём L3-кеша теперь составляет от 48 Мбайт до 336 Мбайт. Intel заявила, что чипы серии 6700P обеспечат от 14 % до 54 % прироста производительности по сравнению с флагманскими чипами Xeon Emerald Rapids. Intel по-прежнему в значительной степени опирается на интегрированные ускорители, чтобы получить преимущество по производительности по сравнению с конкурентами. Компания уже много лет встраивает кастомные ускорители в процессоры для выполнения нагрузок шифрования, безопасности, хранения, аналитики, обработки сетевого трафика и ИИ. В то же время у некоторых моделей по-прежнему активно лишь по два или три, а не по четыре акселератора DSA/DLB/IAA/QAT. Ещё одно отличие — поддержка 1024 или 2048 ключей TDX для защиты конфиденциальности в зависимости от модели. Примечательно, что NVIDIA добавила в Blackwell поддержку TDX. Intel утверждает, что в дополнение к увеличению числа ядер и инструкций за такт (IPC) в новом поколении процессоров с криптографическими движками и поддержкой AMX это позволяет одному серверному чипу Xeon 6 заменить до десяти систем Cascade Lake, по крайней мере, для таких рабочих нагрузок, как классификация изображений и работа веб-сервера Nginx с TLS. По словам Intel, её новые чипы обеспечивают преимущество по сравнению с новейшими процессорами AMD EPYC Turin в производительности в 62 % для Nginx с TLS, 17 % для MongoDB, 52 % в бенчмарке HPCG, 43 % в программной среде OpenFOAM и 2,17x в ResNet-50. The Register также отметил, что выход процессоров Intel Xeon 6 серий 6700P и 6500P демонстрирует выросшую агрессивнось Intel в отношении ценообразования. Intel традиционно дороже из расчёта за ядро по сравнению с AMD. Но теперь Intel пытается соответствовать своему конкуренту в ценах при любом количестве ядер или на целевых рынках. Компания даже незаметно снизила цены на 6900P в конце прошлого года, всего через несколько месяцев после запуска. Единственным исключением являются поддерживающие 4S- и 8S-конфигурации процессоры, у которых нет конкурентов на рынке x86-чипов. Стоимость CPU доходит до $19 тыс./шт. Естественно, здесь стоит сделать традиционную оговорку, что и AMD, и у Intel рекомендованные цены указаны за партии от 1 тыс. шт., но на практике их реальная стоимость будет варьироваться в зависимости от объёма заказа и нужд конкретного клиента, да и просто договорённостей с продавцами, интеграторами и другими участниками цепочки поставок. Наконец, у Intel появилось одно неожиданное преимущество перед AMD — «кремний» Xeon по-прежнему делается на собственных фабриках в США, тогда как AMD всё ещё зависит от тайваньской TSMC. Если новая администрация США введёт тариф на импорт полупроводников в размере 25 % и более, то Intel Xeon 6 наверняка окажутся выгоднее AMD EPYC. Intel также объявила, что Xeon 6 рекомендуются в качестве хост-процессоров для платформ NVIDIA MGX и HGX. Заявлена и поддержка OCP DC-HMS.

25.02.2025 [13:00], Сергей Карасёв

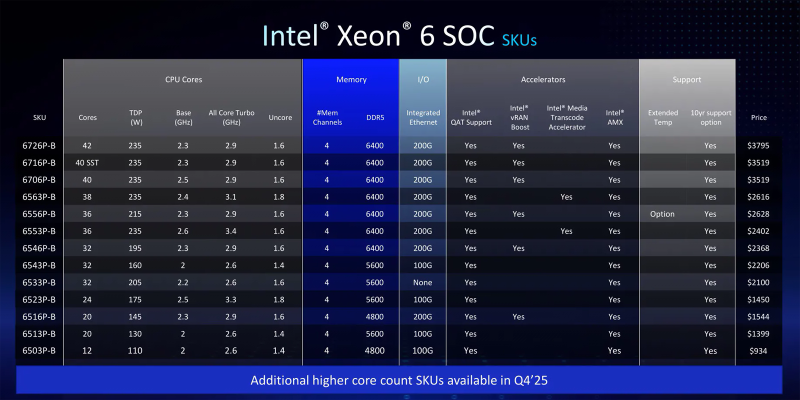

Granite Rapids-D для 5G с ИИ: дебютировали чипы Intel Xeon 6 SoC для сетевых и периферийных устройствКорпорация Intel представила чипы Xeon 6 SoC семейства Granite Rapids-D, рассчитанные на использование в сетевом оборудовании, а также встраиваемых устройствах с ИИ-функциями. Чипы поддерживают технологию Intel QAT (QuickAssist Technology) для ускорения криптографических операций, компрессии и обработки сетевого трафика. На сегодняшний день в серию Xeon 6 SoC вошли 13 моделей с количеством вычислительных ядер от 12 до 42. Все они имеют четыре канала памяти DDR5 с частотой 4800, 5600 или 6400 МГц. Показатель TDP находится в диапазоне от 110 до 235 Вт, а турбо-частота при использовании всех ядер достигает 2,9 ГГц. Все чипы имеют BGA-упаковку. Большинство процессоров располагают интегрированным контроллером Ethernet 200G или 100G (за исключением Xeon 6533P-B). Некоторые модификации обладают поддержкой vRAN Boost и содержат ускоритель для транскодирования медиаданных. При этом все изделия поддерживают расширения AMX (Advanced Matrix Extensions), обеспечивающие ускорение рабочих нагрузок ИИ и машинного обучения. На вершине семейства находится чип Xeon 6726P-B с 42 ядрами, TDP 235 Вт, базовой частотой 2,3 ГГц (повышается до 2,9 ГГц), поддержкой четырёхканальной памяти DDR5-6400 и 200GbE-контроллером: стоит изделие $3795. Младшая версия Xeon 6503P-B с 12 ядрами, TDP в 110 Вт, частотой 2,0–2,6 ГГц, поддержкой DDR5-4800 и 100GbE-контроллером оценена в $934. Отмечается, что в IV квартале текущего года будут представлены физически более крупные модели Xeon 6 SoC, имеющие 12 каналов DDR5, от 56 до 72 P-ядер и TDP на уровне 280–325 Вт. Кроме того, корпорация Intel сообщила, что процессоры следующего поколения Clearwater Forest на основе энергоэффективных ядер E-Core, которые придут на смену Sierra Forest, будут выпущены в I половине 2026 года.

25.02.2025 [12:45], Сергей Карасёв

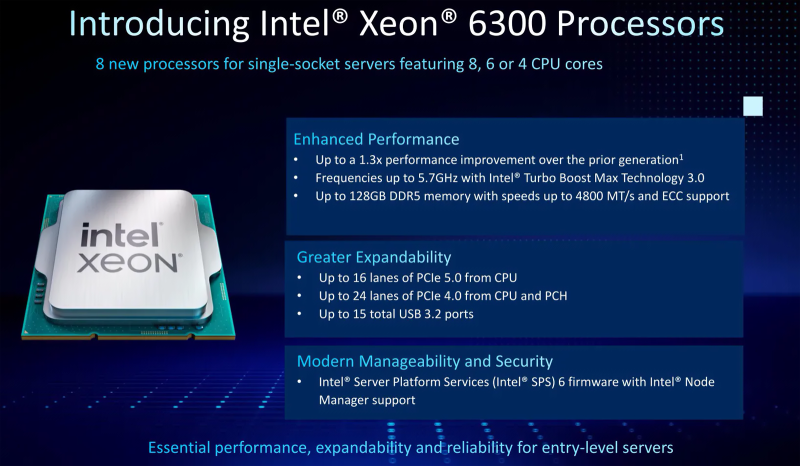

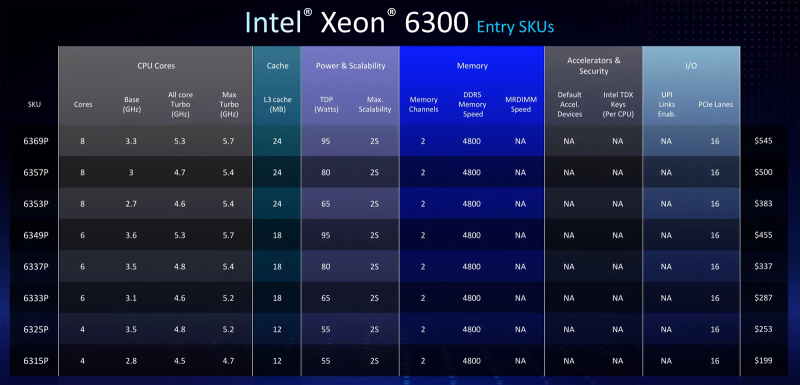

Привет из 2019-го: Intel представила восьмиядерные процессоры Xeon 6300 для серверов начального уровняКорпорация Intel анонсировала процессоры Xeon 6300, о подготовке которых стало известно около недели назад. Чипы рассчитаны на применение в серверах начального уровня — прежде всего в односокетных моделях. Как отмечается, изделия Xeon 6300 представляют собой обновление семейства Xeon E-2400, дебютировавшего в декабре 2023 года. Обе серии относятся к поколению Raptor Lake. При этом, по заявлениям Intel, по производительности Xeon 6300 превосходят предшественников в 1,3 раза. Платформа Xeon 6300 обеспечивает поддержку до 128 Гбайт двухканальной оперативной памяти DDR5-4800 (ЕСС), до 16 линий PCIe 5.0 (CPU) и до 24 линий PCIe 4.0 (CPU + PCH), а также до 15 портов USB 3.2. В основу процессоров Xeon 6300 положены производительные Р-ядра. На сегодняшний день серия включает восемь моделей с четырьмя, шестью и восемью ядрами, поддерживающими технологию многопоточности (8, 12 или 16 потоков инструкций). Максимальная тактовая частота в турбо-режиме достигает 5,7 ГГц (см. таблицу). Объем кеша L3 в зависимости от модели составляет 12, 18 или 24 Мбайт. Показатель TDP варьируется от 55 до 95 Вт. Цена — от $199 до $545. Как отмечает ServeTheHome, процессорам Xeon 6300 будет трудно конкурировать с существующими чипами AMD EPYC 4004, которые содержат до 16 ядер (32 потока инструкций). Поэтому анонс Xeon 6300 следует рассматривать скорее в качестве унификации брендинга серверных чипов Xeon и незначительного апдейта ранее существовавших изделий Xeon E-2400. Кстати, отдельные материнские платы и серверы под Xeon E-2400 совместимы с процессорами Xeon 6300.

18.02.2025 [13:56], Сергей Карасёв

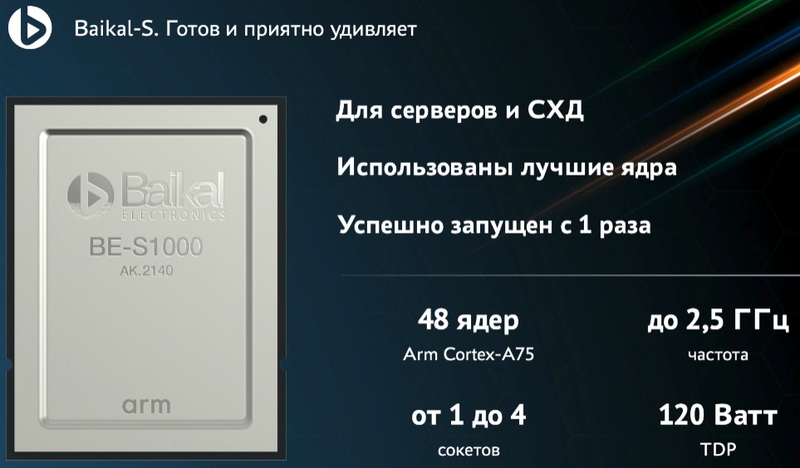

Поставки российских процессоров Baikal-S возобновятся в конце 2025 годаКомпания «Байкал Электроникс», по сообщению CNews, получила декларацию о соответствии требованиям технического регламента ЕАЭС на серийный выпуск серверных процессоров Baikal-S и их продажи в России. Поставки чипов, как ожидается, возобновятся в конце 2025 года. Чипы Baikal-S насчитывают 48 ядер Arm Cortex-A75, поддерживают память DDR4-3200 МГц, имеют 80 линий PCIe 4.0 и два интерфейса 1GbE. Первая партия процессоров была получена в конце 2021 года. Изначально предполагалось, что производством изделий займётся TSMC с применением 16-нм технологии. Однако TSMC отказалась обслуживать российских заказчиков, и с выпуском Baikal-S возникли сложности. В результате, летом 2022-го «Байкал Электроникс» отменила производство и продажи этих процессоров. Но в конце 2024 года стало известно о том, что в Россию поступила партия из 1 тыс. чипов Baikal-S. Говорилось, что почти все они достались некой крупной компании с государственным участием. При этом несколько сотен чипов были распределены по госпроектам и проданы другим производителям. И вот теперь сообщается, что выпуск изделий Baikal-S возобновится.

Источник изображения: «Байкал Электроникс» В документах ЕАЭС в качестве места производства процессоров значится город Красногорск в Московской области, где находится один из офисов «Байкал Электроникс». Но по факту чипы будут изготавливаться на неназванном предприятии в Азии. Участники рынка считают, что изделия Baikal-S будут востребованы прежде всего среди тех отечественных производителей, которым необходимо выполнять «балльные обязательства», чтобы попадать в реестр российской продукции Минпромторга.

17.02.2025 [12:22], Сергей Карасёв

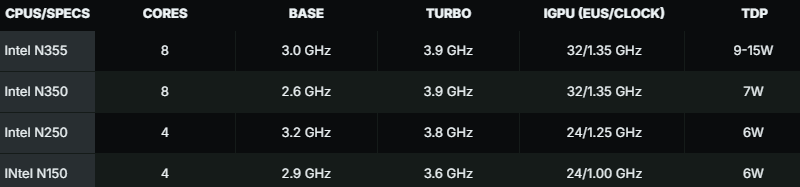

Intel выпустила процессоры Twin Lake с четырьмя и восемью ядрами E-CoreВ ассортименте корпорации Intel появились процессоры семейства Twin Lake, рассчитанные на применение в таких устройствах, как компьютеры небольшого форм-фактора и одноплатные изделия. По сути, чипы Twin Lake представляют собой обновление решений Alder Lake-N. Сообщается, что вычислительные ядра Twin Lake базируются на архитектуре Gracemont, как и у Alder Lake-N, но по сравнению с прародителями имеют несколько более высокие частоты. Предусмотрен встроенный графический ускоритель Intel UHD Graphics. Показатель TDP в зависимости от модификации варьируется от 6 до 15 Вт.

Источник изображения: Intel Конструкция Twin Lake включает исключительно энергоэффективные ядра E-Core, тогда как производительные ядра P-Core не предусмотрены. Таким образом, технология многопоточности не поддерживается. Объём кеш-памяти L3 у всех новинок составляет 6 Мбайт. На сегодняшний день в семейство входят четыре чипа: Intel Core 3 Processor N355, Intel Core 3 Processor N350, Intel Processor N250 и Intel Processor N150. Первые два наделены восемью ядрами, два других — четырьмя. Максимальная частота в турбо-режиме достигает 3,9 ГГц (см. таблицу). Поддерживается работа с оперативной памятью DDR4-3200, DDR5-4800 и LPDDR5-4800, максимальный объём которой может достигать 16 Гбайт. Возможен вывод изображения через интерфейсы eDP 1.4b, DP 1.4, HDMI 2.1, MIPI-DSI 1.3. При производстве применяется технология Intel 7 (исполнение — FCBGA1264).

Источник изображения: wccftech.com Сетевые источники отмечают, что с точки зрения реальной производительности процессоры семейства Twin Lake практически идентичны сопоставимым по характеристикам изделиям серии Alder Lake-N. |

|