Материалы по тегу: cpu

|

14.02.2025 [09:45], Сергей Карасёв

Arm выпустит собственные чипы для ЦОД, а их первым покупателем станет Meta✴Британская компания Arm, 90 % которой принадлежит японскому холдингу SoftBank, выйдет на рынок процессоров для серверов, ориентированных на крупные дата-центры. Как сообщает газета Financial Times, эти изделия дебютируют в текущем году, а их первым заказчиком станет Meta✴ Platforms. Весной 2024 года сообщалось, что Arm намерена разработать собственный ИИ-чип. Тогда говорилось, что его массовый выпуск будет налажен к осени 2025-го на мощностях контрактного производителя. В частности, холдинг SoftBank вёл переговоры на соответствующую тему с TSMC.

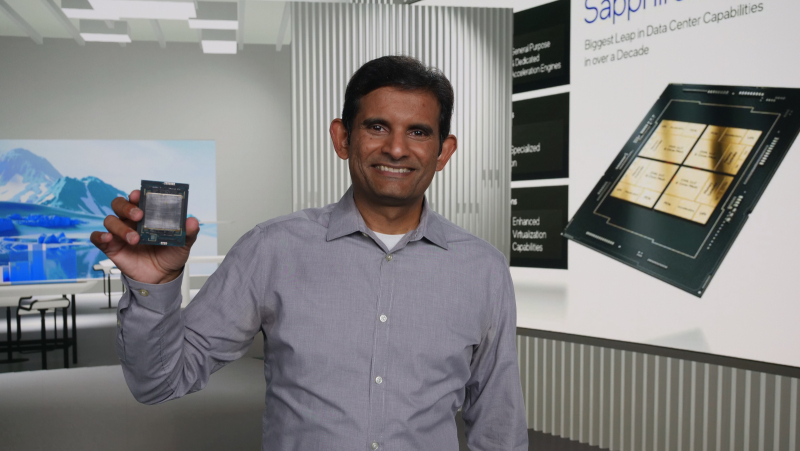

Источник изображения: Arm Как теперь стало известно, первым изделием собственной разработки Arm станет серверный CPU, а не ИИ-чип. Архитектура готовящегося решения предполагает возможность кастомизации под нужды заказчика. Этим воспользуется Meta✴, которая активно расширяет инфраструктуру ЦОД, а перспективе намерена потратить «сотни миллиардов долларов» на развитие ИИ-экосистемы. Рене Хаас (Rene Haas), генеральный директор Arm, отметил, что компания намерена официально представить процессор предстоящим летом. При этом вдаваться в подробности о технических характеристиках изделия он не стал. Выход Arm на рынок аппаратных решений будет означать серьёзное изменение бизнес-модели: ранее компания зарабатывала на лицензировании своих разработок другим участникам рынка, в том числе поставщикам решений для дата-центров и облачных платформ. Вместе с тем в ИИ-сегменте Arm увеличивает выручку путём постоянного повышения лицензионных сборов за свои технологии и благодаря взиманию роялти за каждый чип, продаваемый другими компаниями. Недавно также сообщалось, что SoftBank вскоре может заключить сделку по покупке разработчика серверных Arm-чипов Ampere за $6,5 млрд. Таким образом, японский холдинг и подконтрольная ему британская Arm готовятся составить серьёзную конкуренцию другим игрокам рынка процессоров для серверов. У AWS, Google Cloud и Microsoft Azure уже есть собственные серверные Arm-процесоры: Graviton, Axion и Cobalt 100.

04.02.2025 [13:52], Сергей Карасёв

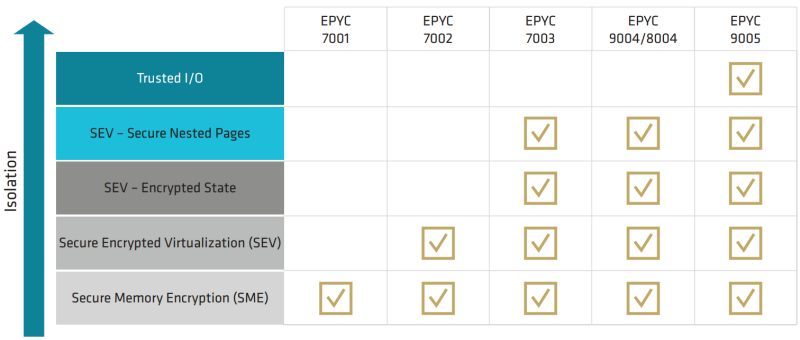

Уязвимость в процессорах AMD позволяет загрузить модифицированный микрокодСпециалисты Google Security Team сообщили об обнаружении опасной уязвимости в проверке подписи микрокода для процессоров AMD на архитектуре от Zen1 до Zen4. Уязвимость даёт возможность загрузить модифицированный микрокод, позволяющий скомпрометировать технологию виртуализации с шифрованием SEV (Secure Encrypted Virtualization) и SEV-SNP (Secure Nested Paging), а также вмешаться в работу Dynamic Root of Trust for Measurement (DRTM). Успешная эксплуатация «дыры» может привести к потере защиты конфиденциальности. Проблема заключается в том, что процессоры используют небезопасную хеш-функцию при проверке подписи обновлений микрокода. Брешь позволяет злоумышленнику с привилегиями локального администратора загрузить вредоносный микрокод CPU. Исследователи подготовили пример атаки на AMD EPYC 7B13 (Milan) и Ryzen 9 7940HS (Phoenix), в результате которой функция RDRAND вместо возврата случайного числа всегда возвращает 4. AMD подготовила патчи для защиты функций SEV в EPYC 7001 (Naples), EPYC 7002 (Rome), EPYC 7003 (Milan и Milan-X), а также EPYC 9004 (Genoa, Genoa-X и Bergamo/Siena) и Embedded-вариантов EPYC 7002/7003/9004. Для устранения проблемы требуется обновление микрокода чипов. Уязвимость получила идентификатор CVE-2024-56161. Они признана достаточно опасной — 7.2 (High) по шкале CVSS. Отмечается, что Google впервые уведомила AMD об уязвимости 25 сентября 2024 года. При этом в связи с широкой распространённостью процессоров AMD и разветвлённой сетью их поставок Google сделала единовременное исключение из стандартной политики раскрытия информации об уязвимостях и отложила публичное уведомление до 3 февраля 2025-го. Кроме того, Google не стала раскрывать полные детали о «дыре», чтобы предотвратить возможные атаки. Все подробности и инструменты будут опубликованы 5 марта 2024 года.

02.02.2025 [15:50], Владимир Мироненко

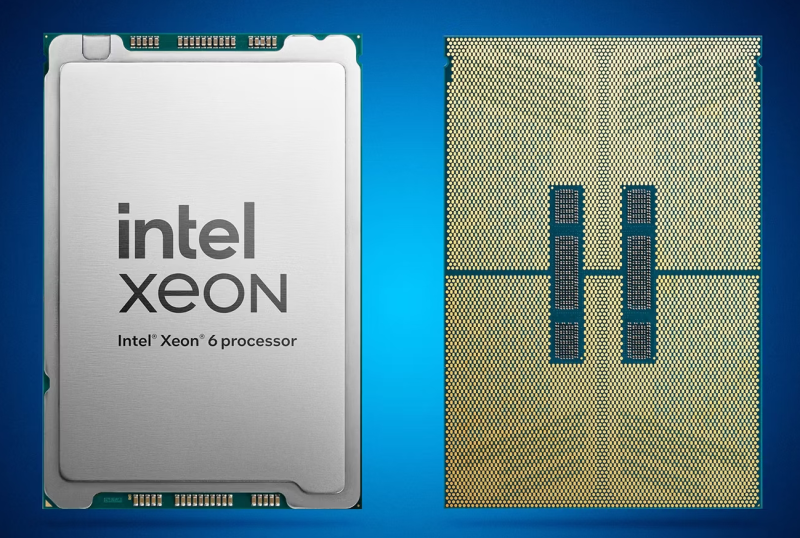

Intel отложила выпуск Xeon Clearwater Forest — рынок пока не готов, да и с упаковкой проблемыВ ходе отчёта за IV квартал 2024 года Intel рассказала о будущих продуктах и продвижении в развёртывании новых технологий. Компания сообщила, что будет наращивать производство с использованием техпроцесса Intel 18A (1,8 нм) во II половине 2025 года, но нового Xeon Clearwater Forest с E-ядрами ждать в этом году не стоит, пишет ServeTheHome. В августе 2024 года Intel заявила о запуске тестового производства Clearwater Forest и Panther Lake с использованием техпроцесса Intel 18A и новой технологии упаковки, а в сентябре продемонстрировала образец Clearwater Forest, планируя начать серийное производство этих чипов в III квартале 2025 года. 288-ядерный чип Sierra Forest-AP (6900E) предполагалось запустить в массовое производство в I квартале 2025 года. Однако в ходе квартального отчёта со-генеральный директор Intel Мишель Джонстон Холтхаус (MJ Holthaus) сообщила, что компания добилась «прогресса в (разработке) Clearwater Forest, первом серверном продукте с использованием Intel 18A», который планирует выпустить в I половине уже 2026 года. По её словам, причина переноса заключается в пока низком спросе на Xeon, «изобилующие E-ядрами». «Мы увидели, что это скорее нишевый рынок, и мы не видим, чтобы объём материализовался на нём так быстро, как мы ожидали», цитирует The Register её слова. Далее она добавила, что особенности упаковки Foveros 3D также стали причиной переноса выпуска серверного чипа на 2026 год. Как отмечает ServeTheHome, общая тенденция на рынке серверов заключается в том, что ИИ-серверы в дефиците их довольно легко продать. Вместе с тем они очень дороги, поэтом компании стоят перед выбором: купить ИИ-системы, которые прослужат ещё год-два, или же купить серверы с самыми современным CPU, чтобы консолидировать нагрузки (например, 8:1) и избавиться от старых систем. Само появление таких процессоров — одна из крупнейших революций в области серверов за более чем десять лет, сообщили в ServeTheHome. И пока что многие заказчики делают выбор в пользу ИИ-серверов. Эта тенденция влияет на других игроков рынка, включая, например, Ampere. А раз так, то нет смысла отдавать производственные мощности 18A и тратить силы на быстрое решение проблем с упаковкой Clearwater Forest, который будет не слишком востребован — пока будет достаточно и Sierra Forest. Компания также передумала выпускать на рынок ускорители Falcon Shores.

29.01.2025 [13:00], Сергей Карасёв

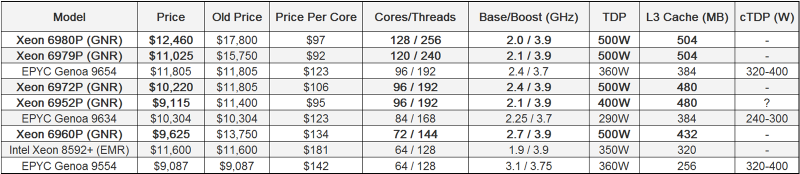

Intel незаметно снизила рекомендованные цены на процессоры Xeon 6Корпорация Intel, по сообщению ресурса Tom's Hardware, без громких анонсов существенно снизила рекомендованные цены (RCP) на серверные процессоры Xeon 6 поколения Granite Rapids. В результате, с точки зрения стоимости в пересчёте на одно вычислительное ядро изделия Intel стали дешевле конкурирующих чипов AMD EPYC Genoa. Процессоры Xeon 6900P (Granite Rapids), официально представленные 24 сентября 2024 года, стали самыми дорогими решениями с архитектурой x86 в истории. В частности, цена флагманской модели Xeon 6980P со 128 ядрами на момент выхода на рынок составляла $17 800, или приблизительно $139 в пересчёте на одно ядро. Впрочем, после обновления прайс-листа эти чипы стали гораздо более доступными. В зависимости от модели снижение цены варьируется от $1585 за 96-ядерный Xeon 6972P до $5340 за упомянутый Xeon 6980P: эти чипы теперь стоят соответственно $10 220 и $12 460. В плане процентного снижения три из пяти представителей Xeon 6 Granite Rapids подешевели на 30 %, один (Xeon 6972P) — на 13 % и один (Xeon 6952P) — на 20 %. Подчёркивается, что Intel официально не объявляла о снижении стоимости процессоров, но эти корректировки отражены в онлайн-базе данных корпорации на сайте ark.intel.com, причём сделаны они были ещё в декабре 2024 года. Таким образом, новые цены на момент написания данного материала являются действительными. Благодаря снижению стоимости 128-ядерный Intel Xeon 6980P в пересчёте на ядро стал дешевле 96-ядерного AMD EPYC 9654 — $97 против $123. То же самое касается и других представителей семейства Intel Granite Rapids в сравнении с их прямыми конкурентами AMD EPYC. Следует учесть, что речь идёт о рекомендованных ценах (Recommended Customer Price) в партиях от 1 тыс. шт. Путём снижения стоимости чипов корпорация Intel, вероятно, рассчитывает увеличить их продажи и тем самым улучшить финансовое положение. В III квартале 2024 финансового года, который был закрыт 30 сентября, компания получила $13,28 млрд выручки, что на 6 % меньше результата годичной давности. При этом Intel сообщила о чистом убытке в размере $16,99 млрд, тогда как годом ранее она завершила аналогичный квартал с чистой прибылью в размере $310 млн.

14.01.2025 [12:23], Владимир Мироненко

Qualcomm наняла главного архитектора Intel Xeon для разработки серверных Arm-процессоровРесурсу CRN стало известно, что компания Qualcomm наняла Сайлеша Коттапалли (Sailesh Kottapalli) в качестве старшего вице-президента. Ветеран Intel с 28-летним стажем, являвшийся главным архитектором серверных процессоров Xeon, сообщил в понедельник в соцсети в LinkedIn, что он присоединился к Qualcomm после ухода из Intel, поскольку разработчик чипов формирует команду для выхода на рынок CPU для ЦОД. «Возможность внедрять инновации и расти, помогая при этом расширять горизонты, была для меня чрезвычайно привлекательной — возможность, которая выпадает раз в карьере и которую я не мог упустить», — написал Коттапалли в LinkedIn. Это не первая попытка Qualcomm выйти на рынок серверных процессоров. В 2017 году компания выпустила 10-нм 48-ядерные чипы Centriq 2400, но вскоре забросила развитие этого направления. Пост Коттапалли в LinkedIn, ранее занимавшего должность ведущего инженера по чипам Itanium и Xeon в Intel, прежде чем стать главным архитектором Xeon в компании, появился чуть более чем через месяц после того, как стало известно, что у Qualcomm есть подразделение Qualcomm Data Center, которое занимается созданием «высокопроизводительного, энергоэффективного серверного решения». Разработчик чипов раскрыл эту информацию в опубликованной в декабре вакансии архитектора безопасности серверной системы на кристалле (SoC). В ней говорилось, что команда Qualcomm Data Center сосредоточена на создании «эталонных платформ» на основе Snapdragon. Подходящий соискатель возглавит разработку «системной архитектуры для конфиденциальных вычислений в продуктах ЦОД». Конфиденциальные вычисления, позволяющие изолировать данные во время их обработки, стали стандартной функцией в Intel Xeon и AMD EPYC, отметил ресурс CRN.

Источник изображения: Qualcomm Qualcomm разрабатывает серверные ИИ-ускорители Qualcomm Cloud AI, которые она поставляла таким компаниям, как AWS, HPE и Lenovo. Кроме того, компания сотрудничает с Cerebras, ещё одним разработчиком ИИ-ускорителей. Недавно стало известно о планах компании выпустить ускорители Cloud AI 80 (AIC080) для ИИ-задач. В 2021 году Qualcomm приобрела за $1,4 млрд стартап NUVIA, который изначально занимался серверного Arm-процессора Phoenix. Qualcomm утверждала, что будет использовать технологии NUVIA в ноутбуках, смартфонах, ADAS, AR/VR и т.п., но в прошлом году объявила, что также планирует продолжить разработку серверных процессоров. Из-за поглощения NUVIA между Arm и Qualcomm уже несколько лет идут судебные разбирательства.

09.01.2025 [17:57], Владимир Мироненко

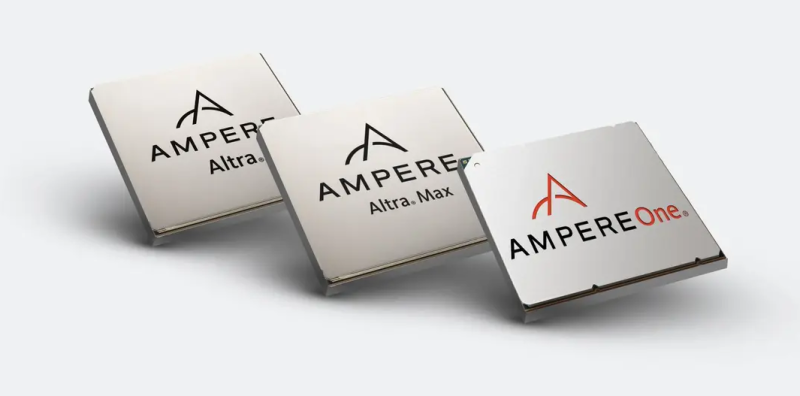

SoftBank и Arm заинтересовались покупкой Ampere, но о переговорах говорить раноЯпонский холдинг SoftBank Group вместе с британской компанией Arm, в которой он владеет 90 % акцией, проявляют интерес к покупке поддерживаемого Oracle стартапа Ampere Computing из Санта-Клары (Калифорния, США), специализирующегося на разработке серверных Arm-процессоров, пишет Bloomberg со ссылкой на информированные источники. По словам источников, на данный момент идёт обсуждение потенциальной сделки и нет гарантий, что дело дойдёт до переговоров. Возможно, что на покупку Ampere найдётся другой претендент. Ранее стало известно, что компания Ampere привлекала финансового консультанта, чтобы обсудить возможные варианты поглощения более крупной компанией. В 2021 году, когда SoftBank планировал инвестировать в компанию, Ampere Computing была оценена в $8 млрд. В какую сумму оценивается рыночная стоимость Ampere Computing на данный момент при обсуждении сделки, выяснить не удалось. Согласно документам, поданным Ampere Computing в регулирующие органы, Oracle инвестировала сотни миллионов долларов в стартап с момента его основания. Oracle заявила в прошлом году, что владеет 29 % стартапа и может снова инвестировать в компанию, чтобы получить полный контроль над производителем чипов. Oracle, по-видимому, является крупнейшим заказчиком продуктов Ampere. Arm постепенно отходит от лицензирования своих разработок, становясь полноценным производителем чипов. Привлечение инженеров Ampere, многие из которых ранее работали в подразделении Intel по производству серверных чипов, может добавить экспертные знания и импульс для выхода Arm на этот рынок, считает Bloomberg. Основатель и генеральный директор Ampere Рене Джеймс (Renee James), бывший топ-менеджер Intel, рассматривала в 2022 году возможность вывода Ampere на биржу в США. Некоторые эксперты предполагали, что компания изначально ориентировалась на поглощение одним из крупных гиперскейлеров, но в итоге AWS, Google Cloud и Microsoft Azure стали развивать собственные Arm-процесоры Graviton, Axion и Cobalt 100.

27.12.2024 [13:44], Сергей Карасёв

Стартап Ubitium создал универсальный чип на базе RISC-V с функциями CPU, GPU, DSP и FPGAСтартап Ubitium, основанный в 2024 году, анонсировал проект по созданию чипа с универсальной архитектурой, которая полностью независима от рабочих нагрузок. Речь идёт об объединении в одном изделии решений разного типа: CPU, GPU, DSP и FPGA. Отмечается, что на протяжении более 50 лет полупроводниковая промышленность занималась созданием самостоятельных центральных, графических и других процессоров, предназначенных для решения конкретных вычислительных задач. Ubitium предлагает пересмотреть данный подход, создав универсальный чип на открытой архитектуре RISC-V, который сможет одинаково хорошо справляться с нагрузками разного типа. Стартап отмечает, что основным препятствием для внедрения новых процессоров являются проприетарные ISA, которые требуют использования специализированных программных инструментов. Кроме того, трудности может создавать отсутствие зрелой программной экосистемы, предоставляющей необходимые фреймворки и приложения. Чипы Ubitium, как утверждается, будут на 100 % совместимы с RISC-V, что упростит и ускорит разработку и внедрение конечных продуктов. В отличие от традиционных процессоров со специализированными ядрами, предназначенными для определённых задач, блоки универсального чипа Ubitium могут динамически «переназначаться» для обработки широкого спектра вычислительных нагрузок, включая простую логику управления, общие вычисления, ИИ и рендеринг графики. Ещё одним преимуществом предлагаемой концепции стартап называет масштабируемость. Ubitium планирует выпускать изделия разного уровня, которые при этом будут иметь идентичную архитектуру и использовать одни и те же программные инструменты. Компания рассчитывает, что её чипы смогут применяться в самых разных сферах — от встраиваемых устройств, бытовой электроники и домашней техники до систем промышленной автоматизации, роботов и космического оборудования. По сравнению с традиционными процессорами, использование решений Ubitium, как утверждается, обеспечит повышение гибкости, снижение стоимости и ускорение разработки. Компания заявляет, что универсальный чип может обеспечить в 10–100 раз большую производительность в расчёте на доллар по сравнению с современными специализированными решениями. В команду Ubitium входят выходцы из Intel, NVIDIA и Texas Instruments. Головной офис компании находится в Дюссельдорфе (Германия). Генеральным директором является Хён Шин Чо (Hyun Shin Cho) из Университета Пердью (Purdue University). Пост технического директора занимает Мартин Форбах (Martin Vorbach), на имя которого зарегистрированы более 200 патентов. Стартап Ubitium уже привлёк $3,7 млн начального финансирования. На данный момент компания создала экспериментальную эмуляцию, которая подтверждает, что универсальный процессор работоспособен. Первые коммерческие решения планируется выпустить к 2026 году.

21.12.2024 [14:00], Сергей Карасёв

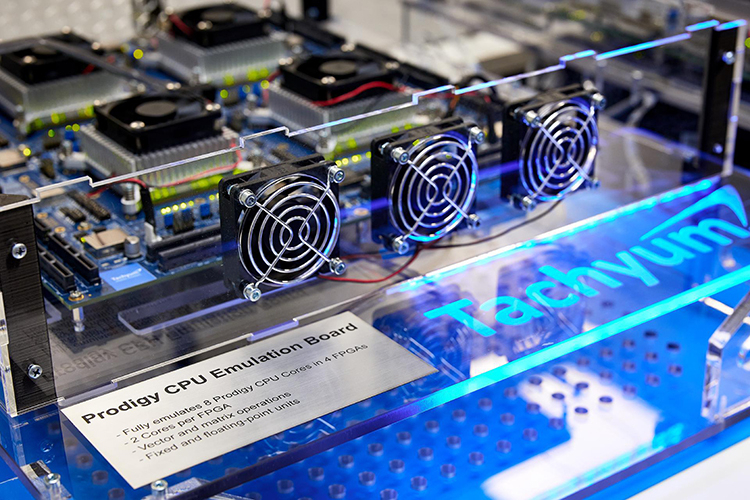

Для невыпущенного суперчипа Tachyum Prodigy выпустили 1600-страничное руководство по оптимизации производительностиСловацкая компания Tachyum, разрабатывающая процессоры Prodigy с уникальной архитектурой, объявила о выпуске руководства по оптимизации производительности этих чипов. Точнее, для FPGA-эмулятора Prodigy, поскольку самих чипов всё ещё нет. Огромный документ на 1600 страниц содержит подробную информацию о том, как в полной мере воспользоваться потенциалом новинки. Первая информация о разработке Prodigy появилась в 2019–2020 гг. Эти суперпроцессоры, как утверждается, объединяют возможности CPU, GPU и TPU. Они предназначены для решения различных ресурсоёмких задач, связанных в том числе с ИИ и машинным обучением. Сроки выпуска Prodigy несколько раз пересматривались: сначала выход чипов был перенесён с 2021-го на 2022 год, затем — на 2023 год, а впоследствии — на 2024-й. В соответствии с текущими планами Tachyum намерена начать отгрузку образов чипов в 2025 году.

Источник изображения: Tachyum Подготовленное руководство для изделий Prodigy, как заявляет компания, содержит рекомендации по созданию высокопроизводительного ПО для этой платформы. Документ описывает конкретные методы оптимизации, включая управление ограничениями диспетчеризации, улучшение процедур работы памяти и пр. Кроме того, описаны способы обработки операций кеширования и доступа к специальным регистрам для тонкой настройки с целью достижения максимальной производительности. В руководстве рассматриваются особенности чипов. Архитектура набора инструкций Prodigy (ISA) представляет собой смесь RISC и CISC, но не включает какие-либо сложные и/или длинные и неэффективные инструкции переменной длины. Все инструкции имеют ширину 32 или 64 бит, а некоторые из них содержат функции доступа к памяти для дальнейшего повышения производительности. Изделия Prodigy объединяют до 192 ядер с тактовой частотой до 5 ГГц и выше. Реализованы 16 каналов памяти DDR5-7200 с возможностью использования до 32 Тбайт ОЗУ в расчёте на процессорный разъём. Поддерживаются 96 линий PCIe 5.0. Планируемая технология производства — 5 нм. В конце 2023 года Tachyum получила заказ на поставку чипов Prodigy для создания суперкомпьютера с ИИ-производительностью до 8 Зфлопс.

12.12.2024 [12:50], Сергей Карасёв

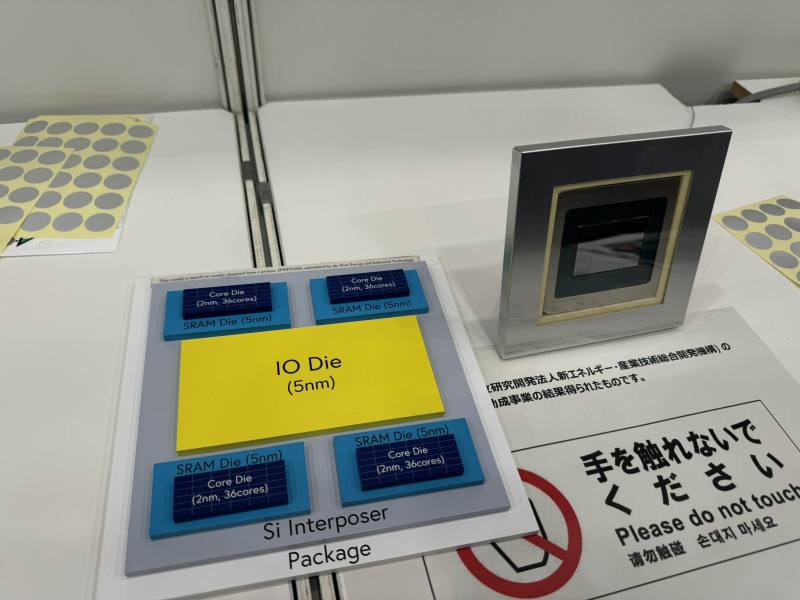

144-ядерный Arm-процессор Fujitsu Monaka получит 3.5D-упаковку от BroadcomКорпорация Fujitsu, по сообщению ресурса Tom's Hardware, продемонстрировала прототип серверного процессора Monaka для дата-центров. Это изделие проектируется с прицелом на НРС-платформы, а также на ЦОД, ориентированные на решение ресурсоёмких задач в области ИИ. О проекте Monaka стало известно в начале 2023 года. Тогда говорилось, что разработка изделия является частью программы, курируемой японской Организацией по развитию новых энергетических и промышленных технологий (NEDO). Процессор основан на архитектуре Arm с набором инструкций Armv9-A и поддержкой масштабируемых векторных расширений SVE2. Как теперь сообщается, для чипа Monaka предусмотрено использование технологии Broadcom 3.5D eXtreme Dimension System in Package (SiP). Конструкция процессора включает четыре 36-ядерных вычислительных чиплета, изготовленных по 2-нм технологии TSMC. Таким образом, суммарное количество ядер достигает 144. Эти чиплеты монтируются поверх «плиток» SRAM с использованием гибридного медного соединения (HCB). Блоки SRAM, выполняющие функции кеш-памяти, производятся по 5-нм техпроцессу TSMC. Кроме того, имеется крупный чиплет ввода-вывода, в состав которого входят контроллеры DDR5 (12 каналов) и PCI Express 6.0/CXL 3.0. Процессор Monaka нацелен на широкий спектр рабочих нагрузок в дата-центрах. Для чипа не предусмотрено использование памяти HBM — вместо этого будет применяться DDR5, возможно, в реализациях MR-DIMM и MCR-DIMM. Упомянуты расширенные функции безопасности, включая Confidential Computing Architecture (CCA). Monaka предстоит конкурировать с процессорами AMD EPYC и Intel Xeon. Одним из главных преимуществ нового изделия перед этими чипами, по всей видимости, станет более высокая энергетическая эффективность. Fujitsu намерена начать продажи Monaka в течение 2027 финансового года, который у компании продлится с 1 апреля 2026-го до 31 марта 2027-го.

11.12.2024 [23:47], Владимир Мироненко

BadRAM: для обхода защиты виртуальных машин в процессорах AMD EPYC достаточно оборудования стоимостью всего $10

amd

cpu

ddr4

ddr5

dram

epyc

hardware

виртуализация

информационная безопасность

уязвимость

шифрование

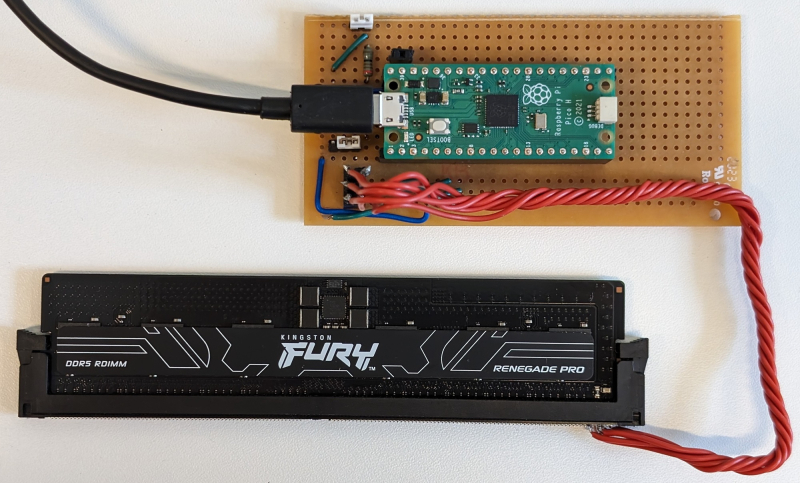

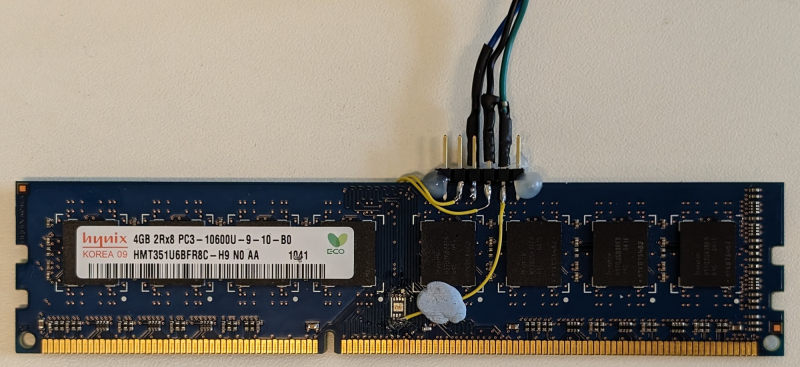

Исследователи Лёвенского католического университета (Бельгия), Любекского университета (Германия) и Бирмингемского университета (Великобритания) обнаружили, что система защиты виртуальных машин от атак с использованием вредоносного гипервизора AMD SEV-SNP (Secure Nested Paging), не так безопасна, как утверждает разработчик, пишет The Register. Технологии Secure Encrypted Virtualization (SEV) предоставляют доверенную среду исполнения (TEE), призванную обеспечить защиту виртуальных машин от незаконных попыток вмешательства со стороны тех, кто имеет доступ к оборудованию ЦОД. Механизм SEV-SNP реализован в процессорах AMD EPYC, начиная с 7003 (Milan). Аналогичные механизмы есть и у конкурентов: Intel Software Guard Extensions (SGX) и Trusted Domain Extensions (TDX), а также Arm Confidential Compute Architecture (CCA). Все эти технологии отвечают за шифрование памяти и изоляцию ресурсов. Исследователи разработали способ обхода SEV-SNP, который они назвали BadRAM (CVE-2024-21944 и AMD-SB-3015). Для атаки требуется оборудование стоимостью около $10, включая Raspberry Pi Pico, разъём DDR и батарею на 9 В. Атака BadRAM требует наличие физического доступа к оборудованию. Она основана на манипуляциях с чипом SPD (Serial Presence Detect), который передаёт данные о модуле DDR4/DDR5 во время загрузки системы. Манипулируя SPD, злоумышленники создают адреса-фантомы для физической памяти, благодаря которым можно незаметно получить доступ к данным в виртуальной машине. «Мы удваиваем видимый в системе объём DIMM, чтобы обмануть контроллер памяти CPU и заставить его использовать дополнительные «фантомные» биты адресации, — объясняют авторы исследования. — Два разных физических адреса теперь ссылаются на одно и то же местоположение DRAM». С помощью таких фантомов злоумышленники могут обойти защиту памяти, раскрывая конфиденциальные данные или вызывя сбои. BadRAM позволяет подделать критически важные отчёты удалённой аттестации и вставлять необнаруживаемые бэкдоры в любую виртуальную машину, защищённую SEV-SNP. Атака может быть реализована и без физического доступа к оборудованию, поскольку некоторые поставщики DRAM оставляют чип SPD разблокированным, что противоречит спецификациям JEDEC. Авторы исследования обнаружили по крайней мере два DDR4-модуля Corsair без должной защиты SPD. Память DDR3 тоже может быть взломана путём замены чипа SPD. «BadRAM полностью подрывает доверие к технологии защищённой зашифрованной виртуализации AMD (SEV-SNP), которая широко используется крупными поставщиками облачных услуг, включая Amazon AWS, Google Cloud и Microsoft Azure», — сообщил The Register Джо Ван Балк (Jo Van Bulck), профессор лаборатории DistriNet на кафедре компьютерных наук KU Leuven. Исследователи отметили, что решения SGX и TDX Intel не имеют такой уязвимости, поскольку в них реализованы контрмеры против создания псевдонимов (alias) памяти. Arm CCA, судя по спецификации, тоже не имеет проблем, но для проверки этого у исследователей не было коммерческих чипов. Полный доклад об атаке исследователи планируют представить в мае 2025 года на конференции IEEE Symposium on Security and Privacy. Исследователи уведомили AMD о найденных проблемах в феврале 2024 года. «AMD рекомендует использовать модули памяти, которые блокируют SPD, а также следовать передовым практикам в области физической безопасности систем. AMD также выпустила обновления прошивок защиты от уязвимости», — сообщили в AMD ресурсу The Register в ответ на просьбу прокомментировать публикацию исследователей. |

|