Материалы по тегу: cpu

|

20.11.2024 [10:56], Сергей Карасёв

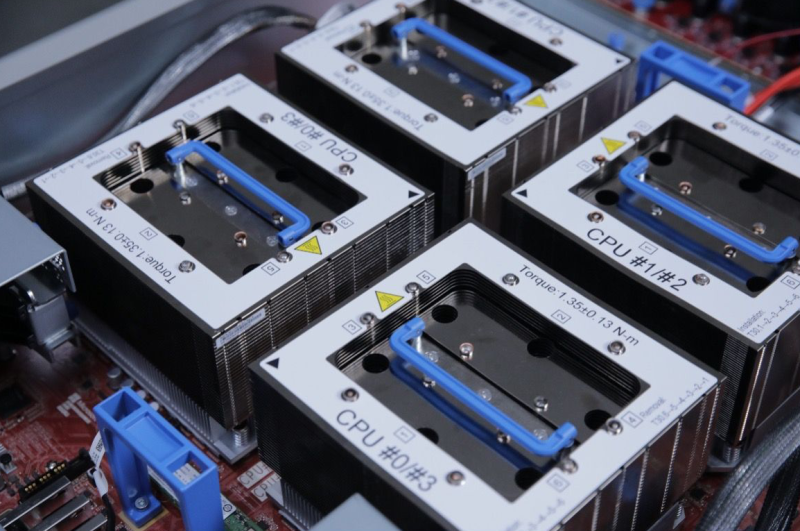

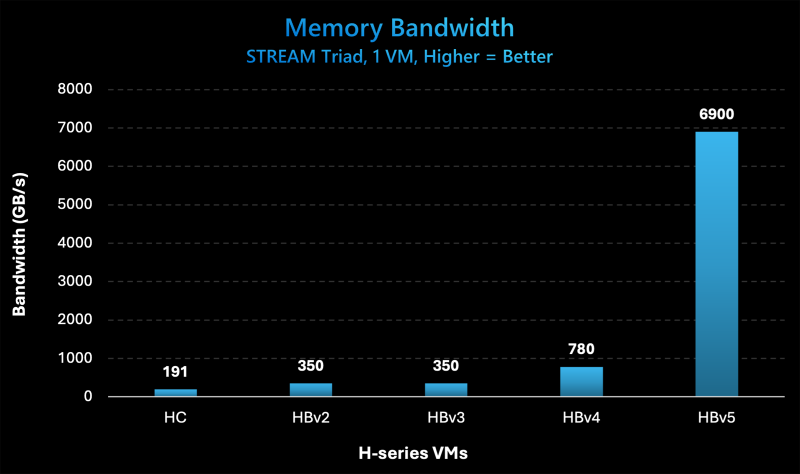

Microsoft представила инстансы Azure HBv5 на основе уникальных чипов AMD EPYC 9V64H с памятью HBM3Компания Microsoft на ежегодной конференции Ignite для разработчиков, IT-специалистов и партнёров анонсировала облачные инстансы Azure HBv5 для HPC-задач, которые предъявляют наиболее высокие требования к пропускной способности памяти. Новые виртуальные машины оптимизированы для таких приложений, как вычислительная гидродинамика, автомобильное и аэрокосмическое моделирование, прогнозирование погоды, исследования в области энергетики, автоматизированное проектирование и пр. Особенность Azure HBv5 заключается в использовании уникальных процессоров AMD EPYC 9V64H (поколения Genoa). Эти чипы насчитывают 88 вычислительных ядер Zen4, тактовая частота которых достигает 4 ГГц. Ближайшим родственником является изделие EPYC 9634, которое содержит 84 ядра (168 потоков) и функционирует на частоте до 3,7 ГГц. По данным ресурса ComputerBase.de, чип EPYC 9V64H также фигурирует под именем Instinct MI300C: по сути, это процессор EPYC, дополненный памятью HBM3. При этом клиентам предоставляется возможность кастомизации характеристик. Отметим, что ранее x86-процессоры с набортной памятью HBM2e были доступны в серии Intel Max (Xeon поколения Sapphire Rapids). Каждый инстанс Azure HBv5 объединяет четыре процессора EPYC 9V64H, что в сумме даёт 352 ядра. Система предоставляет доступ к 450 Гбайт памяти HBM3, пропускная способность которой достигает 6,9 Тбайт/с. Задействован интерконнект NVIDIA Quantum-2 InfiniBand со скоростью передачи данных до 200 Гбит/с в расчёте на CPU. Применены сетевые адаптеры Azure Boost NIC второго поколения, благодаря которым пропускная способность сети Azure Accelerated Networking находится на уровне 160 Гбит/с. Для локального хранилища на основе NVMe SSD заявлена скорость чтения информации до 50 Гбайт/с и скорость записи до 30 Гбайт/с. Отмечается, что по показателю пропускной способности памяти виртуальные машины Azure HBv5 примерно в 8 раз превосходят новейшие альтернативы bare-metal и cloud, в 20 раз опережают инстансы Azure HBv3 и Azure HBv2 (на базе EPYC Milan-X и EPYC Rome) и в 35 раз обходят HPC-серверы возрастом 4–5 лет, жизненный цикл которых приближается к завершению. Машины Azure HBv5 станут доступны в I половине 2025 года.

19.11.2024 [11:47], Сергей Карасёв

Esperanto и NEC займутся созданием HPC-решений на базе RISC-VСтартап Esperanto Technologies и корпорация NEC объявили о заключении соглашения о сотрудничестве в области НРС. Речь идёт о создании программных и аппаратных решений следующего поколения, использующих открытую архитектуру RISC-V. Напомним, Esperanto разрабатывает высокопроизводительные RISC-V-чипы для задач НРС и ИИ. Первым продуктом компании стало изделие ET-SoC-1, которое объединяет 1088 энергоэффективных ядер ET-Minion и четыре высокопроизводительных ядра ET-Maxion. Решение предназначено для инференса рекомендательных систем, в том числе на периферии. В августе 2023 года стало известно о подготовке чипа ET-SoC-2 с высокопроизводительными ядрами RISC-V с векторными расширениями. В рамках соглашения о сотрудничестве, как отмечается, будут объединены опыт и экспертизы NEC в области проектирования суперкомпьютеров и создания специализированного софта для HPC-задач с технологиями Esperanto в сфере высокопроизводительных энергоэффективных чипов на основе набора инструкций RISC-V. При этом упоминаются достижения NEC по направлению векторных процессоров: японская компания проектировала уникальные изделия SX-Aurora, но их разработка была остановлена в 2023 году.

Источник изображения: Esperanto «Используя глубокий опыт и экспертные знания NEC в области HPC, а также открытый набор инструкций RISC-V в сочетании с вычислительной технологией Esperanto, мы сможем разрабатывать масштабируемые и эффективные решения для ИИ и высокопроизводительных вычислений», — отметил Арт Свифт (Art Swift), президент и генеральный директор Esperanto.

11.11.2024 [11:43], Сергей Карасёв

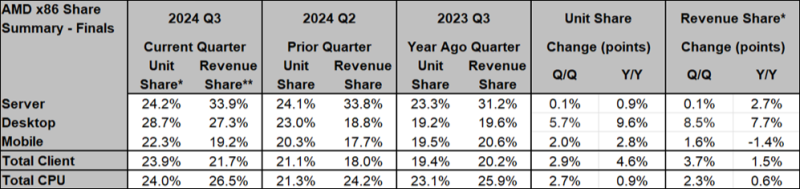

AMD наращивает долю на рынке серверных чипов на фоне проблем IntelКомпания AMD быстро укрепляет позиции на рынке процессоров с архитектурой х86. Причём, как сообщает ресурс Tom's Hardware, ссылаясь на данные аналитиков Mercury Research, речь идёт обо всех ключевых сегментах — серверном, настольном и мобильном. По итогам III квартала 2024 года доля AMD на глобальном рынке CPU с учётом всех сегментов достигла 24,0 % в штучном выражении. Для сравнения: во II четверти 2024-го этот показатель равнялся 21,3 %, а годом ранее — 23,1 %. Если рассматривать продажи в денежном исчислении, то AMD заняла 26,5 % против 24,2 % во II квартале текущего года и 25,9 % в III квартале 2023-го. AMD наращивает долю на рынке серверных чипов: показатель достиг 24,2 % в натуральном выражении. Во II четверти 2024 года компания контролировала 24,1 % сегмента, а годом ранее — 23,3 %. Если оценивать отгрузки в деньгах, то доля AMD зафиксирована на отметке 33,9 %. Кварталом ранее это значение составляло 33,8 %, а год назад — 31,2 %. В исследовании отмечается, что Intel остаётся лидером в области серверных процессоров с архитектурой х86: доля корпорации в III квартале 2024 года равна 75,8 %. Тем не менее, AMD смогла реализовать больше чипов высокого класса, на что указывает более высокая доля рынка в денежном выражении по сравнению с натуральным. Кроме того, впервые подразделение дата-центров AMD превзошло по выручке группу DCAI в составе Intel — $3,549 млрд против $3,3 млрд по итогам III квартала 2024 года. Отчёт не включает заказные чипы AMD, которые устанавливаются в игровые консоли, а также процессоры для оборудования IoT. Успехи AMD отчасти связаны с проблемами Intel, которая оказалась в очень сложном положении: она борется с жёсткой конкуренцией, а прогресс в сфере ИИ оставляет желать лучшего. Intel вынуждена сокращать тысячи сотрудников по всему миру, уменьшать офисные площади и отказываться от неактуальных продуктов ради улучшения финансовых показателей.

11.11.2024 [11:29], Сергей Карасёв

США запретили TSMC выпускать передовые чипы для китайских ИИ-компанийTSMC, по сообщению The Register, полностью прекратит выпуск передовых изделий для китайских заказчиков, которые занимаются разработкой аппаратных ИИ-решений, включая ускорители на базе GPU. Данная мера, как утверждается, продиктована необходимостью соблюдения экспортных требований США. Власти США последовательно вводят различные санкции, призванные ограничить возможности китайской полупроводниковой индустрии. Речь идёт о закупках чипов NVIDIA, памяти HBM и других компонентов. А нидерландской компании ASML запрещено поставлять в Китай оборудование для DUV-литографии, на котором можно изготавливать 5- и 7-нм продукцию. Теперь новые ограничительные меры в отношении клиентов из КНР вводит TSMC. Этот контрактный производитель объявил о том, что с 11 ноября 2024 года прекращает отгружать чипы, произведённые по 7-нм и более совершенным технологиям, китайским заказчикам, которые занимаются разработкой ИИ-устройств и GPU. Напомним, что в октябре TSMC уведомила американские власти о том, что некий китайский клиент, по всей видимости, пытается обойти экспортный контроль в отношении Huawei, размещая заказы на изделия, схожие с ИИ-ускорителем Ascend 910B. Это продукт был разработан Huawei в качестве альтернативы NVIDIA A100. Решение Ascend 910B представляет собой следующее поколение 7-нм чипа Ascend 910. По имеющейся информации, TSMC, следуя экспортным ограничения США, прекратила все поставки изделий этому неназванному клиенту. Решение TSMC ограничит возможности китайских компаний по использованию технологий с нормами 7-нм и менее при создании ИИ-устройств. Вместе с тем, подчёркивается, что правила не распространяются на китайских клиентов, которые заказывают у TSMC 7-нм чипы для других приложений, таких как мобильные устройства и системы связи. Как отмечает TrendForce, решение TSMC «отражает осторожную позицию гиганта контрактного производства в глобальной цепочке поставок полупроводников на фоне разгорающейся войны в сфере микрочипов между двумя мировыми сверхдержавами».

25.10.2024 [13:24], Сергей Карасёв

От тостера до ЦОД: RISC-V International ратифицировала унифицированный профиль RVA23 для процессоров будущегоОрганизация RISC-V International объявила о ратификации профиля RVA23. Это значимое событие, которое, как ожидается, поможет открытой архитектуре RISC-V укрепить позиции по отношению к Arm и x86, избегая при этом потенциальных проблем, связанных с лицензированием. Профили RVA необходимы для обеспечения переносимости ПО между различными аппаратными реализациями. Таким образом, разработчики софта могут избежать привязки к конкретному поставщику аппаратных решений. Иными словами, одно и то же приложение сможет функционировать на любых устройствах, оснащённых процессорами с архитектурой RISC-V. Профиль RVA23 стандартизирует набор инструкций ISA (Instruction Set Architecture). Ключевой задачей является устранение фрагментации внутри экосистемы RISC-V. Отмечается, что в рамках ратификации профиль RVA23 прошёл длительный процесс разработки, рассмотрения и утверждения в многочисленных рабочих группах.

Источник изображения: pixabay.com RVA23 делает обязательными такие функции, как векторные операции, инструкции с плавающей запятой и атомарные инструкции, которые необходимы во многих сферах, включая НРС, машинное обучение и ИИ. В частности, векторные расширения ускоряют рабочие нагрузки с интенсивными математическими расчётами, включая криптографию, (де-)компрессию, обучение ИИ и пр. Важным компонентом RVA23 является поддержка гипервизоров. Это позволяет виртуализировать корпоративные рабочие нагрузки как на локальных серверах, так и в облаке. Таким образом, может быть ускорена разработка оборудования, ОС и прикладных программ для архитектуры RISC-V. Поддержка виртуализации также улучшит безопасность мобильных приложений путём разделения защищённых и незащищённых компонентов.

25.10.2024 [00:35], Игорь Осколков

NVIDIA за год отгрузила более 1 млрд RISC-V ядерВ рамках саммита RISC-V 2024 компания NVIDIA поделилась любопытной статистикой — за год в составе GPU и других ускорителей она отгрузила более 1 млрд ядер RISC-V собственной разработки, передаёт TechPowerUp. Они входят в состав GSP (GPU System Processor), который отвечает за управление GPU и иные служебные функции. В состав GSP входит от 10 до 40 ядер, в зависимости от сложности чипа, которым он управляет. Компания переключилась на разработку нового GSP на базе RISC-V в 2016 году. До этого более десяти лет NVIDIA использовала для GSP проприетарный процессор Falcon, возможностей и гибкости которого со временем стало не хватать. Вместо покупки и доработки готовых ядер от сторонних вендоров (Arm, MIPS, Synopsys ARC) или попыток улучшить Falcon, компания решила обратиться к открытой архитектуре RISC-V и к настоящему моменту разработала три типа ядер. Так, NV-RISCV32 представляет собой самое простое 32-бит ядро без внеочередного исполнения, работающее на частоте до 1,8 ГГц и имеющее производительность до 1,8 CoreMark/МГц. NV-RVV является NV-RISCV32 с 1024-бит векторными расширениями. А NV-RISCV64 — это уже более серьёзное 64-бит ядро с поддержкой внеочередного исполнения и SMP, частотой 2 ГГц и производительностью 5 CoreMark/МГц. Кроме того, NVIDIA разработала более 20 расширений ISA под специфические задачи. Впервые GSP на базе RISC-V появился в поколении Turing в 2018 году. Сейчас GSP отвечает за управление питанием и ресурсами ускорителя, безопасность, межчиповое взаимодействие, управление видеокодеками, вывод видео, работу с NVDLA и т.д. Google выбрала похожий путь — в её ИИ-ускорителях TPU используются ядра SiFive. Впрочем, сейчас есть уже и «большие» ИИ-ускорители, построенные исключительно на ядрах RISC-V: Meta✴ MTIA первого и второго поколений, InspireSemi Thunderbird, Tenstorrent Wormhole и Grayskull, а также Esperanto ET-SoC-1 и ET-SoC-2.

11.10.2024 [00:35], Владимир Мироненко

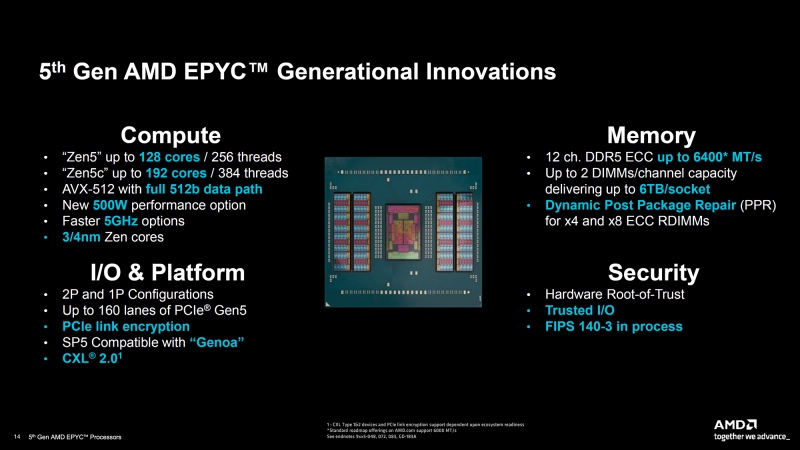

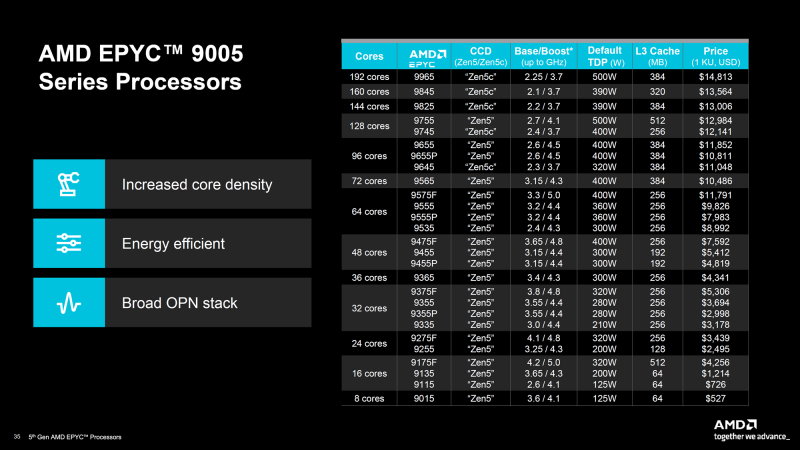

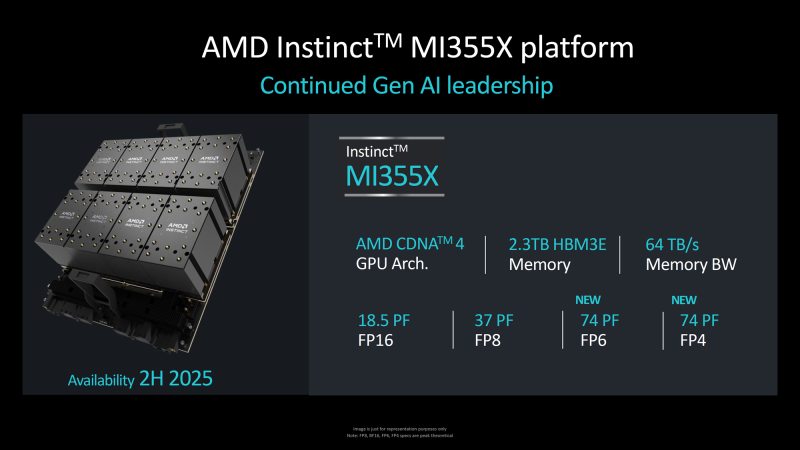

AMD представила серверные процессоры EPYC 9005 Turin и ускорители Instinct MI325XКомпания AMD представила ряд новых решений, включая серверные процессоры серии EPYC 9005 (Turin) и ускорители Instinct MI325X, которые, по словам компании, устанавливают новый стандарт производительности для ЦОД. Процессоры AMD EPYC 5-го поколения под кодовым названием Turin производятся с использованием техпроцесса 3 нм и 4 нм TSMC. Они предлагают тактовую частоту до 5,0 ГГц и от 8 до 192 ядер. AMD сообщила, что новая серия обеспечивает прирост показателя IPC на 17 % по сравнению с EPYC Genoa для корпоративных и облачных рабочих нагрузок и до 37 % в ИИ- и HPC-задачах по сравнению с Zen 4. Серия AMD EPYC 9005 включает 64-ядерный AMD EPYC 9575F, специально разработанный для ИИ-платформ на базе ускорителей, которым требуются максимальные возможности CPU. Турбочастота может достигать 5 ГГц, тогда как решение конкурента ограничено 3,8 ГГц — он до 28 % быстрее обрабатывает и передаёт данные ускорителям, что важно для требовательных рабочих нагрузок ИИ. В серии AMD EPYC 9005 доступны две версии чипов: 128-ядерная версия с классическими ядрами Zen5 и 192-ядерная версия с Zen5c. Оба варианта EPYC 9005 используют сокет SP5 и совместимы с некоторыми существующими платформами для Genoa (Zen4). Новинки поддерживают 12-канальную память DDR5-6400, а также предлагают полноценные обработку инструкций AVX-512 (целиком 512 бит за раз). Как сообщает компания, флагманский процессор серии EPYC 9965 имеет 192 ядра Zen5c и тактовую частоту до 3,7 ГГц. Серверы на базе процессоров AMD EPYC 9965 обеспечивают по сравнению с серверами на базе процессоров Intel Xeon Platinum 8592+ (Emerald Rapids):

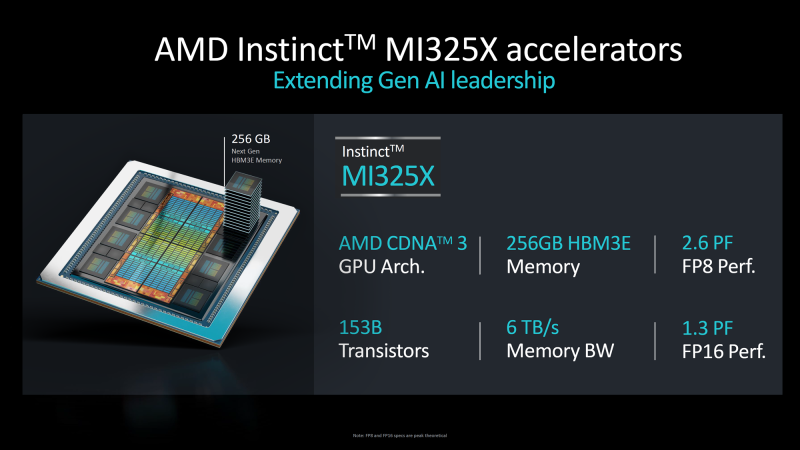

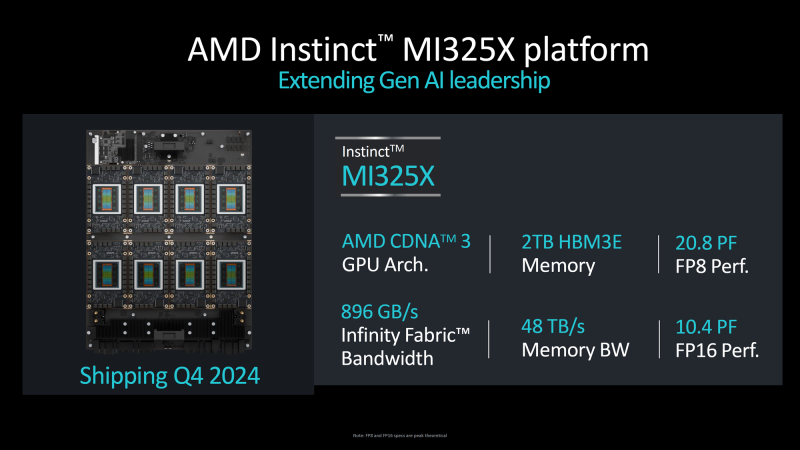

Также сообщается, что в сравнении с конкурентом 192-ядерный процессор EPYC 9965 обеспечивает до 3,7 раза большую производительность на end-to-end рабочих нагрузках ИИ, таких как TPCx-AI, которые имеют решающее значение для эффективного подхода к генеративному ИИ. Что касается AMD Instinct MI325X, то новый ускоритель, построенный на архитектуре AMD CDNA 3, имеет 256 Гбайт памяти HBM3e с пропускной способностью 6,0 Тбайт/с, что соответственно в 1,8 и 1,3 раза больше, чем у NVIDIA H200. Ускоритель обеспечивает 2,6 Пфлопс производительности в режиме FP8, 1,3 Пфлопс производительности в режиме FP16. Как утверждает AMD, по сравнению с H200 новый ускоритель в 1,3 раза быстрее в задачах инференса ИИ-модели Mistral 7B (FP16), в 1,2 раза — Llama 3.1 70B (FP8), в 1,4 раза — Mixtral 8x7B (FP16). Ускорители AMD Instinct MI325X будут доступны с I квартала 2025 года. AMD также анонсировала следующее поколение ускорителей серии AMD Instinct MI350 на основе архитектуры AMD CDNA 4, разработанные для обеспечения 35-кратного улучшения производительности инференса по сравнению с ускорителями на базе AMD CDNA 3. Серия AMD Instinct MI350 получит до 288 Гбайт памяти HBM3e на ускоритель и поддержку форматов FP6/FP4. Новинка будет доступна во II половине 2025 года.

04.10.2024 [13:16], Сергей Карасёв

Драгоценные «камни»: цена Intel Xeon Granite Rapids достигает рекордных $17 800Стала известна стоимость процессоров Intel Xeon 6900P семейства Granite Rapids, которые были официально представлены 24 сентября нынешнего года. Цена чипов достигает $17 800 — это самый высокий показатель для современных изделий с архитектурой x86. Серия Xeon 6 Granite Rapids включает процессоры, насчитывающие до 128 ядер. Чипы несут на борту до 504 Мбайт кеша, а показатель TDP достигает 500 Вт. Обеспечивается поддержка памяти DDR5-6400 и MCR-8800, до 96 линий PCIe Gen 5.0/CXL 2.0 и до 6 линий UPI 2.0. Как сообщается, в $17 800 оценён флагманский процессор Xeon 6980P со 128 ядрами (приблизительно $139 в пересчёте на одно ядро). Для сравнения, чип предыдущего поколения Xeon Platinum 8592+ (Emerald Rapids) на старте продаж имел цену в $11 600 (спецверсия для СЖО стоила $12 400). Вместе с тем 128-ядерный AMD EPYC 9754 (Bergamo) сразу после выхода предлагался за $11 900, а 96-ядерный EPYC 9684X (Genoa-X) — за $14 756.

Источник изображения: Intel Названа также стоимость других представителей Intel Xeon 6900P. В частности, 120-ядерный Xeon 6979P оценён в $15 750, что эквивалентно $131 за ядро. Модель Xeon 6972P с 96 ядрами стоит $14 600, или $152 за ядро. 72-ядерный Xeon 6960P обойдётся в $13 750 ($191 за ядро). Процессор Xeon 6952P с 96 ядрами стоит $11 400, или $119 в пересчёте на ядро. Указанные цифры являются прейскурантными. Отмечается, что гиперскейлеры и крупные клиенты получают процессоры по цене значительно ниже той, что указана в официальных прайс-листах. То же самое касается и процессоров AMD.

02.10.2024 [10:24], Сергей Карасёв

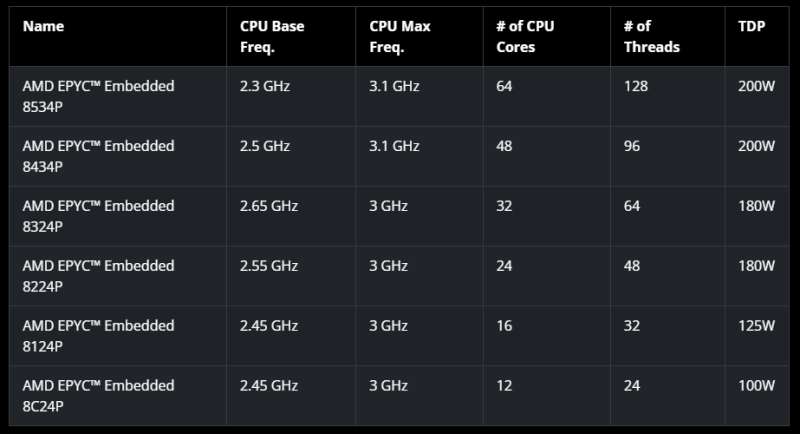

AMD представила процессоры EPYC Embedded 8004: до 64 ядер Zen 4c, 6 каналов DDR5-4800 и 96 линий PCIe 5.0Компания AMD анонсировала процессоры EPYC Embedded 8004 (Siena) для встраиваемых систем с интенсивными вычислительными нагрузками. Чипы подходит для сетевого оборудования, маршрутизаторов, устройств обеспечения безопасности, корпоративных и облачных теплых/холодных хранилищ и промышленных периферийных изделий. В основу процессоров положена оптимизированная архитектура Zen 4 — Zen 4c, которая отличается повышенной энергоэффективностью. В семейство EPYC Embedded 8004 вошли чипы с 12, 16, 24, 32, 48 и 64 ядрами, поддерживающими технологию многопоточности. Показатель TDP варьируется от 100 до 200 Вт. Базовая частота у новинок варьируется от 2,3 до 2,65 ГГц, а максимальная частота составляет 3,0 или 3,1 ГГц. Процессоры поддерживают шесть каналов памяти DDR5-4800, максимальный объём которой может составлять 1152 Гбайт в конфигурации 12 × 96 Гбайт. Доступны 96 линий PCIe 5.0. Среди особенностей отмечено наличие DMA-движка, NTB, возможность сброса DRAM на NVMe-накопитель для защиты данных в случае потери питания, поддержка двух SPI ROM (для BIOS и безопасного загрузчика), поддержка Yocto Linux, а также наличие механизма криптографической аттестации процессора, который препятствует неавторизованной замене CPU. Новые чипы имеют настраиваемый показатель cTDP (configurable TDP). У младшей версии EPYC Embedded 8C24P с 12 ядрами стандартное значение в 100 Вт может быть снижено до 70 Вт, тогда как у старшей модификации EPYC Embedded 8534P с 64 ядрами стандартную величину в 200 Вт можно регулировать в диапазоне от 155 до 225 Вт. Процессоры EPYC Embedded 8004 выполнены в компактном форм-факторе SP6, который на 19 % меньше по сравнению с EPYC Embedded 9004. Жизненный цикл чипов составляет семь лет.

27.09.2024 [21:50], Руслан Авдеев

Ampere создаст кастомные Arm-процессоры для UberКомпания Uber намерена использовать кастомные Arm-процессоры Ampere Computing в облаке Oracle Cloud Infrastructure (OCI). В частности, компании займутся оптимизацией чипов для ИИ-задач. До недавнего времени Uber использовала преимущественно собственные ЦОД, но в 2022 году приняла решение перенести большую часть задач в облака. С ростом количества ЦОД и зон доступности управлять IT-инфраструктурой Uber становилось всё сложнее. На ввод в эксплуатацию новой зоны порой требовались месяцы и сотни специалистов, поскольку управление серверами происходило чуть ли не «вручную», а инструменты автоматизации часто подводили. Рассмотрев различные варианты развития, Uber постепенно пришла к сотрудничеству с Ampere, Goolge и Oracle. А в феврале 2023 года компания подписала крупные семилетние облачные контракты с Google и Oracle. По данным Uber, водители и курьеры компании выполняют более 30 млн заказов ежедневно. Для этого требуется большая IT-инфраструктура, например, для оптимизации маршрутов, в том числе с применением ИИ-технологий — ежесекундно к ИИ-моделям приходит 15 млн запросов. По оценкам Uber и Ampere, перенос нагрузок в OCI не только снизил инфраструктурные затраты, но и уменьшил энергопотребление на 30 %. Сейчас компании совместно работают над новыми чипами, выявляя, какие изменения в микроархитектуру стоит внести, чтобы будущие процессоры оптимально подходили для задач Uber. Собственные Arm-процессоры разрабатывают AWS, Google Cloud и Microsoft Azure — Graviton, Axion и Cobalt 100 соответственно. Однако кастомизацией под конкретного клиента, пусть даже крупного, они не занимаются. Тем не менее, эксперты IDC считают, что облачные клиенты безусловно выиграют от совместной подготовки с разработчиками чипов новых полупроводниковых решений. Клиенты могут обладать специфическими знаниями и интеллектуальной собственностью, но как правило не имеют возможности самостоятельно вывести на рынок готовый продукт. Сейчас Uber переносит тысячи микросервисов, многочисленные платформы хранения данных и десятки ИИ-моделей в OCI. Компания уже перевела значительную часть бессерверных рабочих нагрузок на платформы на базе Ampere. Впрочем, дело не ограничивается только Ampere — компания также активно использует инстансы на базе чипов AMD. |

|