Лента новостей

|

01.08.2022 [15:52], Руслан Авдеев

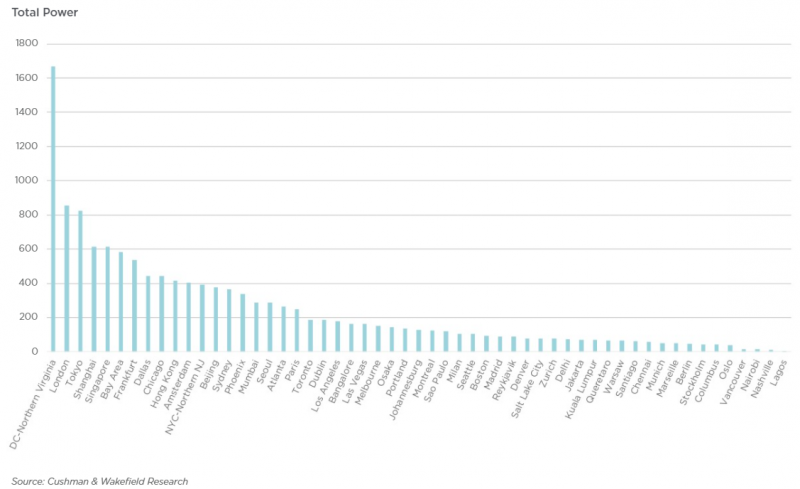

На крупнейшем в мире рынке ЦОД наметился катастрофический недостаток электроэнергии — дата-центрам не хватает ЛЭПРынок ЦОД Северной Вирджинии продолжают преследовать неприятности. Помимо того, что местные жители активно выступают против старых и новых дата-центров, в местной округе наметилась масштабная нехватка электроэнергии. Как сообщает The Register, в регионе буквально не хватает линий электропередач для снабжения всех ЦОД энергией. По данным Digital Realty, владеющей и обслуживающей более 290 ЦОД, местная энергоснабжающая компания Dominion Energy разослала оповещение ключевым местным потребителям, сообщив, что проблемы с электроснабжением в регионе закончатся не раньше 2026 года. При этом проблема заключается не в нехватке генерирующих мощностей, а именно в дефиците линий электропередач для достаточного энергообеспечения ЦОД. Текущая ёмкость дата-центров в штате составляет порядка 1,7 ГВт.

Источник изображения: Matthew Henry/unsplash.com Округ Лаудон (Loudoun County) фактически является крупнейшим в мире хабом для дата-центров с общей полезной площадью ЦОД в миллионы квадратных метров. Округ нередко называют «ключевым игроком» в мировой цифровой экономике. Одни только налоги на недвижимость от сектора ЦОД должны составить в фискальном 2023 году почти $600 млн — этого достаточно, чтобы покрыть все расходы властей округа. Проблемы с энергоснабжением могут означать, что многие планируемые проекты переедут в соседние округа Принс-Уильям (Prince William) и Фокир (Fauquier), а то и вовсе в соседний штат Мэриленд. Dominion Energy как минимум частично обслуживает и Принс-Улильям, а вот округ Фредерик в Мэриленде подключен к другой энергосети.

Источник изображения: Álvaro Serrano/unsplash.com Известно, что беспрецедентный рост нагрузки на сеть Dominion начался в 2018 году на фоне стремительного развития дата-центров и всё ещё не остановился, поэтому в существующие планы развития энергосетей придётся вносить корректировки. На днях Dominion Energy признала, что не сможет обслуживать потребности города Эшберна (Ashburn) в округе Лаудон, где расположена т.н. «Аллея дата-центров». Это будет означать не только остановку уже стартовавших многомиллиардных проектов строительства ЦОД, но и снижение налоговых поступлений. Как сообщает портал DataCenter Dynamics, по прогнозам Wells Fargo, компания может остановить поставки энергии новым ЦОД до 2025 или 2026 года — если проектам, до завершения строительства которых осталось не более полугода, энергии может хватить, то совсем новые объекты, возможно, электричества не получат, несмотря на ранее полученные от Dominion гарантии. А строительство ЦОД, запланированных на 2023-2024 годы, может быть значительно отложено. Впрочем, в Wells Fargo считают, что с нехваткой электричества могут в скором времени столкнуться и уже существующие в регионе кампусы ЦОД.

29.07.2022 [14:18], Алексей Степин

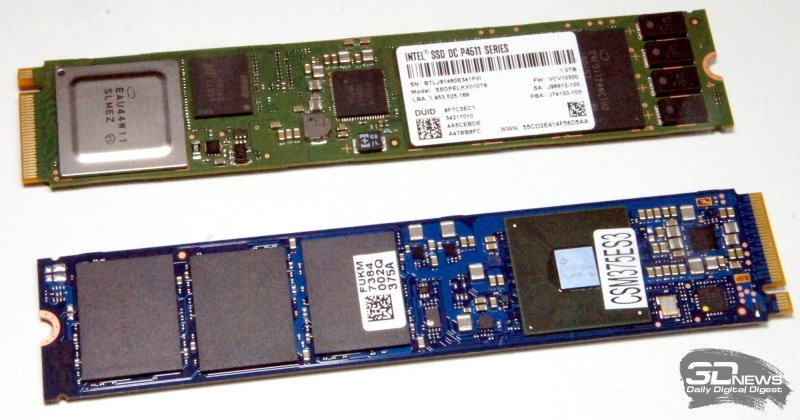

Бесславный конец Optane: полмиллиарда убытков и полный отказ от технологииВ своё время совместная инициатива Intel и Micron, целью которой стало создание принципиально нового типа энергонезависимой памяти 3D XPoint, наделало много шума. Первые же выпущенные на основе данной технологии SSD показали великолепные результаты. Эту память сегодня мы знаем как Optane, и, увы, с надеждами на появление новых решений на её основе придётся распрощаться. Тревожные звонки раздавались давно: в 2018 году Micron вышла из бизнеса, уступив своё производство 3D XPoint партнёру, а сама Intel отказалась от идеи выпуска потребительских накопителей на базе Optane. Но, по крайней мере, на тот момент она сосредоточила усилия на выпуске серверных решений. В их число вошёл и принципиально новый продукт: энергонезависимые модули DCPMM/PMem.  Они устанавливались в обычные слоты DIMM, не слишком сильно уступали в производительности классической оперативной памяти и позволяли кардинально нарастить объём доступной памяти за меньшую стоимость, нежели при использовании только DRAM. Казалось бы, память Optane нашла свою, пусть и довольно экзотическую нишу, что подтверждалось и многочисленными результатами тестов систем с Optane DCPMM, в том числе, в научных задачах. Но грянул гром! По результатам II квартала 2022 года Intel сообщила, что изрядно похудевшее к этому моменту подразделение Optane принесло $559 млн убытков. Решение списать текущие запасы готовых решений и чипов по графе «убытки» окончательно доказывает то, что Intel действительно намеревается покончить с этой страницей своей истории. Равно как и с SSD — соответствующее подразделение продано компании SK Hynix.  На данный момент сама Intel официально подтвердила отказ от Optane: в рамках новой стратегии оптимизации бизнеса IDM 2.0 компания закроет подразделения, не являющиеся решающими в стратегическом отношении, либо просто недостаточно прибыльные. Впрочем, поддержка клиентов, уже вложившихся в Optane будет продолжена. Сама же Intel отметила, что переход на CXL позволит хотя бы отчасти заменить Optane PMem. Из альтернатив технологии Optane, тоже не слишком популярных, можно вспомнить Samsung Z-SSD и Toshiba/Kioxia XL-Flash. Таким образом, приходится расстаться с мечтой о твердотельных накопителях не просто надёжных, но и лишённых традиционной медлительности NAND при операциях записи, особенно мелкоблочных. Стоимость производства чипов 3D XPoint даже во втором поколении, когда память удалось сделать четырёхслойной, всё же оказалась слишком высокой для того, чтобы устройства на её основе стали действительно выгодными для Intel.

28.07.2022 [23:13], Алексей Степин

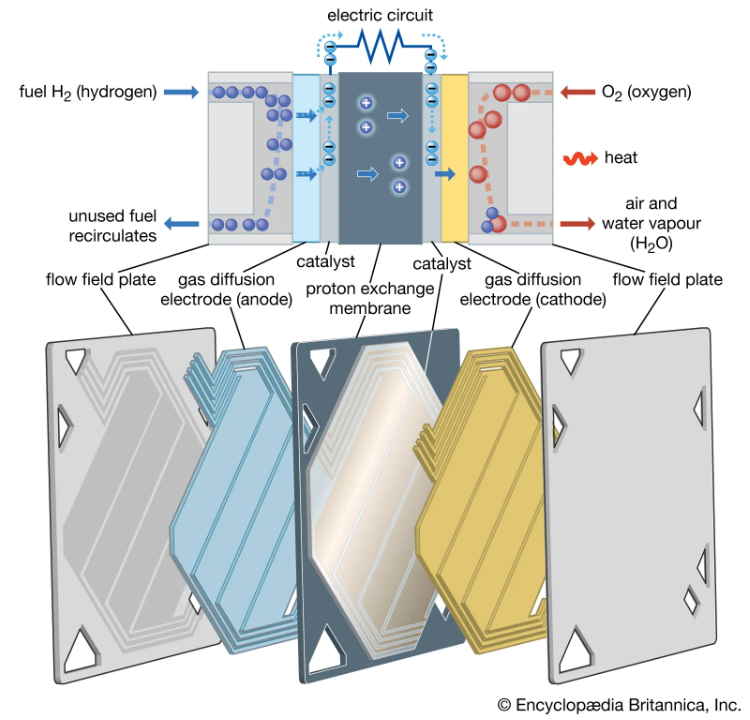

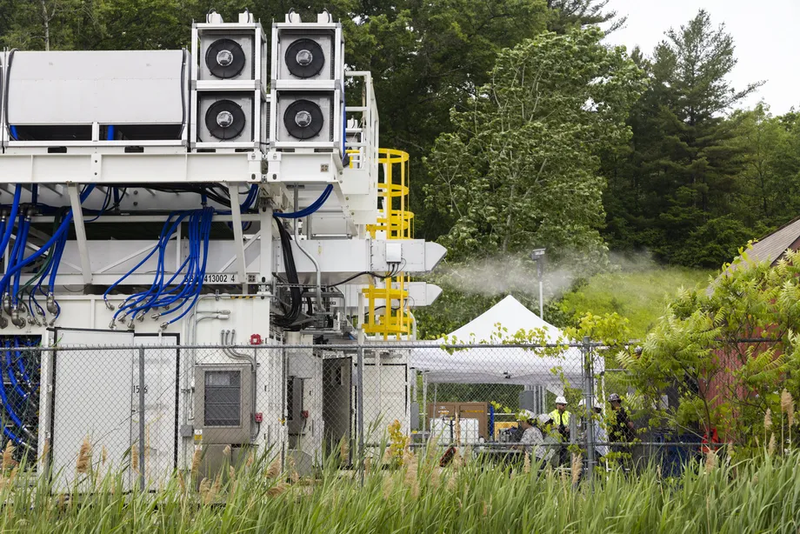

Microsoft и Plug Power успешно протестировали водородные топливные элементы для резервного питания ЦОДДизель-генератор — неотъемлемая часть подсистемы резервного питания любого серьёзного ЦОД, но по природе своей он не может похвастаться нейтральностью выхлопа. Многие ищут традиционным генераторам замену, и в их числе Microsoft. На днях компания сообщила, что ей удалось достичь важной вехи в освоении водородных топливных элементов, которые, по замыслу Microsoft, и должны заменить традиционные дизель-генераторы в принадлежащих ей центрах обработки данных. Компания начала тестирование новой генераторной станции мощностью 3 МВт, построенной на базе топливных ячеек с протонообменной мембраной (PEM). Она способна обеспечивать питание 10 тыс. серверов. С топливными элементами компания экспериментирует давно, ещё с 2013 года, но более ранние разработки использовали природный газ и не по факту не являлись такими уж экологичными.

Тестовая станция мощностью 3 мВт. Источник: Microsoft/John Brecher Разработать водородные PEM-ячейки компании удалось в сотрудничестве с Plug Power. В течение нескольких недель июня компании совместно протестировали прототип генератора нового поколения. Новая система, выбрасывающая в атмосферу лишь нагретый водяной пар, сработала успешно, так что Plug Power уже работает над созданием коммерческой версии системы.

Протонообменная мембрана: конструкция и принцип действия. Источник: Encyclopedia Britannica Первый же экземпляр будет установлен научно-исследовательском центре Microsoft, но пока конкретных сроков пока озвучено не было. У IT-гиганта большие надежды на подобные технологии: к 2030 году компания планирует обновить системы резервного питания во всех своих ЦОД.

В работе система выделяет только горячий водяной пар. Источник: Microsoft/John Brecher Правда, в полной экологичности водородных топливных элементов есть сомнения: работают они без вредных выбросов, но само их производство может оказаться далеко не таким чистым, как эксплуатация. Тем не менее, администрация США одобрила план стоимостью $8 млрд по развитию производства водорода в рамках программы альтернатив ископаемому топливу. В Европе есть аналогичные инициативы — как совсем скромные (€2,5 млн), так и весьма крупные (€1 млрд).

28.07.2022 [18:12], Руслан Авдеев

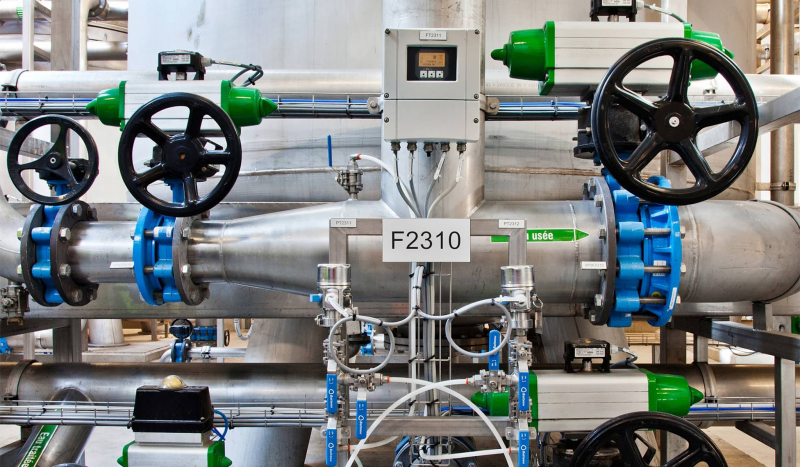

Европейские дата-центры хотят снизить потребление воды до 400 мл/кВт·ч, но только к 2040 годуГруппа Climate Neutral Data Centre Pact (CNDCP), объединяющая 90 % европейских операторов ЦОД, предложила добровольно снизить потребление воды до 400 мл на 1 кВт·ч к 2040 году и добиться углеродной нейтральности намного раньше 2050 года. Соответствующая цель уже поставлена ЕС, но операторы намерены добиваться её без законодательного принуждения и с опережением графика, — сообщает Data Center Dynamics. Хотя использование воды способно оказать значительное влияние на экологию, этот фактор часто недооценивают, учитывая только расход энергии. При этом многие ЦОД активно используют воду для охлаждения оборудования, благодаря чему снижается расход всё той же энергии, но растут затраты самой жидкости, что имеет критическое значение для некоторых регионов. Группу CNDCP сформировали в 2021 году с намерением достичь углеродной нейтральности европейских ЦОД к 2030 году, а также обеспечить достойный ответ прочим экологическим вызовам, в том числе снизить расход воды. Для оценки эффективности использования воды используется коэффициент WUE, который отражает расход воды на каждый затраченный киловатт·час электричества. Например, исследование 2016 года показало, что на тот момент WUE для ЦОД в США составлял в среднем 1,8 л/кВт·ч.

Источник изображения: Christian Lue/unsplash.com Цели поставлены с учётом жизненного цикла уже действующих систем охлаждения, поскольку их немедленная массовая замена может принести больше вреда, чем пользы из-за ущерба экологии в процессе производства самих систем. Поэтому в CNDCP заявили, что все 74 оператора ЦОД, участвовавшие в заключении пакта, добьются потребления не более 400 мл/кВт·ч только к 2040 году. Такой показатель вывели с учётом разницы технологий, климатических и иных условий, характерных для тех или иных ЦОД. Отдельные участники рынка уже заявили о намерении добиться положительного водного баланса для своих дата-центров — ЦОД будут отдавать больше чистой воды, чем потреблять. Так, Meta✴ и Microsoft планируют добиться этой цели к 2030 году. Последняя также начала устанавливать станции для очистки сточных вод ЦОД. А вот Google отметилась тем, что пыталась всеми возможными способами скрыть расход воды своими дата-центрами даже от властей. Помимо ограничения расхода воды, подписанты CNDCP предложили ввести и другие цели для дата-центров. Например, уже сформированы две рабочие группы для подготовки к переходу на «циркулярную экономику» со вторичным использованием материалов и переработкой различных ресурсов. В частном порядке аналогичную инициативу уже несколько лет развивает Microsoft в рамках проекта Circular Center.

27.07.2022 [17:11], Руслан Авдеев

Жители Северной Вирджинии ополчились против крупных дата-центровЖители Северной Вирджинии всё более и более недовольны распространению дата-центров гиперскейл-класса и готовы активно противостоять их строительству. По данным DataCenter Dynamics, вслед за жителями округа Принс-Уильям (Prince William), жалующихся на невыносимый уровень шума ЦОД Amazon, обитатели округа Фокир (Fauquier) потребовали от властей запретить строительство дата-центра той же компании, которая за последний десяток лет вложила в местные ЦОД более $35 млрд. Примечательно, что Северная Вирджиния десятилетиями является едва ли не крупнейшим хабом для строительства дата-центров в мире, последовательно привлекающим новые компании, объекты и инвестиции. Изначально ЦОД концентрировались преимущественно в округе Лаудон, а теперь распространяются на территорию округов Калпепер (Culpeper), Фокир и Принс-Уильям, жители которых начали вести организованную борьбу с инициативами IT-гигантов и местных властей. В наиболее «пострадавшем» округе Лаудон предложили новые правила зонирования для дата-центров, определяющих, где будущие ЦОД можно строить так, чтобы не побеспокоить местных жителей. Кроме того, предложено пересмотреть экологические стандарты строительства и допустимого уровня шума. Ожидается, что в определённых местах будет прекращено и одобрение строительства ЦОД в ускоренном порядке. Жители округа Калпепер подали в суд, требуя аннулировать разрешение на перезонирование и развитие ЦОД Amazon. В округе Фокир Amazon уже купила более 16 га земли, подала заявку на строительство нового дата-центра и договорилась с местной энергосбытовой компанией Dominion Energy. Изначально местные жители протестовали против строительства 230-кВ линий электропередач над их домами, но потом поняли, что они вообще не понадобятся, если дата-центра не будет. Местных жителей беспокоит не только экология и комфортность окружающей среды, но и экономика — скупка земли для ЦОД поднимает её цены. Кроме того, всё чаще задаётся вопрос, почему налоги для жителей не падают по мере развития дата-центров. О полном отказе от ЦОД речь не идёт, поскольку они обеспечивают около трети местных налоговых поступлений.

26.07.2022 [10:56], Сергей Карасёв

Kioxia представила корпоративные SSD серии CM7 с PCIe 5.0 и NVMe 2.0Компания Kioxia анонсировала твердотельные накопители CM7 корпоративного класса, оптимизированные для использования в высокопроизводительных и высокоэффективных серверах, а также системах хранения данных. Уже начаты отгрузки устройств некоторым заказчикам. Изделия серии CM7 доступны в двух вариантах исполнения: EDSFF E3.S и SFF толщиной 15 мм. Задействован интерфейс PCIe 5.0 (спецификация NVMe 2.0): утверждается, что по сравнению с накопителями предыдущего поколения производительность увеличилась в два раза. Заявленная скорость чтения информации достигает 14 Гбайт/с; скорость записи не уточняется. Заказчики смогут выбирать между устройствами с разным уровнем надёжности: 1 DWPD (полных перезаписей в сутки) и 3 DWPD. В первом случае вместимость достигает 30,72 Тбайт, во втором — 12,80 Тбайт.

Источник изображения: Kioxia Накопители CM7 имеют двухпортовую конструкцию. Среди поддерживаемых функций названы SR-IOV, CMB, Multistream writes, SGL. Говорится о поддержке TCG-Opal в соответствии со стандартом FIPS 140-3. Наконец, упомянуты средства обеспечения безопасности Flash Die Failure Protection.

22.07.2022 [21:52], Алексей Степин

Бразильская нефтегазовая компания Petrobras получит самый мощный суперкомпьютер в Латинской Америке — PegasusСовременный суперкомпьютер, а лучше несколько, стремится иметь любая страна или корпорация, и гонка HPC-решений проходит не только между США и Китаем — так, крупнейшая бразильская нефтегазовая компания Petrobras анонсировала создание нового кластера в Рио-де-Жанейро. Будущий суперкомпьютер получил имя Pegasus, и он должен стать самой мощной HPC-системой в латиноамериканском регионе с производительностью около 21 Пфлопс. Система будет включать в себя 2016 ускорителей неизвестной пока модели и 678 Тбайт оперативной памяти, а в качестве интерконнекта планируется использовать 400-Гбит/с сеть. Вероятно, это будeт InfiniBand NDR.

Рио-де-Жанейро. Источник: Pixabay Суперкомпьютеры активно применяются в нефтегазовой отрасли в самых различных сценариях, от поиска новых месторождений до повышения эффективности существующих процессов переработки природных ресурсов. Petrobras уже располагает солидными вычислительными мощностями, составляющими 42 Пфлопс. Главной задачей Pegasus будет обработка обширных массивов данных в рамках геологоразведывательного проекта EXP100, а также поиск способов ускорить начало разработок новых нефтегазовых полей в проекте PROD1000.

Машинный зал Dragão. Источник: Agência Petrobras В июне 2021 года компания Petrobras запустила систему Dragão с 200 Тбайт памяти и 100G-интерконнектом. Система на базе процессоров Xeon Gold 6230R занимает 60 место в TOP500 с пиковой теоретической производительностью 14,01 Пфлопс. Также у Petrobras есть машины Atlas (8,84 Пфлопс) и Fênix (5,37 Пфлопс). Для сравнения — система HPC5, принадлежащая итальянской нефтегазовой компании Eni S.p.A., сейчас находится на 12 месте TOP500 и имеет пиковую теоретическую производительность 51,72 Пфлопс. До момента ввода в строй Pegasus, который запланирован на декабрь 2022 года, Dragão продолжит оставаться мощнейшей латиноамериканской HPC-системой. К концу 2022 года компания намеревается нарастить свой пул вычислительных мощностей до 80 Пфлопс, но пока явно отстаёт от графика. Впрочем, темпы роста впечатляют: ещё в 2018 году в распоряжении Petrоbras было лишь 3 Пфлопс.

21.07.2022 [17:27], Руслан Авдеев

Жители Северной Вирджинии жалуются на «катастрофический шум» от дата-центровКак сообщает портал Data Center Dynamics, домовладельцы и гражданские активисты округа Принс-Уильям (Prince William County) в Северной Вирджинии (США), пожаловались на «катастрофический» шум, издаваемый местными ЦОД. Шум доносится из принадлежащих Amazon дата-центров, расположенных на территории кампуса Tanner Way. Сейчас техногигант ведёт строительство в городе Манассасе, но речь идёт не о шуме стройки. По словам активистов, непрекращающийся шум вызван работой систем воздушного охлаждения на крышах ЦОД, создающих неблагоприятную среду обитания для жильцов района Great Oak, состоящего из 291 домохозяйства.

Источник изображения: Elyas Pasban/unsplash.com Круглый стол ассоциации домовладельцев округа совместно с ассоциацией города Манассас направили жёсткую жалобу в Наблюдательный совет округа, сообщив о «чрезвычайном промышленном шуме», продолжающемся круглосуточно и без выходных, никаких мер по устранению которого не принимается. По словам местных активистов, шум загрязняет окрестности непрерывно, чему есть аудио- и видеодоказательства. От наблюдательного совета требуют найти решение проблемы. Активисты напоминают о прецедентах — аналогичные жалобы в Аризоне в 2018 году привели к прекращению развития ЦОД в регионе решением местных властей. По данным активистов, пока руководство совета не смогло напрямую решить проблему с ЦОД, и теперь жители требуют приостановки разрешений на работу дата-центров в округе Принс-Уильям до тех пор, пока проблема не будет устранена. Основная беда в том, что Наблюдательный совет округа намеренно исключил шум от промышленных кондиционеров из правил 1989 года, в соответствии с которыми и строились дата-центры, в результате чего округ потерял законную возможность контролировать работу ЦОД в этом отношении, независимо от того, какой громкости звук издают объекты. Местные жители жалуются на проблемы как с собственным здоровьем, так и с состоянием домашних питомцев. Благодаря местным регуляциям Северная Вирджиния крайне привлекательна для строителей и операторов дата-центров. Текущая ёмкость ЦОД в штате составляет порядка 1,7 ГВт, а через два года, как ожидается, она достигнет 2 ГВт. И это самый крупный в мире рынок ЦОД. Для сравнения — суммарная ёмкость сразу четырёх европейских рынков FLAP только-только добралась до 2 ГВт. Та же Amazon за последний десяток лет вложила в постройку дата-центров в Северной Вирджинии более $35 млрд.

20.07.2022 [15:56], Владимир Мироненко

Аномальная жара привела к сбоям в лондонских дата-центрах Google и Oracle

google cloud platform

hardware

oracle cloud infrastructure

великобритания

облако

охлаждение

сбой

цод

Во вторник, 19 июля, в ЦОД Google Cloud Platform (GCP) в Лондоне произошёл сбой в системе охлаждения, в связи с чем несколько сервисов компании временно вышло из строя. В лондонском регионе облака Oracle тоже возникли проблемы с охлаждением оборудования ЦОД. Сбои произошли из-за рекордной жары в Великобритании — температура превысила +40°C. Некоторые операторы дата-центров были вынуждены принять нестандартные меры, начав обрызгивать водой внешние модули систем кондиционирования, установленные на крыше. Отключение ряда сервисов Google произошло в 18:13 по местному времени (20:13 мск). В журнале статуса оборудования сбой описан как «связанный с охлаждением». Google заявила, что сбой затронул лишь небольшое количество клиентов. В частности, отключение коснулось сервисов Persistent Disk и Autoscaling. Хотя Google утверждает, что сбой продолжался до 22:00 BST (24:00 мск), в означенное время всё ещё поступали жалобы на ошибки в работе Persistent Disk. С подобными проблемами в Лондоне столкнулась и облачная служба Oracle. Проблемы с перегревом у неё начались примерно в 17:00 по местному времени (19:00 мск). Oracle ранее арендовала ресурсы в ЦОД Equinix в лондонском кампусе Слау, но сейчас не раскрывает местонахождение своих мощностей. «В результате несезонных температур в регионе возникла проблема с частью инфраструктуры охлаждения в центре обработки данных на юге Великобритании (в Лондоне), — говорится в сообщении компании. — Это привело к тому, что часть нашей сервисной инфраструктуры пришлось отключить, чтобы предотвратить неконтролируемые сбои оборудования».

20.07.2022 [00:56], Владимир Мироненко

Из-за жары лондонские дата-центры вынуждены охлаждать оборудование на крыше, поливая его водой из шланговВ этом году в Великобритании наблюдается аномальная жара. 19 июля температура воздуха в стране установила новый рекорд, превысив 40° С. Как сообщает Bloomberg, в некоторых британских ЦОД выбрали оригинальный способ борьбы с перегревом оборудования, используя обрызгивание водой внешних модулей систем кондиционирования, установленных на крыше. По словам Адриана Тревельяна (Adrian Trevelyan), директора по послепродажному обслуживанию компании Airedale International, которая поставляет и обслуживает системы охлаждения для ЦОД, многие лондонские дата-центры вынуждены прибегнуть к такому необычному способу охлаждения. Небольшие ЦОД в густонаселённых городских районах, работающие почти на полную мощность, просто требуют экстренного орошения во время жары. Тревельян сообщил, что орошение позволяет снизить температуру воздуха вокруг змеевиков внешнего контура охлаждения, чтобы они продолжали эффективно рассеивать тепло. Он отказался назвать конкретные компании, применяющие такой способ охлаждения, но сказал, что это делают «в пределах (кольцевой автомагистрали) M25 и в городе». Однако от жары страдают не только малые, но и крупные дата-центры, которые всё же имеют запас по охлаждению ключевых подсистем — 10 июля в лондонском ЦОД AWS произошёл перебой питания из-за так называемого «теплового события» (thermal event). Использование полива шлангами может выручить в очень жаркий день, но негативно отразится на сроке службы оборудования, сообщила София Флюкер (Sophia Flucker), директор консалтинговой фирмы Operational Intelligence, отметив, что если используется вода повышенной жёсткости (как в Лондоне), это может привести к накоплению накипи. Флюкер также рассказала, что многие операторы колокации, сдающие мощности в аренду третьим лицам, сталкиваются со штрафами за несоблюдение температурного режима в машинных залах. |

|