Материалы по тегу: arm

|

17.11.2025 [10:02], Сергей Карасёв

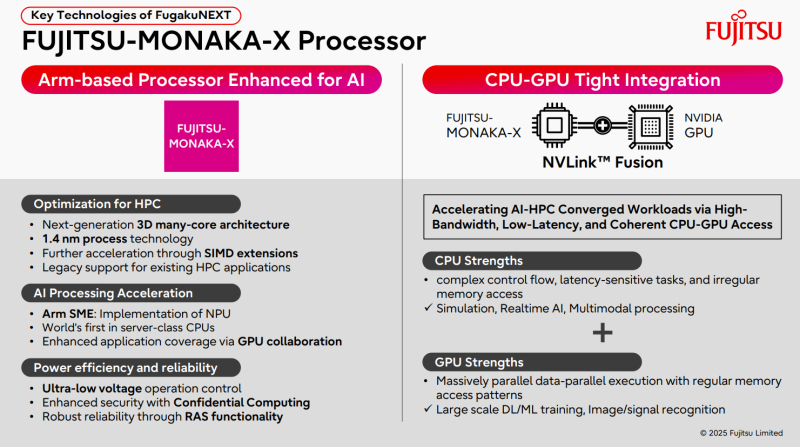

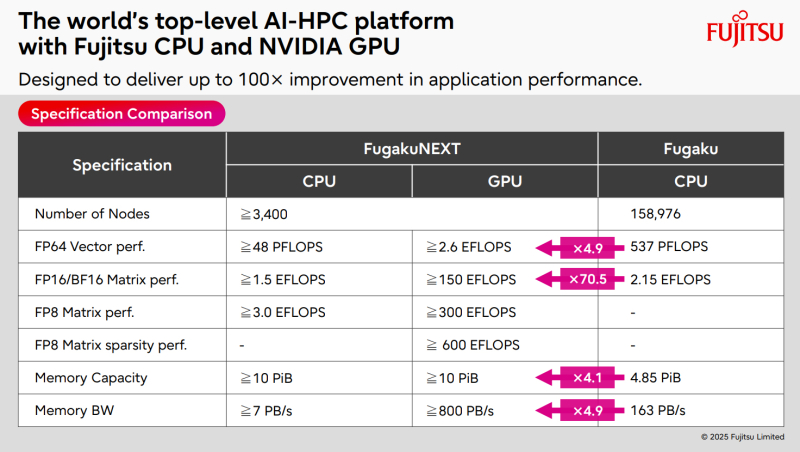

ИИ-производительность японского суперкомпьютера FugakuNEXT превысит 600 ЭфлопсКомпания Fujitsu поделилась информацией о суперкомпьютере следующего поколения FugakuNEXT (Fugaku Next), который создаётся совместно с японским Институтом физико-химических исследований (RIKEN). Проект реализуется при поддержке Министерства образования, культуры, спорта, науки и технологий Японии (MEXT). FugakuNEXT придёт на смену вычислительному комплексу Fugaku, который в 2020 году стал самым высокопроизводительным суперкомпьютером в мире. В рейтинге ТОР500 от июня 2025 года эта НРС-система занимает седьмое место с FP64-быстродействием приблизительно 442 Пфлопс (теоретическая пиковая производительность достигает 537,21 Пфлопс). Разработку архитектуры FugakuNEXT планируется полностью завершить к середине 2028 года, после чего начнутся производство и монтаж суперкомпьютера. В эксплуатацию система будет введена не ранее середины 2030 года. Известно, что в основу FugakuNEXT лягут Arm-процессоры Fujitsu MONAKA-X, при производстве которых предполагается использовать 1,4-нм технологию. Чипы получат до 144 вычислительных ядер. Кроме того, в состав машины войдут ИИ-ускорители NVIDIA, для связи которых с CPU планируется задействовать шину NVLink Fusion. Платформа также получит новые интерконнекты для горизонтального и вертикального масштабирования. В материалах Fujitsu говорится, что FugakuNEXT получит в общей сложности свыше 3400 узлов CPU и GPU. Их объём памяти превысит 10 ПиБ (Пебибайт). Агрегированная пропускная способность памяти в случае CPU-блоков составит более 7 Пбайт/с, GPU-модулей — свыше 800 Пбайт/с против 163 Пбайт/с у нынешней системы Fugaku. Кроме того, раскрываются ожидаемые показатели ИИ-быстродействия FugakuNEXT. У CPU-секции производительность превысит 48 Пфлопс в режиме FP64, 1,5 Эфлопс на операциях FP16/BF16 и 3 Эфлопс в режиме FP8. В случае GPU-раздела быстродействие FP64, FP16/BF16, FP8 и FP8 Sparse составит более 2,6 Эфлопс, 150 Эфлопс, 300 Эфлопс и 600 Эфлопс соответственно.

16.11.2025 [12:35], Сергей Карасёв

Qualcomm представила чипы Dragonwing IQ-X для индустриальных Windows-компьютеровКомпания Qualcomm анонсировала новые SoC семейства Dragonwing IQ-X — изделия IQ-X5181 и IQ-X7181, ориентированные на индустриальный сектор. Чипы предназначены для построения промышленных Windows-компьютеров, систем автоматизации, робототехнических платформ, медицинского оборудования и пр. Решение IQ-X5181 объединяет восемь кастомизированных ядер Qualcomm Oryon (Armv8) с тактовой частотой до 3,4 ГГц, модификация IQ-X7181 — двенадцать. В состав SoC входит графический ускоритель Qualcomm Adreno с частотой соответственно 1,1 и 1,25 ГГц. Младшая версия способна справляться с декодированием видеоматериалов 4Kp60 VP9/AV1 и кодированием 4Kp30 AV1, старшая — 4K120 VP9/AV1 и 4Kp60 AV1. Чипы обеспечивают ИИ-производительность до 45 TOPS с учётом блоков CPU, GPU и Hexagon NPU.

Источник изображения: Qualcomm Возможно использование до 64 Гбайт оперативной памяти LPDDR5X-4200, флеш-накопителей UFS 4.0 и карт SD/MMC (SD 3.0). Реализованы интерфейсы eDP (eDP1.4b) с поддержкой разрешения до 4096 × 2160 пикселей при 60 Гц и DisplayPort v1.4a (через USB) с поддержкой разрешения до 5120 × 2880 точек при 60 Гц. Изделие IQ-X5121 располагает двумя интерфейсами камер CSI на четыре линии каждый, IQ-X7181 — четырьмя. Для обеих новинок заявлена поддержка 2 × USB 3.1, 3 × USB 4.0 Type-C (DisplayPort v1.4a Alt Mode), 6 × eUSB 2.0 и 221 × GPIO (UART, SPI, I3C, I2C via QUP). В случае IQ-X5181 реализованы интерфейсы 2 × PCIe 4.0 х4 и 2 × PCIe 3.0 х2, в случае IQ-X7181 — PCIe 4.0 х8, PCIe 4.0 х4 и 2 × PCIe 3.0 х2. Кроме того, говорится о поддержке Ethernet (чип-компаньон QPS615), Wi-Fi и Bluetooth (посредством модуля M.2 PCIe), Wi-Fi 7 / Wi-Fi 6E (через WCN785/WCN6856), а также 5G (модем Snapdragon X65). Изделия выполнены в корпусе 1747-ball BGM с размерами 58 × 58 мм с максимальной толщиной 3 мм. Диапазон рабочих температур простирается от -40 до +105 °C. Говорится о совместимости с Windows 10/11 IoT Enterprise LTSC, Qt, CODESYS, EtherCAT и пр. Гарантирована доступность чипов в течение более чем 10 лет.

12.11.2025 [14:09], Сергей Карасёв

Компактная рабочая станция Minisforum MS-R1 получила 12-ядерный Arm-процессор с NPU и два порта 10GbEКомпания Minisforum анонсировала рабочую станцию небольшого форм-фактора MS-R1, подходящую для решения различных ИИ-задач. В новинке, которая уже доступна для заказа, соседствуют процессор с архитектурой Arm и ОС на ядре Linux. Устройство заключено в корпус объемом примерно 1,78 л с габаритами 196 × 189 × 48 мм. Применён чип Cix CP8180 (P1) с 12 вычислительными ядрами в конфигурации DynamIQ: 4 × Cortex-A720 с частотой до 2,6 ГГц, 4 × Cortex-A720 с частотой 2,3–2,4 ГГц и 4 × Cortex-A520 с частотой 1,8 ГГц. В состав изделия входит графический ускоритель Arm Immortalis G720 MC10 с поддержкой Vulkan 1.3, OpenGL ES 3.2, OpenCL 3.0. Встроенный VPU-блок обеспечивает возможность декодирования материалов 8Kp60 AV1, H.265, H.264, VP9, VP8, H.263, MPEG-4, MPEG-2, а также кодирования видео 8Kp30 H.265, H.264, VP9, VP8. Процессор наделён нейромодулем (NPU) с поддержкой операций INT4/INT8/INT16/FP16/BF16 и производительностью до 28,8 TOPS. Общее ИИ-быстродействие с учётом CPU и GPU достигает 45 TOPS.

Источник изображения: Minisforum Компьютер может нести на борту до 64 Гбайт LPDDR5-5500. Есть коннектор M.2 2280/22110 для NVMe SSD с интерфейсом PCIe 4.0 x4. Кроме того, присутствует x16-слот (PCIe 4.0 x8) для карты расширения. В оснащение входят адаптеры Wi-Fi 6E и Bluetooth 5.3 (модуль M.2 2230 E-Key) и двухпортовый сетевой контроллер 10GbE (Realtek RTL8127). Устройство располагает тремя портами USB 3.1 Type-A и четырьмя разъёмами USB 2.0 Type-A, двумя интерфейсами USB 3.1 Type-C (DisplayPort 1.4 Alt Mode), двумя гнёздами RJ45 для сетевых кабелей, интерфейсом HDMI 2.0, аудиогнездом на 3,5 мм и 40-контактной колодкой GPIO. Питание (19 В, 180 Вт) подаётся через DC-разъём. Система охлаждения включает три медные тепловые трубки и вентилятор. Новинка поставляется с Debian 12. Цена варьируется примерно от $500 за версию с 32 Гбайт ОЗУ без накопителя до $700 за модификацию с 64 Гбайт памяти и SSD вместимостью 1 Тбайт.

07.11.2025 [12:16], Владимир Мироненко

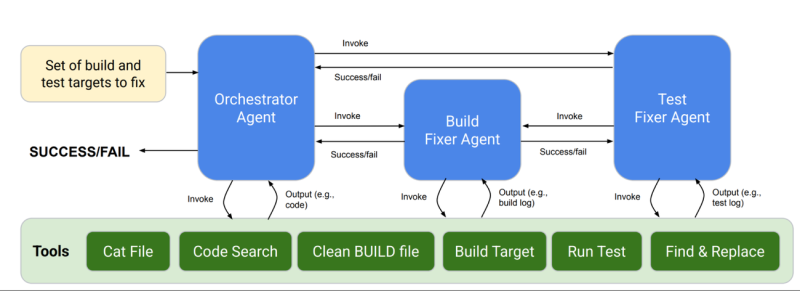

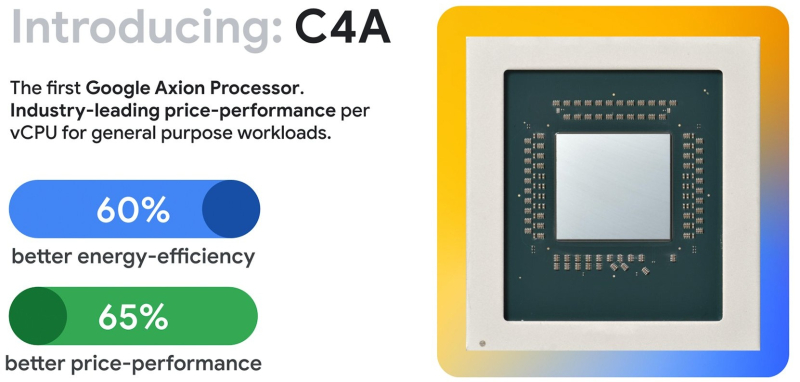

Google представила инстансы N4A и C4A Metal на базе фирменных Arm-процессоров AxionGoogle представила новые инстансы на базе фирменных Arm-процессоров Axion: N4A и C4A Metal. N4A — самая экономичная виртуальная машина серии N на сегодняшний день, которая уже доступна в тестовом режиме (Preview Mode). N4A предлагает до двух раз лучшее соотношение цены и производительности, чем сопоставимые виртуальные машины текущего поколения на базе x86. N4A доступен в готовых и настраиваемых конфигурациях: до 64 vCPU, 512 Гбайт DDR5 и сетевым подключением 50 Гбит/с. N4A предлагается в конфигурациях с высокой производительностью процессора (2 Гбайт RAM на vCPU), стандартной (4 Гбайт на vCPU) и с высокой производительностью памяти (8 Гбайт на vCPU). Виртуальные машины N4A поддерживают новейшие решения для хранения данных Hyperdisk, включая Hyperdisk Balanced, Hyperdisk Throughput и Hyperdisk ML (будет доступно позже), обеспечивая до 160 тыс. IOPS и пропускную способность 2,4 Гбайт/с на инстанс. N4A демонстрирует высокие результаты в ряде отраслевых бенчмарков, отражающих ключевые рабочие нагрузки. Например, по сравнению с аналогичными x86-инстансами текущего поколения N4A обеспечивает до 105 % лучшее соотношение цены и производительности для вычислительных нагрузок, до 90 % — для масштабируемых веб-серверов, до 85 % — для Java-приложений и до 20 % — для баз данных общего назначения. N4A доступен в виде превью для Compute Engine, Google Kubernetes Engine (GKE), Dataproc и Batch, а поддержка Dataflow и других сервисов появится в ближайшее время. C4A Metal — первый инстанс Google на базе Arm-архитектуры на bare metal-серверах. Он включает до 96 vCPU, до 768 Гбайт DDR5, сетевое подключение со скоростью до 100 Гбит/с и полную поддержку Google Cloud Hyperdisk, включая варианты хранения Hyperdisk Balanced, Extreme, Throughput и блочный доступ. Этот инстанс оптимизирован для специализированных рабочих нагрузок, таких как гипервизоры и разработка нативных приложений для Arm-архитектуры. Как облачное решение, C4A Metal обеспечивает снижение совокупной стоимости владения (TCO), предлагая предсказуемые эксплуатационные расходы. Компания отметила, что, запуская конвейеры разработки и тестирования на физических экземплярах процессоров Axion с использованием C4A Metal, разработчики Android могут получить выгоду от нативной производительности, устраняя накладные расходы на управление эмуляцией, такие как медленные уровни трансляции инструкций. Кроме того, они могут значительно сократить задержки для инструментов сборки Android и автоматизированных систем тестирования, что приведёт к ускорению циклов обратной связи. C4A Metal также решает проблемы производительности, связанные с вложенной виртуализацией, что делает его отличной платформой для масштабируемых сред Cuttlefish (Cloud Android). После сегодняшнего анонса портфолио инстансов на базе процессоров Axion теперь включает три варианта: N4A, C4A и C4A Metal. Вместе серии C и N позволяют снизить общие расходы на ведение бизнеса без ущерба для производительности или требований к конкретной рабочей нагрузке, отметила компания. «Независимо от того, используете ли вы Ironwood и Axion вместе или комбинируете их с другими вычислительными решениями, доступными на базе AI Hypercomputer, этот системный подход обеспечивает вам максимальную гибкость и производительность для самых требовательных рабочих нагрузок», — заявила Google.

06.11.2025 [22:34], Владимир Мироненко

Qualcomm и Arm разошлись во мнениях по поводу развития ИИ-вычисленийQualcomm и Arm опубликовали в среду квартальные отчёты, дав разные прогнозы относительно рынка процессоров для инференса, пишет The Register. Генеральный директор Qualcomm Криштиану Амон (Cristiano Amon) сообщил аналитикам в ходе телефонной конференции, посвященной квартальным финансовым результатам о том, что его компания выйдет на рынок ЦОД с чипами, предназначенными для выполнения задач инференса и потребляющими меньше энергии, чем «железо» конкурентов. Амон рассказал, что Qualcomm разрабатывает SoC и плату для неё, поскольку «рост ИИ-ЦОД смещается от обучения к специализированным рабочим нагрузкам инференса, и ожидается, что эта тенденция усилится в ближайшие годы». Вместе с тем он отметил, что Qualcomm не сможет отчитаться о «существенной» выручке в сегменте ЦОД до 2027 года. Генеральный директор Arm Рене Хаас (Rene Haas) тоже придерживается мнения, что энергопотребление является «узким местом» в ЦОД, и что спрос сместится с обучения на инференс, вместе с тем считая, что такого рода задачи будут выполняться и за пределами дата-центров. Он отметил растущий спрос на различные архитектуры и вычислительные решения, позволяющие выполнять инференс не в облаке. «Очевидно, что вы не будете полностью полагаться на что-то, что находится на периферии. Но сегодня всё наоборот. Всё на 100 % зависит от облака. И мы думаем, что это изменится», — заявил Хаас во время телефонной конференции с аналитиками, посвящённой финансовому отчёту Arm. Qualcomm анонсировала новую серию чипов для ИИ ЦОД AI200/AI250, заявив, что ИИ-стартап Humain, основанный суверенным фондом Саудовской Аравии, станет одним из их заказчиков. В ходе телефонной конференции Амон сообщил, что Qualcomm ведёт переговоры с другим крупным заказчиком-гиперскейлером, отметив, что они проходят успешно, пишет Reuters. Выручка Qualcomm в IV квартале 2025 финансового года, завершившемся 28 сентября 2025 года, составила $11,27 млрд, что на 10 % больше, чем годом ранее, и выше консенсус-прогноза аналитиков, опрошенных LSEG, в размере $10,79 млрд. В полупроводниковом сегменте (QCT) выручка компании составила $9,82 млрд, превысив результат годичной давности на 13 %. При этом выручка в автомобильном сегменте выросла на 17 % до $1,05 млрд, в сегменте Интернета вещей — на 7 % до $1,81 млрд. Скорректированная прибыль на акцию составила $3,00 при прогнозе от LSEG в размере $2,88. Из-за единовременной налоговой выплаты в размере $5,7 млрд компания завершила квартал с чистым убытком в $3,12 млрд, или $2,89 на акцию, тогда как годом ранее у неё была чистая прибыль в размере $2,92 млрд, или $2,59 на акцию. Выручка Qualcomm за 2025 финансовый год составила $44,3 млрд, что на 14 % больше показателя предыдущего финансового года. Чистая годовая прибыль снизилась на 45 % до $5,5 млрд. В I квартале 2026 финансового года Qualcomm прогнозирует выручку в размере $11,8–$12,6 млрд, что соответствует среднему значению в $12,2 млрд. По данным LSEG, это превышает консенсус-прогноз аналитиков в $11,62 млрд. Скорректированная прибыль на акцию, согласно ожиданиям компании, составит $3,30–$3,50 при прогнозе Уолл-стрит в размере $3,31 на акцию. Arm объявила о выручке во II квартале 2026 финансового года в размере $1,14 млрд, что на 34 % больше, чем годом ранее, а также больше прогноза аналитиков в размере $1,06 млрд, пишет Reuters. Третий квартал подряд выручка компании превышает $1 млрд. Выручка компании от роялти выросла год к году на 21 % до рекордных $620 млн, а от лицензирования — на 56 % до $515 млн благодаря новым крупным соглашениям в сфере вычислительных технологий нового поколения. Скорректированная операционная прибыль (Non-GAAP), достигла $467 млн, а скорректированная прибыль на акцию (Non-GAAP), составила $0,39, что в обоих случаях превышает прогноз, отметил ресурс Converge! Network Digest. Финансовый директор Джейсон Чайлд (Jason Child) сообщил инвесторам, что наибольший вклад в рост выручки внесли смартфоны, но «более высокие ставки роялти за чип в ЦОД, где мы по-прежнему наблюдаем рост доли кастомных чипов для гиперскейлеров», безусловно, не были помехой. Arm отметила, что набирает обороты вклад своей архитектуры в развитие облачного ИИ: более 1 млн ядер Arm Neoverse уже развёрнуто в инфраструктуре гиперскейлеров. Ожидается, что доля процессоров Arm в установленных ведущими гиперскейлерами чипах в этом году достигнет почти 50 %. Среди новых игроков на этом рынке компания отметила Google, которая уже перенесла более 30 тыс. облачных приложений на Arm-чипы Axion, включая Gmail и YouTube, и намерена перенести большую часть из более чем 100 тыс. своих приложений. Также в минувшем квартале Microsoft расширила использование процессоров Cobalt 100 на базе Arm до 29 регионов по всему миру. «Открытие пяти новых ЦОД Stargate AI, все из которых основаны на Arm как стратегической вычислительной платформе, подчёркивает роль Arm в обеспечении масштабируемого ИИ», — отметила компания. Доля Arm на рынке серверных процессоров действительно достигла 25 %, но во многом благодаря внедрению интегированных в суперчипы NVIDIA процессорам Grace.

28.10.2025 [20:35], Сергей Карасёв

NVIDIA анонсировала DPU BlueField-4: 800G-порты, ConnectX-9, CPU Grace и PCIe 6.0NVIDIA анонсировала DPU BlueField 4, рассчитанный на использование в составе масштабных инфраструктур ИИ. Устройство оснащено 800G-портами. Новинка в этом отношении вдвое быстрее BlueField-3, дебютировавших ещё в 2021 году. NVIDIA отмечает, что ИИ-фабрики продолжают развиваться с беспрецедентной скоростью. При этом требуется обработка колоссальных массивов структурированных и неструктурированных данных. Для удовлетворения этих потребностей необходимо формирование инфраструктуры нового класса, на которую как раз и ориентирован DPU BlueField-4. Новинка использует программно-определяемую архитектуру для ускорения сетевых операций, функций безопасности и задач хранения данных. По заявлениям NVIDIA, BlueField-4 позволяет трансформировать дата-центры в безопасную интеллектуальную ИИ-инфраструктуру с высокой производительностью. BlueField-4 объединяет 64-ядерный Arm-процессор NVIDIA Grace (114 Мбайт L3-кеш), 128 Гбайт LPDDR5, 512 Гбайт SSD, сетевой адаптер NVIDIA ConnectX-9 SuperNic (1,6 Тбит/с), а также коммутатор PCIe 6.0 с 48 линиями. Новинка будет доступна в виде карты расширения (PCIe 6.0 x16) и в виде модуля для узлов VR NVL144. Утверждается, что по сравнению с BlueField-3 вычислительная производительность выросла в шесть раз. При этом возможно формирование ИИ-фабрик вчетверо большего масштаба. Кроме того, BlueField-4 поддерживает многопользовательскую сеть, быстрый доступ к данным и микросервисы NVIDIA DOCA. Задействована архитектура NVIDIA BlueField Advanced Secure Trusted Resource Architecture. Предполагается, что BlueField-4 возьмут на вооружение такие производители серверов и платформ хранения данных, как Cisco, DDN, Dell Technologies, HPE, IBM, Lenovo, Supermicro, VAST Data и WEKA. О поддержке новинки заявили Armis, Check Point, Cisco, F5, Forescout, Palo Alto Networks и Trend Micro, а также системные интеграторы Accenture, Deloitte и World Wide Technology. Интегрировать BlueField-4 в свои платформы намерены Canonical, Mirantis, Nutanix, Rafay, Red Hat, Spectro Cloud и SUSE. На рынок BlueField-4 поступит в 2026 году как часть экосистемы Vera Rubin.

24.10.2025 [22:50], Владимир Мироненко

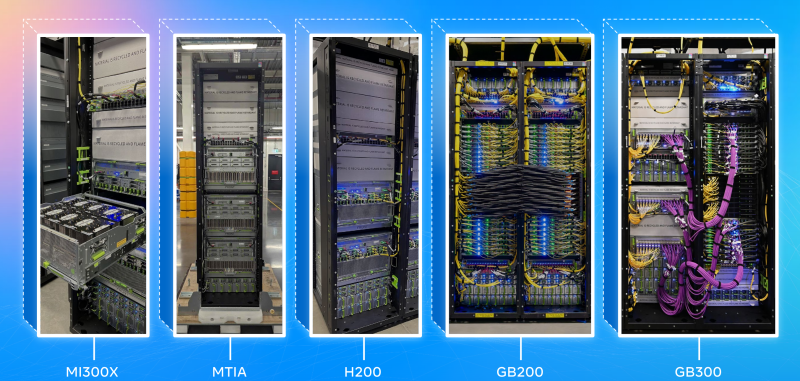

ИИ помог Google перенести 30 тыс. внутренних нагрузок на Arm-процессоры Axion, на очереди ещё 70 тыс.Google объявила, что портировала около 30 тыс. внутренних нагрузок на Arm-архитектуру и планирует перенести ещё порядка 70 тыс. Помогает ей в этом ИИ, но пока не слишком успешно. При этом целиком отказываться от x86-процессоров в пользу собственных Arm-чипов Axion компания пока не планирует. YouTube, Gmail и BigQuery уже работают как на системах с x86, так и c Arm. В процессе портирования приходится уделять внимание архитектурным различиям, таким как особенности работы с числами с плавающей запятой, параллелизм, платформенно-зависимые технологии и производительность. Специалисты Google рассказали, что сначала они перенесли некоторые из ключевых задач, такие как F1, Spanner и Bigtable, используя стандартные методы разработки ПО с привлечением инженеров. Оказалось, что современные компиляторы и инструменты, такие как санитайзеры и фаззеры, избавили разработчиков от множества сюрпризов. Большая часть времени по факту ушла на исправление тестов, обновление сложных систем сборки и развёртывания, как правило, для самых старых и самых нагруженных сервисов, устранение проблем с массовым развёртыванием в рабочих средах и принятие мер по предотвращению дестабилизации критически важных систем. 30 тыс. приложений — это достаточно большой объём кода для того, чтобы задуматься об автоматизации задач. Поэтому компания создала новый мультиагентный ИИ-инструмент CogniPort для исправления ошибок сборки и тестирования. Он успешно справлялся с проблемами примерно в 30 % случаев и лучше всего — с исправлениями тестов, платформенно-зависимыми особенностями и особенностями представления данных. Эффективность не впечатляет, но Google предстоит портировать ещё десятки тысяч нагрузок. пакетов. Кроме того, компания внедрила новую систему непрерывного мониторинга и развёртывания мультиархитектурных нагрузок CHAMP (Continuous Health Monitoring Platform), которая автоматически отбрасывает задачи, работа которых на Arm сопровождается проблемами вроде циклических сбоев или недостаточной производительности, для последующих отладки и профилирования. Чем больше будет запущено нагрузок, тем лучше Borg, управляющий кластерами внутри Google, сможет распределять задачи таким образом, чтобы эффективно использовать Arm-серверы. Это позволит сэкономить затраты, поскольку по словам Google, системы на базе Axion обеспечивают на 65 % лучшее соотношение цены и производительности, чем экземпляры на базе x86, а также на 60 % более высокую энергоэффективность. Ранее Google, по неофициальным данным, высказывала недовольство показателем TCO последних поколений Intel Xeon. Возможно, это побудило компанию заняться созданием собственного процессора. Первой на этот путь, тоже ради улучшения TCO, ступила Amazon, которая разработала уже четыре поколения Arm-процессоров Graviton. В прошлом году компания похвасталась, что у неё есть уже 2 млн этих чипов. Alibaba Cloud в 2021 году представила свой первый Arm-процессор Yitian 710. У Microsoft с прошлого года есть собственные Arm-чипы Cobalt 100, на которые также возложена часть внутренних нагрузок. Наконец, Oracle два года назад сообщила о завершении миграции всех своих облачных сервисов на Arm, включая флагманскую СУБД. Oracle использует процессоры компании Ampere Computing, в которой она владела заметной долей до сделки с SoftBank. Все эти процессоры позволили Arm занять четверть рынка серверных CPU, однако решающую роль сыграло внедрение NVIDIA GB200/GB300. Arm также заключила стратегическое соглашение с Meta✴, чтобы помочь последней с оптимизацией ПО.

17.10.2025 [14:44], Сергей Карасёв

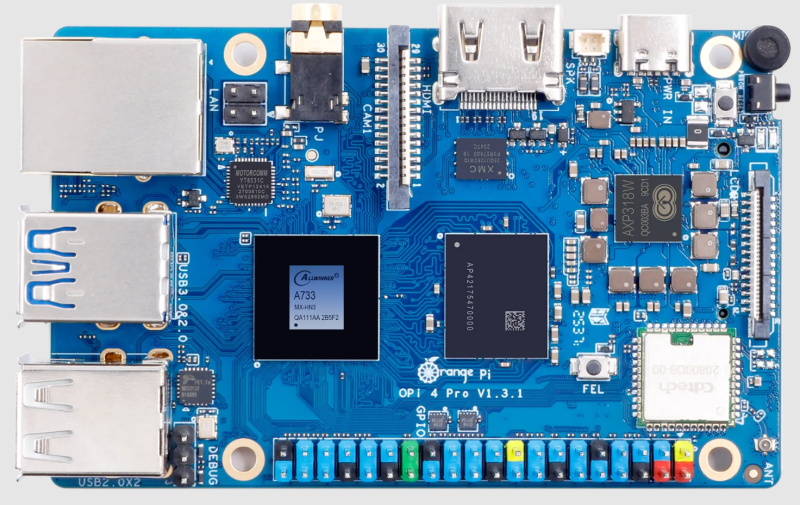

Одноплатный компьютер Orange Pi 4 Pro объединил ядра Arm и RISC-VДебютировал одноплатный компьютер Orange Pi 4 Pro, предназначенный для построения периферийных устройств с ИИ-функциями, систем промышленной автоматизации, сетевых хранилищ данных, шлюзов и пр. В основу новинки положена аппаратная платформа Allwinner. Применён процессор A733, объединяющий два ядра Arm Cortex-A76 с частотой до 2 ГГц, шесть ядер Arm Cortex-A55 с частотой до 1,8 ГГц, а также ядро реального времени XuanTie E902 RISC-V с частотой 200 МГц. Чип содержит графический блок Imagination BXM-4-64 и нейропроцессорный модуль (NPU) с производительностью до 3 TOPS на операциях INT8 (говорится также о поддержке INT16/FP16/BF16). Объём оперативной памяти LPDDR5 может составлять 4, 6, 8, 12 и 16 Гбайт. Изделие располагает коннектором M.2 M-Key для SSD с интерфейсом PCIe 3.0 (NVMe) и слотом microSD с поддержкой карт ёмкостью до 128 Гбайт, а опционально может быть добавлен накопитель eMMC вместимостью 16, 32, 64 или 128 Гбайт. Предусмотрены адаптеры Wi-Fi 6 и Bluetooth 5.4 (BLE), сетевой контроллер 1GbE (YT8531CA) с поддержкой PoE. В набор разъёмов входят три порта USB 2.0 Type-A, по одному порту USB 3.0 Type-A и USB Type-C (служит для подачи питания 5 В / 3 А), гнездо RJ45 для сетевого кабеля, коннектор HDMI 2.0 и аудиогнездо на 3,5 мм. Есть интерфейс MIPI-DSI (4 линии), два интерфейса MIPI-CSI (4 и 2 линии) и 40-контактная колодка GPIO, совместимая с Raspberry Pi. Габариты составляют 89 × 56 мм, масса — 58 г. Стоимость Orange Pi 4 Pro начинается примерно с $30 в варианте с 4 Гбайт ОЗУ.

16.10.2025 [10:11], Сергей Карасёв

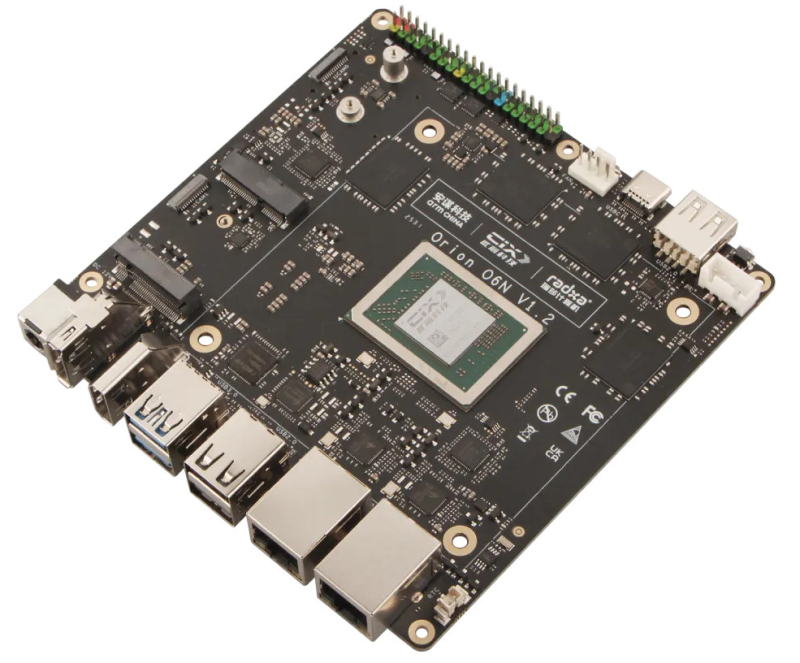

Одноплатный компьютер Radxa Orion O6N обеспечивает ИИ-производительность до 45 TOPSКомпания Radxa, как сообщает ресурс CNX Software, пополнила ассортимент одноплатных компьютеров моделью Orion O6N в форм-факторе Nano-ITX. Новинка предназначена для создания различных устройств с ИИ-функциями. В основу положен процессор Cix P1 (CD8160), который объединяет 12 ядер Arm в конфигурации 4 × Cortex-A720 с тактовой частотой до 2,6 ГГц, 4 × Cortex-A720 с частотой 2,4 ГГц и 4 × Arm Cortex-A520 с частотой 1,8 ГГц. Имеется графический ускоритель Arm Immortalis G720 MC10 с поддержкой Vulkan 1.3, OpenGL ES 3.2, OpenCL 3.0. Встроенный VPU-блок обеспечивает возможность декодирования материалов 8Kp60 AV1, H.265, H.264, VP9, VP8, H.263, MPEG-4 и MPEG-2, а также кодирования 8Kp30 H.265, H.264, VP9 и VP8. В состав чипа входит нейропроцессорный модуль (NPU) с производительностью до 30 TOPS (заявлена поддержка операций INT4/INT8/INT16, FP16/BF16, TF32). Общее ИИ-быстродействие Cix P1 достигает 45 TOPS. Изделие изготавливается по 6-нм технологии TSMC. Одноплатный компьютер может нести на борту от 8 до 64 Гбайт оперативной памяти LPDDR5-5500 (вариант с 32 Гбайт стоит около $200). Есть два коннектора M.2 M-Key для SSD с интерфейсом PCIe 4.0 x4 (NVMe) и разъём UFS. Кроме того, предусмотрены слот M.2 E-Key (PCIe 4.0 x2 + USB) для адаптера Wi-Fi 7/6E и Bluetooth, а также слот M.2 B-Key для модема 4G/5G. Присутствует двухпортовый сетевой контроллер 2.5GbE. Допускается вывод изображения одновременно на три монитора через интерфейсы HDMI 2.0 (до 4Kp60), DisplayPort 1.4 (до 4Kp120) и USB Type-C (DisplayPort Alt Mode; до 4Kp60). Упомянуты два интерфейса MIPI CSI (4 линии) и 40-контактная колодка GPIO с поддержкой 3 × UART, 2 × I2C, 2 × I2S, 2 × PWM, 1 × SPI и пр. В число доступных разъёмов входят два гнезда RJ45 для сетевых кабелей, три порта USB 2.0 Type-A, два порта USB 3.2 Gen2 Type-A, разъём USB 3.2 Gen2 Type-C. Питание (12 В) подаётся через DC-коннектор (5,5/2,5 мм). Габариты составляют 120 × 120 мм. Есть 4-контактный разъём для подсоединения вентилятора охлаждения с ШИМ-управлением. Заявлена совместимость с Debian/Ubuntu Linux.

16.10.2025 [00:33], Владимир Мироненко

От мВт до МВт: Arm и Meta✴ объявили о стратегическом партнёрство в области ИИArm Holdings и Meta✴ Platforms объявили о стратегическом партнёрстве, направленном на «масштабирование эффективности ИИ на каждом уровне вычислений, охватывающем ПО и инфраструктуру ЦОД». Как отмечено в пресс-релизе, сотрудничество позволит использовать ИИ в различных типах вычислений, рабочих нагрузках и процессах, которые лежат в основе глобальных платформ Meta✴, а также объединить «лидерство Arm в области энергоэффективных вычислений на базе ИИ с инновациями Meta✴ в области продуктов, инфраструктуры и открытых технологий на базе ИИ для достижения значительного повышения производительности и эффективности». «От взаимодействия с нашими платформами до создаваемых нами устройств, ИИ меняет способы взаимодействия и творчества людей. Партнёрство с Arm позволяет нам эффективно масштабировать эти инновации для более чем 3 млрд пользователей приложений и технологий Meta✴», — заявил руководитель глобальной инфраструктуры Meta✴. Сообщается, что в рамках сотрудничества системы ранжирования и рекомендаций Meta✴ на основе ИИ, играющие ключевую роль в поиске и персонализации в таких сервисах, как Facebook✴ и Instagram✴, будут использовать платформы Arm Neoverse для обеспечения более высокой производительности и более низкого энергопотребления по сравнению с x86-системами. Решения британского разработчика также позволят Meta✴ улучшить показатель производительности на Вт, что подчёркивает эффективность и масштабируемость Arm для гиперскейлеров, отметила Arm. Сделка с Meta✴ станет важным подтверждением эффективности архитектуры Arm, которая конкурирует с устоявшейся архитектурой x86, используемой Intel и AMD, отметило агентство Reuters. Новое соглашение позволит углубить сотрудничество в области оптимизации ПО для ИИ-технологий в рамках фреймворка МО PyTorch, движка выполнения периферийных вычислений ExecuTorch и движка инференса vLLM, а также обеспечит дальнейшее совершенствование платформы Executorch, оптимизированной с помощью Arm KleidiAI. Также компании отметили, что сотрудничество позволит упростить развёртывание ИИ-моделей и повысить производительность ИИ-приложений от периферии до облака.

Источник изображения: Meta✴ Сообщается, что проекты с открытым исходным кодом играют ключевую роль в стратегии Meta✴ в области ИИ, позволяя разрабатывать и внедрять различные решения: от рекомендаций до разговорного интеллекта. Компании подтвердили намерение расширять в дальнейшем возможности оптимизации этих проектов с открытым исходным кодом, позволяя миллионам разработчиков по всему миру создавать и запускать ИИ-решения на базе Arm. Работа над открытым исходным кодом будет способствовать более широкому внедрению Arm-архитектуры за счет повышения совместимости ПО, что является ключевым препятствием для её более широкого использования, пишет Reuters. Как отметил ресурс TechCrunch, Arm и Meta✴ не обмениваются долями собственности или элементами инфраструктуры, что отличает это соглашение о сотрудничестве от ряда недавних сделок на рынке ИИ-инфраструктуры. Доля Arm на рынке серверных процессоров стремительно выросла за последние годы, во многом благодаря ИИ-платформам NVIDIA. По данным The Register, пока речь идёт как раз об оптимизации ПО для уже развёрнутых Arm-платформ, а не о создании кастомного CPU. |

|