Материалы по тегу: arm

|

14.03.2026 [10:16], Сергей Карасёв

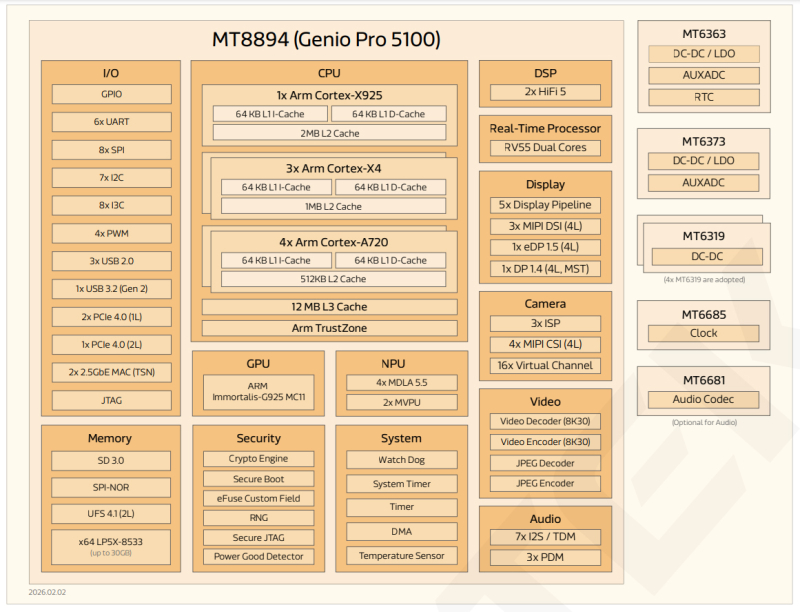

MediaTek представила чипы Genio Pro 5100 и Genio 420 для AIoT-приложенийКомпания MediaTek представила процессоры Genio Pro 5100 и Genio 420 с архитектурой Arm для AIoT-приложений и встраиваемых систем. Первый из названных чипов подходит, в частности, для автономных мобильных роботов, дронов, периферийного оборудования и автомобильных платформ, второй — для устройств умного дома, интерактивных дисплеев и пр. Изделие Genio Pro 5100 изготавливается по 3-нм технологии. Оно содержит восемь вычислительных ядер в конфигурации 1 × Arm Cortex-X925, 3 × Arm Cortex-X4 и 4 × Arm Cortex-A720. Присутствуют графический блок Arm Immortalis-G925 MC11 с поддержкой OpenGL, Vulkan и OpenCL, а также нейропроцессорный узел (NPU) с ИИ-производительностью более 50 TOPS. Модуль VPU обеспечивает возможность кодирования материалов H.264 и H.265 (до 8K30) и декодирования H.264, H.265, AV1 и VP9 (до 8K30). Реализована поддержка оперативной памяти LPDDR5x-8533 (до 30 Гбайт), а также флеш-памяти UFS 4.1, SD 3.0 и SPI-NOR. Допускается вывод изображения одновременно на три дисплея формата 4Kp60 через интерфейсы eDP 1.5 (4 линии), DisplayPort 1.4 (MST) и 3 × MIPI DSI (4 линии). Благодаря четырём интерфейсам MIPI-CSI (4 линии) возможно использование до 16 камер (1080p30). Среди прочего упомянута поддержка 2 × 2.5GbE, Wi-Fi 7 и Bluetooth 5.4 (через внешний модуль), 1 × PCIe 4.0 (2 линии) и 2 × PCIe 4.0 (1 линия), 6 × UART, 7 × I2C, 8 × I3C, 4 × PWM, 7 × I2S/TDM, 3 × PDM, 1 × USB 3.2 Gen2 (10 Гбит/с), 2 × USB 2.0 (Host/Device) и 1 × USB 2.0 (Host). Изделие выполнено в корпусе ETFC TFBGA с размерами 15,9 × 16,6 мм. Диапазон рабочих температур простирается от -40 до +105 °C. Вторая новинка, Genio 420, производится по 6-нм технологии. Процессор объединяет восемь ядер (2 × Arm Cortex-A78 с тактовой частотой 1,8 ГГц и 6 × Arm Cortex-A55 с частотой 1,6 ГГц) и графический ускоритель Arm Mali-G57 MC2. Модуль MediaTek NPU восьмого поколения обеспечивает ИИ-производительность на уровне 6,1 TOPS. Блок VPU поддерживает кодирование материалов H.264/H.265 (до 4Kp30) и декодирование H.264/H.265/VP9 (до 4Kp60) и MPEG4/VP8 (до 1080p60). Чип позволяет использовать оперативную память LPDDR4X-4266 (до 8 Гбайт) и LPDDR5/LPDDR5X-6400 (до 16 Гбайт), а также флеш-память UFS 3.1 (2 линии), eMMC 5.1, SD 3.0 / SDIO 3.0, SPI-NOR. Возможен вывод изображения на монитор 4Kp60 или два дисплея 2.5Kp60 через интерфейсы eDP, DP, LVDS и MIPI-DSI. Допускается использование до шести камер 1080p30 через 2 × MIPI-CSI. Прочие характеристики процессора таковы: контроллер 1GbE, опциональные адаптеры Wi-Fi 6 (1×1) + Bluetooth 5.3 на базе MT6631X или Wi-Fi 6E (2×2) + Bluetooth 5.3 на основе MT6637X, 1 × PCIe 2.0 (1L, RC, WoWLan), 4 × UART, 9 × I2C, 6 × SPI Master, 3 × PWM, GPIO, JTAG, 3 × USB 2.0, 1 × USB 3.2 Gen1 (5 Гбит/с; Host), 1 × USB 3.2 Gen1 (Host/Device). Чип выполнен в корпусе VFBGA с размерами 13,8 × 11,8 × 0,9 мм. Диапазон рабочих температур — от -20 до +95 °C. Процессоры поддерживают такие средства обеспечения безопасности, как Arm TrustZone, Security Boot (RSA4096), Crypto Engine и RNG. Говорится о совместимости с различными вариантами Linux, включая Yocto и Ubuntu.

07.03.2026 [22:20], Сергей Карасёв

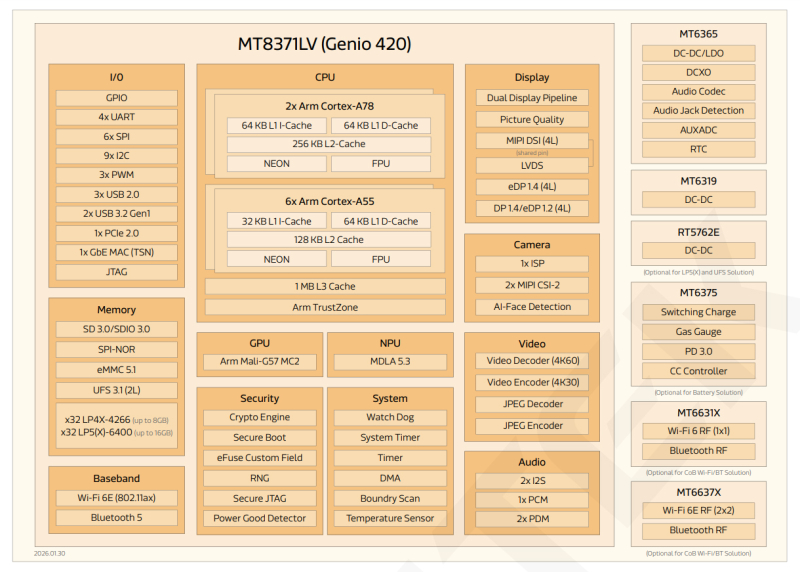

640 Кбайт хватит для ИИ: микроконтроллеры STM32U3B5/C5 со сверхнизким энергопотреблением могут работать даже без батарейSTMicroelectronics анонсировала микроконтроллеры STM32U3B5 и STM32U3C5, ориентированные на автономные устройства с функциями ИИ и машинного обучения. Изделия отличаются сверхнизким энергопотреблением и возможностью перехода в режим глубокого сна при отсутствии данных. Таким образом, допускается работа без батарей — исключительно за счёт преобразования энергии окружающей среды (свет, тепло, вибрации, радиоволны) в электрическую. Микроконтроллеры используют 32-бит ядро Arm Cortex-M33 с частотой 96 МГц. Заявленная производительность достигает 1,5 DMIPS/МГц (Dhrystone 2.1) и 395,4 CoreMark (4,12 CoreMark/МГц). В оснащение входит HSP (Hardware Signal Processor) — специальный блок, предназначенный для ускорения определенных вычислений, связанных с ИИ. Есть 640 Кбайт SRAM и 2 Мбайт флеш-памяти. Предусмотрены интерфейсы SDMMC и OCTOSPI с поддержкой внешней памяти SRAM, PSRAM, NOR, NAND и FRAM. Реализована поддержка 114 × GPIO, USB 2.0, SAI (Serial Audio Interface), 4 × I2C FM+, SMBus/PMBus, 3 × I3C (SDR), 3 × USART и 2 × UART (SPI, ISO 7816, LIN, IrDA, Modem), 1 × LPUART, 4 × SPI, 2 × CAN FD, GPDMA (12 каналов), 2 × 12-bit ADC, 12-bit DAC и др. Возможны различные варианты исполнения, в том числе UFQFPN48 (7 × 7 мм), LQFP48 (7 × 7 мм), LQFP64 (10 × 10 мм), WLCSP72 (3,67 × 3,58 мм), WLCSP99 (3,67 × 3,58 мм), LQFP100 (14 × 14 мм), WLCSP126 (3,67 × 3,58 мм), UFBGA132 (7 × 7 мм) и LQFP144 (20 × 20 мм). Диапазон рабочих температур простирается от -40 до +105 °C. В микроконтроллеры встроены развитые средства безопасности, включая Arm TrustZone, генератор случайных чисел TRNG, защиту от несанкционированного доступа и пр. Единственное различие между решениями STM32U3B5 и STM32U3C5 заключается в том, что второе включает криптографическое ядро для ускорения операций шифрования и дешифрования. Цена варьируется от $2,9298 до $4,6829 за штуку в зависимости от конфигурации при заказах партий от 10 тыс. единиц.

19.02.2026 [12:50], Сергей Карасёв

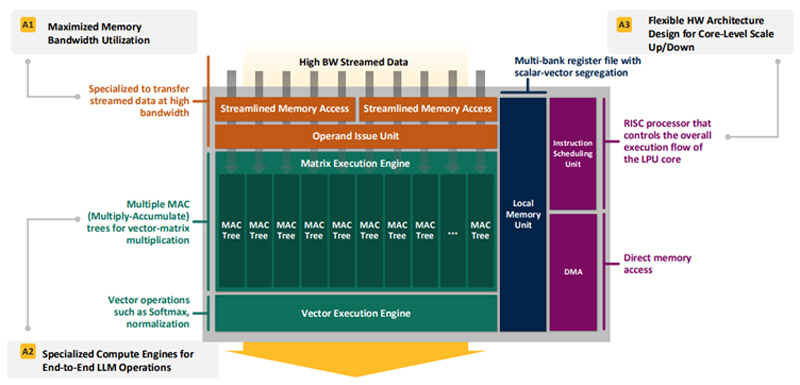

Впятеро энергоэффективнее H100: HyperAccel разработала экономичный чип Bertha 500 для ИИ-инференсаЮжнокорейский стартап HyperAccel, по сообщению EETimes, готовится вывести на рынок специализированный чип Bertha 500, предназначенный для ИИ-инференса. Утверждается, что благодаря особой архитектуре изделие способно генерировать в пять раз больше токенов в секунду по сравнению с решениями на основе GPU при том же уровне TOPS. В Bertha 500 упор сделан на экономическую эффективность. С этой целью используется память LPDDR вместо дорогостоящей HBM. При этом благодаря отказу от традиционной иерархии памяти достигается утилизация пропускной способности LPDDR на 90 %. Дальнейшее повышение эффективности обеспечивается путём оптимизации архитектуры именно для задач инференса. Для сравнения, как утверждает HyperAccel, в случае GPU при инференсе используется только около 45 % пропускной способности памяти и 30 % вычислительных ресурсов. Иными словами, немного жертвуя производительностью, чип Bertha 500 позволяет достичь значительного снижения стоимости. Изделие Bertha 500 будет производиться по 4-нм техпроцессу Samsung. В состав чипа входят 32 ядра LPU (LLM Processing Unit), четыре ядра Arm Cortex-A53 и 256 Мбайт SRAM. Подсистема памяти LPDDR5x использует восемь каналов; пропускная способность достигает 560 Гбайт/с. Заявленная ИИ-производительность на операциях INT8 составляет 768 TOPS. Кроме того, поддерживаются другие 16-, 8- и 4-бит форматы, включая FP16. В целом, по заявлениям HyperAccel, пропускная способность Bertha 500 в расчёте на доллар примерно в 20 раз выше по сравнению с NVIDIA H100, тогда как энергоэффективность больше в пять раз. Чип Bertha 500 будет потреблять около 250 Вт.

Источник изображения: EETimes Программный стек HyperAccel поддерживает все модели из репозитория HuggingFace. Кроме того, компания работает над предметно-ориентированным языком (DSL) под названием Legato, который предоставит разработчикам низкоуровневый доступ к системе. Образцы Bertha 500 появятся к концу I квартала 2026 года, а серийное производство планируется организовать в начале 2027 года. Отмечается также, что совместно с LG стартап разрабатывает «урезанную» версию Bertha 500 для периферийных устройств — Bertha 100. Эта SoC получит ядра Arm Cortex-A55 и отдельные компоненты LG, а также два канала памяти LPDDR5x. Среди возможных сфер применения названы автомобильная промышленность, бытовая электроника и робототехника. Bertha 100 планируется выпускать в виде модулей M.2: первые изделия выйдут в IV квартале текущего года. Решение сможет, например, осуществлять преобразование текста в речь или речи в текст. Стартап HyperAccel основан профессором Корейского института передовых технологий (KAIST) Джуёном Кимом (Jooyoung Kim) вместе с группой его студентов в начале 2023 года. На сегодняшний день компания привлекла $45 млн инвестиций, а её рыночная стоимость оценивается в $200 млн. Штат насчитывает около 80 человек. Первым продуктом HyperAccel стал специализированный сервер Orion на базе FPGA, предназначенный для решения ИИ-задач.

18.02.2026 [09:19], Сергей Карасёв

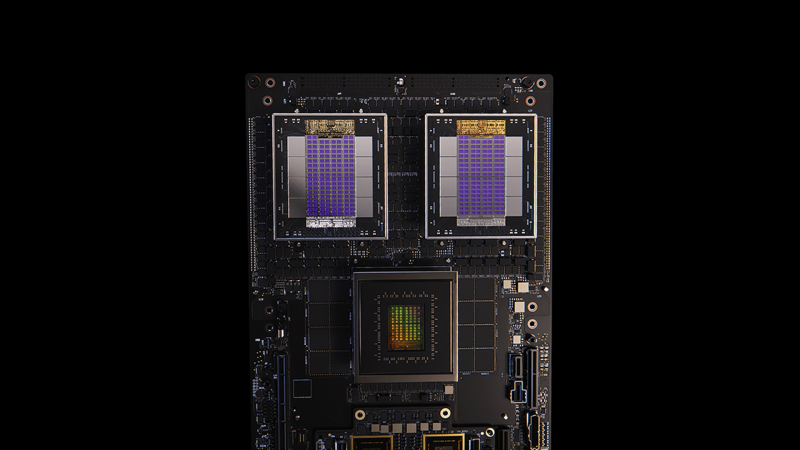

Meta✴ развернёт ИИ-инфраструктуру на «миллионах ускорителей NVIDIA Blackwell и Rubin», а также Arm-чипах GraceКомпании NVIDIA и Meta✴ объявили о многолетнем стратегическом партнёрстве, охватывающем локальную, облачную и ИИ-инфраструктуры. В частности, Meta✴ будет использовать в своих дата-центрах решения NVIDIA как для обучения больших языковых моделей (LLM), так и для инференса. Сообщается, что Meta✴ возьмёт на вооружение чипы NVIDIA Grace, которые будут использоваться в серверах, основанных исключительно на CPU-архитектуре (без ускорителей на основе GPU). Изделия Grace, напомним, объединяют 72 вычислительных ядра Armv9 Neoverse V2 (Demeter) с тактовой частотой до 3,35 ГГц и до 480 Гбайт памяти LPDDR5x. Доступна также сборка Grace Superchip, которая состоит из двух кристаллов Grace и чипов памяти LPDDR5x общим объёмом до 960 Гбайт. Meta✴ намерена применять изделия Grace для решения общих задач, а также поддержания работы ИИ-агентов, которым не требуются ИИ-ускорители. Вице-президент NVIDIA Иэн Бак (Ian Buck) отмечает, что решения Grace способны обеспечить вдвое большую производительность на 1 Вт при выполнении операций общего назначения по сравнению с альтернативными платформами. В дальнейшем Meta✴ планирует использовать Arm-процессоры NVIDIA следующего поколения — решения Vera. Крупномасштабные развёртывания систем на базе Vera намечены на 2027 год, что поможет Meta✴ в развитии энергоэффективных вычислений и формировании широкой экосистемы Arm.

Источник изображения: Meta✴ Кроме того, в рамках партнёрства Meta✴ будет использовать «миллионы ускорителей NVIDIA Blackwell и Rubin». Так, на основе изделий NVIDIA GB300 компании создадут единую среду, охватывающую локальные дата-центры и облачные ресурсы, что позволит упростить операции при одновременном улучшении производительности и масштабируемости. Среди прочего Meta✴ будет применять сетевую платформу NVIDIA Spectrum-X Ethernet и технологию NVIDIA Confidential Computing для защиты данных. «Мы рады расширить партнёрство с NVIDIA с целью создания передовых кластеров на основе платформы Vera Rubin — это позволит предоставить персональный суперинтеллект каждому человеку в мире», — говорит Марк Цукерберг (Mark Zuckerberg), основатель и генеральный директор Meta✴. Нужно отметить, что среди гиперскейлеров только Meta✴ и Oracle используют в своих инфраструктурах сторонние чипы с архитектурой Arm. В то же время AWS, Google и Microsoft развивают собственные Arm-проекты — изделия Graviton, Axion и Cobalt соответственно.

16.12.2025 [11:30], Сергей Карасёв

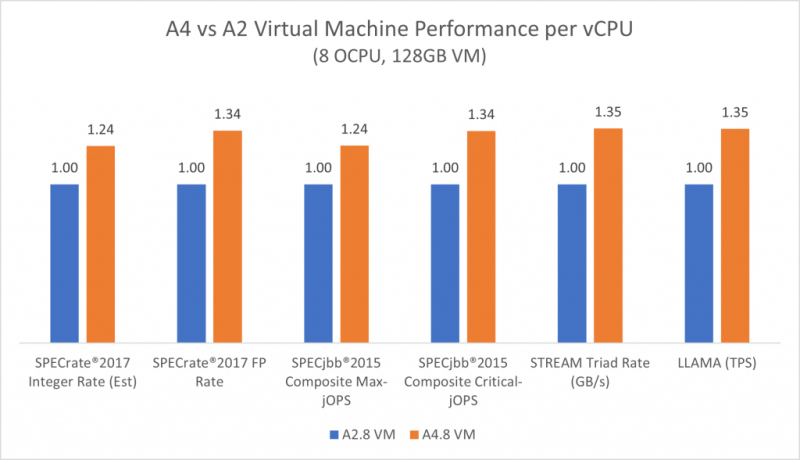

192-ядерные Arm-процессоры AmpereOne M появились в облаке OracleКомпании Ampere и Oracle объявили о том, что в облачной инфраструктуре OCI (Oracle Cloud Infrastructure) стали доступны инстансы A4 Standard на основе процессоров AmpereOne M. Эти экземпляры, как утверждается, подходят для широкого спектра рабочих нагрузок — от традиционных корпоративных приложений до ресурсоёмких задач ИИ-инференса. Чипы AmpereOne M содержат от 96 до 192 кастомизированных 64-бит ядер на базе Arm v8.6+. Используются 12 каналов DDR5-5600 с возможностью установки до 3 Тбайт памяти и 96 линий PCIe 5.0. Тактовая частота варьируется от 2,6 до 3,6 ГГц, показатель TDP — от 239 до 348 Вт. Инстансы A4 Standard обеспечивают более высокую производительность на ядро и большую пропускную способность памяти, чем экземпляры предыдущих поколений OCI A1 и A2 с чипами Ampere. Клиентам доступны виртуальные машины VM.Standard.A4.Flex с 45 OCPU (каждый OCPU содержит два ядра AmpereOne M), 700 Гбайт памяти, блочным хранилищем и сетевым подключением с пропускной способностью 100 Гбит/с. Кроме того, предлагаются экземпляры BM.Standard.A4.48 класса Bare Metal с 48 OCPU, 768 Гбайт памяти, накопителем вместимостью 3,84 Тбайт в рамках блочного хранилища и сетевым подключением на 100 Гбит/с. Заказчики, переходящие с виртуальных машин OCI A2, могут рассчитывать на повышение производительности каждого ядра до 35 % — в зависимости от рабочей нагрузки. Для ресурсоёмких вычислительных задач заявлено улучшение показателей SPECint до 24 % и SPECfp до 34 %: это особенно важно для таких приложений, как аналитика данных, пакетная обработка и научные вычисления. В случае рабочих нагрузок, чувствительных к задержкам, обеспечивается улучшение производительности SPECjbb до 34 %. Oracle подчёркивает, что для инстансов A4 Standard действуют выгодные цены: $0,0138 в расчёте на OCPU в час и $0,0027 за 1 Гбайт в час. В целом, на сегодняшний день более 110 сервисов OCI работают на оборудовании с процессорами Ampere.

11.12.2025 [12:38], Сергей Карасёв

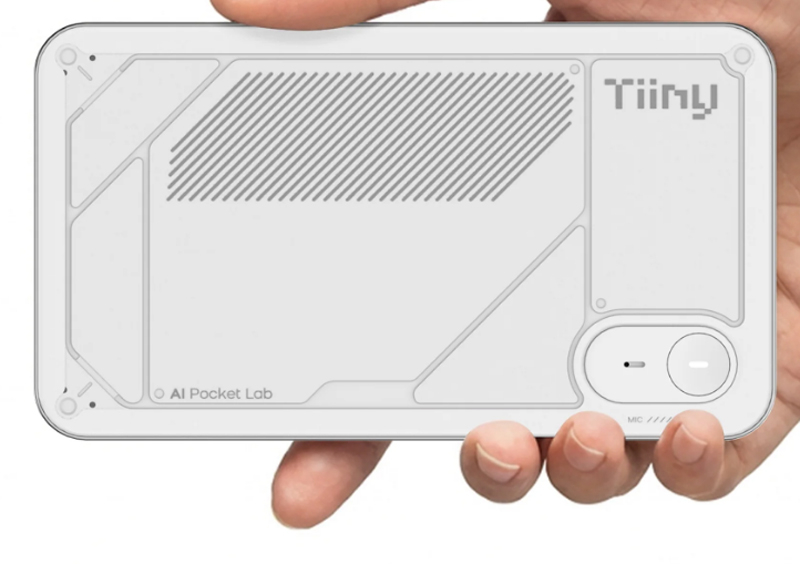

«Карманный ИИ-суперкомпьютер» Tiiny AI Pocket Lab справляется с LLM, насчитывающими до 120 млрд параметровАмериканский стартап Tiiny AI представил устройство AI Pocket Lab: это, как утверждается, самый компактный в мире персональный суперкомпьютер для задач ИИ. Он способен работать с большими языковыми моделями (LLM), насчитывающими до 120 млрд параметров: при этом не требуется подключение к облачным сервисам. Устройство заключено в корпус с размерами 142 × 80 × 25,3 мм, а вес составляет около 300 г. Применён процессор с 12 вычислительными ядрами на архитектуре Armv9.2. Кроме того, задействован нейромодуль dNPU. Общий объём памяти LPDDR5X составляет 80 Гбайт, из которых 32 Гбайт приходится на CPU и 48 Гбайт — на dNPU. В оснащение входит SSD вместимостью 1 Тбайт. Типовое энергопотребление находится на уровне 65 Вт.

Источник изображений: Tiiny AI Суммарная заявленная ИИ-производительность достигает 190 TOPS: из них примерно 30 TOPS обеспечивает CPU, ещё 160 TOPS — блок dNPU. Компьютер ориентирован прежде всего на локальную работу с моделями, насчитывающими от 10 до 100 млрд параметров: подобные решения, как утверждается, удовлетворяют более чем 80% реальных потребностей. Устройство может поддерживать такие функции, как многоэтапное рассуждение, глубокое понимание контекста, агенты ИИ, генерация контента и безопасная обработка конфиденциальной информации без необходимости подключения к удалённым серверам.  Tiiny AI Pocket Lab поддерживает быструю установку популярных открытых ИИ-моделей, включая OpenAI GPT-OSS, Llama, Qwen, DeepSeek, Mistral и Phi. При этом могут развертываться различные ИИ-агенты, например, OpenManus, ComfyUI, Flowise, Presenton, Libra, Bella и SillyTavern. Среди потенциальных пользователей компьютера названы разработчики, исследователи, создатели контента, учащиеся и пр. Новинка будет демонстрироваться в следующем месяце на выставке электроники CES 2026.

04.12.2025 [22:18], Владимир Мироненко

AWS анонсировала 192-ядерные серверные Arm-процессоры Graviton5AWS анонсировала свой самый мощный на сегодняшний день серверный Arm-процессор — 3-нм 192-ядерный Graviton5. Новые инстансы M9g на базе Graviton5 отличаются более высокой производительностью благодаря впятеро большему общему L3-кешу и в 2,6 раза большему объёму кеша на ядро по сравнению с Graviton4, более высокой скорости памяти и повышенной пропускной способности сетевого подключения. Также компания снизила задержку передачи данных между ядрами на треть. В Graviton5 появилась функция Nitro Isolation Engine с формальной верификацией изоляции исполняемых рабочих нагрузок друг от друга и от самой AWS. Процессоры предлагают полное шифрование памяти, расширенный предсказатель ветвлений, улучшенную подсистему предвыборки выделенные кеши для каждого vCPU и аутентификацию указателей (PAC). Кроме того, Graviton5 получили систему охлаждения на кристалле. Процессор содержит 172 млрд транзисторов. Процессор использует ядра Neoverse V3 (Poseidon) с ISA Armv9.2-A. Хотя сам чип монолитный, он разделён на два NUMA-домена для снижения задержек обращений к памяти. Каждому ядру полагается 2 Мбайт L2-кеша, а общий объём L3-кеша составляет 192 Мбайт — суммарно 576 Мбайт. Процессор имеет 12 каналов DDR5-8800, причём AWS работает с поставщиками памяти для валидации их DIMM. Также отмечено снижение задержки доступа до менее чем 100 нс. Для связи с внешним миром есть восемь контроллеров PCIe 6.0. Как сообщается, клиенты AWS уже провели первые тесты Graviton5, показавшие прирост производительности от 25 до 60 % в зависимости от типа рабочей нагрузки. Помимо инстансов M9g в 2026 году также появятся инстансы C9g для ресурсоёмких вычислений и R9g с оптимизацией по памяти. Новые инстансы имеют в среднем на 15 % более высокую скорость сетевого подключения и на 30 % более высокую скорость доступа к EBS-томам (в том числе с шифрованием). Кроме того, они получили чипы Nitro 6, ответственные за виртуализацию, защиту и разгрузку сетевых функций и функция хранения. Процессоры Graviton теперь обеспечивают более половины всех новых вычислительных мощностей, добавляемых в AWS третий год подряд, причем 98 % из 1000 ведущих клиентов EC2 уже используют эту архитектуру. Постепенно осваивают Arm и прямые конкуренты Amazon — Google активно портирует своё ПО на CPU Axion, у Microsoft недавно представила уже второе поколение процессоров Cobalt.

21.11.2025 [23:59], Сергей Карасёв

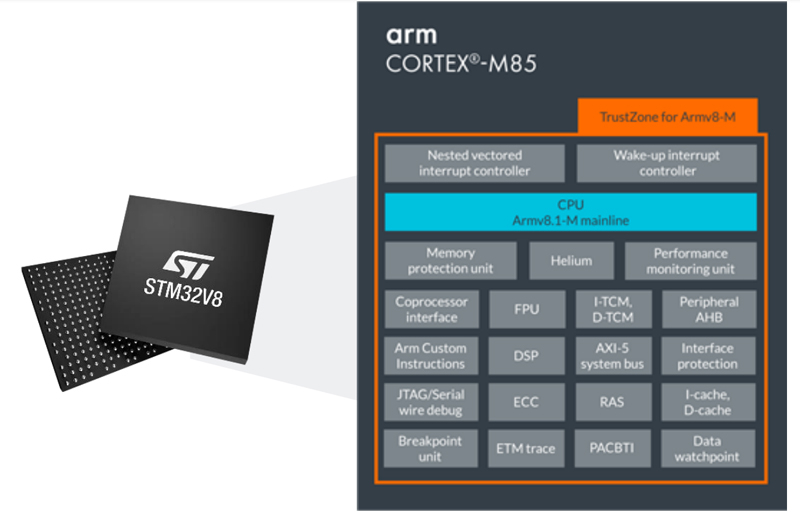

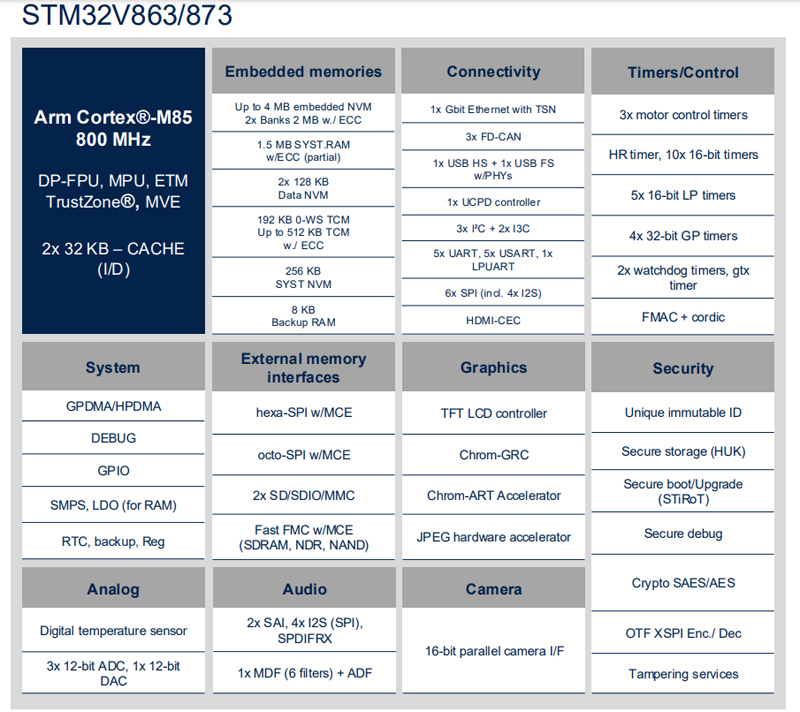

По-настоящему космический микроконтроллер STMicroelectronics STM32V8 пропишется в спутниках Starlink: 800 Мгц, защита от радиации и работа при +140 °CКомпания STMicroelectronics анонсировала микроконтроллер STM32V8 для индустриальной сферы. Среди возможных областей применения названы системы промышленной автоматизации, робототехника, оборудование для аэрокосмической отрасли и здравоохранения, устройства для умных городов и пр. Изделие изготавливается по 18-нм техпроцессу FD-SOI в партнёрстве с Samsung Foundry. Основой служит 32-бит ядро Arm Cortex-M85 (до 800 МГц) с поддержкой Arm Helium, Arm MVE и TrustZone. По заявлениям STMicroelectronics, на сегодняшний день новинка является самым производительным микроконтроллером серии STM32. Одной из особенностей STM32V8 является наличие 4 Мбайт (два блока по 2 Мбайт) энергонезависимой памяти на основе фазового перехода (РСМ). Она устойчива к воздействию радиации, что позволяет использовать микроконтроллер в том числе в космическом пространстве. Отмечается, что компания SpaceX будет применять изделие в своих спутниках системы Starlink. Еще одна особенность решения — широчайший диапазон рабочих температур, который простирается от -40 до +140 °C.

Источник изображений: STMicroelectronics В состав чипа входят графический блок Chrom-ART 2D GPU и аппаратный JPEG-ускоритель. Есть 1,5 Мбайт памяти System SRAM с поддержкой ECC и 8 Кбайт памяти Backup RAM. Реализованы интерфейсы внешней памяти Hexa-SPI, Octo-SPI, 2 × SD/SDIO/MMC, SDRAM, NAND. Упомянута поддержка 1GbE, 2 × SAI, 4 × I2S, S/PDIF Rx, 1 × USB HD, 1 × USB FS, UCPD (USB-C PD), 3 × I2C, 2 × I3C, 5 × USART, 5 × UART, 1 × LPUART, 3 × FD-CAN, 6 × SPI, 3 × ADC (12 бит), 1 × DAC (12 бит).  Для микроконтроллера доступны различные варианты исполнения, включая 68-pin VQFN (8 × 8 мм), 100-pin LQFP/TFBGA (14 × 14 или 8 × 8 мм), 144-pin LQFP (20 × 20 мм), 176-pin LQFP (24 × 24 мм), 176+25-pin UFBGA (10 × 10 мм) и 273-pin TFBGA (14 × 14 мм). Пробные поставки изделия избранным клиентам уже начались. Массовые отгрузки запланированы на следующий год.

19.11.2025 [15:39], Сергей Карасёв

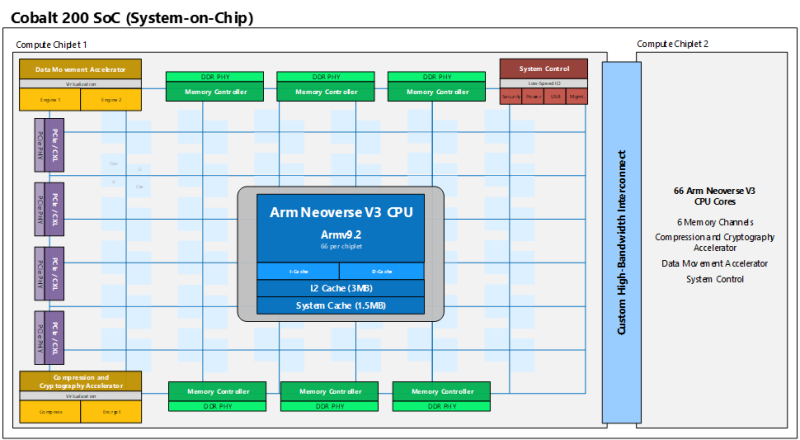

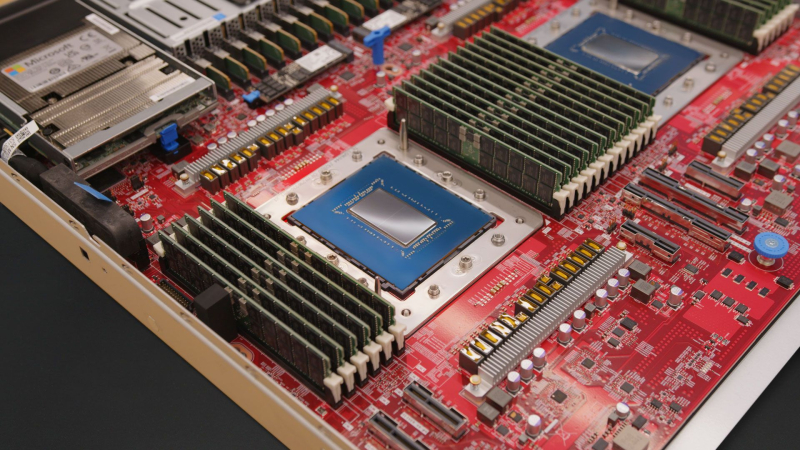

132 «динамических» Arm-ядра и 12 каналов памяти: Microsoft представила процессоры Cobalt 200 для облака AzureКорпорация Microsoft анонсировала процессоры Cobalt 200 на архитектуре Arm, спроектированные специально для облачных платформ. Изделия, в частности, будут применяться в составе инстансов Azure следующего поколения. Первые серверы на базе Cobalt 200 уже запущены в дата-центрах Microsoft, а более широкое внедрение намечено на 2026 год. Оригинальные чипы Cobalt 100 дебютировали в ноябре 2023 года. Они объединяют 128 ядер Armv9 Neoverse N2 (Perseus). Они развёрнуты уже в 32 регионах Azure. И Microsoft, и её клиенты успешно переносят на новые чипы часть своих нагрузок. В частности, после миграции производительность Microsoft Teams выросла на 45 %, теперь сервису требуется на 35 % меньше вычислительных ядер при обработке видео- и аудиостриминга. Среди крупных пользователей Cobalt 100 компания также называет Databricks и Snowflake. При разработке Cobalt 200, как заявляет Microsoft, были оценены более 350 тыс. вариантов конфигурации. С помощью моделирования и ИИ были оценены различные комбинации компонентов — от ядер, кешей и памяти до питания, архитектуры отдельных узлов и целых стоек. Созданное в результате изделие по производительности более чем на 50 % превосходит решения первого поколения в реальных нагрузках Azure, данные о которых были собраны с помощью телеметрии, при сохранении энергоэффективности, говорит компания. Cobalt 200 представляет собой SoC, состоящую из двух чиплетов. Каждый из них насчитывает 66 ядер с архитектурой Armv9.2 (Neoverse V3) и шесть каналов DDR. Таким образом, в общей сложности используются 132 ядра и 12 каналов памяти. Чипы получили 3 Мбайт L2-кеша в расчёте на ядро и 192 Мбайт общего L3-кеша. Количество и тип линий PCIe/CXL не уточняется. Одной из уникальных особенностей процессоров является индивидуальное динамическое регулирование напряжения и частоты (DVFS) для каждого ядра. Это означает, что каждое из 132 ядер может работать с разным уровнем производительности, обеспечивая оптимальное энергопотребление независимо от нагрузки. Изделия производятся по 3-нм техпроцессу TSMC. При разработке Cobalt 200 особое внимание уделено безопасности. Применён специальный контроллер памяти с активированным по умолчанию шифрованием, которое практически не влияет на производительность. Кроме того, реализована архитектура Arm CCA (Confidential Compute Architecture) с поддержкой аппаратной изоляции памяти виртуальной машины от гипервизора и операционной системы хоста. Кроме того, компания внедрила в чипы блоки аппаратного ускорения компрессии и шифрования данных собственной разработки. Узлы с новыми чипами получили DPU Azure Boost и аппаратный HSM-модуль.

18.11.2025 [23:59], Владимир Мироненко

Arm добавила Neoverse поддержку NVIDIA NVLink FusionArm объявила о расширении возможностей платформы Neoverse с помощью NVIDIA NVLink Fusion в рамках партнёрства с NVIDIA, обеспечивая всей экосистеме ту же производительность, пропускную способность и эффективность, которые впервые были реализованы на платформах Grace Hopper и Grace Blackwell. «NVLink Fusion — это связующее звено эпохи ИИ, объединяющее все CPU, GPU и ускорители в единую архитектуру стоечного масштаба», — заявил Дженсен Хуанг (Jensen Huang), основатель и генеральный директор NVIDIA. Как сообщается в пресс-релизе, два года назад Arm и NVIDIA представили платформу Grace Hopper, в которой технология NVLink обеспечила согласованную интеграцию CPU и GPU. NVLink Fusion обеспечивает компаниям возможность подключать вычислительные системы на базе Arm к предпочитаемым ими ускорителям через согласованный интерфейс с высокой пропускной способностью. Устойчивый спрос на Grace Blackwell способствует распространению NVLink Fusion во всей экосистеме Neoverse, позволяя партнёрам создавать дифференцированные, энергоэффективные ИИ-системы на базе Arm, отвечающие современным требованиям к производительности и масштабируемости. Arm отметила, что на текущий момент развёрнуто более чем 1 млрд ядер Neoverse и уверенно движется к достижению 50 % доли рынка среди ведущих гиперскейлеров к 2025 году. Все крупные провайдеры — AWS, Google, Microsoft, Oracle и Meta✴ — используют Neoverse, а ИИ ЦОД следующего поколения, такие как проект Stargate, используют Arm как основную вычислительную платформу. NVLink Fusion совместим с технологией AMBA CHI C2C (Coherent Hub Interface Chip-to-Chip) компании Arm, которая обеспечивает когерентное высокоскоростное соединения между CPU и ускорителями. Arm внедряет в платформу Neoverse последнюю версию протокола AMBA CHI C2C, чтобы SoC Neoverse могли беспрепятственно передавать данные между CPU Arm и ускорителями. Благодаря этому обеспечивается более быстрая интеграция, более быстрый вывод на рынок и большая гибкость для разработчиков ИИ-систем нового поколения. В свою очередь, NVIDIA работает над стандартизацией многих компонентов в этих системах для повышения надёжности и времени безотказной работы. С этой целью в CPU NVIDIA Vera следующего поколения будут использоваться кастомные ядра Arm вместо ядер Neoverse. Fujitsu также разрабатывает собственные Arm-процессоры MONAKA-X, которые тоже получат NVLink Fusion. NVLink Fusion получат и x86-процессоры Intel. |

|