Компания Ampere Computing анонсировала процессоры семейства AmpereOne M, разработанные специально для поддержания ресурсоёмких ИИ-нагрузок в дата-центрах. Утверждается, что чипы подходят для задач инференса, работы с большими языковыми моделями (LLM), генеративным ИИ и пр.

О подготовке новых изделий впервые сообщалось летом прошлого года. Конфигурация процессоров включает от 96 до 192 кастомизированных 64-бит ядер на базе Arm v8.6+. Имеется 16 Кбайт кеша инструкций и 64 Кбайт кеша данных L1 в расчёте на ядро, а также 2 Мбайт L2-кеша на ядро. Объём системного кеша составляет 64 Мбайт. Реализованы 12 каналов DDR5-5600 (поддерживается один модуль DIMM на канал) с возможностью адресации до 3 Тбайт памяти.

Источник изображений: Ampere

Конструкция чипов включает 96 линий PCIe 5.0 с поддержкой бифуркации до режима x4 и возможностью использования до 24 дискретных подключённых устройств. Упомянуты средства виртуализации, шифрование памяти, поддержка прерываний I2C, GPIO, QSPI и GPI, системный и сторожевой таймеры. Предусмотрены развитые функции обеспечения безопасности, включая повышение производительности криптографических алгоритмов RNG, SHA512, SHA3.

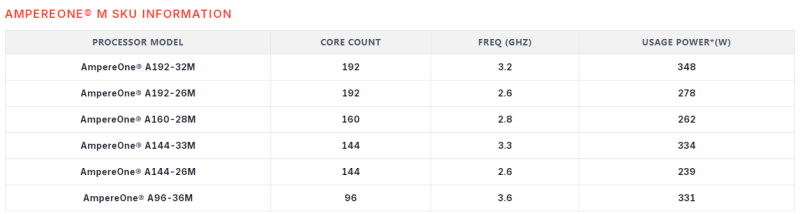

На сегодняшний день в серию AmpereOne M входят шесть моделей с тактовой частотой от 2,6 до 3,6 ГГц. Показатель TDP варьируется от 239 до 348 Вт. Благодаря интеллектуальной сети с высокой пропускной способностью и большому количеству однопоточных вычислительных ядер обеспечивается линейное масштабирование производительности в зависимости от текущей рабочей нагрузки. Возможна динамическая оптимизация мощности.

Процессоры используют 7228-контактный разъём FCLGA. При производстве применяется 5-нм технология TSMC. По заявлениям Ampere, новые CPU подходят для применения в составе систем для серверных стоек высокой плотности. Благодаря этому достигается снижение эксплуатационных расходов по сравнению с ИИ-инфраструктурой на базе GPU.

Источник: