Материалы по тегу: arm

|

14.10.2025 [19:00], Сергей Карасёв

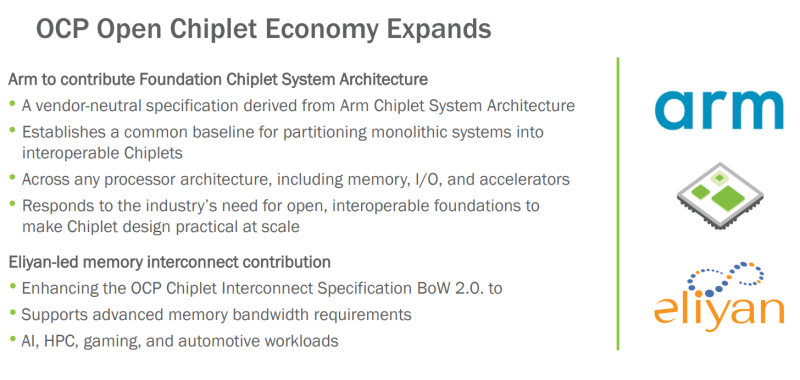

OCP поможет в унификации чиплетов с применением открытых стандартов: Arm и Eliyan поделились наработкамиНекоммерческая организация Open Compute Project Foundation (OCP) сообщила о расширении так называемой «открытой чиплетной экономики» (Open Chiplet Economy). Свои наработки в данной сфере сообществу передали компании Arm и Eliyan. Open Chiplet Economy — это инициатива OCP Server Project Group. Она позволяет разработчикам чиплетов посредством открытого рынка взаимодействовать с производителями продукции. Речь идет о формировании унифицированной экосистемы, за поддержание которой в актуальном состоянии отвечает OCP. В рамках проекта компания Arm передала организации OCP и её участникам архитектуру FCSA (Foundation Chiplet System Architecture), основанную на CSA (Chiplet System Architecture). Она определяет общие базовые стандарты для разделения монолитных систем на чиплеты, которые затем могут использоваться в составе различных изделий, включая память, устройства ввода-вывода и ускорители. Такой подход, как ожидается, упростит создание новых продуктов благодаря повторному использованию уже разработанных блоков. Кроме того, повысится гибкость за счёт отказа от привязки к проприетарным стандартам чиплетов. В свою очередь, Eliyan предоставит сообществу разработки, которые помогут расширить спецификацию интерконнекта для чиплетов OCP BoW 2.0 (Bunch of Wires). В частности, будут добавлены функции для систем, которым требуется высокая пропускная способность: это могут быть приложения ИИ, НРС, игры, автомобильные платформы и пр. Целевым показателем является поддержка скоростей памяти HBM4 (2 Тбайт/с для чтения или записи) вместе с дополнительным каналом связи для сигналов ECC и управления.

13.10.2025 [11:32], Сергей Карасёв

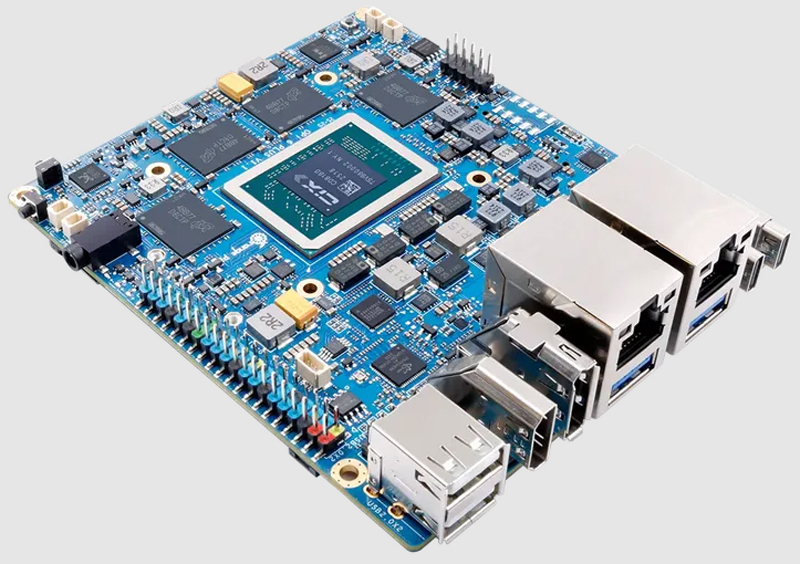

Одноплатный компьютер Orange Pi 6 Plus получил 12-ядерный чип с NPU и 64 Гбайт ОЗУДебютировал одноплатный компьютер Orange Pi 6 Plus, предназначенный для создания различных устройств с ИИ-функциями. Это могут быть системы промышленной автоматизации, компактные рабочие станции, edge-оборудование, домашние серверы и пр. Изделие построено на процессоре Cix CD8180/CD8160 с 12 ядрами в конфигурации 4 × Arm Cortex-A720 с тактовой частотой до 2,8 ГГц, 4 × Arm Cortex-A720 с частотой 2,4 ГГц и 4 × Arm Cortex-A520 с частотой 1,8 ГГц. В состав чипа входят графический ускоритель Arm Immortalis-G720 MC10 и нейропроцессорный блок (NPU). Суммарная заявленная ИИ-производительность достигает 45 TOPS.

Источник изображения: Orange Pi Одноплатный компьютер может нести на борту 16, 32 или 64 Гбайт оперативной памяти LPDDR5-5500. Есть два коннектора M.2 2280 M-Key для SSD с интерфейсом PCIe (NVMe), слот для карты microSD, а также разъём M.2 2230 E-Key для адаптера Wi-Fi / Bluetooth. Предусмотрены два сетевых порта 5GbE. В оснащение новинки входят по два порта USB 3.0 Type-C, USB 3.0 Type-А и USB 2.0, интерфейсы HDMI 1.4, eDP и DisplayPort 1.4 (говорится о возможности вывода изображения в формате 4К со скоростью 120 к/с), два гнезда RJ45 для сетевых кабелей, комбинированное аудиогнездо на 3,5 мм. Имеются два интерфейса камеры MIPI CSI (4 линии) и 40-контактная колодка GPIO (UART, I2C, SPI, PWM). Питание подаётся через коннектор USB Type-C (в комплект входит адаптер мощностью 100 Вт). К плате может быть подключён вентилятор охлаждения с ШИМ-управлением. Габариты составляют 115 × 100 мм, масса — 132 г. Заявлена совместимость с Debian, Ubuntu, Android, Windows, ROS2 (Robot Operating System 2).

04.10.2025 [12:56], Сергей Карасёв

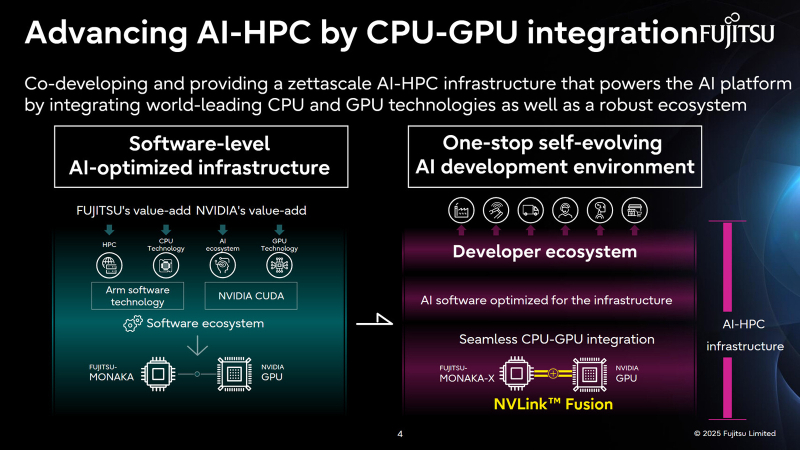

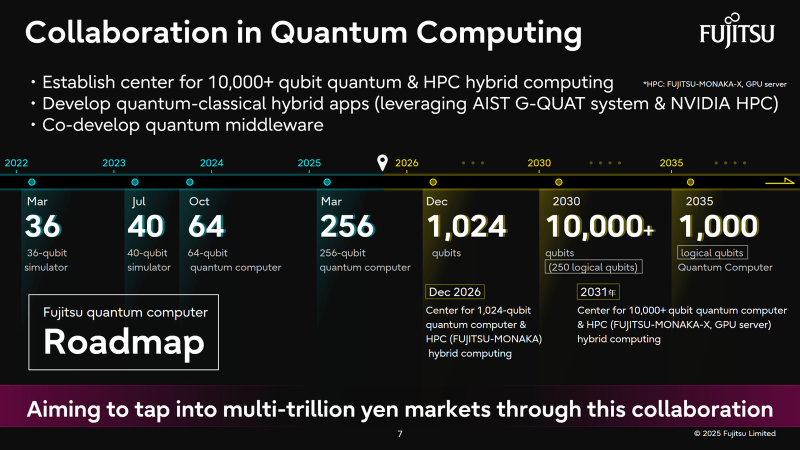

Fujitsu и NVIDIA создадут вычислительную ИИ-инфраструктуру нового поколенияЯпонская корпорация Fujitsu объявила о расширении стратегического сотрудничества с NVIDIA с целью создания полнофункциональной инфраструктуры ИИ следующего поколения, в состав которой войдут ИИ-агенты. Предполагается, что инициатива поможет ускорить развитие таких отраслей, как здравоохранение, производство, робототехника и др. Партнёры намерены работать по ряду направлений. В частности, Fujitsu и NVIDIA займутся созданием передовой вычислительной инфраструктуры для задач ИИ. Речь идёт об объединении серверных процессоров Fujitsu Monaka на архитектуре Arm с высокопроизводительными GPU разработки NVIDIA. Для этого будет задействована технология NVLink Fusion, позволяющая применять скоростные интерконнекты NVLink со сторонними чипами. Конечной целью является предоставление комплексной экосистемы HPC-ИИ с интегрированным софтом Fujitsu для Arm-процессоров и NVIDIA CUDA. Кроме того, сотрудничество предусматривает создание «саморазвивающейся» платформы ИИ-агентов. Она, как ожидается, обеспечит высокую производительность и безопасность. Планируется внедрение механизма, который позволит агентам и моделям ИИ развиваться автономно с возможностью оптимизации под запросы конкретных отраслей. В конечном итоге, такие агенты будут предоставляться заказчикам в виде микросервисов NVIDIA NIM. Ещё одним направлением сотрудничества названо формирование партнёрской экосистемы для расширения использования агентов и моделей ИИ. Планируется также разработка передовых квантовых технологий, включая гибридные квантово-классические вычислительные системы на основе чипов Monaka и НРС-решений NVIDIA. В целом, как отмечается, к 2030 году спрос на вычислительные мощности для ИИ в Японии вырастет в 320 раз по сравнению с 2020-м. На этом фоне местные компании, включая Fujitsu, SoftBank и KDDI, активно реализуют различные проекты, направленные на развитие рынка ИИ.

03.10.2025 [11:46], Владимир Мироненко

CPU двойного назначения: SiPearl анонсировала 80-ядерный Arm-процессор Athena1Французский разработчик серверных Arm-процессоров SiPearl, не имеющий собственных производственных мощностей, объявил о выпуске процессора Athena1 для приложений двойного назначения. Как сообщается в пресс-релизе, созданный на основе опыта, полученного при разработке процессора Rhea1, который будут использоваться в первом европейском экзафлопсном суперкомпьютере JUPITER, новый чип будет предлагать функции, специально разработанные для рабочих нагрузок государственных, оборонных и аэрокосмических приложений, включая такие направления, как защищенная связь и разведка, криптография и шифрование, обработка разведывательных данных, тактические сети, электронное обнаружение и локальная обработка данных на транспортных средствах. В дополнение к вычислительной мощности, Athena1 будет отличаться безопасностью и целостностью данных. Семейство Athena1 будет предлагаться в вариантах с 16, 32, 48, 64 или 80 ядрами Arm Neoverse V1 (Zeus), в зависимости от требуемой мощности для каждого приложения, ограничений по нагреву и других факторов. Подробные технические характеристики будут раскрыты позже. Производством кристаллов Athena1 займётся TSMC. Предполагается, что первоначально упаковка будет осуществляться на Тайване с последующим переносом в Европу, чтобы способствовать развитию европейской промышленной экосистемы. Коммерческий выпуск Athena1 запланирован на II половину 2027 года. Филипп Ноттон (Philippe Notton), генеральный директор и основатель SiPearl отметил, что при разработке новой версии первого процессора компании, «идеально отвечающей требованиям двойного назначения», был использован опыт, накопленный её научно-исследовательскими и опытно-конструкторскими группами в области высокопроизводительных вычислений. «В рамках программы, порученной нам Европой по содействию возвращению высокопроизводительных процессорных технологий на континент, Athena1 является идеальным дополнением к Rhea1, помогая утвердить стратегическую независимость Европы», — подчеркнул Ноттон.

03.10.2025 [08:58], Сергей Карасёв

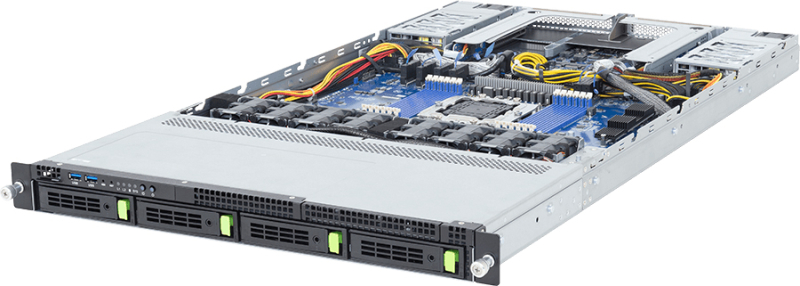

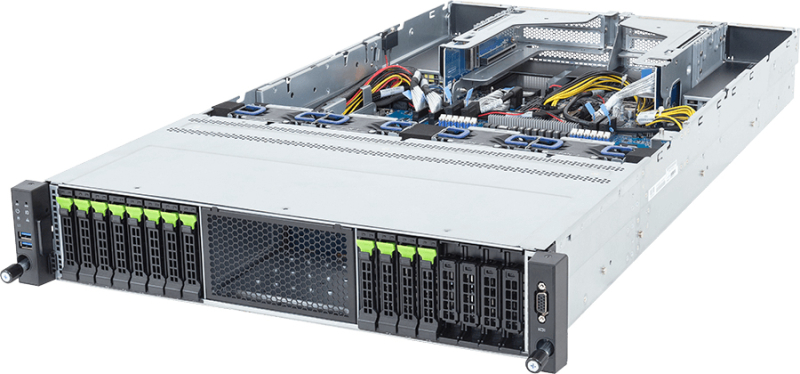

Giga Computing представила серверы с Arm-чипами AmpereOne M для ИИ-инференсаКомпания Giga Computing, подразделение Gigabyte, анонсировала серверы R1A3-T40 и R2A3-T40, построенные на процессорах AmpereOne M, которые спроектированы специально для поддержания ресурсоёмких ИИ-нагрузок в дата-центрах. Представленные системы подходят для инференса, облачных приложений и пр. Модель R1A3-T40 выполнена в форм-факторе 1U, устройство R2A3-T40 — в корпусе 2U. В обоих случаях допускается установка одного чипа AmpereOne M, который может содержать до 192 кастомизированных 64-бит ядер на базе Arm v8.6+. Показатель TDP — до 425 Вт. Есть 12 слотов для модулей оперативной памяти DDR5-5600. Младшая версия располагает четырьмя фронтальными отсеками для накопителей LFF/SFF с интерфейсом SATA/SAS-4 или PCIe 5.0 (NVMe). Доступны два слота PCIe 5.0 x16 для карт расширения типоразмера FHHL и два разъёма OCP NIC 3.0 PCIe 5.0 x16. Сервер 2U, в свою очередь, оснащён 12 посадочными местами для SFF-накопителей (SATA/SAS-4 или PCIe 5.0), одним слотом PCIe 5.0 x16 и одним разъёмом OCP NIC 3.0 PCIe 5.0 x16. Новинки несут на борту контроллер ASPEED AST2600 и сетевой адаптер Intel I210-AT стандарта 1GbE. Есть выделенный сетевой порт управления 1GbE, а также коннектор M.2 для SSD формата 2242/2260/2280/22110 с интерфейсом PCIe 5.0 x4. Питание обеспечивают два блока мощностью 1600 Вт с сертификатом 80 PLUS Titanium. Предусмотрены три порта USB 3.2 Gen1 Type-A (два располагаются на лицевой панели), порт Micro-USB, интерфейс Mini-DP, гнёзда RJ45 для сетевых кабелей и аналоговый разъём D-Sub (только у модели R2A3-T40). Применена система воздушного охлаждения. Диапазон рабочих температур — от +10 до +35 °C.

24.09.2025 [11:25], Сергей Карасёв

Luckfox представила PicoKVM — миниатюрный IP-KVM с сенсорным дисплеем и ИИ-блокомКомпания Luckfox, по сообщению ресурса CNX Software, начала приём заказов на устройство PicoKVM, предназначенное для удалённого управления персональными компьютерами, рабочими станциями и серверами. Новинка выполнена на аппаратной платформе Rockchip с прошивкой Buildroot (Linux 5.10.160 и U-Boot). Решение заключено в миниатюрный корпус с размерами 48,5 × 48,5 × 29 мм. В верхней части располагается небольшой информационный дисплей с диагональю 1,54″ и разрешением 240 × 240 пикселей; реализовано сенсорное управление. PicoKVM также предлагается в виде платы (44 × 42 × 23,6 мм) без корпуса и экрана.

Источник изображений: CNX Software Основой служит процессор Rockchip RV1106G3, который содержит ядра Arm Cortex-A7 (1,2 ГГц) и RISC-V. В состав изделия входит NPU-модуль с производительностью до 1 TOPS для ускорения операций, связанных с ИИ. Встроенный блок VPU способен декодировать видеоматериалы в форматах H.265/H.264 с разрешением 3072 × 1728 точек и скоростью 30 к/с. Объём оперативной памяти DDR3L составляет 256 Мбайт. В оснащение входит флеш-чип eMMC вместимостью 8 Гбайт с возможностью расширения при помощи карты microSD.  Устройство наделено сетевым портом 10/100MbE с разъёмом RJ45, интерфейсом HDMI, а также портом USB Type-C для подачи питания, программирования и эмулирования клавиатуры/мыши/USB-накопителей. Предусмотрен дополнительный I/O-разъём с поддержкой GPIO, UART, I2C и пр. Отмечается, что основная часть программного обеспечения PicoKVM (прошивка, SDK и т. д.) имеет открытый исходный код, но некоторые драйверы и медиабиблиотеки являются проприетарными. Стоимость PicoKVM составляет около $60 с корпусом и сенсорным дисплеем, тогда как модификацию в виде платы можно приобрести за $35.

22.09.2025 [12:25], Сергей Карасёв

Вышел GL.iNet Comet PoE — компактный IP-KVM с поддержкой PoE и возможностью монтажа в стойкуКомпания GL.iNet представила устройство Comet PoE (GL-RM1PE) — это решение для удалённого управления IP-KVM (Keyboard, Video, Mouse), выполненное в компактном корпусе. Новинка может применяться в «настольном» режиме, а также монтироваться в серверную стойку. По сути, Comet PoE — это улучшенная версия модели Comet (GL-RM1), которая вышла в марте нынешнего года. Как и оригинальная модификация, новинка поддерживает работу с физическим переключателем Fingerbot, который позволяет удалённо нажимать на кнопки, например, на кнопку включения питания на компьютерном корпусе. По сравнению с прародителем вариант Comet PoE получил ряд технических улучшений. В частности, вместо процессора с четырьмя ядрами Arm Cortex-A7 (1,5 ГГц) задействован четырёхъядерный чип Cortex-A53 (это может быть Rockchip RV1126B). Объём оперативной памяти DDR3L, как и прежде, составляет 1 Гбайт, тогда как вместимость флеш-модуля eMMC увеличилась с 8 до 32 Гбайт. Кроме того, реализована поддержка PoE. Устройство оборудовано интерфейсом HDMI с возможностью работы с видео 2K (2160 × 1440@60), сетевым контроллером 1GbE с разъёмом RJ45, портом USB 2.0 Type-A для подключения периферии, такой как Fingerbot, коннектором USB 2.0 Type-C для эмуляции клавиатуры/мыши. Питание (5 В / 2 A) может подаваться через дополнительный разъём USB Type-C. Габариты составляют 102 × 70 × 22 мм, вес — 140 г. Новинку можно заказать по ориентировочной цене $110. Компания GL.iNet предоставляет необходимые файлы для создания методом 3D-печати корпуса, предназначенного для монтажа Comet PoE в 10″ стойку. В комплект поставки входят кабели USB 2.0 Type-A — Type-C, USB 2.0 Type-C — Type-C, Ethernet и HDMI.

20.09.2025 [12:58], Сергей Карасёв

Ubiquiti представила настольные и стоечные NAS с поддержкой до восьми LFF-накопителейКомпания Ubiquiti анонсировала новые сетевые хранилища UniFi — устройства UNAS 2 и UNAS 4 в «настольном» форм-факторе, а также UNAS Pro 4 и UNAS Pro 8, которые предназначены для монтажа в стойку. Новинки рассчитаны на использование в сферах малого и среднего бизнеса, а также в составе корпоративных систем. Модель UNAS 2 несёт на борту процессор с четырьмя ядрами Arm Cortex-A55 с частотой 1,7 ГГц и 4 Гбайт памяти LPDDR4. Предусмотрены два отсека для LFF-накопителей с интерфейсом SATA-3; возможна организация массивов RAID 0/1. Есть один сетевой порт 2.5GbE на основе разъёма RJ45 с поддержкой PoE++ (в комплект входит адаптер на 60 Вт). В оснащение включены контроллер Bluetooth 4.1, информационный дисплей размером 1,47″ и порт USB Type-C. Габариты составляют 135 × 129 × 223,7 мм, масса — 1,3 кг (без установленных HDD). Ступенью выше располагается решение UNAS 4. Оно имеет аналогичные технические характеристики, но допускает установку четырёх LFF/SFF-накопителей, а также двух SSD формата M.2 (NVMe). Этот NAS имеет размеры 246 × 129 × 224,5 мм и весит 2,6 кг. В комплект поставки включён адаптер питания PoE+++ мощностью 90 Вт. Стоечное хранилище UNAS Pro 4 формата 1U располагает четырёхъядерным чипом Arm Cortex-A57 с частотой 2 ГГц и 8 Гбайт ОЗУ. Могут быть задействованы четыре накопителя LFF/SFF (HDD или SSD), а также два NVMe SSD стандарта M.2. Предусмотрены два сетевых порта 10G SFP+ и один порт 1GbE RJ45, а также контроллер Bluetooth 4.1. Габариты — 442,4 × 400 × 43,7 мм, масса — 6,7 кг. Старшая версия, UNAS Pro 8, получила процессор с четырьмя ядрами Arm Cortex-A57 с частотой 2 ГГц и 16 Гбайт RAM. Это 2U-хранилище рассчитано на восемь LFF/SFF-накопителей (HDD или SSD) и два М.2 NVMe SSD. Есть два порта 10G SFP+, один порт 10GbE RJ45, адаптер Bluetooth 4.1. Размеры составляют 442,4 × 480 × 87,4 мм при массе 11,5 кг. Все NAS могут эксплуатироваться при температурах от -5 до +40 °C.

12.09.2025 [23:30], Владимир Мироненко

Благодаря NVIDIA доля Arm на рынке серверных процессоров достигла 25 %Стремительный рост вычислительных мощностей ЦОД на фоне бума ИИ-технологий способствовал росту доходов не только производителей ускорителей и серверных CPU, но и компании Arm, чью архитектуру они используют в своих чипах, передаёт The Register. В январе Arm заявила о намерении занять 50 % рынка чипов для ЦОД к концу 2025 года Согласно исследованию Dell’Oro Group, во II квартале доля Arm-чипов на рынке серверных CPU составила 25 %, тогда как годом ранее она равнялась 15 %. Движущей силой роста стало внедрение суперускорителей NVIDIA GB200 NVL72 и GB300 NVL72, которые включают 36 Arm-процессоров Grace на базе архитектуры Neoverse V2 (Demeter) с интерфейсом NVLink-C2C. Заказы на поставку чипов NVIDIA расписаны на месяцы вперёд, что обеспечивает гарантированный источник доходов Arm наряду с ростом доли на рынке. Аналитик Dell’Oro Барон Фунг (Baron Fung) сообщил The Register, что ещё год назад рост Arm на рынке серверных процессоров обеспечивался практически исключительно за счёт кастомных CPU, таких как AWS Graviton. Но теперь выручка от продаж Grace сопоставима с доходами от облачных GPU. AWS использует кастомные процессоры на архитектуре Arm с 2018 года. А Microsoft и Google лишь в последние несколько лет начали всерьёз развивать свои Arm-процессорах Cobalt и Axion соответственно, отметил The Register. Рост доли Arm на рынке зависит от того, насколько больше разработчиков чипов выведет свои чипы на рынок серверных процессоров. NVIDIA сейчас работает над новым процессором на базе Arm с использованием кастомных ядер Vera. Qualcomm и Fujitsu также работают над серверными чипами. А появление NVIDIA NVLink Fusion может привести к созданию новых гибридных чипов. По данным Dell’Oro, рост рынка ИИ-технологий также привёл к росту рынка компонентов для серверов и СХД, составившему во II квартале 44 % в годовом исчислении. Продажи SmartNIC и DPU, которые зачастую тоже используют Arm-ядра, примерно удвоились по сравнению с прошлым годом на фоне перехода на Ethernet для вычислительных ИИ-кластеров. Поставки ASIC для обработки ИИ-нагрузок сейчас сопоставимы с объёмами поставок GPU, хотя GPU по-прежнему приносят большую часть доходов.

11.09.2025 [18:04], Сергей Карасёв

В облаке Astra Cloud появились выделенные серверы с процессорами Baikal-SОблачный провайдер «Астра Облако» (Astra Cloud), входящий в «Группу Астра», и российский производитель микроэлектроники «Байкал Электроникс» объявили о запуске сервиса аренды выделенных серверов, оснащённых отечественными процессорами Baikal-S. Предложение ориентировано в том числе на объекты критической информационной инфраструктуры (КИИ). Чипы Baikal-S (BE-S1000) содержат 48 ядер Arm Cortex-A75, поддерживают память DDR4-3200 МГц (6 каналов, до 128 Гбайт на канал), имеют 80 линий PCIe 4.0 и два интерфейса 1GbE. Заявленное энергопотребление находится на уровне 120 Вт. Серверы расположены в московском дата-центре с надёжностью Tier IV, что гарантирует максимальную отказоустойчивость инфраструктуры. На таких объектах дублируются и основные, и дополнительные системы, а показатель доступности достигает 99,995 %. Время простоя не превышает 26 минут в год. Сервис аренды серверов на базе Baikal-S ориентирован на заказчиков, которым необходимо отладить и адаптировать своё ПО под отечественную архитектуру. Помимо предприятий КИИ, это могут быть государственные организации, корпоративные заказчики и пр. Благодаря арендной модели аппаратные ресурсы полностью закрепляются за клиентом. Это, как утверждается, обеспечивает предсказуемую производительность приложений и высокий уровень защиты данных. Среди других преимуществ нового сервиса названы возможность формирования частных облаков и отказоустойчивых кластеров, гибкость в настройке систем под индивидуальные потребности, отсутствие капитальных затрат на покупку и обслуживание оборудования, технологическая независимость от зарубежных платформ. «Запуск аренды выделенных серверов на процессорах Baikal-S — это важный шаг в развитии отечественной IT-сферы. Мы даём бизнесу и государственным структурам доступ к надёжной, предсказуемой и безопасной платформе для построения частных облаков и работы с критичными нагрузками», — говорит технический директор «Группы Астра». |

|