Материалы по тегу: ускоритель

|

06.06.2024 [13:23], Руслан Авдеев

Маск подтвердил передачу ИИ-стартапу xAI 12 тыс. ускорителей H100, предназначавшихся TeslaГлава Tesla и других компаний Илон Маск (Elon Musk) подтвердил передачу ускорителей NVIDIA H100, ранее заказанных Tesla, социальной сети X и ИИ-стартапу xAI. Слухи об этом, напоминает The Register, появились в СМИ — в распоряжение журналистов попала внутренняя документация и электронная переписка с NVIDIA. В частности, в одной из записок за декабрь прошлого года прямо указывалось, что Илон отдаёт приоритет внедрению 12 тыс. ускорителей в X вместо Tesla. Общая стоимость такого количества H100 превышает $500 млн. Вместо этого заказанные для X экземпляры H100 позже будут переданы Tesla (поставки ожидались в январе и июне 2024 года). Кроме того, есть проблемы и с созданием ИИ-суперкомпьютера Dojo на базе собственных чипов, который должен улучшить положение Tesla. Приоритетным для Маска, вероятно, является кластер H100, создаваемый X и тесно связанным с сетью стартапом xAI. Компании совместно работают над большими языковыми моделями, стоящими за чат-ботом Grok, уже доступным премиум-подписчикам X. По данным утечки из NVIDIA, 100 тыс. H100 приказано передать к концу года в xAI для создания «крупнейшего в мире» кластера ускорителей, который разместится в Северной Дакоте.

Источник изображения: Alexander Shatov/unsplash.com Хотя на уровне компаний комментариев не поступало, сам Маск подтвердил, что у Tesla просто не было места для чипов NVIDIA, поэтому они хранились на складе. При этом ещё не так давно Маск уверял инвесторов Tesla, как важны HPC-системы и ИИ для компании. Более того, ещё в апреле появилась новость о том, что автопроизводитель только в течение одного квартала вложил в ИИ $1 млрд. Также миллиардер сообщал, что один из заводов Tesla в Техасе вместит 50 тыс. H100 для обучения систем автономного вождения, в общей сложности число ускорителей достигло бы 85 тыс. Пока нет точных данных об обстоятельствах передачи ускорителей между Tesla и X или xAI. Нет даже информации о том, заплатила ли уже Tesla за «железо» и получила ли за него какую-то компенсацию. Условия передачи H100 могут иметь большое значение с учётом того, что Маск не является единоличным владельцем Tesla. Если выяснится, что Маск злоупотребил властью, к нему могут возникнуть вопросы как у инвесторов, так и у регуляторов. Впрочем, Tesla не впервые приходится делиться активами с X. Вскоре после покупки Twitter более 50 сотрудников автопроизводителя якобы отправили на «усиление» социальной соцсети. Есть данные, что сотрудников Tesla привлекают к работам и в других компаниях Маска, причём без дополнительной платы. Время для новостей не особенно удачное — на следующей неделе акционеры Tesla будут голосовать по ряду предложений, главным из которых является официальный перенос штаб-квартиры в Техас. Также речь пойдёт о переизбрании брата Кимбала, брата Илона Маска (Kimbal Musk), в совет директоров и других ключевых для бизнесмена вопросах. Тем временем в Tesla падают продажи со II половины 2022 года, увольняют сотрудников и, главное, стоимость акций компании падает критическими темпами. Приказ передать H100 станет дополнительным козырем в руках критиков миллиардера, которые утверждают, что его активное участие в других проектах мешает ему сконцентрироваться на автобизнесе и эффективно выполнять обязанности главы Tesla.

05.06.2024 [14:07], Руслан Авдеев

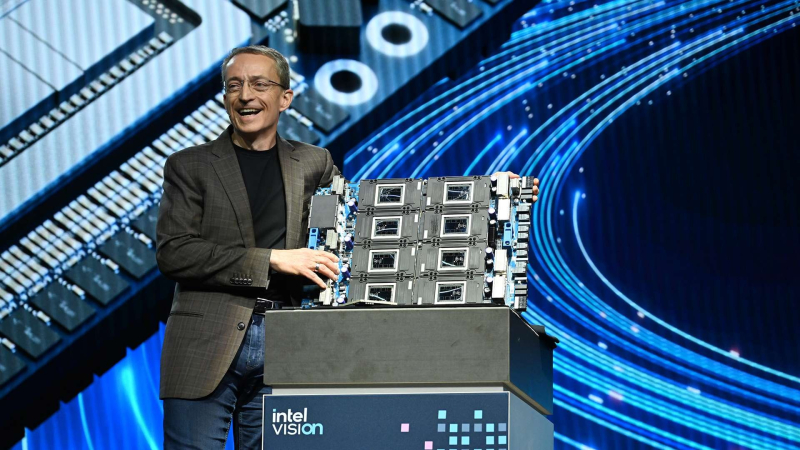

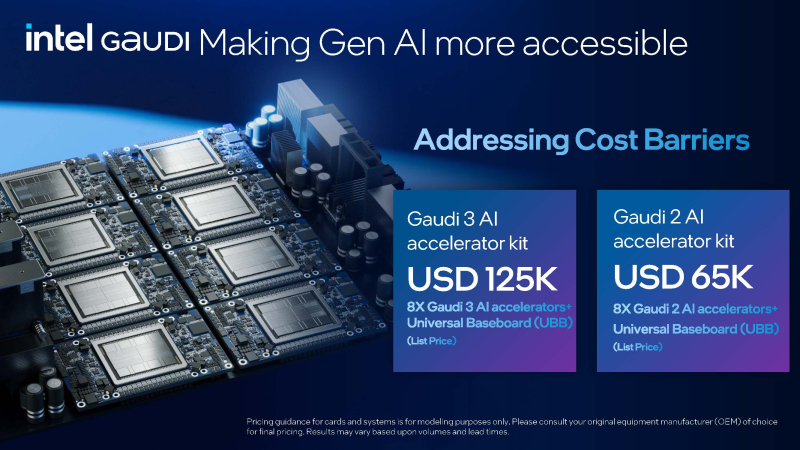

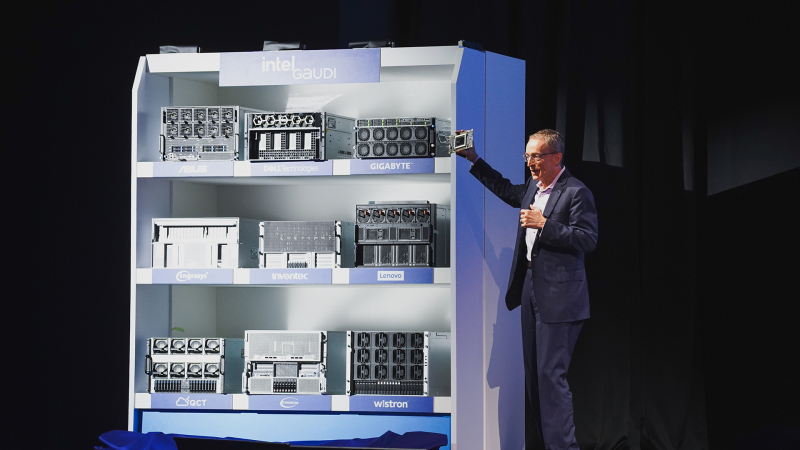

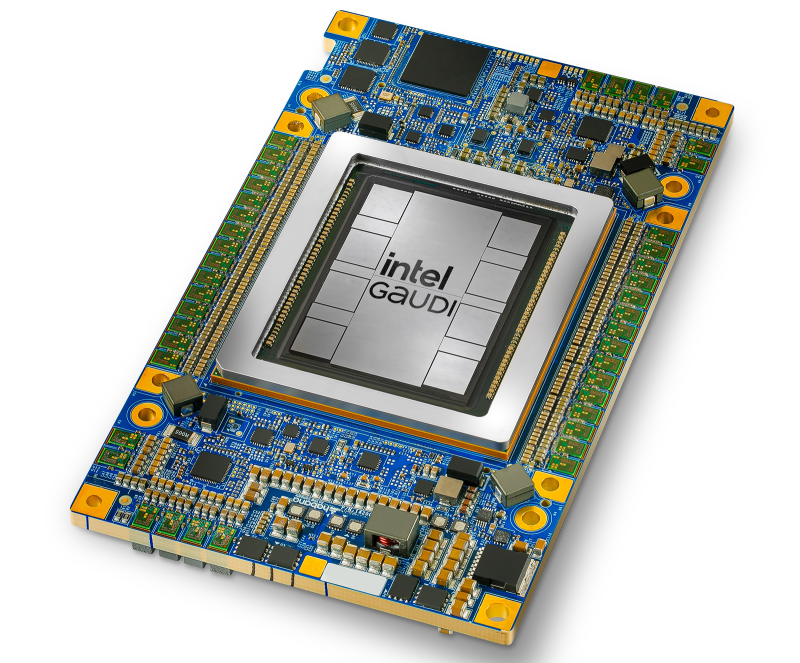

Против всех правил: Intel публично раскрыла стоимость ИИ-ускорителей GaudiХотя производители легко раскрывают рекомендованные цены на классические процессоры, в случае с ИИ-ускорителями ситуация обстоит иначе. Как сообщает портал CRN, Intel публично объявила стоимость новейшей платформы Gaudi3. Фактически компания нарушила негласно принятые в отрасли нормы секретности, сообщив в ходе выставки Computex, что UBB-плата с восемью OAM-модулями Gaudi3 будет стоить $125 тыс. для производителей серверов, намеренных поддержать платформу в момент выпуска в III квартале 2024 года. Intel раскрыла цены после того, как конкуренты в лице NVIDIA и AMD пообещали представлять всё более мощные чипы ежегодно — это станет серьёзной угрозой как для Intel, так и для менее крупных игроков. По оценкам Intel, $125 тыс. — это всего ⅔ стоимости платформы NVIDIA с восемью ускорителями H100, лежащих в основе системы NVIDIA DGX и серверов стороннего производства. Хотя в самой NVIDIA цены своих ускорителей или платформ не раскрывают, если верить расчётам Intel, платформа HGX H100 обходится приблизительно в $187 тыс. Цена может меняться в зависимости от объёмов закупок и конфигурации серверов. При этом ускорители Blackwell B200 будут стоить уже $30-$40 тыс./шт. В Intel утверждают, что по соотношению цена/производительность чипы Gaudi3 в сравнении с H100 в 2,3 раза эффективнее при инференсе и на 90 % — при обучении. UBB-плата с восемью ускорителями Gaudi2 стоит всего $65 тыс., это приблизительно треть от стоимости платформы NVIDIA HGX H100. При этом в публичных бенчмарках MLPerf только Gaudi2 смогли составить конкуренцию H100 как в обучении, так и в инференсе. Цены на отдельные чипы Gaudi 3 пока не называются. Есть и ещё один важный момент — ускорители Gaudi используют встроенные Ethernet-контроллеры как для связи между собой, так и для общения с внешним миром, тогда как решениям NVIDIA требуется отдельный адаптер InfiniBand/Ethernet на каждый ускоритель, что увеличивает итоговую стоимость платформы. В Intel уверены, что клиенты всё больше уделяют внимания показателю токен/$, на который большое влияние оказывает стоимость инфраструктуры. В компании пояснили, что раскрытие цен на Gaudi2 и Gaudi3 поможет клиентам более эффективно планировать инвестиции в ИИ-проекты. Например, стартапы часто не имеют точных сведений об экосистеме, ценах и процессе закупок, так что теперь им будет легче рассчитать, чего можно ожидать от предлагаемого оборудования. Открытость Intel нашла поддержку у крупных производителей IT-оборудования.

05.06.2024 [12:15], Сергей Карасёв

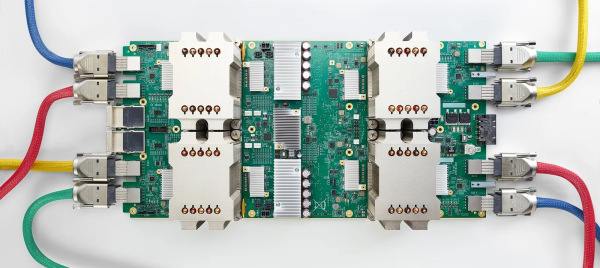

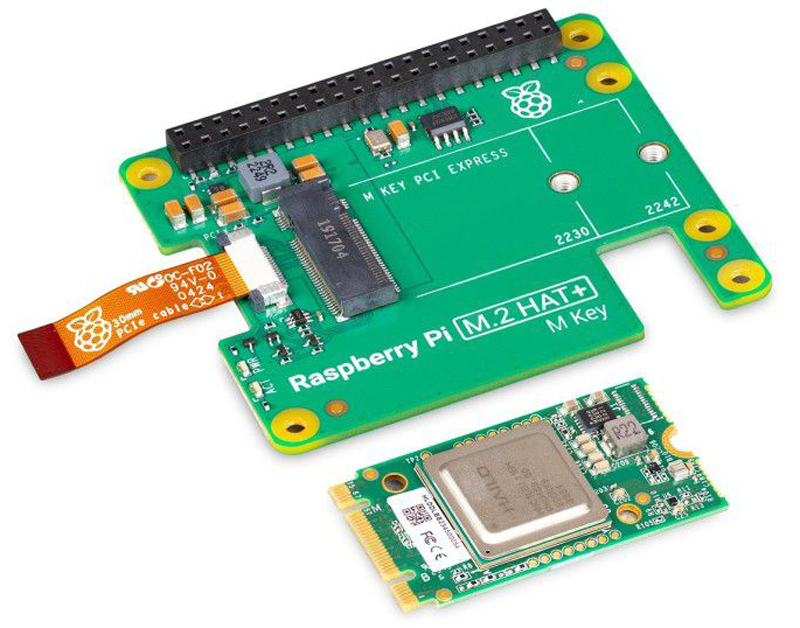

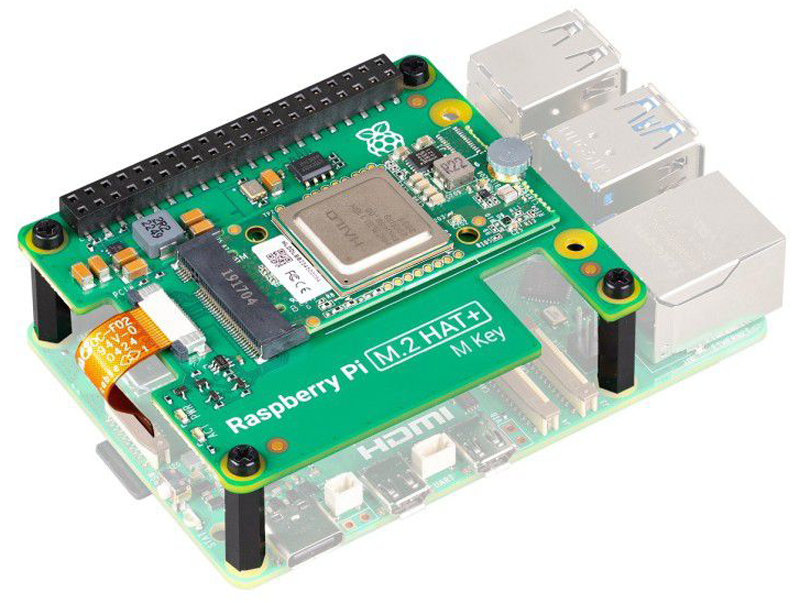

Комплект Raspberry Pi AI Kit с ИИ-ускорителем Hailo расширит возможности Raspberry Pi 5Команда Raspberry Pi анонсировала комплект Raspberry Pi AI Kit, который позволяет наделить ИИ-возможностями одноплатный компьютер Raspberry Pi 5, дебютировавший в сентябре 2023 года. Модуль расширения уже доступен для заказа по ориентировочной цене $70. В основу Raspberry Pi AI Kit положен ИИ-чип Hailo-8L, созданный Hailo Technologies. Это изделие ориентировано на приложения, которым не требуется слишком высокое ИИ-быстродействие. Заявленное быстродействие достигает 13 TOPS, а стандартное энергопотребление составляет 1,5 Вт.

Источник изображений: Raspberry Pi В случае Raspberry Pi AI Kit чип Hailo-8L установлен на модуль типоразмера M.2 2242, который подключается к соответствующему коннектору на плате расширения M.2 HAT+. Эта плата, в свою очередь, обменивается данными с Raspberry Pi 5 посредством интерфейса PCIe 2.0. Габариты M.2 HAT+ составляют 65 × 56,5 × 5,6 мм. Заявленный диапазон рабочих температур простирается от 0 до +50 °C. Новинка может быть смонтирована поверх одноплатного компьютера.  Отмечается, что при использовании обновлённой версии Raspberry Pi OS распознавание чипа Hailo-8L происходит автоматически, после чего ускоритель становится доступен для обработки ИИ-нагрузок. Говорится о полной интеграции с программным стеком Raspberry Pi Camera, что позволяет реализовывать различные приложения на основе машинного зрения.

03.06.2024 [23:50], Алексей Степин

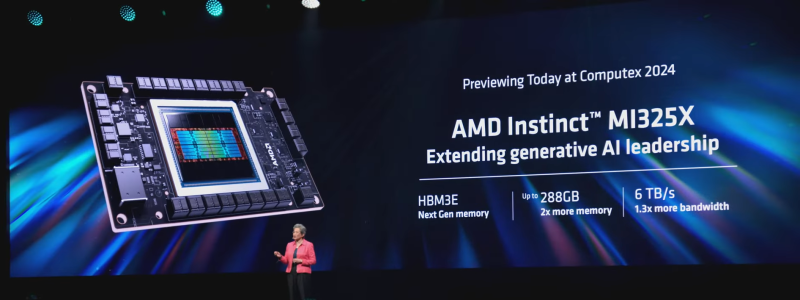

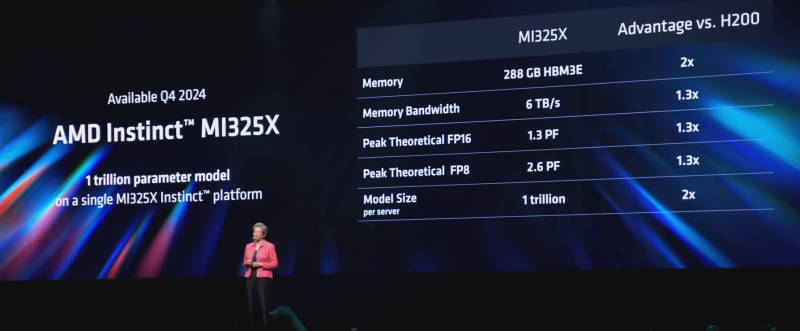

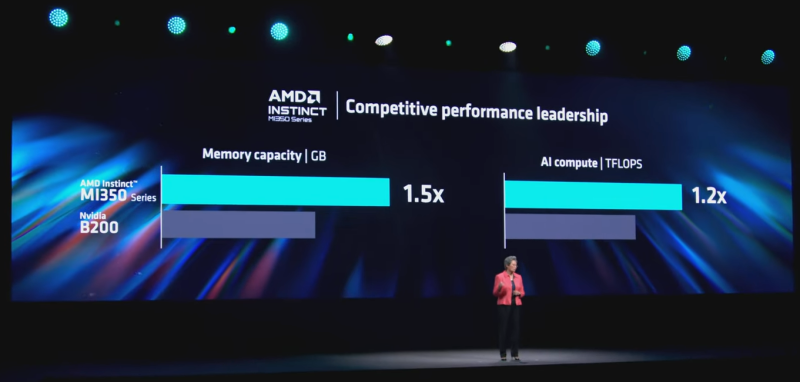

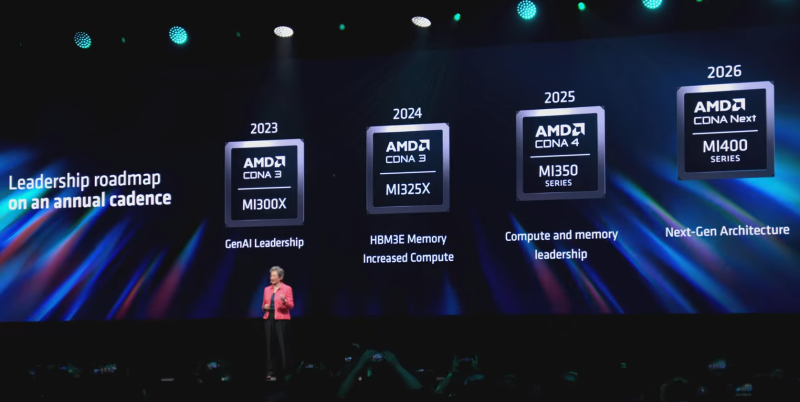

AMD готовит ускорители Instinct MI325X и MI350XВместе с EPYC Turin компания AMD анонсировала и новые ускорители серии Instinct. Так, на смену MI300X компания предложит Instinct MI325X, оснащённый памятью HBM3e. Он должен стать достойным ответом на серию ускорителей NVIDIA Blackwell. Последний также получит память данного типа, тогда как более совершенные NVIDIA Rubin с памятью HBM4 увидят свет лишь в 2026 году. Технически MI325X представляет собой усовершенствованный вариант MI300X. Использование более плотной HBM3e позволило довести объём набортной памяти до 288 Гбайт, что больше, нежели у Blackwell В100 (192 Гбайт) и Hopper H200 (141 Гбайт). Выросла и пропускная способность, с 5,3 до 6 Тбайт/с. В настоящее время тройка главных поставщиков памяти уже готовят HBM3e-сборки 12-Hi ёмкостью до 36 Гбайт. Micron и SK Hynix освоили ПСП 9,2 Гбит/с на контакт, в то время как Samsung планирует достичь 9,8 Гбит/с. Правда, для MI325X эта цифра составит примерно 5,9 Гбит/с на контакт. В остальном конфигурация нового ускорителя осталась прежней в сравнении с MI300X. Под вопросом разве что теплопакет, но вряд ли он так уж значительно превысит уже имеющиеся 750 Вт. AMD Instinct MI325X получит полную совместимость с любой инфраструктурой на базе MI300X, достаточно будет лишь заменить модули OAM. Начало поставок новинки запланировано на IV квартал 2024 года, но, как считают зарубежные обозреватели, AMD придётся конкурировать за поставки памяти с другими разработчиками ускорителей. Вместе с анонсом MI325X компания впервые за два года опубликовала план дальнейшего развития семейства Instinct. Сейчас AMD активно работает над архитектурой CDNA4, которая дебютирует в ускорителях MI350 в 2025 году. Они будут производиться с использованием 3-нм техпроцесса и получат поддержку FP4/FP6. Ожидается повышение как производительности, так и энергоэффективности. Причём AMD намеревается сохранить лидерство по объёму памяти. Следующее поколение архитектуры под условным названием CDNA Next появится лишь в 2026 году в серии Instinct MI400, где AMD ещё более активно задействует чиплетный подход. AMD вслед за NVIDIA переходит к ежегодному выпуску новых ускорителей и к переходу на новую архитектуру каждые два года. Гонка в сфере ИИ ускоряется и взятый темп позволит компании более успешно играть на этом рынке. Работает AMD и над программной составляющей, развивая пакет ROCm, адаптирую и упрощая запуск всё большего количества моделей, сотрудничая с Hugging Face и развивая PyTorch, TensorFlow и JAX.

30.05.2024 [11:05], Сергей Карасёв

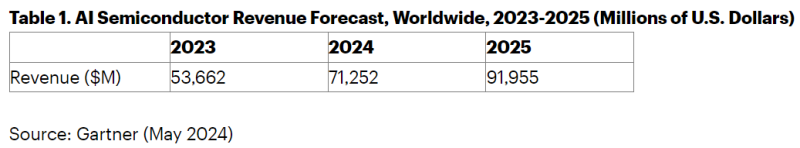

Gartner: объём рынка ИИ-чипов в 2024 году увеличится на третьВ 2023 году, по оценкам Gartner, объём глобального рынка ИИ-чипов достиг приблизительно $53,66 млрд. В дальнейшем ожидается стремительный рост данной отрасли. Так, в 2024-м затраты могут увеличиться на треть — до $71,25 млрд, а в 2025-м достигнут $91,96 млрд. Отмечается, что в 2024 году расходы на ИИ-ускорители для серверов составят приблизительно $21 млрд. К 2028-му, прогнозируют аналитики, затраты в этом сегменте поднимутся до $33 млрд. Gartner подчёркивает, что на сегодняшний день все основные гиперскейлеры, включая AWS, Google, Meta✴ и Microsoft, инвестируют в разработку собственных ИИ-чипов.

Источник изображения: pixabay.com Так, AWS предлагает ИИ-ускорители Trainium2 и Inferentia2. Google выпустила изделия Cloud TPU v5p и v5e и уже готовит TPU v6. Microsoft представила Maia 100, а Meta✴ намерена активно внедрять собственные ИИ-ускорители Artemis. Хотя разработка ИИ-чипов обходится дорого, использование специально созданных решений может повысить эффективность работы ЦОД и снизить затраты на предоставление пользователям услуг на основе ИИ. Gartner прогнозирует, что поставки ПК с возможностями ИИ достигнут 22 % от общего объёма продаж в 2024 году. А к концу 2026-го 100 % новых компьютеров корпоративного класса будут оснащаться нейропроцессорным модулем (NPU) для ускорения ИИ-задач. Ожидается, что в 2024 году выручка от продаж ИИ-чипов для вычислительной электроники составит $33,4 млрд, или 47 % от общего объёма рынка. На ИИ-изделия для автомобильной электроники придётся $7,1 млрд, для бытовой электроники — $1,8 млрд.

25.05.2024 [20:50], Сергей Карасёв

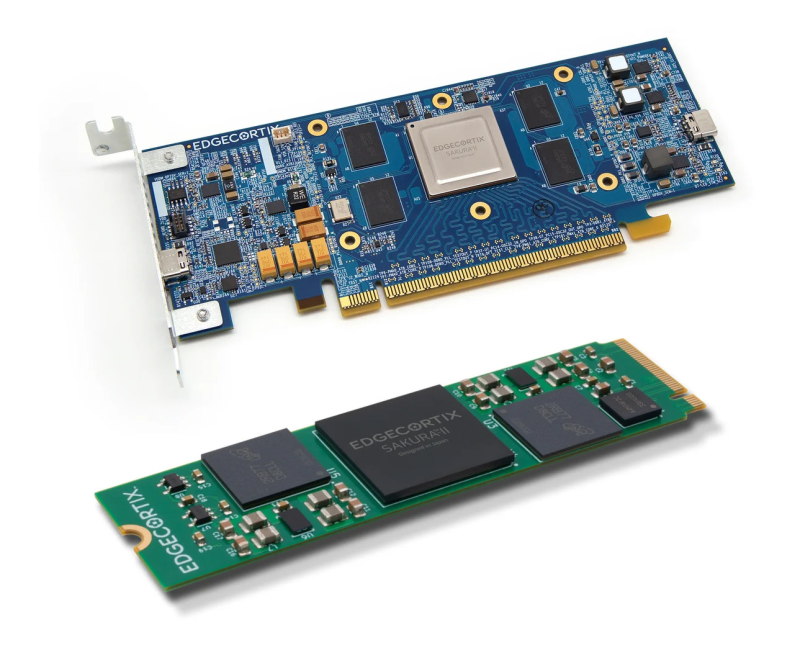

EdgeCortix представила ИИ-ускоритель SAKURA-II Edge AI с производительностью до 60 TOPSКомпания EdgeCortix, по сообщению CNX Software, анонсировала ускоритель SAKURA-II Edge AI, предназначенный для выполнения ИИ-задач на периферии. Новинка, как утверждается, способна справляться с обработкой больших языковых моделей (LLM), больших визуальных моделей (LVM) и пр. В основу изделия положен нейропроцессорный движок с архитектурой Dynamic Neural Accelerator (DNA) второго поколения. Заявленная производительность достигает 60 TOPS на операциях INT8 и 30 Тфлопс на операциях BF16. Ускоритель может нести на борту 8, 16 или 32 Гбайт памяти LPDDR4x с пропускной способностью 68 Гбайт/с. Есть 20 Мбайт памяти SRAM. Заявленное типовое энергопотребление составляет 8 Вт. Изделие имеет упаковку BGA с размерами 19 × 19 мм. Диапазон рабочих температур простирается от -40 до +85 °C. Для ускорителя доступен программный комплект MERA с поддержкой PyTorch, TensorFlow Lite и ONNX. Помимо собственно ускорителя SAKURA-II Edge AI, компания EdgeCortix представила решения на его основе. Это, в частности, модуль формата M.2 2280: он использует интерфейс PCIe Gen 3.0 x4, а энергопотребление равно 10 Вт. Доступны модификации с 8 и 16 Гбайт памяти LPDDR4. Стоят такие модули $249 и $299. Кроме того, выпущены однослотовые низкопрофильные карты расширения с интерфейсом PCIe 3.0 x8. Такие устройства существуют в вариантах с одним и двумя чипами SAKURA-II Edge AI. Во втором случае производительность удваивается и достигает 120 TOPS на операциях INT8 и 60 Тфлопс на операциях BF16. Младшая версия оснащена 16 Гбайт памяти и имеет энергопотребление 10 Вт. Старший вариант несёт на борту 32 Гбайт памяти и обладает энергопотреблением 20 Вт. Цена — $429 и $749 соответственно.

24.05.2024 [15:09], Сергей Карасёв

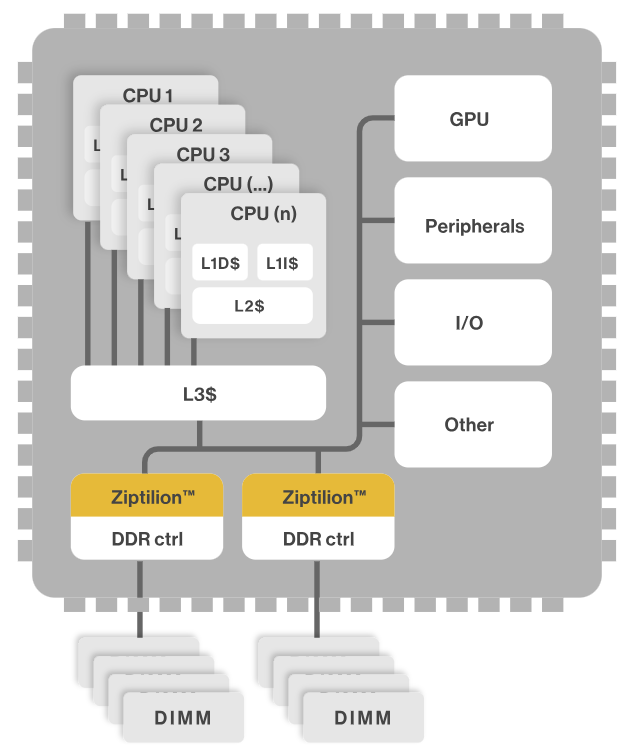

Разработчик «компрессора» для оперативной памяти ZeroPoint получил первые инвестицииСтартап ZeroPoint Technologies AB, разрабатывающий специализированные аппаратные решения для сжатия данных в высокопроизводительных системах, объявил о проведении раунда финансирования Series A, в ходе которого на развития привлечено €5 млн.

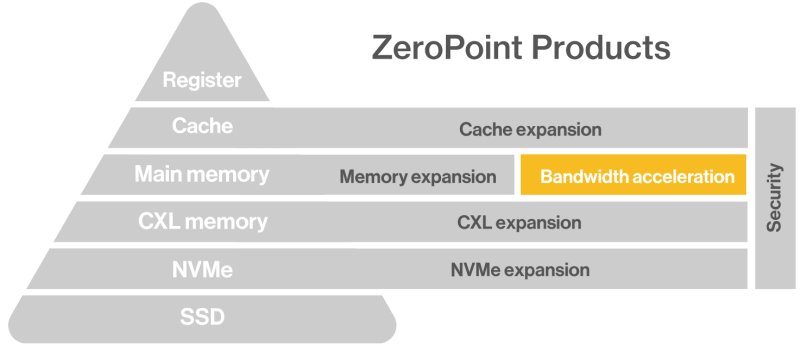

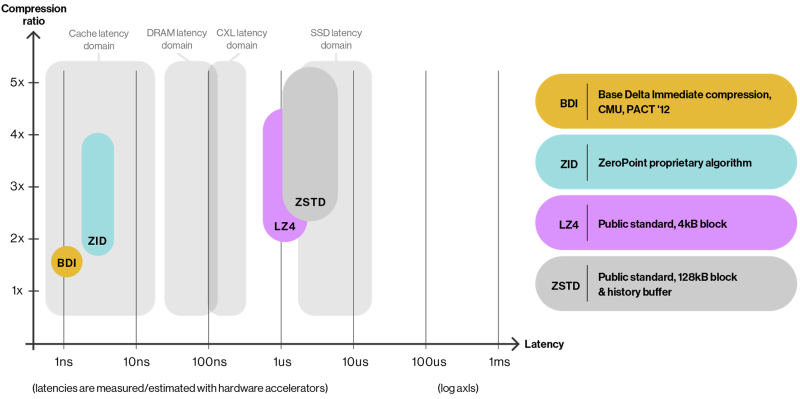

Источник изображений: ZeroPoint ZeroPoint — это дочерняя компания Технического университета Чалмерса (Chalmers University of Technology) в Гётеборге (Швеция). Стартап запущен с целью коммерциализации исследований в области методов сжатия данных, которые его соучредители Пер Стенстрём (Per Stenström) и Ангелос Арелакис (Angelos Arelakis) проводили в вузе. Скорость, с которой серверный процессор может извлекать данные из DRAM, напрямую влияет на его производительность, а значит, и на быстродействие всей системы в целом. При этом, как заявляет ZeroPoint, обычно до 70 % хранимых данных являются избыточными. Одним из способов ускорить процесс получения информации является сжатие. Однако исторически применение этого метода было непрактичным, поскольку даже самые продвинутые алгоритмы компрессии относительно медленны, что сводит на нет любую потенциальную выгоду. ZeroPoint решает проблему с помощью, как утверждается, первого в своём роде подхода с аппаратным ускорением. Технология сочетает в себе сверхбыстрое сжатие данных без потерь и на лету, уплотнение в реальном времени и «прозрачное» управление памятью. Для выполнения этих задач применяется небольшой IP-блок Ziptilion-BW, который может быть интегрирован практически с любым стандартным контроллером памяти и совместим с (LP)DDR4/5 и HBM. ZeroPoint заявляет, что предложенный подход позволят увеличить эффективную ёмкость памяти в 2–4 раза, а также обеспечивает повышение производительности на Ватт до 50 %. Таким образом, общая стоимость владения серверами в дата-центрах может быть снижена на 25 %. Утверждается, что технология ZeroPoint в 1000 раз быстрее, чем другие существующие методы сжатия. ZeroPoint использует проприетарные методы, которые динамически определяют, какие именно данные можно сжать и каким именно образом. Для дополнительного ускорения извлечения данных в устройство интегрирован собственный кеш. Раунд финансирования Series A возглавила мюнхенская компания Matterwave Ventures. Средства также предоставили Industrifonden, Climentum Capital и Chalmers Ventures. Деньги будут использованы для дальнейших разработок и коммерциализации технологии. Компания также предлагает «компрессоры» для L2/L3-кеша и CXL/NVMe-устройств, ускоритель для zram/zswap и блок (де-)шифрования.

22.05.2024 [21:45], Руслан Авдеев

Google обогнала AMD на рынке процессоров для ЦОД и вот-вот догонит Intel

cpu

google

google cloud platform

hardware

techinsights

tpu

анализ рынка

гиперскейлер

ии

облако

ускоритель

цод

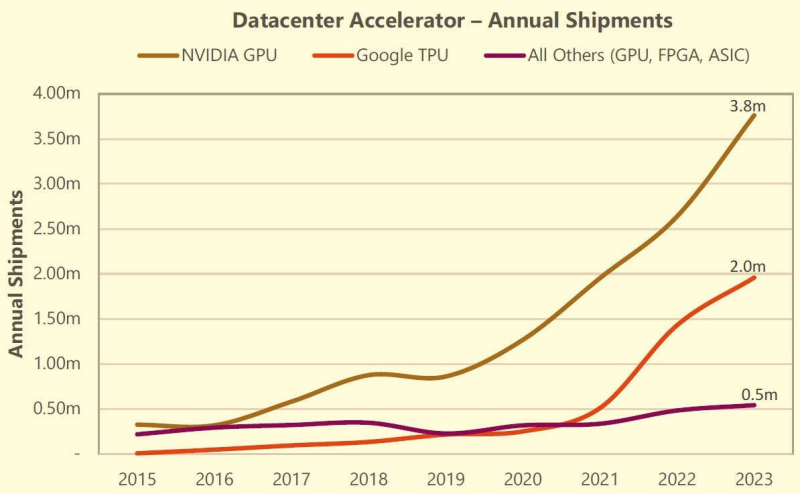

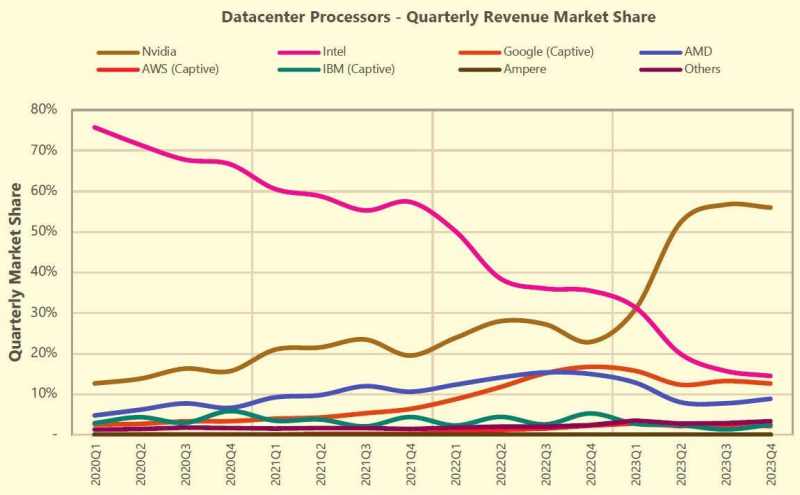

В прошлом месяце компания Google анонсировала долгожданный серверный CPU на архитектуре Arm. Впрочем, как сообщает The Register, она уже оказалась третьей на рынке процессоров для ЦОД (сюда входят не только CPU, но и GPU, TPU и иные ускорители). Согласно отчёту TechInsights, компания теперь уступает только NVIDIA и Intel и давно обогнала AMD. Как и другие крупные облачные операторы, IT-гигант выпускает собственные чипы TPU, шестое поколение которых было представлено на прошлой неделе. Хотя на сторону их не продают, компания заказывает огромные партии TPU для оснащения собственных ЦОД — только в прошлом году речь шла о 2 млн штук. Ключевым партнёром Google в создании кастомного «кремния» является Broadcom. Поставки TPU нарастают с каждым поколением, следуя за ростом самой компании. После премьеры TPU v4 в 2021 году в связи с развитием больших языковых моделей (LLM) объём полупроводникового бизнеса Google значительно вырос. TPU применяются компанией для внутренних задач, а ускорители NVIDIA — для облака. В TechInsights считают, что на сегодняшний день у Google имеется крупнейшая в отрасли база установленных ИИ-ускорителей и самая масштабная ИИ-инфраструктура. В прошлом году на серверным рынке произошла «масштабная коррекция запасов» — гиперскейлеры увеличили срок службы оборудования, отложив замену серверов общего назначения и повысив капитальные затраты на ИИ-серверы и ускорители NVIDIA. Аналитики Omdia говорят о таких тенденциях на рынке что в прошлом, что в начале этого года. В TechInsights считают, что по итогам I квартала 2024 года Google сможет догнать или даже перегнать Intel по доле на этом рынке. Конечно, Google — не единственная облачная компания, разрабатывающая собственные чипы. Microsoft работает над серверным CPU Azure Cobalt и ИИ-ускорителями Maia 100. AWS и вовсе годами использует собственные Arm-процессоры Graviton и ИИ-ускорители серий Trainium и Inferentia. В прошлогоднем докладе Bernstein Research сообщалось, что архитектуру Arm используют уже около 10 % серверов по всему миру, а более 50 % из них внедряется AWS. Softbank в начале 2023 года говорила о том, что Arm захватила 5 % облачного рынка. Впрочем, с появлением процессоров TPU V5e и TPU V5p решения Google будут использоваться всё шире из-за «взрывного роста» больших языковых моделей вроде Gemini. В 2024 году у Google появится Arm-процессор Axion. И его внедрение, по мнению TechInsights, будет происходить намного быстрее, чем Graviton, поскольку у Google уже имеется программная инфраструктура для такого чипа. Всё это необходимо компании, чтобы идти в ногу с AWS, Microsoft и, в меньшей степени, Alibaba. При этом в докладе упоминается, что рынок полупроводников для ЦОД быстро меняется — раньше на нём доминировала Intel с архитектурой x86. Теперь его структура определяется потребностями ИИ-систем.

21.05.2024 [18:48], Алексей Степин

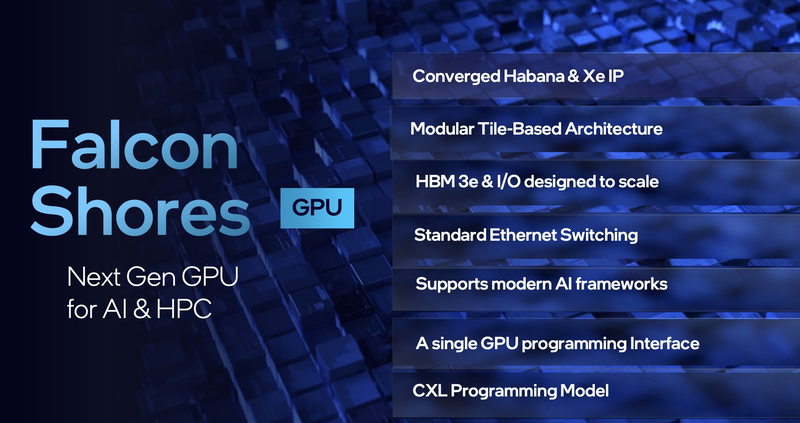

Intel отказалась от Ponte Vecchio в пользу Gaudi и Falcon ShoresУскоритель Intel Ponte Vecchio на базе архитектуры Xe стал настоящим технологическим чудом, объединив 47 чиплетов в своей сложнейшей, многослойной компоновке на базе EMIB и Foveros. Увы, амбициозный ускоритель задержался: анонсирован он был в 2019 году, но его массовое производство было налажено только к 2023 году. Он продолжит трудиться в уже построенных суперкомпьютерах — в свежем TOP500 система Aurora, использующая данные ускорители, добралась до второго места, хотя постройка машины была завершена почти год назад. Однако новых ускорителей на базе этого решения не будет — проект Rialto Bridge свернут, да и жизненный цикл Ponte Vecchio подходит к концу. Эту архитектуру погубил именно замах: Ponte Vecchio был задуман как универсальный ускоритель, способный эффективно работать практически со всеми существующими форматами вычислений, от полновесного FP64 до характерных для ИИ FP16, BF16 и INT8. Но решения NVIDIA и AMD успели уйти вперёд, появились и более узкоспециализированные ИИ-решения. Причём последние появились и у самой Intel: с приобретением активов Habana Labs компания получила перспективную ИИ-архитектуру Gaudi. С точки зрения рыночных перспектив она оказалась куда лучше Ponte Vecchio, уже во втором поколении чипов успешно сражаясь с решениями NVIDIA, особенно в области удельной производительности. И в области ИИ-ускорителей Intel теперь делает ставку именно на Gaudi3.  В Falcon Shores компания намерена совместить несколько подходов. Согласно последним данным, новинка будет включать в себя элементы архитектур Xe и Gaudi, получит модульный дизайн, поддержку современных ИИ-фреймворков и будет использовать масштабируемые интерфейсы ввода-вывода и HBM3e. Выпуск Falcon Shores намечен на 2025 год. Intel намеревается сфокусировать своё внимание на рынке корпоративных ИИ-систем, для чего планируется как можно быстрее расширять рыночную нишу Gaudi. Однако для рынка HPC ведущей связкой пока останется Xeon с ускорителями серии Max.  Следует отметить, что фокус на специфичных для ИИ архитектурах не означает экономичность. Если самый быстрый вариант Ponte Vecchio в лице OAM-ускорителя Data Center GPU Max 1550 имеет TDP 600 Вт, то у Gaudi3 даже с воздушным охлаждением этот показатель вырастет до 900 Вт. Это вынуждает использовать формат OAM 2.0, но для Falcon Shores и он не подойдёт — Intel говорит уже 1500 Вт, что больше, нежели у NVIDIA Blackwell с его 1200 Вт.

16.05.2024 [23:30], Алексей Степин

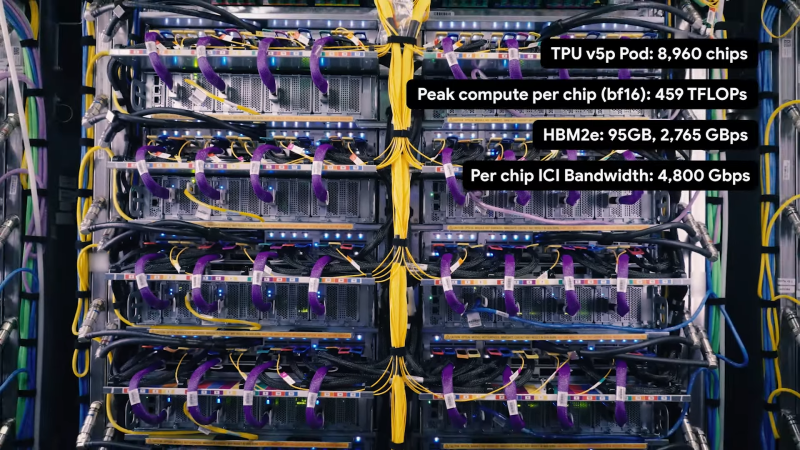

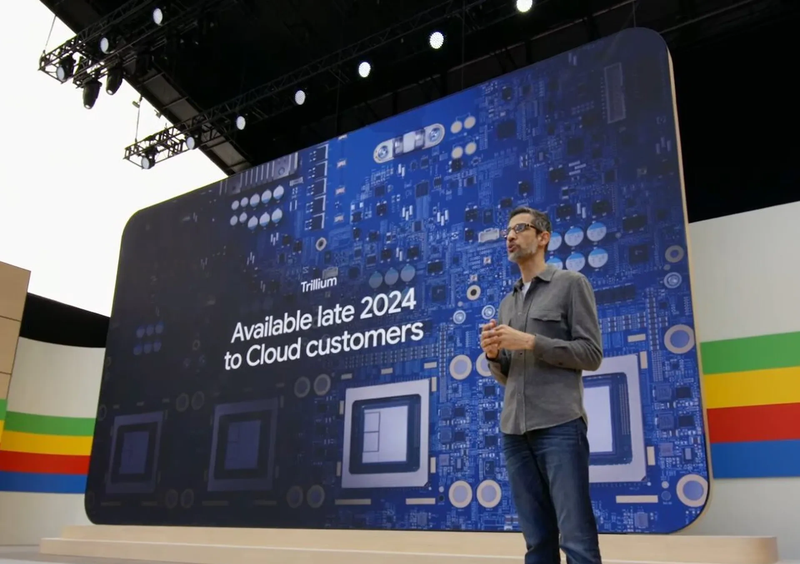

Шестое поколение ускорителей Google TPU v6 готово к обучению ИИ-моделей следующего поколенияGoogle успешно занимается разработкой ИИ-ускорителей порядка 10 лет. В прошлом году компания заявила, что четвёртое поколение TPU в связке с фирменными оптическими коммутаторами превосходит кластеры на базе NVIDIA A100 с интерконнектом InfiniBand, а к концу того же года было представлено уже пятое поколение, причём в двух вариантах: энергоэффективные TPU v5e для малых и средних ИИ-моделей и высокопроизводительные TPU v5p для больших моделей. Сбавлять темпа компания явно не собирается — не прошло и полугода, как было анонсировано последнее, шестое поколение TPU, получившее, наконец, собственное имя — Trillium. Клиентам Gooogle Cloud новинка станет доступна до конца этого года, в том числе в составе AI Hypercomputer. Сведений об архитектуре и особенностях Trillium пока не очень много, но согласно заявлениям разработчиков, он в 4,7 раза быстрее TPU v5e.

Источник: The Verge Ранее аналитик Патрик Мурхед (Patrick Moorhead) опубликовал любопытное фото, на котором глава подразделения кастомных чипов Broadcom держит в руках некий XPU, разработанный для «крупной ИИ-компании». Не исключено, что сделан он именно для Google. На снимке видна чиплетная сборка из двух крупных кристаллов в окружении 12 стеков HBM-памяти. Любопытно и то, что TPU v6 нарекли точно так же, как и проект Arm шестилетней давности по созданию нового поколения ИИ-ускорителей. Пропускная способность 32 Гбайт набортной HBM-памяти составляет 1,6 Тбайт/с. Межчиповый интерконнект ICI имеет пропускную способность до 3,2 Тбит/с, хотя в TPU v5p скорости ICI уже 4,8 Тбит/с. По словам Google, новый чип получился на 67% энергоэффективнее TPU v5e. Складывается ощущение, что компания сознательно избегает сравнения с TPU v5p. Но это объяснимо, поскольку заявленный почти пятикратный прирост производительности в сравнении с TPU v5e даёт примерно 926 Тфлопс в режиме BF16 и 1847 Топс в INT8, что практически вдвое выше показателей TPU v5p.

Кластер Google на базе TPU v5e. Источник: Google При этом компания не бравирует высокими цифрами в INT4/FP4, как это делает NVIDIA в случае с Blackwell. Согласно опубликованным данным, прирост производительности достигнут за счёт расширения блоков перемножения матриц (MXU) и прироста тактовой частоты. В новом TPU также использовано новое, третье поколение блоков SparseCore, предназначенных для ускорения работы с ИИ-модели, часто использующихся в системах ранжирования и рекомендаций. Масштабируется Trillium практически так же, как TPU v5e — в составе одного блока («пода») могут работать до 256 чипов. Эти «поды» формируют кластер с технологией Multislice, позволяющий задействовать в одной задаче до 4096 чипов. В таких кластерах на помощь приходят DPU Titanium, берущие на себя обслуживание IO-операций, сети, виртуализации, безопасности и доверенных вычислений. Размеры кластера могут достигать сотен «подов». Google полагает, что TPU v6 готовы к приходу ИИ-моделей нового поколения и имеет для этого все основания: ориентировочно каждый Trillium с его 32 Гбайт быстрой памяти может оперировать примерно 30 млрд параметров, а речь, напомним, в перспективе идёт о десятках тысяч таких чипов в одном кластере. В качестве интерконнекта в таких системах используется платформа Google Jupiter с оптической коммутацией, совокупная пропускная способность которой уже сейчас превышает 6 Пбайт/с. |

|