Материалы по тегу: risc-v

|

27.06.2024 [11:04], Сергей Карасёв

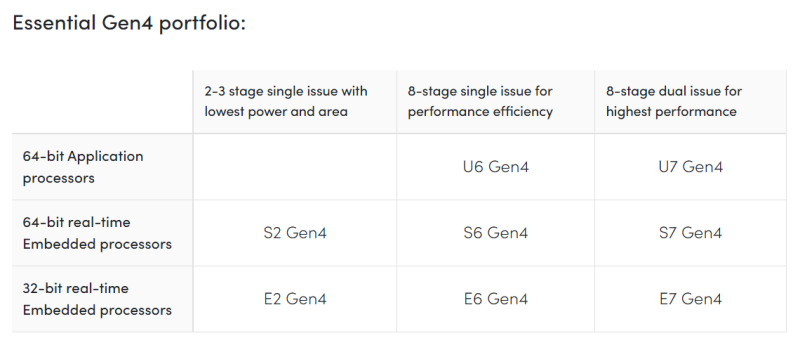

SiFive анонсировала новое семейство процессоров RISC-V для встраиваемых устройствКомпания SiFive, разработчик процессоров на архитектуре RISC-V, представила решения семейства Essential Gen4 для различных встраиваемых устройств. В серию вошли восемь модификаций базовых ядер RISC-V, которые могут применяться в таком оборудовании, как камеры наблюдения, решения FPGA, накопители на основе флеш-памяти, носимые гаджеты и пр. В частности, анонсированы 64-бит решения U6 и U7 для процессоров приложений, 64-бит ядра реального времени S2, S6 и S7 для встраиваемых систем, а также 32-бит ядра реального времени E2, E6 и E7. Для новинок заявлено снижение энергопотребления в рабочем режиме до 40 % по сравнению с ядрами RISC-V предыдущего поколения. Говорится об улучшенном кеше L2 и расширенном кеше L1. Разработчикам предоставляются гибкие возможности в плане конфигурирования устройств: тип CPU, различные варианты интегрированной памяти, выбор периферийных компонентов и портов. Кроме того, упомянуты развитые средства управления питанием и обеспечения безопасности. Ядра SiFive Essential Gen4 могут использоваться со встраиваемыми ОС Linux и FreeRTOS. Заявлена интеграция с IDE Eclipse. В целом, изделия четвёртого поколения обеспечивают более высокую производительность, повышенную энергоэффективность и более гибкие возможности в плане использования интерфейсов. При этом полные технические характеристики новинок компания не раскрывает. Отмечается также, что на сегодняшний день по всему миру реализовано более 2 млрд чипов с ядрами SiFive RISC-V для встраиваемых устройств. Данный рынок продолжает активно развиваться, что говорит о росте популярности открытой архитектуры RISC-V.

22.06.2024 [15:01], Сергей Карасёв

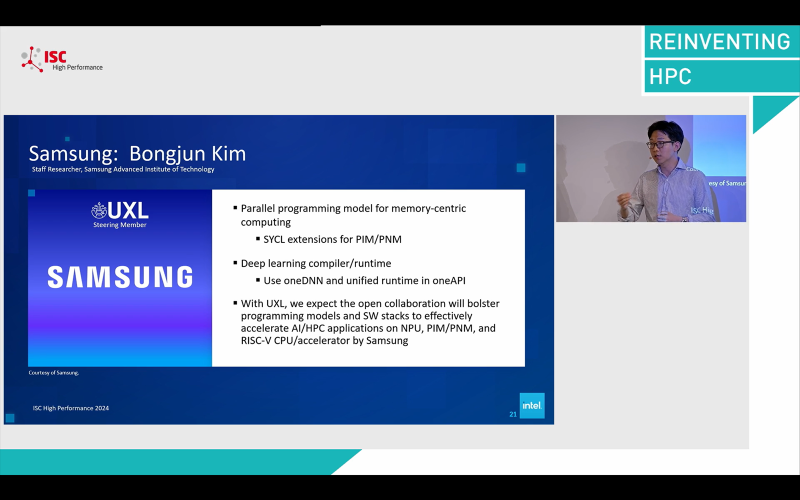

Samsung случайно упомянула о разработке RISC-V чипа для ИИ-задачВ ходе конференции ISC 2024 компания Samsung, по сообщению HPC Wire, намекнула на разработку некоего чипа на открытой архитектуре RISC-V. Предполагается, что это изделие будет использоваться при решении задач, связанных с ИИ и НРС. На одном из продемонстрированных южнокорейским производителем слайдов упоминается изделие CPU/ИИ-ускоритель на базе RISC-V («RISC-V CPU/AI accelerator from Samsung»). О чём именно идёт речь, сказать трудно. Возможно, Samsung проектирует процессор RISC-V с нейромодулем для ускорения ИИ-операций. С другой стороны, это может быть самостоятельный чип, предназначенный для работы в связке с ИИ-ускорителем. Например, Google уже использует RISC-V процессоры SiFive вместе со своим TPU. Отмечается, что слайд был показан на сессии ISC 2024, посвящённой инициативе UXL Foundation (Unified Acceleration Foundation). Целью данного проекта является создание универсального открытого ПО, которое позволит разработчикам ИИ-решений отказаться от CUDA и использовать ускорители других производителей. В состав UXL входят Intel, Qualcomm, Samsung, Arm и Google. На слайде также упоминается модель параллельного программирования в контексте вычислений в памяти. Данная концепция позволяет повысить производительность, в том числе при обучении ИИ-моделей. Ранее Samsung и AMD представили экспериментальный ИИ-суперкомпьютер, скрестив «вычислительную» память HBM-PIM и ускорители Instinct MI100. Кроме того, Samsung работает над похожей концепцией PNM (processing-near-memory), которая будет использоваться в модулях памяти CXL. Samsung также работает над собственными ИИ-ускорителями Mach-1, которые уже заказала ведущая южнокорейская интернет-компания Naver. По заявлениям Samsung, изделие Mach-1 позволяет выполнять инференс больших языковых моделей (LLM) даже с маломощной памятью. Таким образом, есть вероятность, что новый RISC-V-процессор Samsung сможет работать в связке с ИИ-ускорителями компании для максимизации производительности.

22.06.2024 [00:05], Алексей Степин

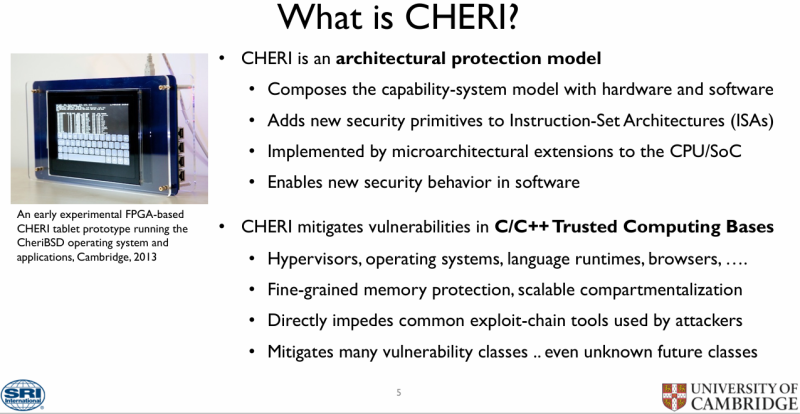

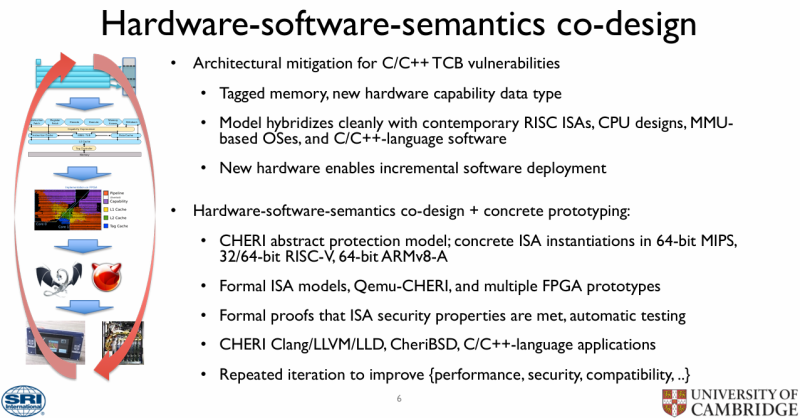

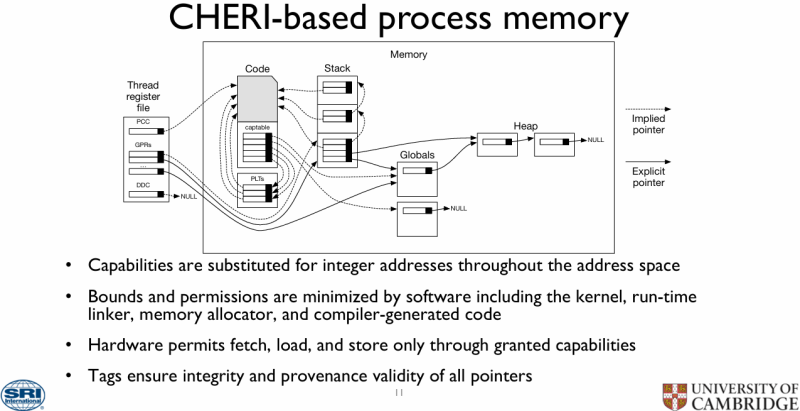

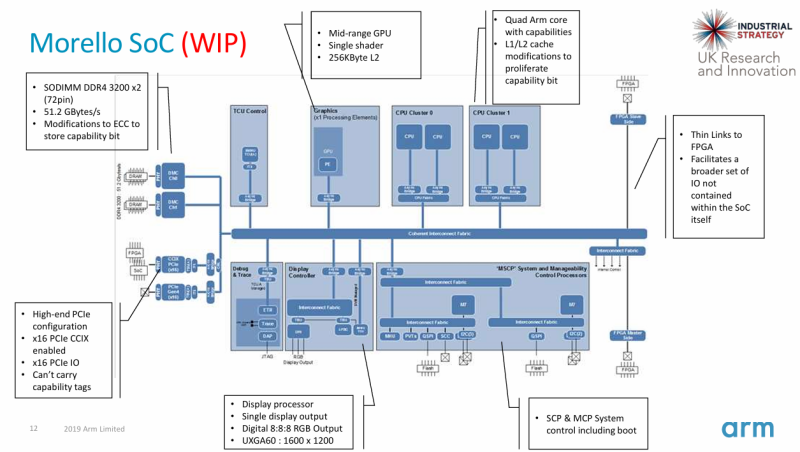

Альянс CHERI будет продвигать технологию надёжной защиты памяти от атак — первой её могут получить процессоры RISC-VВ современных процессорах немало возможностей для атак связано с особенностями работы современных подсистем памяти. Для противостояния подобным угрозам Capabilities Limited, Codasip, FreeBSD Foundation, lowRISC, SCI Semiconducto и Кембриджский университет объявили о создании альянса CHERI (Capability Hardware Enhanced RISC Instructions). Целью новой организации должна стать помощь в стандартизации, популяризации и продвижении на рынок разработанных Кембриджским университетом совместно с исследовательским центром SRI International процессорных расширений, позволяющих аппаратно реализовывать механизмы защиты памяти, исключающие целый ряд потенциальных уязвимостей, например, переполнение буфера или некорректная работа с указателями. Сама технология имеет «модульный» характер. Она может применяться выборочно для защиты функций от конкретных атак и требует лишь весьма скромной адаптации кода. Согласно заявлению CHERI Alliance, огромный пул уже наработанного ПО на языках семейств С и C++ может быть легко доработан для серьёзного повышения уровня безопасности. Кроме того, данная технология позволяет реализовать высокопроизводительные и масштабируемые механизмы компартментализации (compartmentalization) и обеспечения минимально необходимых прав (least privilege). Такое «разделение на отсеки» должно защитить уже скомпрометированную систему и не позволить злоумышленнику развить атаку, даже если он воспользовался ранее неизвестной уязвимостью. Технологии, предлагаемые альянсом CHERI, хорошо проработаны — их развитие идёт с 2010 года, а актуальность массового внедрения подобных решений за прошедшее время успела лишь назреть. Однако для успеха данной инициативы потребуется широкое содействие со стороны индустрии как аппаратного обеспечения, так и программного. Участники альянса настроены оптимистично, однако в их число пока не входит ни один из крупных разработчиков CPU, в частности, Arm. В настоящее время главной архитектурой для приложения своих усилий они видят RISC-V, о чём свидетельствует документация на CHERI ISAv9. Впрочем, черновой вариант расширений имеется и для x86-64. Сама Arm этого оптимизма не разделяет. Компания имеет за плечами пятилетний опыт разработки проекта Morello, основанному на идеях CHERI, но, по словам представителя Arm, процесс тестирования прототипов защищённых систем выявил ряд ограничений, пока препятствующий их широкому распространению на рынке. Тем не менее, работы над платформой Morello будут продолжены. При этом буквально на днях для Arm-процессоров была выявлена атака TikTag, направленная на обход механизма защиты памяти Memory Tagging Extensions (MTE).

10.06.2024 [08:11], Сергей Карасёв

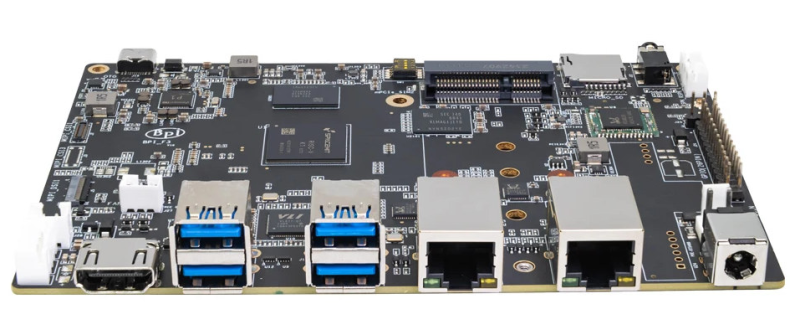

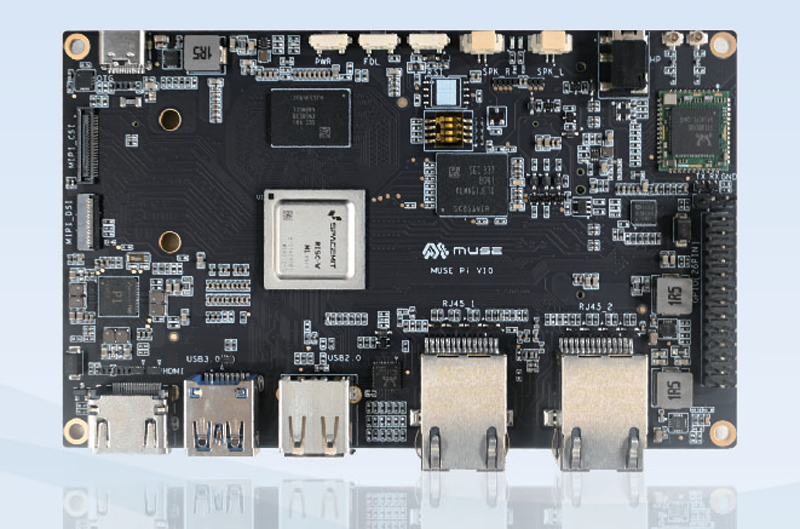

Одноплатный компьютер SpacemiT Muse Pi оснащен 8-ядерным чипом RISC-VКитайская компания SpacemiT анонсировала одноплатный компьютер Muse Pi, оснащённый процессором SpacemiT M1 на архитектуре RISC-V. Новинка доступна для заказа в конфигурации с 8 Гбайт оперативной памяти LPDDR4x-4266 и флеш-модулем eMMC вместимостью 32 Гбайт по ориентировочной цене $200. В плане форм-фактора изделие аналогично модели Banana Pi BPI-F3, которая оснащена чипом SpacemiT K1 на базе RISC-V с восемью ядрами, а также нейропроцессорным модулем (NPU) с производительностью до 2 TOPS. По заявлениям SpacemiT, процессор М1 по сравнению с К1 обладает более высокой производительностью. Он содержит восемь ядер с тактовой частотой до 1,6 ГГц и поддерживает стандарты RISC-V 64GCVB и RVA22.

Источник изображения: SpacemiT Одноплатный компьютер Muse Pi получил два сетевых порта 1GbE на основе разъёмов RJ-45, адаптеры Wi-Fi 6 (частотные диапазоны 2,4 и 5 ГГц) и Bluetooth 5.0 (с поддержкой Bluetooth Low Energy). Есть интерфейс HDMI 1.4 с поддержкой видео Full HD (1920 × 1080 пикселей; 60 Гц). Присутствуют порты USB 2.0 OTG Type-C (подача питания и обмен данными), USB 3.0 Type-A и USB 2.0 Type-A. Среди прочего упомянуты интерфейсы MIPI DSI (4 линии) и 2 × MIPI CSI (4 линии), 26-контактная колодка GPIO и слот для карты microSD. Говорится об использовании кастомизированного чипа P1 для управления питанием. В качестве программной платформы применяется Bianbu OS — сборка Linux, основанная на Debian и оптимизированная для процессоров SpacemiT с архитектурой RISC-V.

28.05.2024 [11:50], Сергей Карасёв

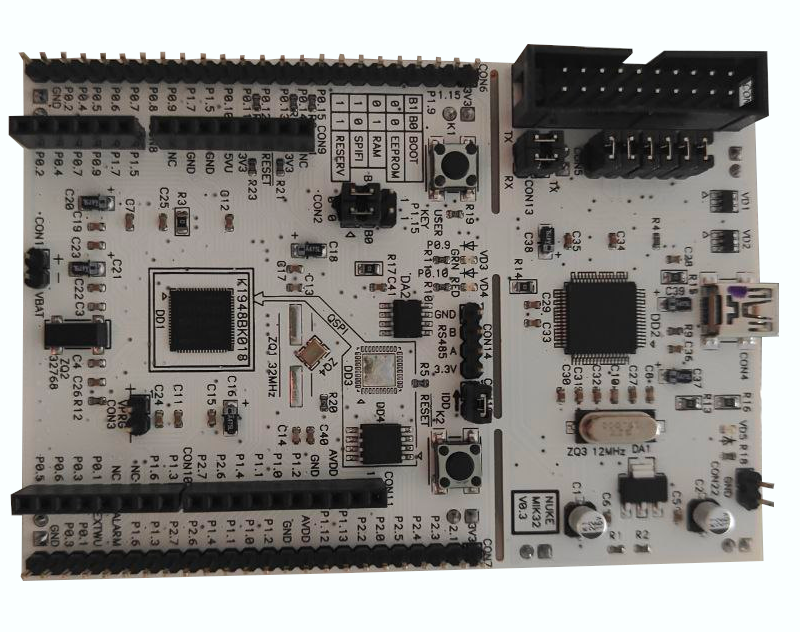

RISC-V DevBoards: стартует первая в России программа раннего доступа к архитектуре RISC-VАльянс RISC-V объявил о начале приёма заявок на участие в RISC-V DevBoards — это первая в России программа раннего доступа к архитектуре RISC-V с использованием отладочных плат для микроконтроллеров. Участие в программе не требует приобретения оборудования — оно предоставляется бесплатно. Отмечается, что участники RISC-V DevBoards смогут одними из первых протестировать возможности отечественных микроконтроллеров на открытой архитектуре RISC-V, а также создать прототипы собственных устройств. На первом этапе будет предоставлен доступ к микроконтроллеру «MIK32 Амур» (К1948ВК018) на базе отладочной платы MIK32. Напомним, изделие «MIK32 Амур», разработанное компанией «Микрон», содержит ядро RISC-V, однократно программируемую память (ПЗУ на 256 бит), ОЗУ ёмкостью 16 Кбайт, а также ПЗУ (EEPROM; 8 Кбайт). В дальнейшем перечень микроконтроллеров, доступных в рамках программы RISC-V DevBoards, планируется расширять.

Источник изображения: Альянс RISC-V / «Микрон» Компания Positive Technologies, входящая в состав Альянса RISC-V, оценит безопасность и уровень защищённости спроектированных устройств. Результаты тестирования лучших проектов будут опубликованы, а о разработке узнают профессионалы российского IT-рынка. Инициатива должна способствовать развитию экосистемы RISC-V в России.

27.05.2024 [14:51], Сергей Карасёв

RISC-V для учёбы: НИУ МИЭТ и YADRO представили микроконтроллер HackeeНациональный исследовательский университет «МИЭТ» и российский производитель вычислительной техники YADRO (ООО «КНС групп») представили учебный микроконтроллер Hackee на открытой архитектуре RISC-V. Новинка предназначена для применения во встраиваемых системах, носимой электронике и оборудовании Интернета вещей (IoT). В основу изделия положено 32-битное ядро SCR1. Тактовая частота составляет 85 МГц. Чип располагает 128 Кбайт оперативной памяти, таймерами, интерфейсами UART, SPI, I2C, CAN, JTAG. Изделие производится на предприятии АО «Микрон» по 180-нм технологии. Отмечается, что Hackee является результатом сотрудничества участников российского Альянса RISC-V — объединения независимых разработчиков вычислительной техники и программного обеспечения на архитектуре RISC-V. Основная цель организации — создание открытого сообщества разработчиков для дальнейшего развития RISC-V в России.

Источник изображения: Альянс RISC-V Нужно отметить, что ранее «Микрон» (входит в ГК «Элемент») представила отечественный микроконтроллер «MIK32 Амур» на базе RISC-V. Решение предназначено для устройств промышленной автоматизации, IoT, беспроводной периферии, интеллектуальных сетей, охранных систем и пр. Причём спрос на это изделие превзошёл ожидания.

10.05.2024 [21:34], Сергей Карасёв

Восьмиядерный RISC-V с NPU: одноплатный компьютер Banana Pi BPI-F3 получил чип SpacemiT K1Banana Pi, по сообщению ресурса CNX Software, начала поставки одноплатного компьютера BPI-F3, особенностью которой является использование процессора SpacemiT K1 на открытой архитектуре RISC-V. Изделие подходит для работы с приложениями ИИ. Новинка была анонсирована в феврале этого года. Чип SpacemiT K1 объединяет восемь 64-бит RISC-V ядер, неназванный графический блок с поддержкой OpenCL 3.0, OpenGL ES3.2 и Vulkan 1.2, а также нейропроцессорный модуль (NPU) с производительностью до 2 TOPS. Говорится о возможности кодирования/декодирования материалов H.265, H.264, VP9, VP8.

Источник изображения: Banana Pi Объём оперативной памяти LPDDR4 может составлять 2 или 4 Гбайт, вместимость флеш-модуля eMMC — 8 или 16 Гбайт. Есть слот для карты microSD и коннектор M.2 Key-M для SSD с интерфейсом PCIe 2.1 x1 или SATA. Опционально могут быть добавлены флеш-чипы SPI NAND на 32 Мбайт и SPI NOR на 4 Мбайт. В оснащение входят два порта 1GbE (RJ-45) на контроллере Realtek RTL8211F с опциональной поддержкой PoE (через плату RT5400), а также адаптеры Wi-Fi 5 (2,4/5 ГГц) и Bluetooth 4.2 на базе Realtek RTL8852BS. Дополнительно предлагается модем 4G в виде модуля mPCIe (плюс слот для SIM-карты). Доступны четыре порта USB 3.0 Type-A, разъём USB 2.0 Type-C и коннектор HDMI 1.4 (до 1080p60). Поддерживаются интерфейсы MIPI DSI (4 линии) и 2 × MIPI-CSI (4 линии). Кроме того, упомянуты 26-контактная колодка GPIO, инфракрасный порт и разъём для подсоединения вентилятора. Питание (12 В / 3 A) подаётся через DC-гнездо. Габариты составляют 148 × 100 мм, вес — около 200 г. Цена начинается примерно с $63.

04.05.2024 [14:15], Сергей Карасёв

Спрос на первый российский микроконтроллер на базе RISC-V оказался очень высокимКомпания «Микрон», входящая в ГК «Элемент», по сообщению газеты «Ведомости», столкнулась с повышенным спросом на изделие «MIK32 Амур» — первый полностью отечественный микроконтроллер на открытой архитектуре RISC-V. Популярность новинки оказалось настолько высокой, что собственных мощностей для её выпуска недостаточно. Решение «MIK32 Амур» вышло в феврале нынешнего года. Микроконтроллер объединяет ядро RISC-V, однократно программируемую память (ПЗУ на 256 бит), ОЗУ ёмкостью 16 Кбайт, а также ПЗУ (EEPROM; 8 Кбайт). Есть 12-битные АЦП и ЦАП с частотой дискретизации до 1 МГц, датчик температуры, часы реального времени с поддержкой полного календаря.

Источник изображения: «Микрон» Говорится, что объём производства «MIK32 Амур» исчисляется миллионами штук. Корпусирование изделий компания «Микрон» вынуждена осуществлять не только на своих мощностях в подмосковном Зеленограде, но и на линиях стороннего контрактного производителя. Утверждается, в частности, что заказы размещены на калининградском предприятии GS Group. Представители ГК «Элемент» не уточняют, какой именно объём производства изделия заказан у GS Group, но осведомлённые источники утверждают, что речь идёт о более чем 2 млн штук в 2024–2025 гг. Контроллер «MIK32 Амур» предназначен для устройств промышленной автоматизации и Интернета вещей, беспроводной периферии, интеллектуальных сетей, охранных систем, сигнализации, телеметрии, мониторинга, умного дома, а также для управления климатом, освещением и пр. В конце 2022 года говорилось, что «Микрон» намерен вложить в разработку изделия 80–90 млн руб., а в последующую организацию серийного производства — ещё 100–300 млн руб. К 2025-му компания намеревается занять 30 % рынка таких контроллеров в России. Кроме того, рассматривается возможность экспорта продукта в страны Юго-Восточной Азии. «Возможный высокий спрос на микроконтроллер "Амур" выглядит вполне закономерным, поскольку на текущий момент это единственный отечественный микроконтроллер, который и разработан, и произведён в России, и доступен для массового производства. Его можно считать прорывным устройством не только для самого "Микрона", но и в целом для российской микроэлектроники», — отмечает гендиректор «Байкал Электроникс».

15.03.2024 [22:43], Алексей Степин

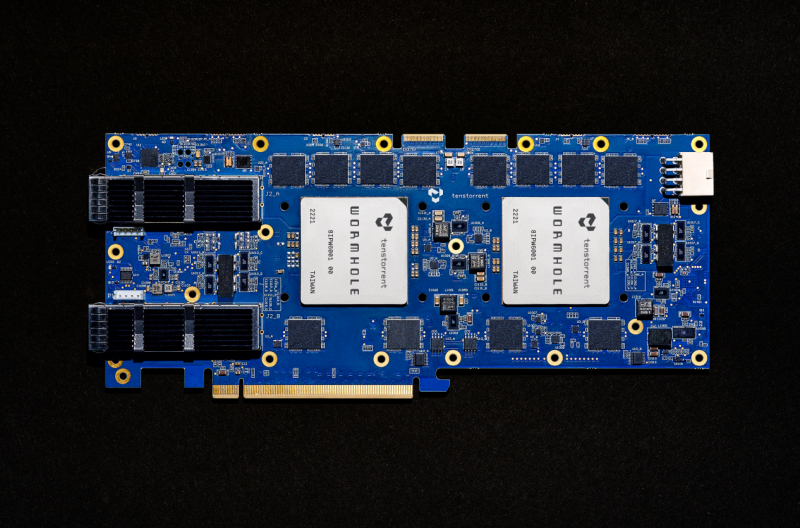

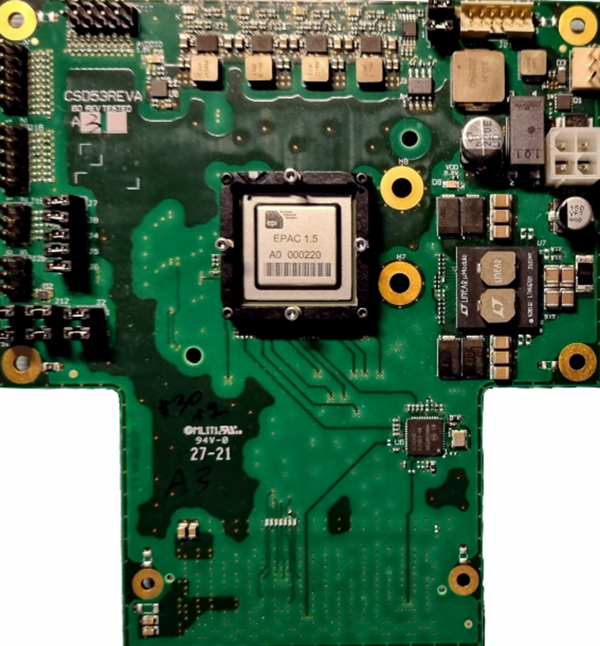

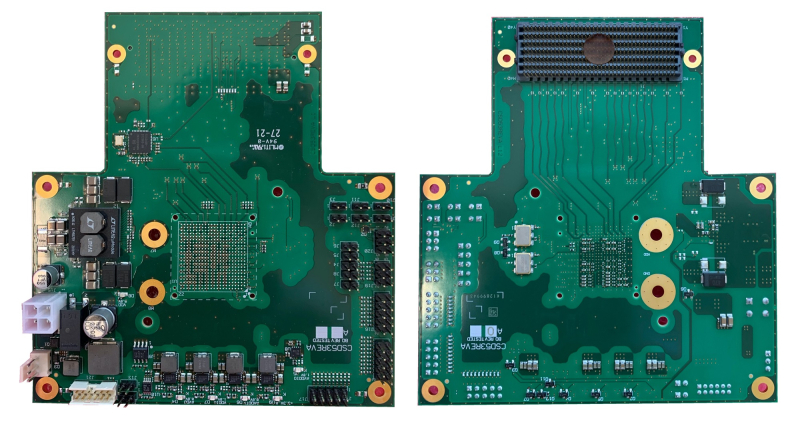

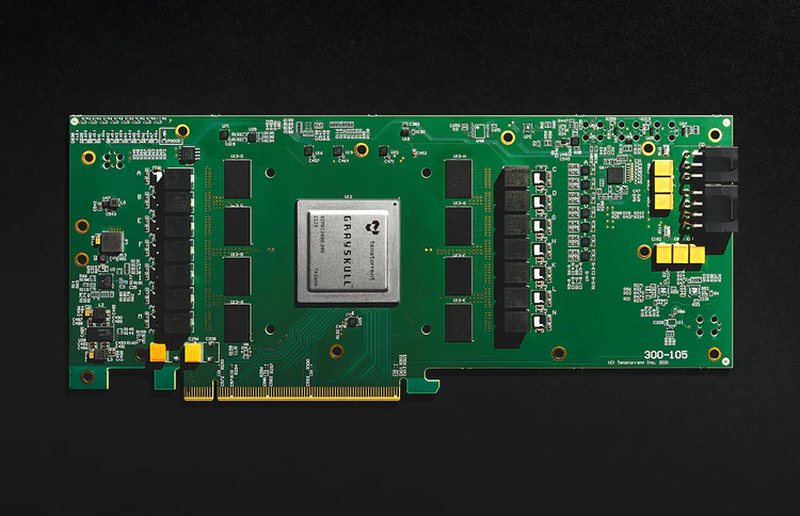

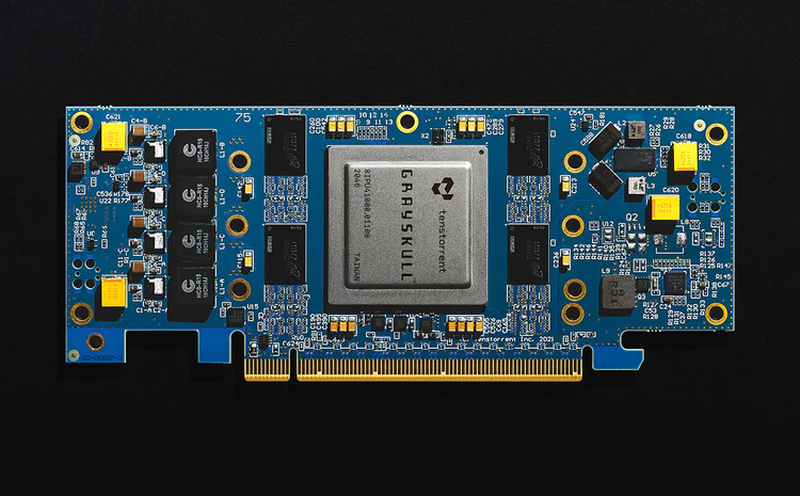

Tenstorrent под руководством Джима Келлера представила свои первые ИИ-ускорители Grayskull на базе RISC-VКанадский разработчик микрочипов Tenstorrent, возглавляемый легендарным Джимом Келлером (Jim Keller), наконец, представил свои первые решения на базе архитектуры RISC-V — ИИ-процессоры Grayskull и ускорители на их основе, Grayskull e75 и e150. Оба варианта доступны для приобретения уже сейчас по цене $599 за младшую версию и $799 за старшую. Данные решения предназначены для инференс-систем, разработки и отладки ПО. В комплект разработчика входят инструменты TT-Buda и TT-Metalium. В первом случае речь идёт о высокоуровневом стеке, предназначенном для компиляции и запуска ИИ-моделей на аппаратном обеспечении Tenstorrent, а во втором — о низкоуровневой программной платформе, обеспечивающей прямой доступ к аппаратным ресурсам. Поддерживается PyTorch, ONNX и другие фреймворки. Создатели делают особенный упор на простоте программирования в сравнении с классическими GPU. Поддерживается широкий спектр ИИ-моделей, но Tenstorrent особенно выделяет BERT, ResNet, Whisper, YOLOv5 и U-Net.

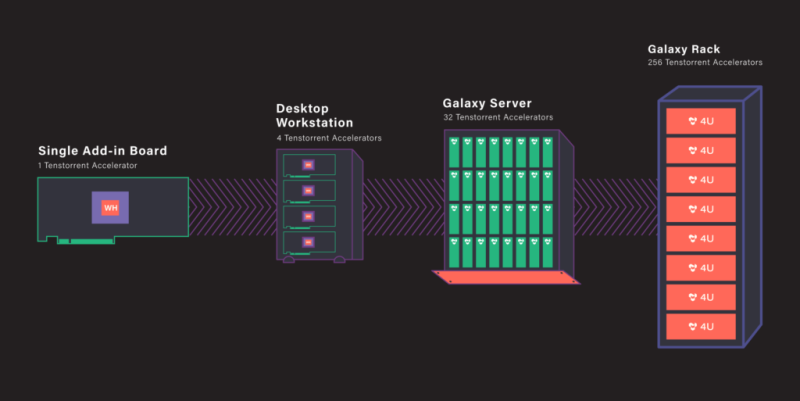

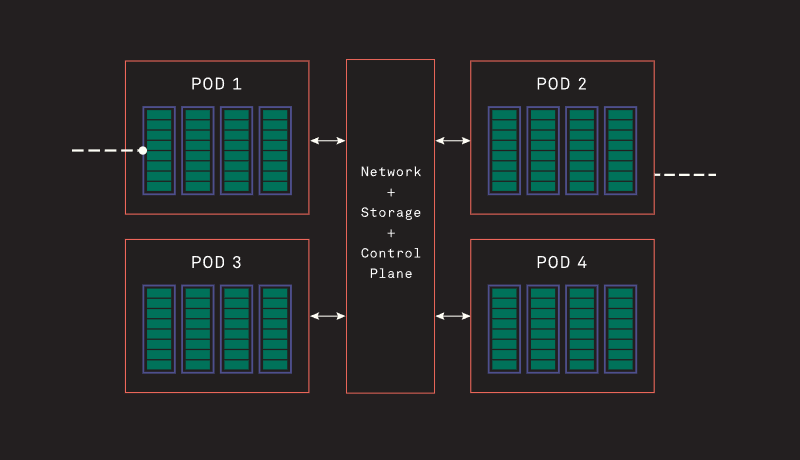

Источник изображений здесь и далее: Tenstorrent Архитектура Grayskull базируется на RISC-V, в настоящий момент максимальное количество фирменных ядер Tensix достигает 120, работают они на частотах вплоть до 1,2 ГГц. Каждое такое ядро содержит пять полноценных ядер RISC-V, блок тензорных операций, блок SIMD для векторных операций, а также ускорители сетевых операций и сжатия/декомпрессии данных. Дополнительно каждое ядро может иметь до 1,5 Мбайт сверхбыстрой памяти SRAM. Между собой ядра общаются напрямую.  В случае Grayskull e150 процессор работает в полной конфигурации со 120 ядрами и 120 Мбайт SRAM, объём внешней памяти LPDDR4 составляет 8 Гбайт (ПСП 118,4 Гбайт/с). Ускоритель выполнен в формате полноразмерной платы расширения с теплопакетом 200 Вт и интерфейсом PCIe 4.0 x16. У младшей модели, Grayskull e75, активных ядер только 96, их частота снижена до 1 ГГц, а пропускная способность внешней памяти при том же объёме снижена до 102,4 Гбайт/с. При этом теплопакет составляет всего 75 Вт, что позволило выполнить ускоритель в виде низкопрофильной платы расширения и обойтись без дополнительного питания. Чипы Wormhole тоже используют Tensix. В составе Wormhole n300 таких ядер 128 (2 × 64), частота равна 1 ГГц при теплопакете 300 Вт. Объём SRAM составляет 1,5 Мбайт на ядро, а внешняя подсистема памяти включает 24 Гбайт GDDR6 и с ПСП 576 Гбайт/с. Wormhole n150 оснащены 72 ядрами Tensix, 108 Мбайт SRAM и 12 Гбайт GDDR6 с ПСП 288 Гбайт/с. TDP составляет 160 Вт. От Grayskull эти решения отличаются возможностью масштабирования путём прямого объединения плат. Также есть по паре сетевых интерфейсов 200GbE. Возможна работа с форматами FP8/16/32, TF32, BFP2/4/8, INT8/16/32 и UINT8. Чипы Tenstorrent Grayskull и Wormhole лежат в основе уникальных масштабируемых платформ собственной разработки — AICloud и Galaxy. В первом случае используются процессоры Grayskull, поскольку Wormhole на рынке должен появиться позже. Платформа предназначена в качестве аппаратной для ИИ и HPC-нагрузок в облаке Tenstorrent.  Каждый 4U-узел AICloud высотой содержит восемь карт (16 чипов) и способен предоставить в распоряжение пользователей от 30 до 60 vCPU и от 256 до 1024 Гбайт памяти, вкупе с дисковым пространством объёмом 100–400 Гбайт. Восемь таких узлов составляют стойку, а четыре стойки — кластер Server Pod. Четыре таких кластера объединены общей системой интерконнекта, управления и СХД (до 200 Тбайт), дальнейшее масштабирование уже выходит на уровень ЦОД. В Tenstorrent Galaxy упор сделан на возможность создания высокопроизводительных ИИ-систем с быстрым интерконнектом на базе Ethernet. Строительным блоком здесь являются 80-ядерные модули Wormhole. 4U-сервер вмещает 32 таких модуля, что в совокупности даёт 2560 ядер Tensix и 384 Гбайт глобально адресуемой GDDR6. Наличие 16 каналов 200GbE в каждом модуле обеспечивает производительность интерконнекта на уровне 3,2 Тбитс. На уровне стойки высотой 48U это дает 256 чипов Wormhole, общий объём SRAM в этом случае достигает 30,7 Гбайт, а GDDR6 — 3 Тбайт. Производительность стойки оценивается разработчиками в 20 Попс (Петаопс), а совокупная скорость интерконнекта — в 76,8 Тбит/с. Расплатой за универсальность и производительность станет энергопотребление, достигающее 60 КВт.

04.03.2024 [17:00], Руслан Авдеев

Евросоюз намерен добиться полупроводникового суверенитета, используя архитектуру RISC-VВ Евросоюзе активно инвестируют в инициативы, призванные обеспечить полупроводниковый суверенитет благодаря использованию открытой архитектуры RISC-V. EE Times сообщает, что инициативу курирует Барселонский суперкомпьютерный центр (Barcelona Supercomputing Center или BSC) — пионер в разработке европейских решений RISC-V. Страны ЕС беспокоит полупроводниковая зависимость от иностранных компаний, и это беспокойство усугубляется относительно недавним дефицитом чипов в мире. В то же время за использование в своих решениях архитектуры RISC-V никому не надо платить и ни у кого не нужно получать разрешений на её применение, поэтому технология так привлекательна для разработчиков. BSC представляет собой один из ведущих исследовательских центров Европы. Он играет ключевую роль в разработке чипов на архитектуре RISC-V и возглавляет несколько проектов, связанных с этой технологией, в частности, European Processor Initiative (EPI). В рамках инициативы EPI стоимостью €70 млн разрабатывается новое поколение высокопроизводительных процессоров. Связанная с BSC компания OpenChip должна найти коммерческое применение разработанным технологиям. BSC начал создавать собственные чипы семейства Lagarto довольно давно — первые 65-нм варианты представили ещё в мае 2019 года. Сегодня речь идёт уже о четвёртом поколении, которое будет выпускаться в соответствии с 7-нм техпроцессом. Центр работает и с другими европейскими компаниями и исследовательскими организациями над созданием комплексной экосистемы RISC-V, включающей ПО, ОС и компиляторы. Подобные инициативы должны снизить зависимость Евросоюза от американских и азиатских производителей — отсутствие в ЕС зрелой индустрии высокопроизводительных чипов расценивается как значимая уязвимость. Европа считает, что RISC-V — идеальная платформа для достижения суверенитета, при этом бесплатная. Впрочем, эксперты признают, что о полной независимости не может быть речи из-за сложности экосистемы полупроводниковой индустрии. Но у Европы есть большая база знаний и потенциал разработки новых решений, предпринимаются и шаги к организации производства. В BSC уже экспериментировали с Arm-процессорами, но после Brexit и приобретения компании Arm группой Softbank, выяснилось, что собственной региональной технологии у ЕС нет, тогда и обратили внимание на общедоступную RISC-V. В 2019 году Еврокомиссию убедили в необходимости начать выпуск чипов на этой архитектуре для суперкомпьютеров. В числе других европейских компаний, предлагающих RISC-V продукты, есть Gaiser, Esperanto Technologies, Semidynamics и Codasip, но они уделяют больше внимания процессорам и ускорителям, а не конечным готовые решения. По оценкам экспертов, в Евросоюзе компаний, работающих с RISC-V, пока недостаточно. Тем не менее, организаторы новых инициатив предостерегают от нереалистичных ожиданий и призывают к стратегическому сотрудничеству — для производства требуются не только разработки, но и сырьё, высокоточное оборудование, и др. Европа может рассчитывать на выпуск решений в пределах 7-нм, более современные техпроцессы пока слишком дороги. Впрочем, ЕС уже добился значительного прогресса в достижении полупроводникового суверенитета с помощью RISC-V. |

|