Материалы по тегу: risc-v

|

16.08.2024 [09:20], Алексей Степин

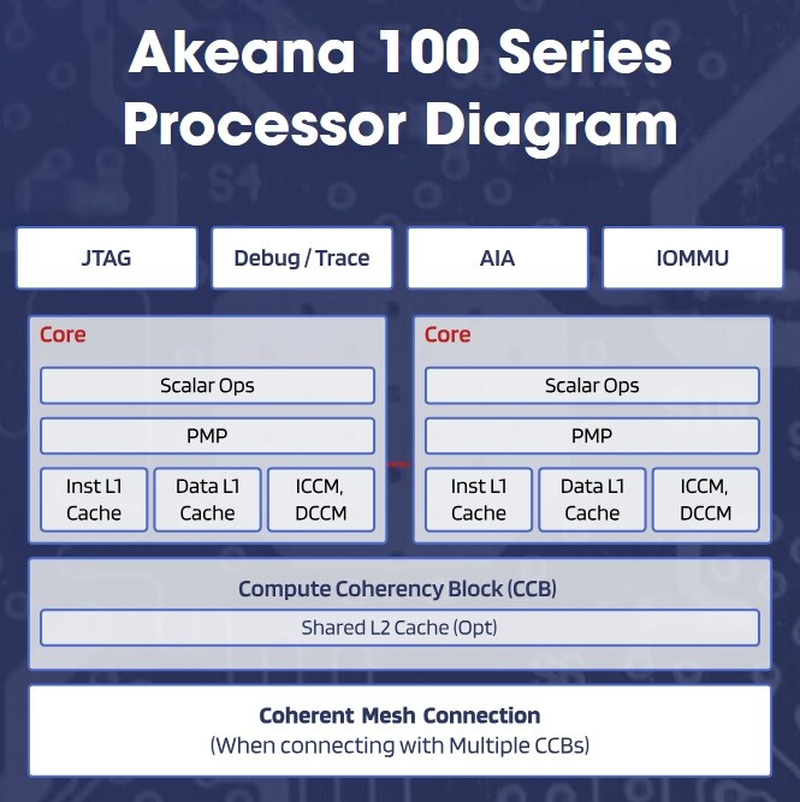

От IoT до ЦОД: Akeana, основанная выходцами из Marvell, представила три семейства ядер RISC-VВ 2021 году выходцы из Marvell и Cavium, стоявшие в своё время за созданием серверных Arm-процессоров ThunderX, основали стартап Akeana, который на днях вышел из т.н. скрытого режима и анонсировал RISC-V ядра собственной разработки. Akeana прямо говорит, что планирует бросить вызов Arm, SiFive, Andes и другим разработчикам чипов с архитектурой RISC-V. За три года Akeana удалось получить от крупных инвесторов, включая Kleiner Perkins, Mayfield и Fidelity, финансирование свыше $100 млн. А на этой неделе Akeana представила целую серию кастомизируемых IP-решений, в том числе три дизайна процессорных ядер с архитектурой RISC-V.

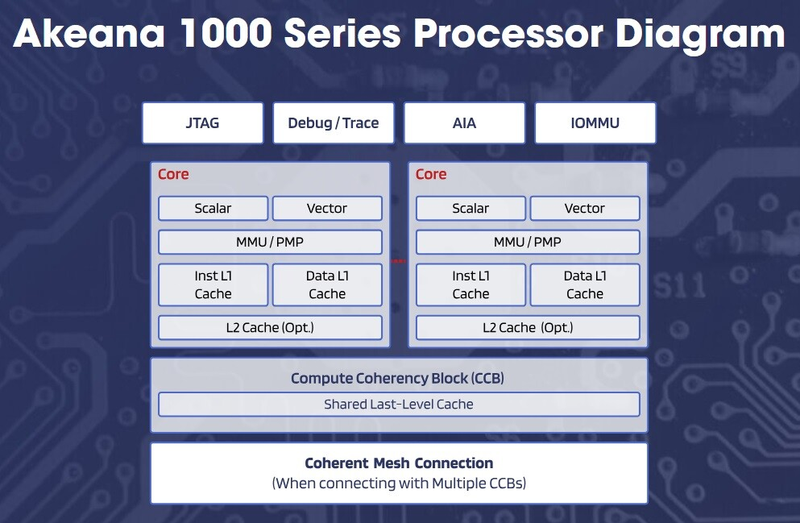

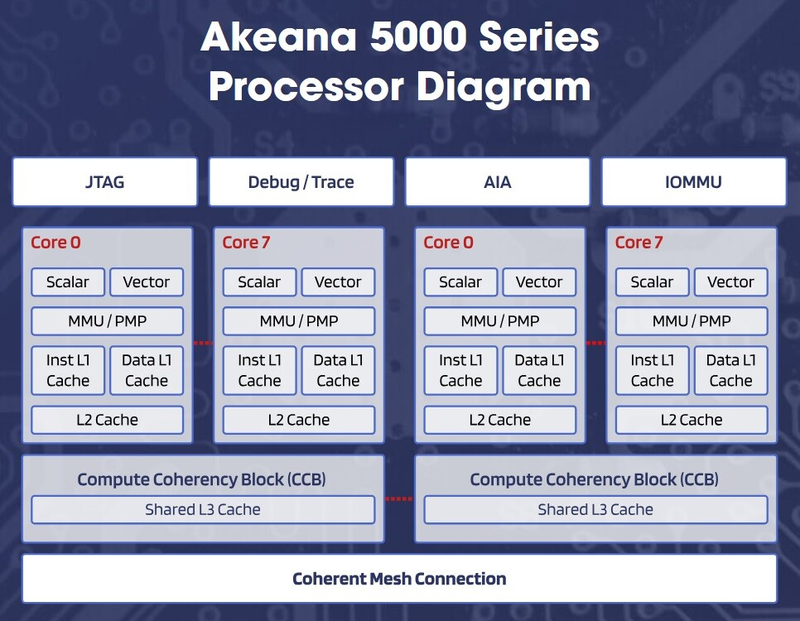

Источник здесь и далее: Akeana Остальные решения относятся к экосистеме, которую планирует сформировать Akeana. Это система высокоскоростного интерконнекта SCI (Scalable Coherent Interconnect, совместим с AMBA CHI), блоки контроллера прерываний, IOMMU, систему кластеризации и когерентности кешей, блоки векторных и матричных вычислений для ИИ-нагрузок и многое другое, включая разнообразные микроконтроллеры и подсистемы.  Что касается процессорных дизайнов, то компания представила сразу три серии:

В каждой из серий анонсировано по три-четыре базовых варианта с разной функциональностью, конфигурацией и объёмами кешей. Наибольший интерес представляет, пожалуй, серия 5000, которая позиционируется в качестве достаточно мощных процессоров для использования как в ПК и ноутбуках (в последнем случае предлагается использовать гетерогенный вариант с Akeana 1000 в качестве «малых» ядер), так и в качестве серверной инфраструктурной основы.  Ядра Akeana поддерживают кластеризацию (до 8 ядер на кластер), но, к сожалению, компания пока не раскрывает пределов масштабирования, тогда как новый дизайн SiFive, как мы уже знаем, позволяет создавать процессоры с числом ядер до 256. Говорить о каких-то реальных прототипах ещё рано, но все три серии ядер Akeana уже доступны для лицензирования клиентами. Очевидно, что экосистема RISC-V вступает в фазу активного развития: одна за другой компании-разработчики представляют всё новые и новые дизайны процессорных ядер и целых платформ, причём в широчайшем диапазоне характеристик — от экономичных микроконтроллеров до многоядерных серверных решений.

15.08.2024 [09:36], Алексей Степин

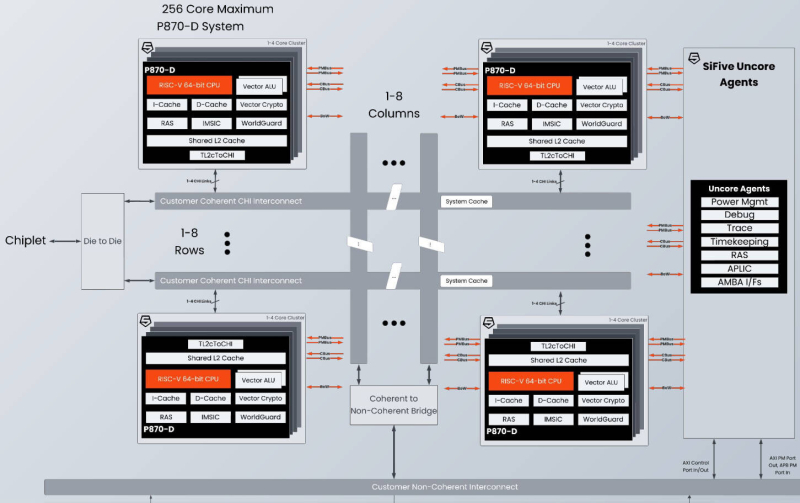

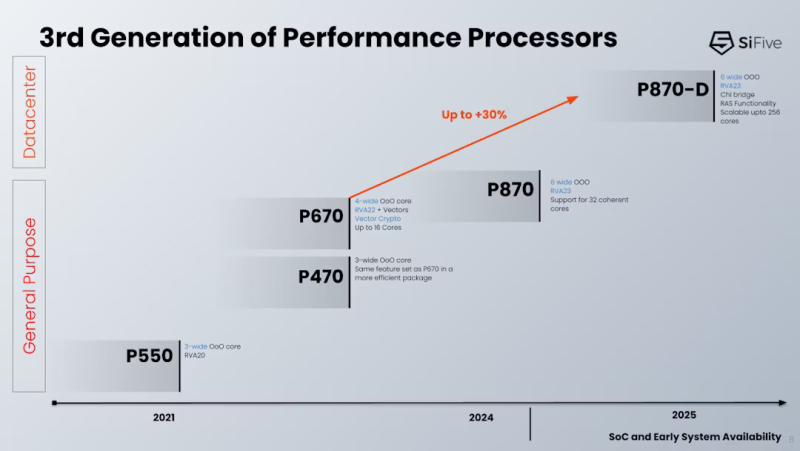

256 × RISC-V: SiFive представила высокопроизводительные ядра P870-D для серверов и СХДОткрытая архитектура RISC-V, которая, как многие надеются, станет конкурентом Arm не только в компактных и экономичных устройствах, но и в серверных системах, продолжает развиваться. Один из ведущих разработчиков в этой сфере, компания SiFive, анонсировала новое ядро P870-D. Как следует из системы обозначений, принятой SiFive, это высокопроизводительное (Performance) ядро, а суффикс D означает Datacenter. Новинка предназначена для серверных процессоров с количеством ядер до 256. Дизайн P870-D нельзя назвать полностью новым, поскольку он основан на ядре P870, анонсированном в конце 2023 года. Данное решение предназначалось для создания процессоров с числом ядер до 32 и включало в себя два 128-бит векторных блока, при этом каждые четыре ядра группировались в кластер, использовавший разделяемый кеш L2. P870-D сохранило черты предшественника. Это 64-бит ядро с поддержкой внеочередного исполнения инструкций и шириной декодера 6. В нём реализована поддержка набора инструкций RVA 23, Vector 1.0 и Vector Crypto. Появилась поддержка функций обеспечения повышенной надёжности RAS (Reliability, availability and serviceability). Контроль чётности присутствует уже на уровне регистровых файлов, а на всех уровнях подсистемы кешей имеется коррекция ошибок SECDED ECC. Но это не всё, в P870D есть поддержка AMBA CHI (4 порта). Это нововведение позволило SiFive существенно улучшить масштабирование — P870-D может служить основой для процессоров с числом ядер до 256, включая гетерогенные, в том числе возможны многочиповые дизайны и варианты с поддержкой CXL. Сами ядра по-прежнему группируются в кластеры по четыре, а CHI-подключение может обеспечиваться как встроенным мостом, так и внешним чиплетом. Также в состав P870-D входит распределённый масштабируемый блок IOMMU, платформа безопасности WorldGuard и uncore-агент, ответственный за питание, отладку, трассировку и т.д. Есть и контроллер прерываний Advanced Interrupt Architecture (AIA) с поддержкой Message Signal Interrupts (MSI) и виртуализации. В настоящее время это самое мощное ядро в арсенале SiFive, основными его конкурентами названы Arm Cortex-X2 и AMD Zen 4c. Однако перекоса в сторону исключительно производительности у P870-D нет. Поскольку данный дизайн ориентирован на современные высокоплотные ЦОД и платформы периферийных вычислений, разработчики уделили серьёзное внимание вопросам энергопотребления и тепловыделения. Впрочем, точных данных по этим параметрам пока приведено не было. Компания активно сотрудничает с партнерами по экосистеме RISC-V. Так, уже заключено соглашение с Arteris, которая выпустит референсные платформы валидации на базе P870-D и X280 с интегрированной поддержкой Arteris Network-on-Chip (NoC), что должно упростить дальнейшую разработку сложных гетерогенных чипов с функциями ИИ (за счёт блоков SiFive Intelligence) и ускорить вывод на рынок решений на базе таких чипов. Образцы чипов на базе SiFive P870-D уже поставляются ведущим партнёрам компании, а начало массового производства намечено на конец текущего 2024 года. Зарубежные аналитики полагают, что за энергоэффективными платформами на базе открытых стандартов большое будущее. К 2030 году решения, подобные SiFive P870-D, как ожидается, займут более 40 % всего рынка серверных процессоров.

09.08.2024 [23:30], Сергей Карасёв

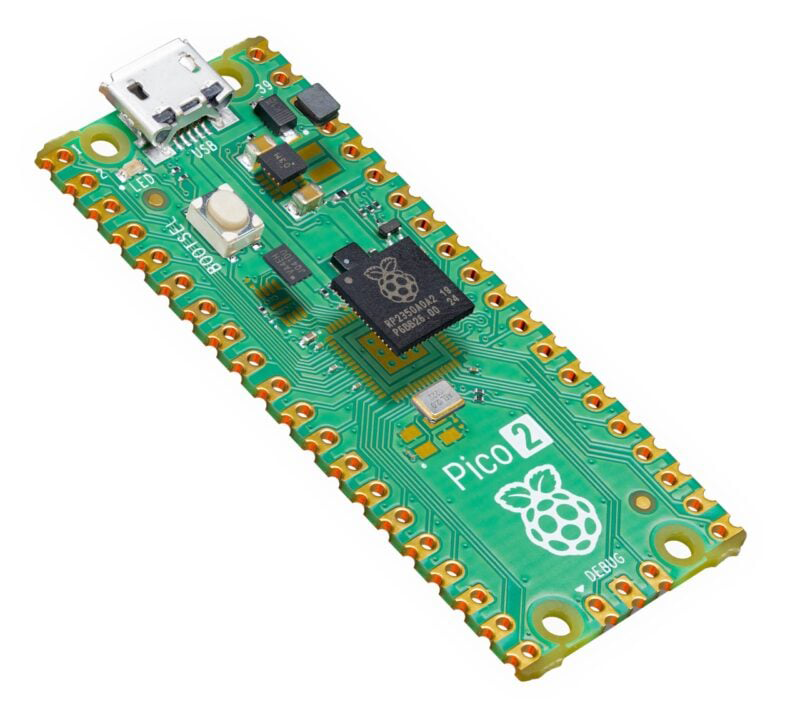

Представлена крошечная плата Raspberry Pi Pico 2 за $5 на чипе с ядрами RISC-V и ArmКомпания Raspberry Pi анонсировала микроплату Pico 2, в основу которого положен гибридный чип RP2350: это изделие объединяет ядра с архитектурой Arm и RISC-V. Для новинки заявлена обратная аппаратная и программная совместимость с более ранними представителями серии Pico. Оригинальная плата Raspberry Pi Pico дебютировала в январе 2021 года. Она получила микрочип собственной разработки RP2040, содержащий два ядра Cortex M0+ с базовой тактовой частотой 48 МГц и возможностью повышения до 133 МГц. Чип RP2350, в свою очередь, имеет более сложную конструкцию.

Источник изображения: Raspberry Pi В состав RP2350 входят по два ядра Arm Cortex-M33 и RISC-V Hazard3 (RV32I с расширениями): в обоих случаях тактовая частота составляет 150 МГц. Однако использовать эти кластеры сообща нельзя — одна из двух конфигураций выбирается при инициализации устройства. Правда, при выборе RISC-V не будут работать часть функций безопасности и FP64-ускорение. Чип существует в модификациях RP2350A (QFN-60; 7 × 7 мм; 30 × GPIO) и RP2350B (QFN-80; 10 × 10 мм; 48 × GPIO). Есть 520 Кбайт памяти SRAM в обоих вариантах исполнения. Плата Raspberry Pi Pico 2 располагает 4 Мбайт флеш-памяти QSPI и портом Micro-USB 1.1. Говорится о поддержке 2 × UART, 2 × SPI, 2 × I2C, 16 × PWM, 4 × ADC. Размеры новинки равны 51 × 21 мм. Напряжение питания — от 1,8 до 5,5 В. Диапазон рабочих температур простирается от -20 до +85 °C. Плата Raspberry Pi Pico 2 предлагается как по отдельности, так и в партиях из 480 штук. Изделие будет производиться как минимум до января 2040 года, то есть жизненный цикл составляет не менее 16 лет. Приобрести новинку можно по цене $5.

09.08.2024 [11:48], Сергей Карасёв

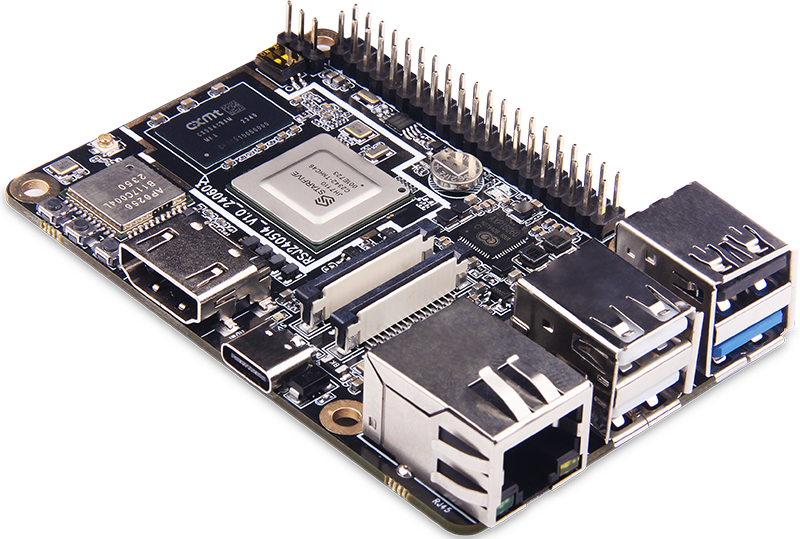

Одноплатный компьютер Geniatech XPI-7110 в стиле Raspberry Pi получил чип RISC-VКомпания Geniatech представила одноплатный компьютер XPI-7110, предназначенный для создания различных устройств Интернета вещей. Новинка, выполненная в стиле Raspberry Pi, использует аппаратную платформу StarFive с процессором на открытой архитектуре RISC-V. Изделие имеет размеры 85 × 56 мм. Установлен чип JH7110, который содержит четыре 64-битных ядра RISC-V (SiFive U74 — RV64GC) с частотой 1 ГГц и графический блок Imagination BXE-4-32 с поддержкой OpenCL 1.2, OpenGL ES 3.2, Vulkan 1.2. Возможно декодирование видео H.264/H.265 4Kp60 и кодирование материалов H.265 1080p30.

Источник изображения: Geniatech В базовой комплектации одноплатный компьютер несёт на борту 2 Гбайт памяти LPDDR4, в максимальной — 8 Гбайт. Есть флеш-модуль eMMC вместимостью 16 Гбайт (до 256 Гбайт), а также слот для карты microSD. В оснащение входят адаптеры Wi-Fi (2,4/5 ГГц, стандарт не указан) и Bluetooth 5.0, сетевой контроллер 1GbE. Есть выход HDMI, порт USB 3.0 и три порта USB 2.0, гнездо RJ-45 для сетевого кабеля. Кроме того, упомянуты интерфейсы MIPI DSI и MIPI CSI, а также 40-контактная колодка GPIO, совместимая с Raspberry Pi. Питание подаётся через разъём USB Type-C (5 В / 3 A). Одноплатный компьютер Geniatech XPI-7110 доступен в коммерческой и индустриальной версиях: в первом случае диапазон рабочих температур простирается от 0 до +60 °C, во втором — от -40 до +85 °C. Заявлена совместимость с Debian Linux.

20.07.2024 [21:45], Владимир Мироненко

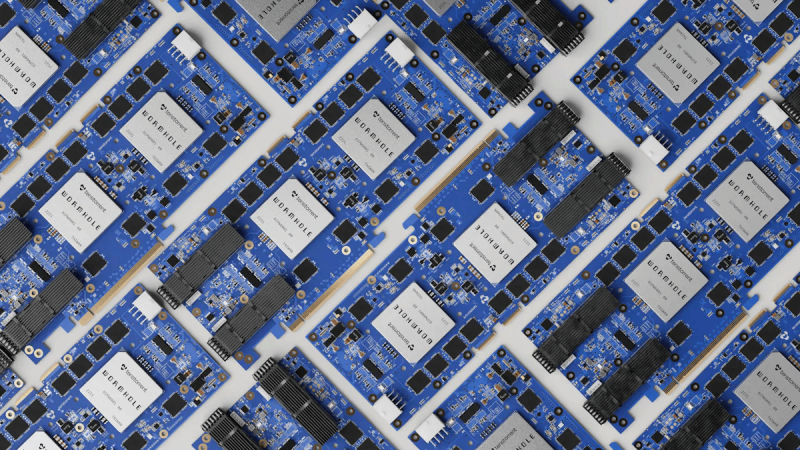

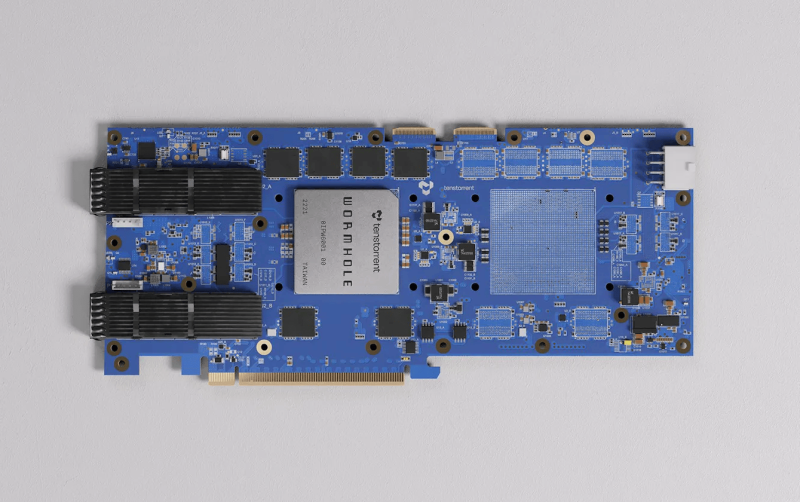

Tenstorrent начала продажи ИИ-ускорителей Wormhole и рабочие станции на их основеКанадский стартап Tenstorrent приступил к выпуску ИИ-чипов Wormhole. В настоящее время стартап предлагает построенные на них ИИ-ускорители Wormhole n150 и n300, а также рабочие станции TT-LoudBox и TT-QuietBox на их базе. ИИ-ускорители Wormhole n150 и n300 представляют собой двухслотовые FHFL-карты (PCIe 4.0 x16): n150 с одним чипом Wormhole, n300 — с двумя. Wormhole n150 и n300 имеют пассивное охлаждение и теплопакет 160 Вт и 300 Вт соответственно. Процессоры Wormhole были разработаны в 2021 году, но их внедрение происходит только сейчас. Это второе поколение ИИ-ускорителей Tenstorrent, которые придут на смену Grayskull. Wormhole n150 оснащён 72 ядрами Tensix, каждое из которых включает пять ядер RISC-V, поддерживающих различные форматы данных, и 108 Мбайт SRAM — вместе они предоставляют до 262 Тфлопс (FP8). Ускоритель также оснащён 12 Гбайт памяти GDDR6 с ПСП 288 Гбайт/с. У Wormhole n300 таких ядер 128, а частота также равна 1 ГГц. Объём SRAM составляет 192 Мбайт, а внешняя подсистема памяти включает 24 Гбайт GDDR6 с ПСП 576 Гбайт/с. Ускоритель обеспечивает производительность до 466 Тфлопс (FP8). RISC-V ядра Tensix обладают аппаратной и программной поддержкой вертикального и горизонтального масштабирования — объединения множества ядер в единое целое как внутри одного узла, так и за его пределами с другими ядрами Tensix на нескольких чипах Wormhole. Именно эта функциональность, как надеется Tenstorrent, позволит ей отобрать долю рынка у NVIDIA. Впрочем, стоимость новинок тоже невелика: Wormhole n150 предлагается по цене $999, а n300 — за $1399. В рабочих станциях Tenstorrent четыре Wormhole n300 могут работать как один ускоритель, который с точки зрерния ПО выглядит как единый массив ядер Tensix. Впрочем, можно отдать по одному ускорителю каждому пользователю или же одновременно обрабатывать восемь разных ИИ-моделей, причём всё это без использования виртуализации. В состав рабочей станции TT-LoudBox помимо четырёх ускорителей n300 (суммарно восемь чипов Wormhole) входят два восьмиядерных процессора Intel Xeon 4309Y (Ice Lake-SP), 512 Гбайт RAM, NVMe-хранилище ёмкостью 4 Тбайт и пара портов 10 GbE. TT-LoudBox уже поступила в продажу по цене $12 тыс. Рабочая станция TT-QuietBox оснащена четырьмя Wormhole n300 и 16-ядерным AMD EPYC 8124P (Siena). Для отвода тепла от компонентов используется жидкостное охлаждение, а остальные характеристики идентичны TT-LoudBox. Устройство доступно для предзаказа по цене $15 тыс. с поставкой в течение 8–10 недель.

17.07.2024 [13:16], Сергей Карасёв

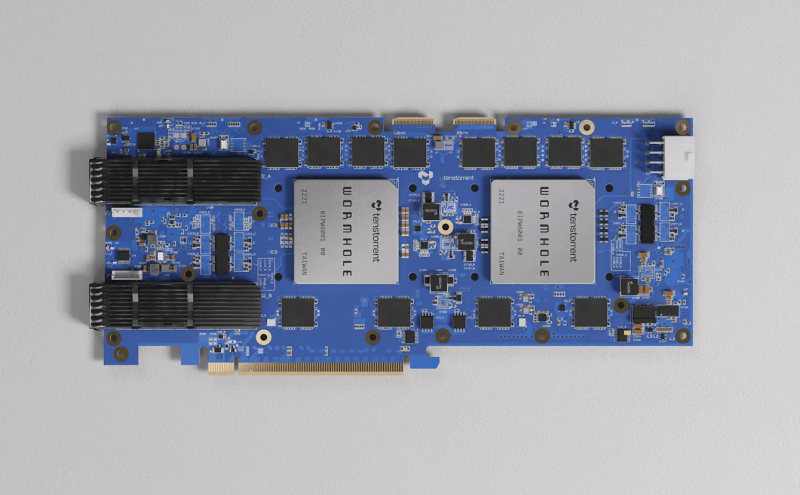

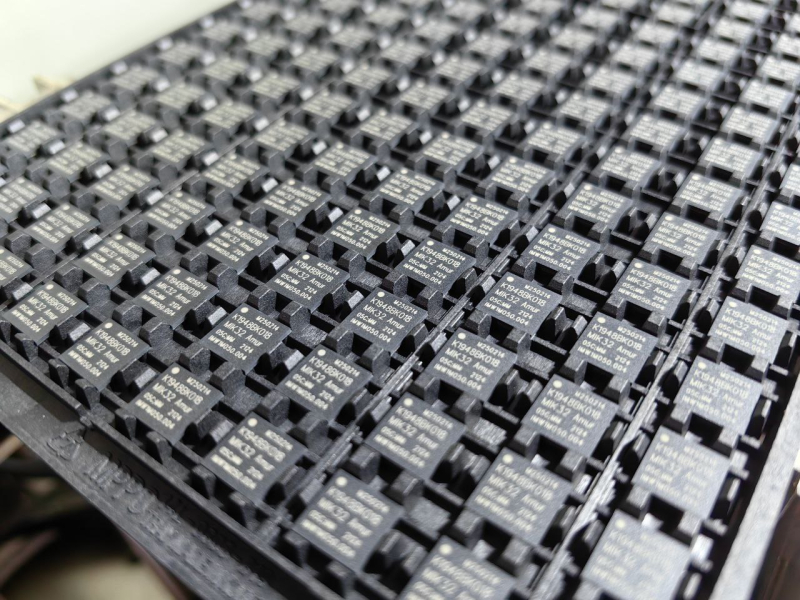

Microchip представила свои первые 64-бит чипы PIC64GX на архитектуре RISC-VКомпания Microchip Technology анонсировала изделия PIC64GX — своё первое семейство 64-бит чипов, выполненных на открытой архитектуре RISC-V. Среди ключевых сфер применения названы устройства для промышленного, автомобильного, коммуникационного, аэрокосмического и оборонного сегментов, а также для Интернета вещей. Первым представителем нового семейства стал чип PIC64GX1000. Он содержит четыре 64-битных ядра SiFive U54 (RV64GC) без внеочередного исполнения инструкций, но с блоком управления памятью (MMU). Тактовая частота достигает 625 МГц. Кроме того, присутствует вспомогательное ядро SiFive E51 RISC-V (RV64IMAC) с той же частотой, отвечающее за функции мониторинга. Чип может работать как в режиме SMP, так и AMP. Заявленный уровень производительности составляет порядка 5 тыс. DMIPS. Реализована подсистема кеша L1 с функциями коррекции ошибок Single-Error Correct, Double-Error Detect (SECDED). Объём кеша L2 с поддержкой SECDED составляет 2 Мбайт (SRAM). Все кеши можно переконфигурировать под свои нужды. Также есть 128 Кбайт энергонезависимой памяти для загрузчика и 56 Кбайт защищённой памяти для хранения пользовательских данных и ключей. Имеется встроенный 36-бит контроллер памяти (LP)DDR4-1333 (SECDED) с поддержкой до 32 Гбит на DDR-интерфейс. Реализована поддержка интерфейсов MMC 5.1, SD, SDIO, HDMI 1.4, MIPI CSI-2 (две линии), 2 × 1GbE, USB 2.0 OTG, PCIe 2.2 x4 (версия FCV) или x1 (модификация FCS), 2 × SPI, 5 × UART, 2 × I2C, 32 × GPIO, 2 × CAN. Средства обеспечения безопасности включают AES/SHA (256 бит), TRNG, HMAC, RSA, ECDSA. Доступны варианты упаковки FCSG325 (11 × 11 × 0,5 мм) c 200 контактами и FCVG484 (19 × 19 × 0,8 мм) с 244 контактами. Будут предлагаться коммерческая и индустриальная модификации: в первом случае диапазон рабочих температур простирается от 0 до +100 °C, во втором — от -40 до +100 °C.

16.07.2024 [22:32], Владимир Мироненко

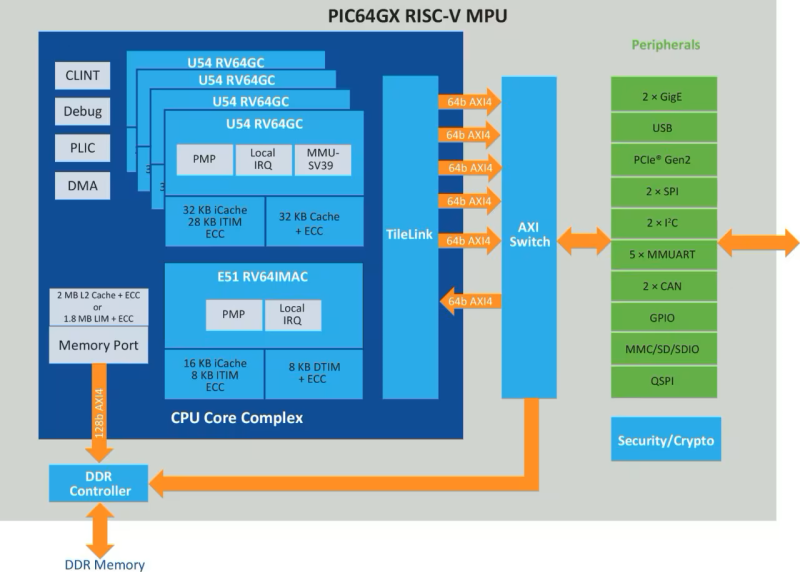

GS Group отгрузила 100 тыс. российских микроконтроллеров «MIK32 Амур» на базе RISC-V — ещё 400 тыс. на подходеПредприятие GS Nanotech из Калининграда, входящее в холдинг GS Group, сообщило о сборке и отгрузке по заказу АО «Микрон» стотысячной партии микроконтроллеров «MIK32 Амур» на открытой архитектуре RISC-V. По словам АО «Микрон», в связи с высоким спросом и в целях наращивания объёмов корпусирования изделий, дополнительно к собственному сборочному производству компания использует мощности предприятия GS Nanotech, которое в рамках соглашения до конца года соберёт в корпус до 0,5 млн микроконтроллеров «Амур». «Мы имеем большой опыт по корпусированию микроконтроллеров и рады применить его в сотрудничестве с нашим давним партнёром», — заявил вице-президент GS Group по развитию производства. Как сообщается, в ходе выполнения заказа GS Nanotech использовала опыт, накопленный ранее при крупносерийной сборке чипов в корпусах BGA, LGA, а также сложных многовыводных микросхем, в том числе по технологии SiP (системы-в-корпусе). Благодаря этому показатель выхода годной продукции составил 99,2 %. Также предприятием была разработана тестовая программа для контроля полного соответствия заявленным характеристикам микроконтроллеров. «MIK32 Амур» (К1949ВК018) представляет собой первый полностью отечественный 32-бит микроконтроллер с ядром на архитектуре RISC-V, который был разработан и производится в России ГК «Элемент» (разработка совместно с НИИМА «Прогресс», производство «Микрона»). Изделие включено в Единый реестр российской радиоэлектронной продукции (ПП РФ 878) и его производство не зависит от лицензируемой зарубежной интеллектуальной собственности.

06.07.2024 [21:58], Сергей Карасёв

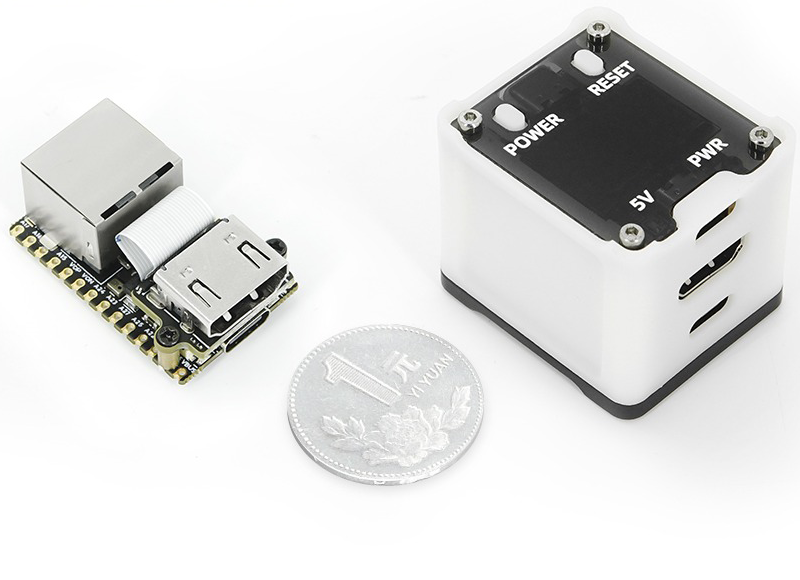

Sipeed представила Lichee NanoKVM — крошечный IP-KVM на базе RISC-V чипаКомпания Sipeed анонсировала изделие Lichee NanoKVM: это крошечное устройство удалённого управления IP-KVM (Keyboard, Video, Mouse). Его можно использовать для взаимодействия с рабочей станцией или иным устройством. В основу новинки положена миниатюрная плата для разработчиков LicheeRV Nano с размерами 22,86 × 35,56 мм. Она оснащена чипом Sophgo SG2002, который объединяет два ядра C906 с частотами 1000 и 700 МГц, одно ядро Arm Cortex-A53 с частотой 1000 МГц, а также контроллер 8051 с частотой от 25–300 МГц. В оснащение входят 256 Мбайт памяти DDR3 и NPU производительностью до 1 TOPS (INT8).

Источник изображения: Sipeed Устройство Lichee NanoKVM доступно в вариантах Lite и Full с размерами 23 × 37 × 15 мм и 40 × 36 × 36 мм соответственно. Оба варианта поддерживают передачу видеопотока вплоть до 1080p@60 (MJPEG, H.264), располагают 100MbE-интерфейсом RJ45, имеют поддержку IPMI и WoL, предлагают HTML5-интерфейс и умеют эмулировать USB- и CD-накопители. Lite-версия представляет собой крошечную плату с тремя разъёмами (RJ45, HDMI-вход, USB-C), к которой при желании можно подключить дополнительные интерфейсы. Full-модификация — это завершённое корпусированное изделие. Она оснащена OLED-дисплеем с диагональю 0,96" (128 × 64), который отображает IP-адрес, уровень загрузки CPU и параметры передаваемого видеопотока. Также на корпусе есть две кнопки (питание и сброс хоста) и два индикатора, один из которых дублирует состояние индикатора питания хоста, а второй указывает на наличие питания у самого NanoKVM. У Full-версии помимо основного порта USB-C для эмуляции HID-мыши/клавиатуры и накопителей есть ещё два таких же порта. Один позволяет запитать NanoKVM от внешнего источника, чтобы не полагаться на питание от самого хоста. Второй предназначен для платы-адаптера, которая позволяет подключиться к ATX-портам на материнской плате хоста. В будущем также станет доступен порт для подключения последовательного интерфейса, а также опции Wi-Fi и PoE. Приём заказов на Lichee NanoKVM уже начался. Модификация Lite оценена в $20, тогда как вариант Full стоит в два раза дороже.

01.07.2024 [12:35], Сергей Карасёв

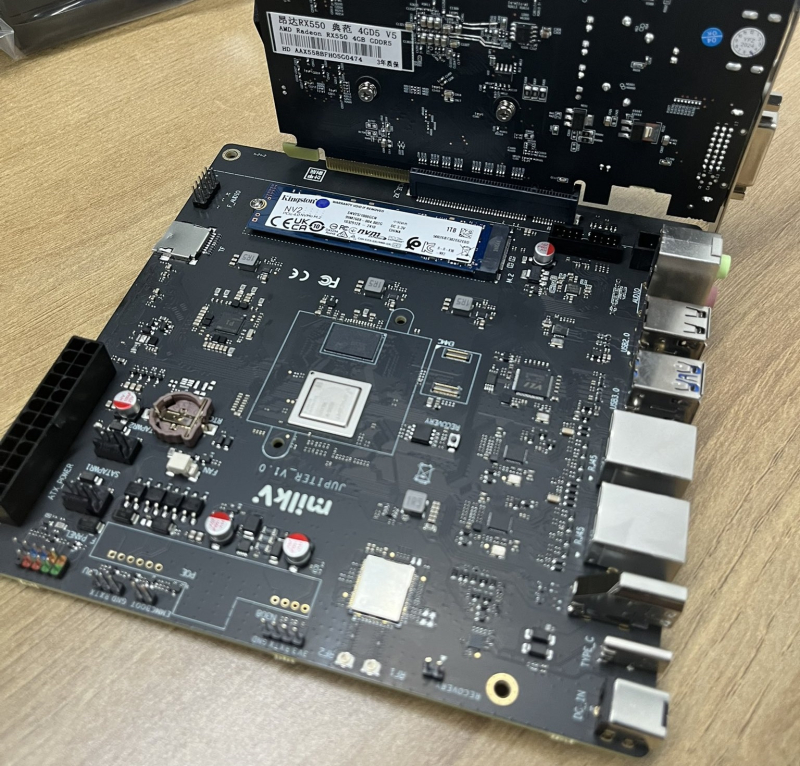

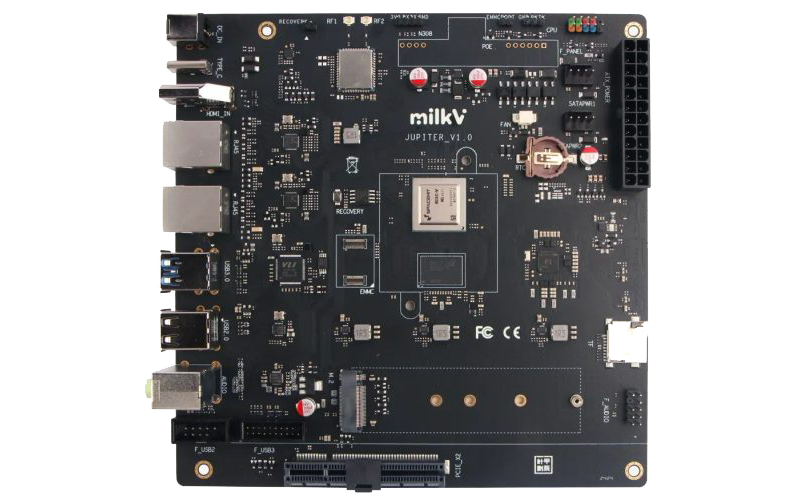

Mini-ITX плата Milk-V Jupiter получила чип RISC-V с восемью ядрамиКомпания Shenzhen MilkV Technology (Milk-V), по сообщению ресурса Liliputing, подготовила к выпуску плату под названием Jupiter, оснащённую процессором на архитектуре RISC-V. Новинка имеет типоразмер Mini-ITX, благодаря чему совместима с разнообразными существующими корпусами. Габариты изделия составляют 170 × 170 мм. В зависимости от модификации применяется процессор SpacemiT K1 или M1 с восемью ядрами SpacemiT X60 на базе RISC-V. В состав чипа входят графический ускоритель Imagination BXE-2-32 и нейропроцессорный модуль (NPU) с производительностью до 2 TOPS. Объём оперативной памяти LPDDR4x может составлять 4, 8 или 16 Гбайт (напаяна на плату, что исключает возможность апгрейда).

Источник изображения: Liliputing Доступны коннектор для SSD формата M.2 2280 с интерфейсом PCIe 2.0 x2 и слот для карты microSD. Кроме того, может быть добавлен чип eMMC. Есть также слот PCIe 2.0 х8 для карт расширения, например, GPU или дополнительных SSD. Поддерживается беспроводная связь Wi-Fi 6 и Bluetooth 5.2. Набор разъёмов включает порты USB 2.0 Type-C, USB 3.0 Type-A (×2) и USB 2.0 Type-A (×2), интерфейс HDMI (до 1920 × 1440 пикселей; 60 Гц), 3,5-мм аудиогнёзда (аудиовыход, вход для микрофона), два коннектора RJ-45 для сетевых кабелей (адаптер 1GbE), DC-гнездо для подачи питания (12 В). Через разъёмы на самой плате также можно задействовать по два дополнительных порта USB 3.0 и USB 2.0. Среди прочего упомянуты коннектор RTC для батарейки стандарта CR1220 и разъём для подключения вентилятора с ШИМ-управлением. Опционально доступна поддержка технологии PoE.

29.06.2024 [12:52], Сергей Карасёв

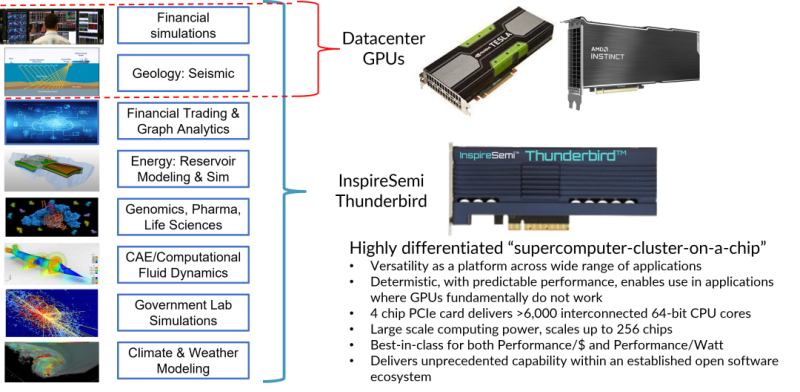

ИИ-ускоритель InspireSemi Thunderbird объединяет 6144 ядра RISC-V на карте PCIeКомпания InspireSemi объявила о разработке чипа Thunderbird на открытой архитектуре RISC-V для ИИ-нагрузок. Это изделие легло в основу специализированной карты расширения с интерфейсом PCIe, которая, как утверждается, подходит для решения широкого спектра задач. Чип Thunderbird содержит 1536 кастомизированных 64-битных суперскалярных ядер RISC-V, а также высокопроизводительную память SRAM. Говорится о наличии ячеистой сети с малой задержкой для меж- и внутричиповых соединений. Кроме того, предусмотрены блоки ускорения определённых алгоритмов шифрования. Идея заключается в том, чтобы объединить универсальность и возможности программирования традиционных CPU с высокой степенью параллелизма GPU. Изделие ориентировано на НРС-приложения, но при этом поддерживает исполнение программ общего назначения. InspireSemi называет новинку «суперкомпьютерным кластером на кристалле». Точно так же назвала свои ИИ-ускорители Esperanto Technologies. Именно её чипы ET-SoC-1, по-видимому, впервые объединили более 1 тыс. ядер RISC-V. Впрочем, сама Esperanto позиционировала их как гибкие и энергоэффективные решения для инференса. В случае Thunderbird четыре могут быть объединены на одной карте PCIe, что в сумме даёт 6144 ядра RISC-V. Более того, заявлена возможность масштабирования до 256 чипов, связанных с помощью высокоскоростных трансиверов. Таким образом, количество ядер может быть доведено до 393 216. Чип обеспечивает производительность до 24 Тфлопс (FP64) при энергетической эффективность 50 Гфлопс/Вт. Для сравнения: NVIDIA A100 обладает быстродействием 19,5 Тфлопс (FP64), а NVIDIA H100 — 67 Тфлопс (FP64). Суперскалярные ядра поддерживают векторные и тензорные операции и форматы данных с плавающей запятой смешанной точности. Однако о совместимости с Linux ничего не говорится. Среди возможных областей применения названы ИИ, НРС, графовый анализ, блокчейн, вычислительная гидродинамика, сложное моделирование в области энергетики, изменений климата и пр. |

|