Материалы по тегу: risc-v

|

04.02.2024 [21:02], Сергей Карасёв

Meta✴ намерена активно внедрять собственные ИИ-ускорители Artemis (MTIA) в качестве альтернативы решениям NVIDIA и AMDВ 2024 году компания Meta✴, по сообщению The Register, после многих лет разработки может начать массовое внедрение собственных ИИ-чипов. Они станут альтернативой ускорителям NVIDIA и AMD, что поможет снизить зависимость от продукции сторонних поставщиков. В 2024 году компания намерена потратить до $37 млрд на развитие своей инфраструктуры. В настоящее время для поддержания ИИ-нагрузок Meta✴ применяет такие решения, как NVIDIA H100. Ожидается, что к концу 2024 года компания будет иметь в своём распоряжении 350 тыс. этих ускорителей. Вместе с тем Meta✴ проявляет интерес и к изделиям AMD Instinct MI300. Ранее компания высоко оценила возможности Qualcomm Cloud AI 100, но отказалась от них из-за несовершенства ПО. Не приглянулись Meta✴ и чипы Esperanto. Сейчас Meta✴ ведёт разработку собственных ИИ-ускорителей.

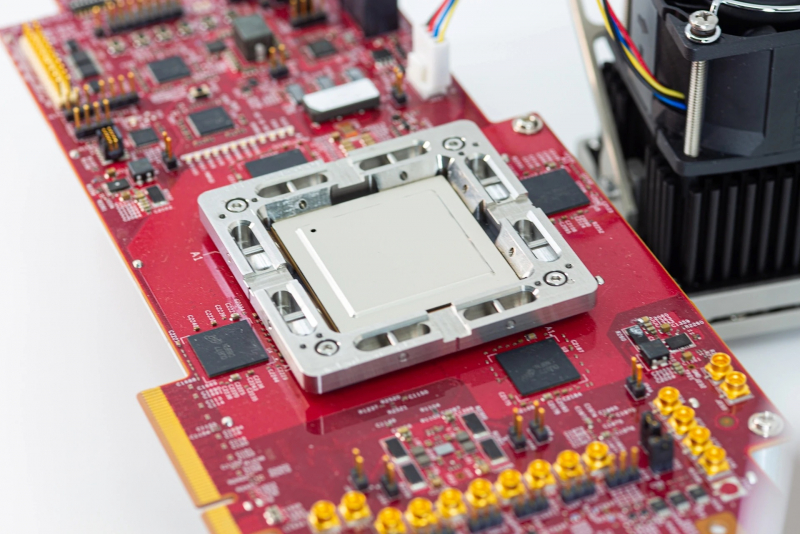

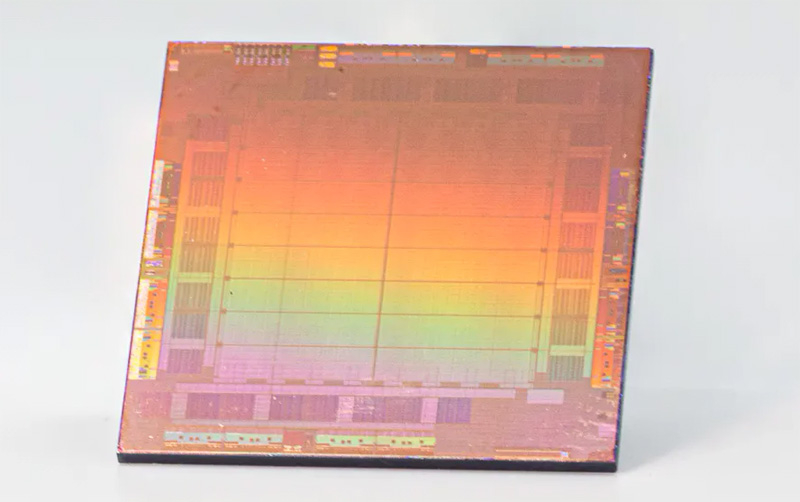

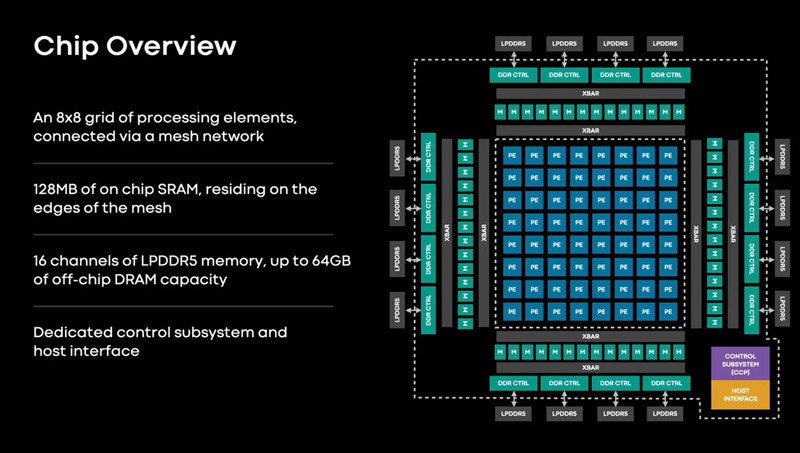

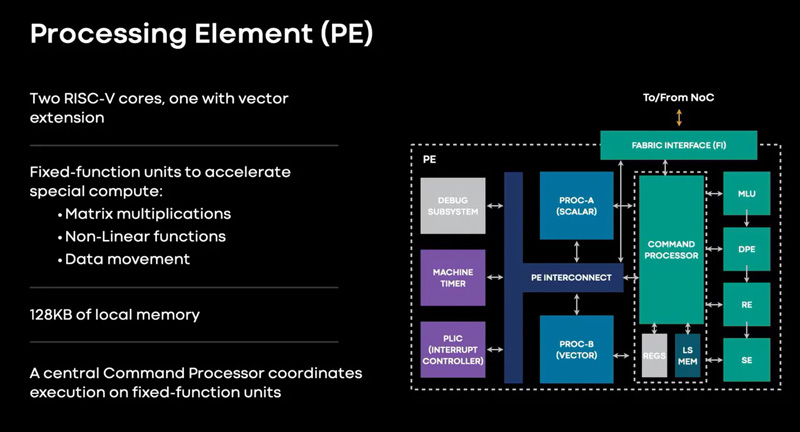

Источник изображения: Meta✴ Весной 2023 года стало известно, что компания создала свой первый ИИ-процессор. Чип под названием MTIA (Meta✴✴ Training and Inference Accelerator; на изображении) представляет собой ASIC в виде набора блоков, функционирующих в параллельном режиме. Задействованы 64 вычислительных элемента в виде матрицы 8 × 8, каждый из которых объединяет два ядра с архитектурой RISC-V. Конструкция включает 128 Мбайт памяти SRAM, а также до 64/128 Гбайт памяти LPDDR5. Показатель TDP равен 25 Вт. Заявленная производительность на операциях INT8 достигает 102,4 TOPS, на операциях FP16 — 51,2 Тфлопс. Процессор производится по 7-нм технологии TSMC.

Источник изображения: Meta✴ Как теперь сообщается, в 2024-м Meta✴ намерена начать активное использование собственных ИИ-ускорителей с кодовым именем Artemis. В их основу лягут компоненты MTIA первого поколения. Чип Artemis, оптимизированный для инференса, будет применяться наряду с ускорителями сторонних поставщиков. При этом, как отметили представители компании, изделия Artemis обеспечат «оптимальное сочетание производительности и эффективности при рабочих нагрузках, специфичных для Meta✴».

Источник изображения: Meta✴ Компания пока не раскрывает ни архитектуру Artemis, ни конкретные рабочие нагрузки, которые будет поддерживать чип. Участники рынка полагают, что Meta✴ будет запускать готовые ИИ-модели на собственных специализированных ASIC, чтобы высвободить ресурсы ускорителей для развивающихся приложений. По данным SemiAnalysis, Artemis получит улучшенные ядра, а компоненты LPDDR5 уступят место более быстрой памяти, использующей технологию TSMC CoWoS. Нужно добавить, что Amazon и Google уже несколько лет используют собственные чипы для ИИ-задач. Например, Amazon недавно ИИ-ускорители Trainium2 и Inferenetia2, тогда как Google в 2023 году представила сразу два новых ускорителя: Cloud TPU v5p и TPU v5e. А Microsoft сообщила о создании ИИ-ускорителя Maia 100.

09.11.2023 [03:15], Алексей Степин

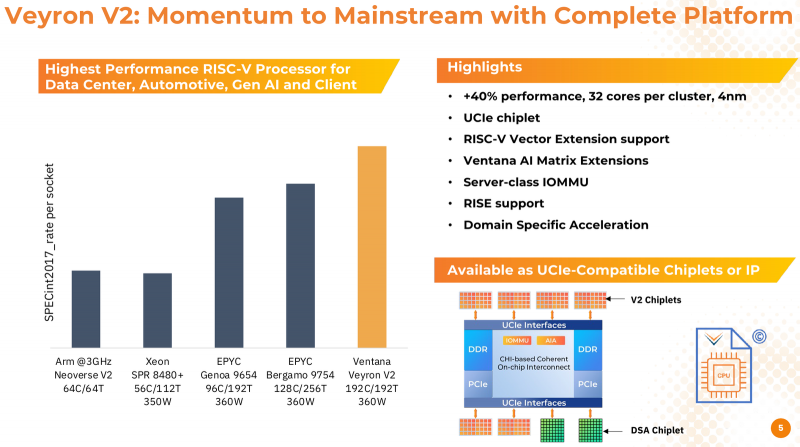

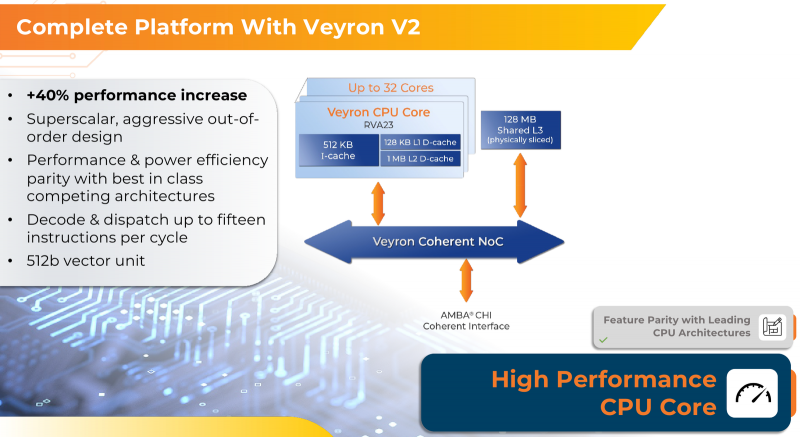

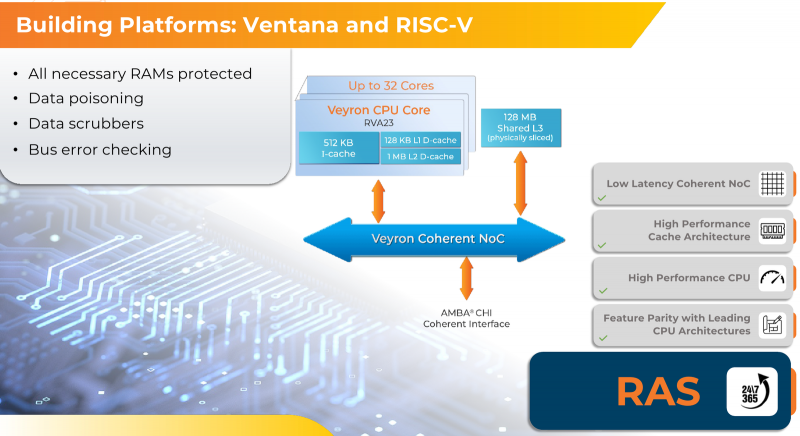

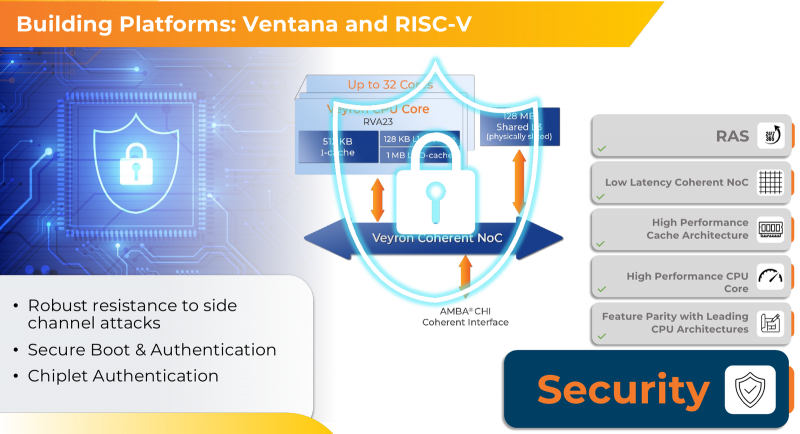

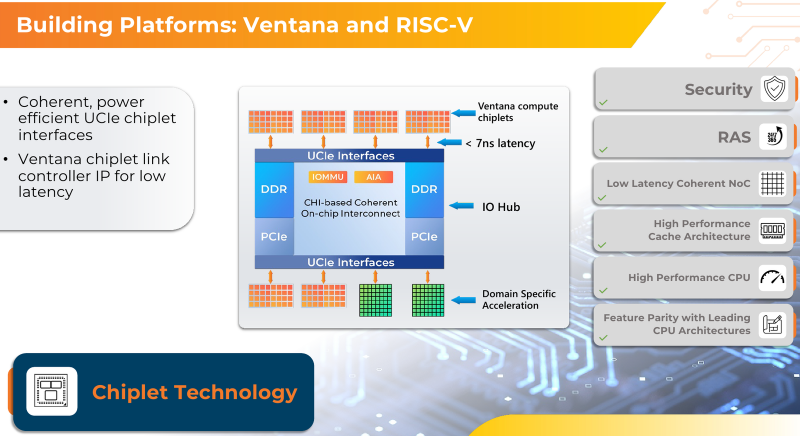

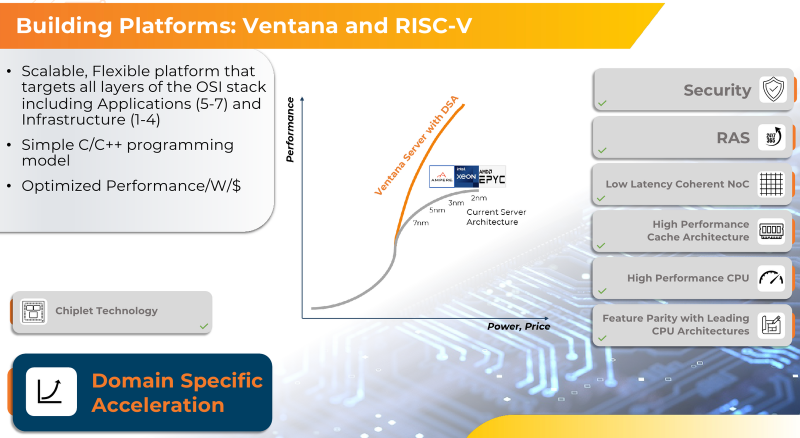

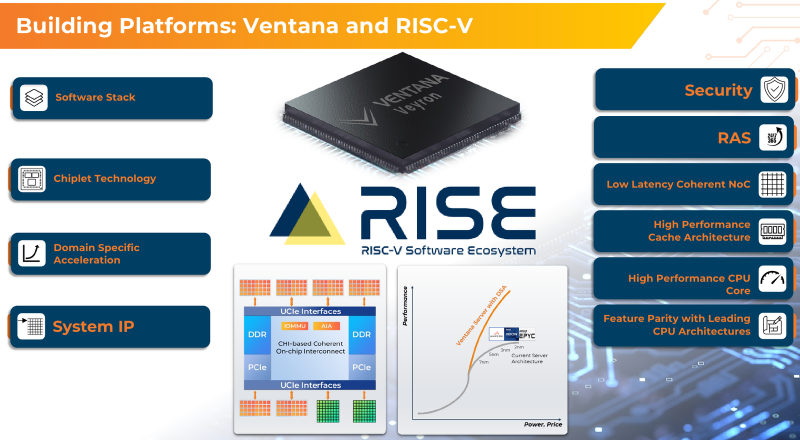

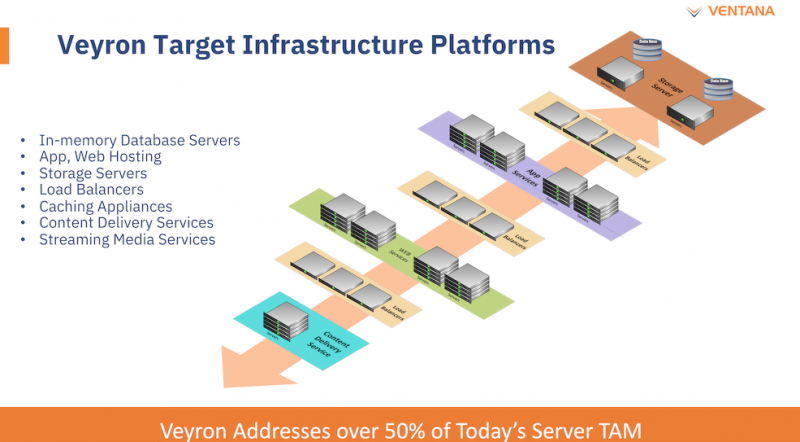

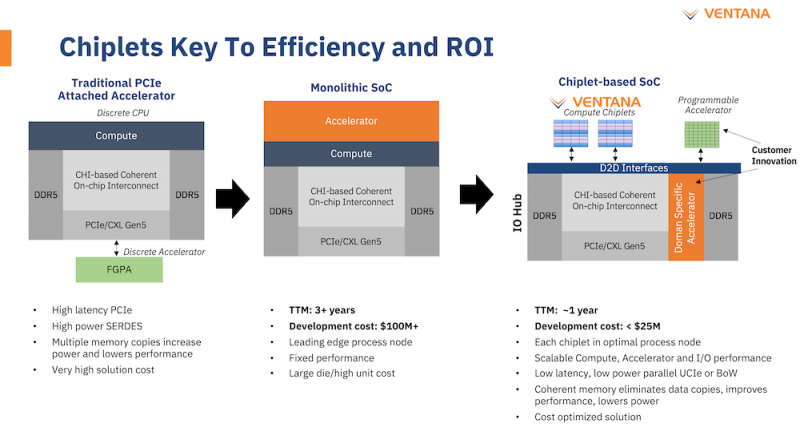

RISC-V с приправой: модульные 192-ядерные серверные процессоры Ventana Veyron V2 можно дополнить ускорителямиВ 2022 года компания Ventana Micro Systems анонсировала первые по-настоящему серверные RISC-V процессоры Veyron V1. Анонс чипов, обещающих потягаться на равных с лучшими x86-процессорами с архитектурой x86, прозвучал громко. Популярности, впрочем, Veyron V1 не снискал, но на днях компания анонсировала второе поколение чипов Veyron V2, более полно воплотившее в себе принципы модульного дизайна и получившее ряд усовершенствований. Как и в первом поколении, компания-разработчик продолжает придерживаться концепции «процессора-конструктора» с чиплетным дизайном. В центре 4-нм Veyron V2 по-прежнему лежит I/O-хаб на базе AMBA CHI, охватывающий контроллеры памяти и шины PCI Express, а также блоки IOMMU и AIA. К нему посредством интерфейса UCIe подключаются вычислительные чиплеты. Латентность UCIe-подключения составляет менее 7 нс.

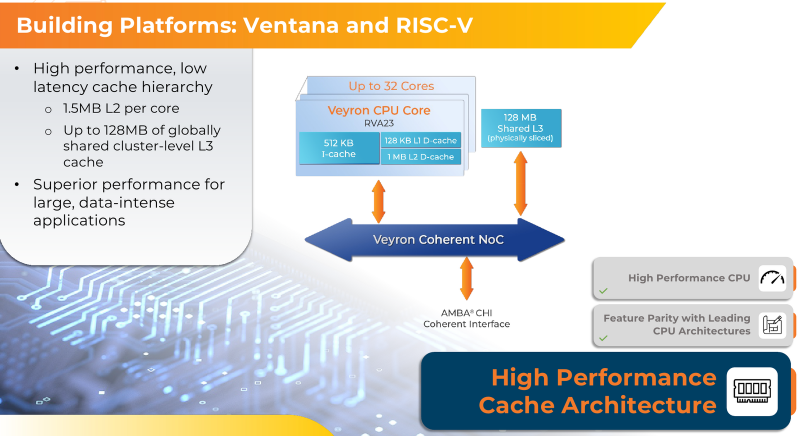

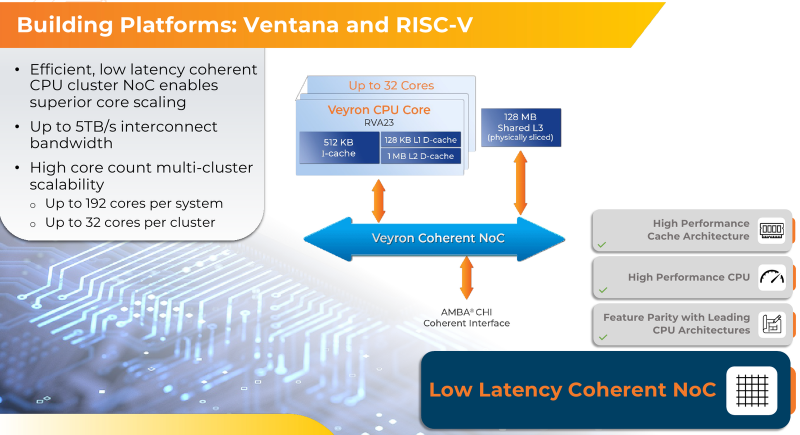

Источник изображений здесь и далее: Ventana Micro Systems Чиплеты эти могут быть разных видов: либо с ядрами общего назначения (по 32 ядра на чиплет), образующие собственно процессор Veyron V2, либо содержащие специфические сопроцессоры под конкретную задачу (domain-specific acceleration, DSA). Последние могуть быть представлены FPGA, ИИ-ускорителями и т.д. Более того, Ventana по желанию заказчика может оптимизировать и I/O-хаб для повышения эффективности работы ядер CPU с сопроцессорами. В классическом варианте Veyron V2 может иметь до шести чиплетов с RV64GC-ядрами V2, что в сумме даёт 192 ядра. Поддержка SMT отсутствует. Удельная производительность в пересчёте на ядро получается несколько ниже, чем у AMD Zen 4c, но согласно результатам тестов, предоставленных Ventana, 192-ядерный Veyron V2 заметно опережает AMD EPYC Bergamo 9754 (128C/256T) при аналогичном теплопакете в 360 Вт. Столь неплохой результат достигнут за счёт оптимизации архитектуры Veyron: по сравнению с первым поколением говорится о 40 % прибавке производительности. Что немаловажно, во втором поколении процессоров Veyron была реализована поддержка 512-бит векторных расширений, фирменных матричных расширений, а также целого ряда других спецификаций. В целом ради совместимости разработчики предпочли остаться в рамках общего профиля RVA23. Сами ядра V2 используют суперскалярный дизайн с агрессивным внеочередным исполнением и продвинутым предсказанием ветвлений. Возможно декодирование и обработка до 15 инструкций за такт. Объём L1-кешей составляет 512 Кбайт для инструкций и 128 Кбайт для данных, дополнительно каждое ядро имеет свой кеш L2 объёмом 1 Мбайт. Общий для всего 32-ядерного чиплета L3-кеш имеет объём 128 Мбайт. Производительность внутренней когерентной шины составляет до 5 Тбайт/с. Позиционируемый в качестве решения для гиперскейлеров, крупных ЦОД и HPC, Veyron V2 имеет развитые средства предотвращения ошибок и защиты данных, от ECC-кешей и поддержки Secure Boot до аутентификации на уровне чиплета и продвинутых RAS-функций. Кроме того, реализована защита от атак по сторонним каналам. Несмотря на то, что мир RISC-V пока ещё похож на «Дикий Запад», Ventana старается опираться на развитые и популярные стандарты: в частности, это выражается в применении UCIe для подключения чиплетов, поддержку гипервизоров первого и второго типа, вложенную виртуализацию и совместимость с программной экосистемой RISC-V RISE. Подход Ventana позволит избежать недостатков, свойственных дискретным PCIe-ускорителям (высокая латентность, энергопотребление и стоимость) и сложным монолитным SoC (очень высокая стоимость разработки и сроки), снизить время и стоимость стоимость новых решений, а также обеспечить более низкий уровень энергопотребления. В общем, компания явно целится в гиперскейлеров. Видение сценариев применения DSA у Ventana очень широкий — от БД-ускорителей и блоков компрессии-декомпрессии данных до поддержки специфических алгоритмов в задачах аналитики и транскодеров в системах доставки контента. Также становятся ненужными дискретные DPU. Первым партнёром Ventana стала Imagination Technologies, крупный разработчик GPU. В качестве вариантов физической реализации новой платформы Ventana предлагает компактный 1U-сервер, содержащий один чип Veyron V2 со 192 ядрами, работающими на частотах до 3,6 ГГц, и 12 каналами DDR5-5600. Вероятнее всего, производителем новой платформы станет GIGABYTE. Ожидать первых поставок следует не ранее II квартала 2024 года. В целом, видение высокопроизводительной модульной платформы, продвигаемое Ventana, выглядит перспективно, а упор на применение DSA может выгодно отличать её большинства Arm-серверов, конкурирующих с решениями Intel/AMD лоб в лоб. Вопрос лишь в поддержке со стороны разработчиков программного обеспечения — и здесь может сыграть ставка разработчиков на максимально открытые, широкие стандарты.

29.09.2023 [13:15], Сергей Карасёв

InnoGrit начала массовый выпуск первого китайского контроллера PCIe 5.0 для серверных SSDКитайская компания Yingren Technology (InnoGrit), по сообщению ресурса Tom's Hardware, организовала массовое производство первого в стране контроллера PCIe 5.0, предназначенного для создания SSD корпоративного класса. Изделие получило обозначение YR S900. Новинка представляет собой четырехканальный контроллер SSD, основанный на архитектуре RISC-V. Выбор RISC-V объясняется в том числе напряжёнными отношениями между США и КНР: в данном случае на изделие не смогут распространяться экспортные ограничения. О типе применённой технологии производства ничего не сообщается. Известно, что контроллер обеспечивает полную поддержку протокола NVMe 2.0. Заявленная скорость последовательного чтения достигает 14 Гбайт/с, последовательной записи — 12 Гбайт/с. Показатель IOPS при произвольных чтении и записи составляет до 3,5 и 2,5 млн соответственно. Контроллер может применяться в 16- и 18-канальной конфигурации.

Источник изображения: Yingren Technology YR S900 наделён процессором ECC третьего поколения для оптимизации кодирования и декодирования 4K LDPC. По заявлению компании, использование решения вместе с новой гибридной адаптивной функцией коррекции ошибок ECC позволяет поднять производительность памяти TLC и QLC NAND. А при работе с Kioxia XL-Flash показана задержка произвольного чтения 4K на уровне 10 мкс. Среди прочего упомянута поддержка FDP (Flexible Data Placement), SR-IOV, CMB (Controller Memory Buffer), а также различных алгоритмов шифрования.

01.08.2023 [10:02], Сергей Карасёв

Esperanto готовит универсальный чип ET-SoC-2 на базе RISC-V для задач НРС и ИИСтартап Esperanto Technologies, по сообщению ресурса HPC Wire, готовит новый чип с архитектурой RISC-V, ориентированный на системы высокопроизводительных вычислений (НРС) и задачи ИИ. Изделие получит обозначение ET-SoC-2. Нынешний чип ET-SoC-1 объединяет 1088 энергоэффективных ядер ET-Minion и четыре высокопроизводительных ядра ET-Maxion. Решение предназначено для инференса рекомендательных систем, в том числе на периферии. Чип ET-SoC-2 будет включать в себя новые высокопроизводительные ядра CPU на базе RISC-V с векторными расширениями. Точные данные о производительности не раскрываются, но говорится, что изделие обеспечит быстродействие с двойной точностью более 10 Тфлопс. Архитектура ET-SoC-2 предполагает совместную работу сотен и тысяч чипов для организации платформ НРС. При этом Esperanto делает упор на энергетической эффективности своих решений.

Источник изображения: Esperanto Technologies По словам Дейва Дитцеля (Dave Ditzel), генерального директора Esperanto, чипы RISC-V смогут взять на себя функции и CPU, и GPU при обработке ресурсоёмких приложений, в частности, машинного обучения. Процессоры RISC-V отстают по производительности от чипов x86 и Arm, хотя разрыв постепенно сокращается. Дитцель сказал, что стойки с чипами ET-SoC-1 могут обеспечить производительность в петафлопсы. Однако проблема с внедрением RISC-V заключается в слабо развитой экосистеме ПО.

19.05.2023 [10:20], Сергей Карасёв

Meta✴ представила ИИ-процессор MTIA для дата-центров — 128 ядер RISC-V и потребление всего 25 ВтMeta✴ анонсировала свой первый кастомизированный процессор, разработанный специально для ИИ-нагрузок. Изделие получило название MTIA v1, или Meta✴ Training and Inference Accelerator: оно оптимизировано для обработки рекомендательных моделей глубокого обучения. Проект MTIA является частью инициативы Meta✴ по модернизации архитектуры дата-центров в свете стремительного развития ИИ-платформ. Утверждается, что чип MTIA v1 был создан ещё в 2020 году. Это интегральная схема специального назначения (ASIC), состоящая из набора блоков, функционирующих в параллельном режиме.

Источник изображений: Meta✴ Известно, что при производстве MTIA v1 используется 7-нм технология. Конструкция включает 128 Мбайт памяти SRAM. Чип может использовать до 64/128 Гбайт памяти LPDDR5. Задействован фреймворк машинного обучения Meta✴ PyTorch с открытым исходным кодом, который может применяться для решения различных задач в области компьютерного зрения, обработки естественного языка и пр.  Процессор MTIA v1 имеет размеры 19,34 × 19,1 мм. Он содержит 64 вычислительных элемента в виде матрицы 8 × 8, каждый из которых объединяет два ядра с архитектурой RISC-V. Тактовая частота достигает 800 МГц, заявленный показатель TDP — 25 Вт. Meta✴ признаёт, что у MTIA v1 присутствуют «узкие места» при работе с ИИ-моделями большой сложности: требуется оптимизация подсистем памяти и сетевых соединений. Однако в случае приложений низкой и средней сложности платформа, как утверждается, обеспечивает более высокую эффективность по сравнению с GPU.  В дальнейшем в семействе MTIA появятся более производительные изделия, но подробности о них не раскрываются. Ранее говорилось, что Meta✴ создаёт некий секретный чип, который подойдёт и для обучения ИИ-моделей, и для инференса: это решение может увидеть свет в 2025 году.

27.01.2023 [23:32], Владимир Мироненко

На фоне колоссальных потерь прибыли Intel отказалась от развития коммутаторов и по-тихому закрыла программу Pathfinder для RISC-VКомпания Intel опубликовала итоги работы в IV квартале 2022 года, окончившемся 31 декабря и принёсшем ей значительные убытки. Выручка компании составила $14,04 млрд, что на 32 % ниже результата за аналогичный период предыдущего года, а также меньше прогноза аналитиков. Intel завершила квартал с чистыми убытками в размере $661 млн (GAAP), в то время как годом ранее её квартальная прибыль составила $4,62 млрд. В IV квартале группа клиентских решений Intel Client Computing Group (CCG) принесла доход в размере $6,63 млрд, что на 36 % ниже результата IV квартала 2021 года. Как сообщает Intel, падение спроса на ПК в основном коснулось потребительского и образовательного рынков, и клиенты решили сократить запасы на складах. По данным Gartner, рынок ПК за отчётный период сократился сильнее, чем в любом другом квартале, с тех пор как компания начала проводить мониторинг отрасли в 1990-х годах.

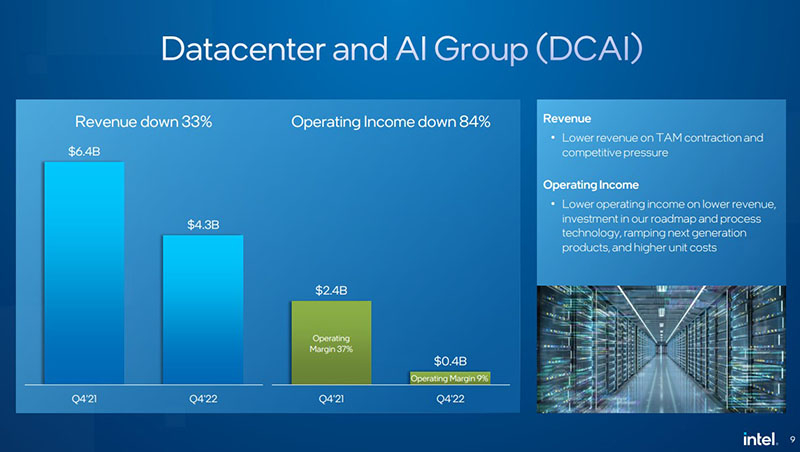

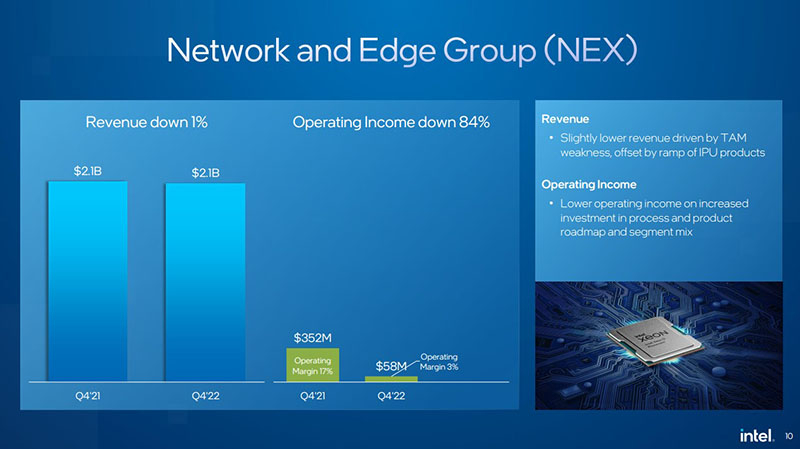

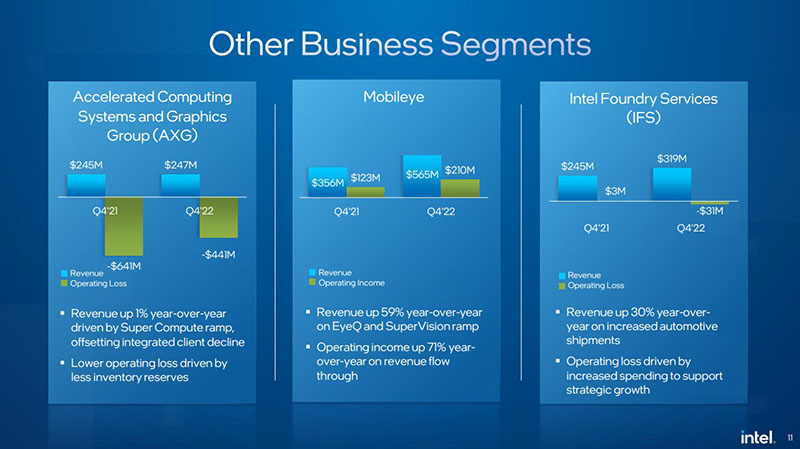

Источник изображений: Intel Группа Datacenter and AI Group (DCAI), которая отвечает за решения для ЦОД и платформы ИИ, принесло компании за квартал доход в размере $4,3 млрд, что на 33 % меньше прошлогоднего, но все же больше прогноза аналитиков. Intel объяснила результат давлением со стороны конкурентов и сокращением размера рынка. Как отметил ресурс The Register, несмотря на запуск в начале этого месяца чипов Xeon Sapphire Rapids (это первые новые CPU для ЦОД от Intel почти за два года), они только сейчас начали поступать к клиентам, включая Dell, Google Cloud, HPE, Lenovo, NVIDIA, Supermicro. То есть Intel вряд ли получит достаточно большую выручку от их реализации в этом квартале. Заодно компания решила не строить лабораторию по развитию решений для ЦОД. Всё это сыграет на руку AMD.  Группа Network and Edge Group (NEX), специализирующаяся на сетевых продуктах и периферийных вычислениях, тоже продемонстрировало признаки замедления спроса в IV квартале. Выручка группы снизилась на 1 % в годовом исчислении (до $2,1 млрд), что означает отход от тенденции к росту, о котором она сообщала в предыдущие кварталы. Впрочем, у группы в финансовом году отмечен рост дохода на 11 %. Тем не менее, компания решила фактически избавиться от бизнеса по производству коммутаторов, хотя всего несколько лет назад она инвестировала в это направление и купила Barefoot Networks. Intel сохранит поддержку текущих решений Tofino, но в дальнейшем сосредоточится на развитии IPU. При этом нельзя не отметить, что коммутаторы являлись важной частью будущей экосистемы IPU/DPU.  Положительным моментом для Intel в IV квартале 2022 года является то, что более мелкие подразделения компании показали рост. Выручка подразделения Accelerated Computing Systems and Graphics (AXG), занимающегося разработкой ускорителей, увеличило выручку на 1 % до $247 млн, а также сократило операционные убытки. Подразделение Mobileye, поставщик решений для автономного вождения, которое недавно провело IPO, принесло компании $565 млн, что больше прошлогоднего результата на 59 %. У подразделения Intel Foundry Services выручка в IV квартале выросла на 30 % до $319 млн. При этом компания без объявления закрыла программу Pathfinder for RISC-V. Кроме того, в 2022 году Intel отказалась от развития 3D XPoint/Optane.  Если говорить о результатах за год, то общая выручка Intel снизилась на 20 % (до $63,1 млрд), это привело к падению чистой прибыли на 60 % (до $8 млрд). В частности, выручка группы DCAI упала на 15 % (до $19,2 млрд), группа NEX принесла компании $8,9 млрд, что на 11 % меньше, чем в предыдущем году. Клиентская группа CCG сократила выручку в годовом исчислении на 23 % (до $31,7 млрд). Согласно прогнозу Intel, в I квартале 2023 года выручка будет примерно на 40 % ниже, чем в I квартале 2022 года, в пределах от $10 до $11,5 млрд. Валовая прибыль Intel будет находиться на уровне 39 %.

13.12.2022 [21:52], Алексей Степин

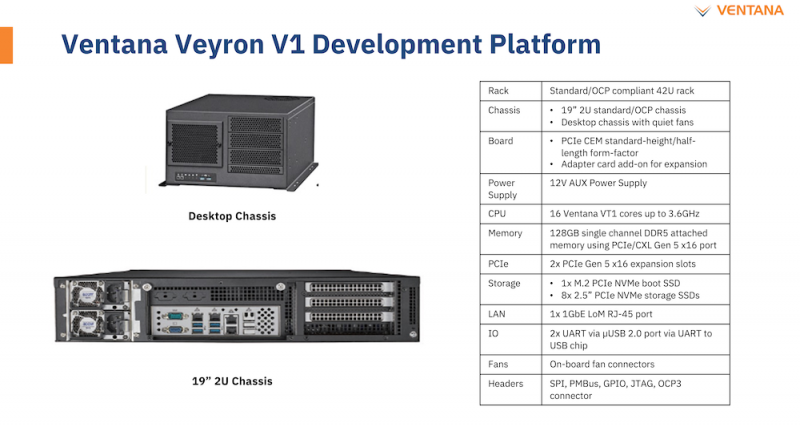

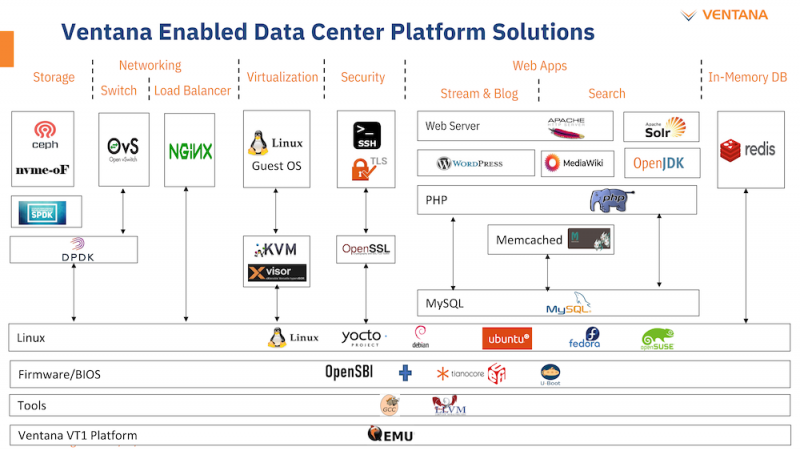

Ventana анонсировала первый по-настоящему серверный RISC-V процессор Veyron V1: 192 ядра с частотой 3,6 ГГцАрхитектура RISC-V достаточно молода и обычно ассоциируется с экономичными чипами на платах, подобных Raspberry Pi. Однако технически она позволяет создавать и мощные процессоры, способные поспорить с лучшими решениями на базе архитектур Arm и x86. На саммите RISC-V компания Ventana Micro Systems анонсировала целое семейство высокопроизводительных процессоров, первенцем в котором стал чип Veyron V1, который, по словам разработчиков, сможет потягаться в однопоточной производительности с самыми современными CPU класса High-End. Новинка нацелена на рынок гиперскейлеров, причём благодаря чиплетному дизайну новый процессор изначально разрабатывался как кастомизируемый под задачи заказчика. Veyron V1 будет предлагаться в виде своеобразного набора-конструктора, включающего в себя один или несколько вычислительных чиплетов Veyron, I/O-хаба и интерконнекта, позволяющего связать все компоненты воедино. Это, по словам разработчиков, должно серьёзно ускорить и удешевить процесс внедрения новой процессорной платформы, снизив расходы на разработку чипов на 75 %, а время создания — до не более чем двух лет.

Платформа Veyron V1 универсальна и покрывает широкий спектр задач. Источник здесь и далее: StorageReview Вычислительный чиплет Veyron V1 использует продвинутые 64-битные ядра RISC-V и располагает 2 Мбайт кеша L2, а также многопоточным контроллером памяти. Предусмотрены конфигурации чиплета с 6, 8, 12 или 16 ядрами с частотой в районе 3 ГГц, что сопоставимо с решениями Google и AWS. Использоваться процессор может не только в ЦОД, но и в различных встраиваемых системах, базовых станциях 5G или даже клиентских рабочих станциях.

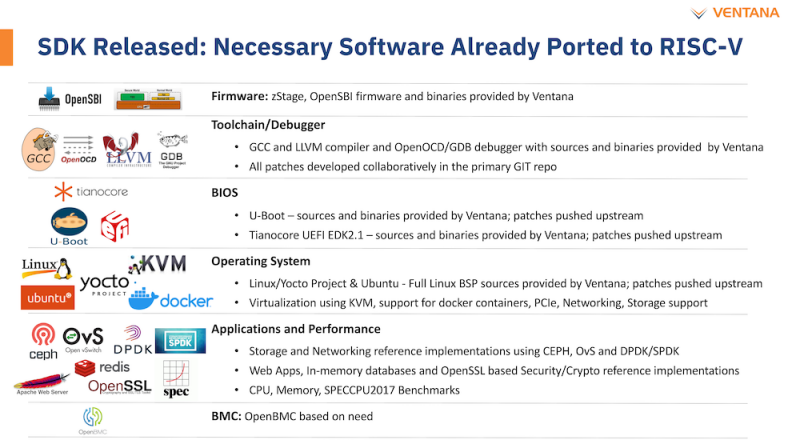

Чиплетная архитектура ускорит цикл разработки и внедрения, а также упростит задачу подключения кастомных ускорителей Архитектурно дизайн Veyron V1 использует агрессивный конвейер шириной восемь инструкций и с внеочередным исполнением. Чип способен работать на частоте до 3,6 ГГц благодаря использованию 5 нм техпроцесса TSMC. I/O-хаб может производиться с использованием более дешёвых 12 или даже 16-нм техпроцессов. Для соединения компонентов процессора разработан специальный низколатентный интерконнект D2D. Каждый чиплет включает в себя до 16 ядер, предусмотрена возможность масштабирования процессора до 192 ядер в 12 чиплетах. Общий объём разделяемого кеша L3 составляет 48 Мбайт. Заявлен высокий уровень защищённости архитектуры от атак по сторонним каналам. Разработчики заявляют о беспрецедентно низком энергопотреблении: 128 ядер V1 уложатся в 280 Вт; AMD EPYC 7763 потребляет столько же при вдвое меньшем числе ядер. Анонс Ventana нельзя назвать «бумажным» — компания говорит о доступности комплектов разработчика, причём сразу в двух типах шасси: в настольном и в серверном корпусе высотой 2U. Конфигурация включает в себя 16-ядерную версию V1, 128 гбайт памяти DDR5, подключенной с помощью интерфейса CXL (PCIe 5.0) x16, два свободных слота расширения PCIe 5.0 x16, загрузочный накопитель NVMe M.2 и 8 NVMe SFF SSD формата 2,5" для хранения данных. Для удалённого управления предусмотрен 1GbE-порт. Компания не забыла и о поддержке со стороны программного обеспечения: платформы разработчика Ventana Veyron V1 будут сопровождаться полноценным SDK с основным ПО, уже портированным на новую архитектуру. В список входят компиляторы GCC и LLVM, отладчик OpenOCD/GDB, исходные коды и бинарные файлы загрузчиков U-Boot и Tianocore UEFI EDK2.1. Поддерживается ряд дистрибутивов Linux, а также другое системное и прикладное ПО. Ожидается, что новые системы будут доступны в начале следующего года.

18.10.2022 [19:00], Сергей Карасёв

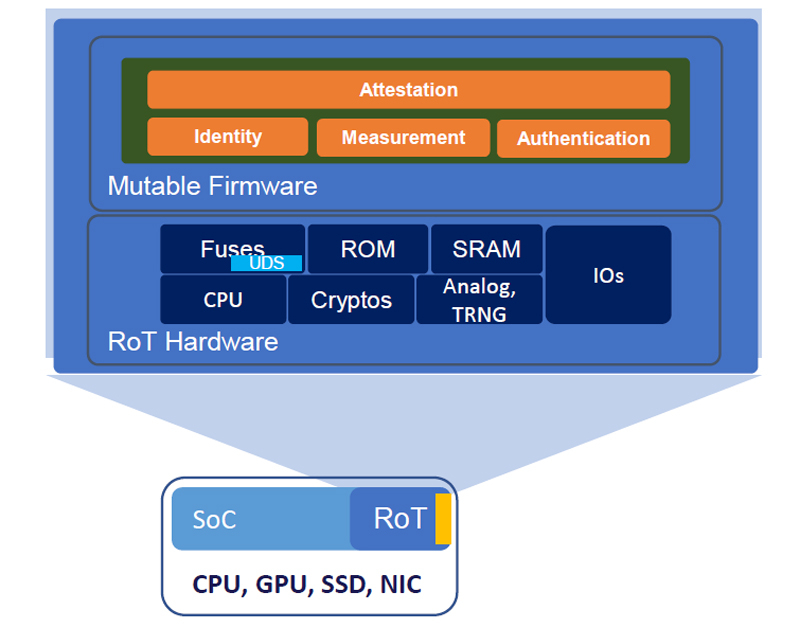

AMD, Google, Microsoft и NVIDIA представили Caliptra — проект по повышению безопасности каждого чипаВ ходе саммита OCP (Open Compute Project) анонсирована открытая спецификация Caliptra 0.5, призванная повысить безопасность процессоров, ускорителей, накопителей и практически любых систем-на-чипе (SoC). Речь идёт об аппаратной реализации технологии Root of Trust (RoT). Она предназначена для проверки целостности и подлинности прошивок и другого встроенного, а также системного программного обеспечения.  RoT гарантирует, что только доверенное ПО может исполняться на чипе. Отмечается, что традиционно средства RoT отделены от SoC и обычно обеспечиваются материнской платой. Однако новые бизнес-модели, предполагающие периферийные и облачные вычисления, предъявляют повышенные требования к обеспечению безопасности. Спецификация Caliptra 0.5 как раз и решает данную проблему.

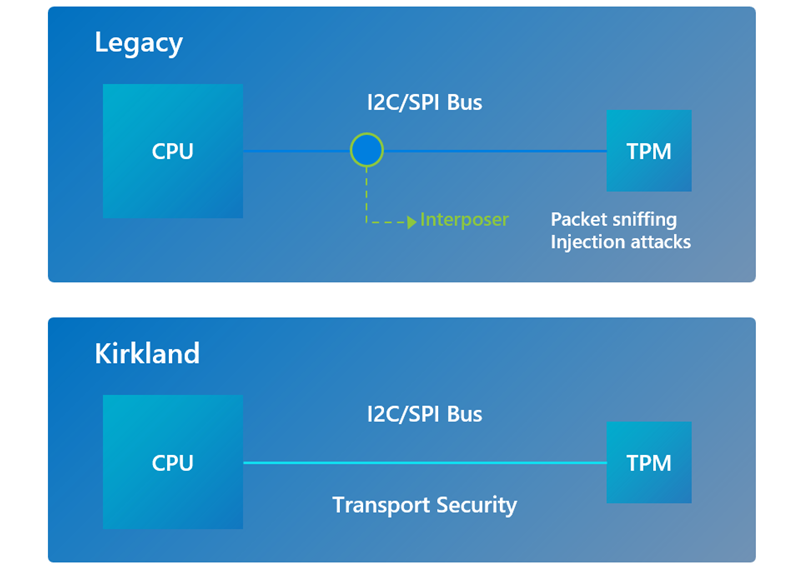

Источник изображений: Caliptra В разработке решения приняли участие AMD, Google, Microsoft и NVIDIA. Спецификация будет поддерживаться различными аппаратными изделиями следующего поколения — CPU, GPU, SSD, NIC и иные ASIC. Отмечается, что Caliptra 0.5 RTL (IP-блоки на базе RISC-V с необходимой обвязкой) распространяется через CHIPS Alliance (Common Hardware for Interfaces, Processors and Systems) — консорциум, который работает над созданием целого спектра открытых решений для SoC и высокоплотных упаковок чипов.  «Существует потребность в улучшенной прозрачности и согласованности низкоуровневой аппаратной безопасности. Мы открываем исходный код Caliptra вместе с нашими партнёрами для удовлетворения этих потребностей», — отмечает Microsoft. Также компания совместно с Google, Infineon и Intel представила Project Kirkland, направленный на создание защищённого канала связи между CPU и TPM с использованием программных средств.

Источник: Microsoft Спецификация Caliptra 0.5 доступна здесь для оценки. На основе отзывов будет выработан окончательный стандарт, отвечающий различным потребностям в зависимости от варианта использования. Кроме того, доступен исходный код, что поможет членам сообщества интегрировать решение в свои микросхемы. Говорится также, что выход спецификации знаменует собой важный шаг вперёд в сторону общеотраслевого сотрудничества в области информационной безопасности.

23.09.2022 [19:58], Алексей Степин

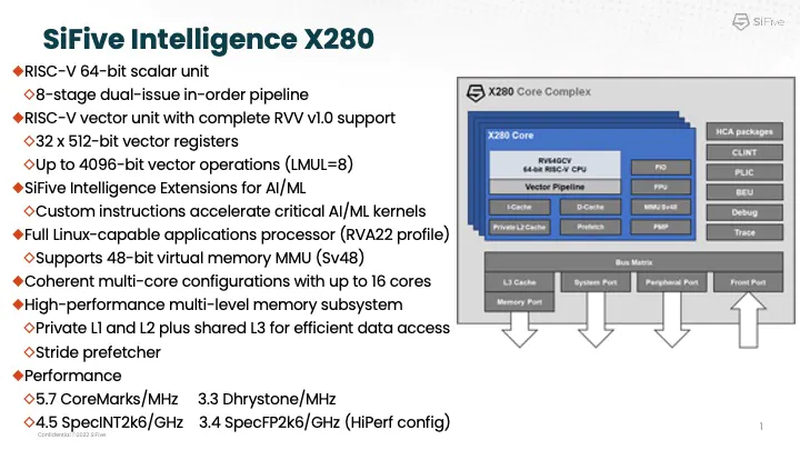

Google заявила, что использует процессоры SiFive Intelligence X280 на RISC-V вместе со своим TPUАрхитектура RISC-V продолжает понемногу набирать популярность и завоевывать внимание ведущих игроков на рынке информационных технологий. На мероприятии AI Hardware Summit в совместном выступлении ведущего архитектора SiFive и архитектора Google TPU было отмечено, что Google уже использует процессоры с ядрами Intelligence X280. Эти ядра — один из вариантов воплощения архитектуры RISC-V, из продвигаемых SiFive. Анонс Intelligence X280 состоялся ещё в апреле 2021 года, когда SiFive выпустила апдейт 21G1, основной упор в котором был сделан на максимизацию характеристик уже существующих ядер RISC-V в области операций с плавающей запятой.

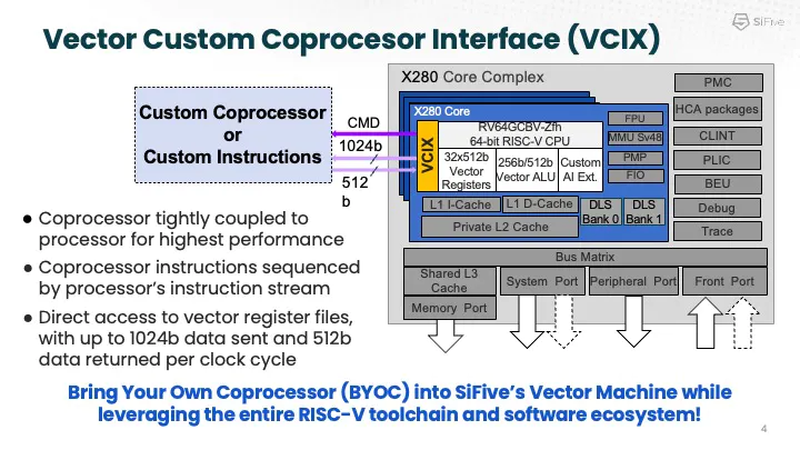

Процессорное ядро Intelligence X280 и его возможности. Источник: SiFive Как следует из названия, данный вариант процессора оптимизирован под задачи машинного интеллекта: ядра RISC-V в нём дополнены векторными конвейерами RISC-V Vector (RVV) с производительностью 4,5 Тфлопс BF16 и 9,2 Топс INT8 на ядро. Одной из самых интересных технологий в Intelligence X280 является интерфейс Vector Coprocessor Interface eXtension (VCIX).

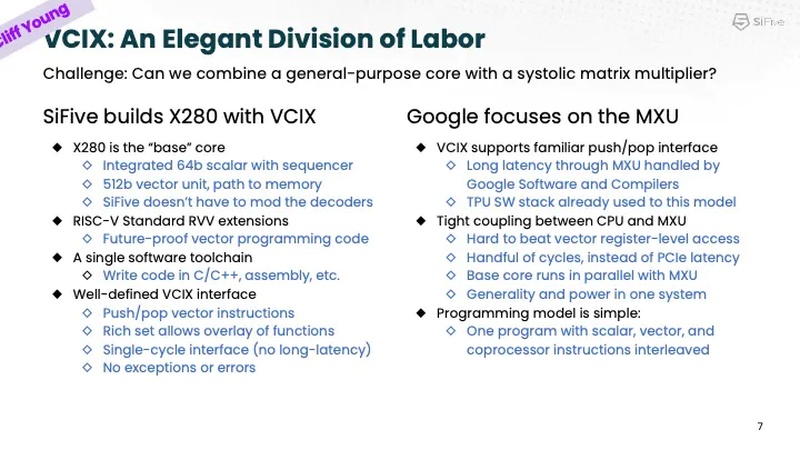

Устройство VCIX. Источник: SiFive Он позволяет подключать внешние ускорители векторных операций напрямую к регистровому файлу X280, минуя основную шину и кеши. Такой подход минимизирует накладные расходы и не требует использования специальных средств при программировании системы, поскольку связка из X280 и подключённого по VCIX ускорителя работает полностью прозрачно в рамках стандартных средств разработки SiFive.

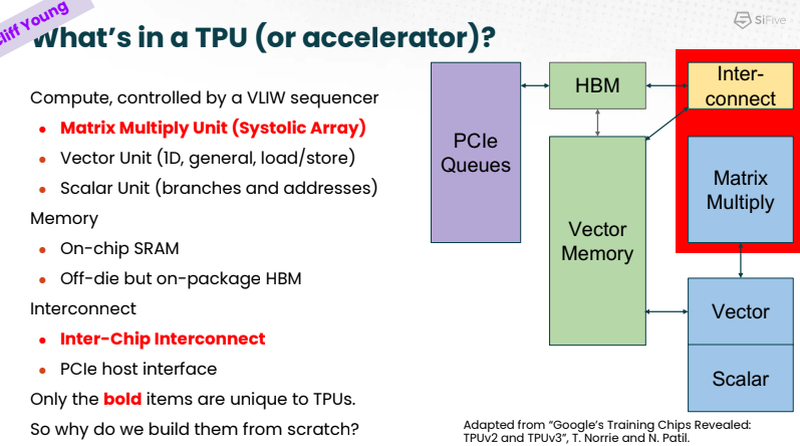

Сильные стороны Google TPU. Источник: SiFive На саммите в Санта-Кларе разработчики SiFive и Google TPU рассказали, что процессоры Intelligence X280 используются в качестве хост-процессоров к ускорителям систолической векторной математики Google MXU; правда, о масштабах внедрения RISC-V в Google сведений приведено не было.

Разделение труда Intelligence X280 и Google TPU. Источник: SiFive Ранее уже появлялась информация, что Google активно тестирует ASIC сторонних разработчиков в связке со своим TPU, в частности, чипы Broadcom, дабы разгрузить его от второстепенных задач и сделать упор на сильных сторонах — матричной математике и быстром интерконнекте. Похоже, SiFive Intelligence X280 решает задачу интеграции подобного рода задач более изящно: как отметил в выступлении Клифф Янг (Cliff Young), архитектор Google TPU, с помощью VCIX можно построить машину, позволяющую усидеть на двух стульях (build a machine that lets you have your cake and eat it too).

24.08.2022 [22:42], Владимир Мироненко

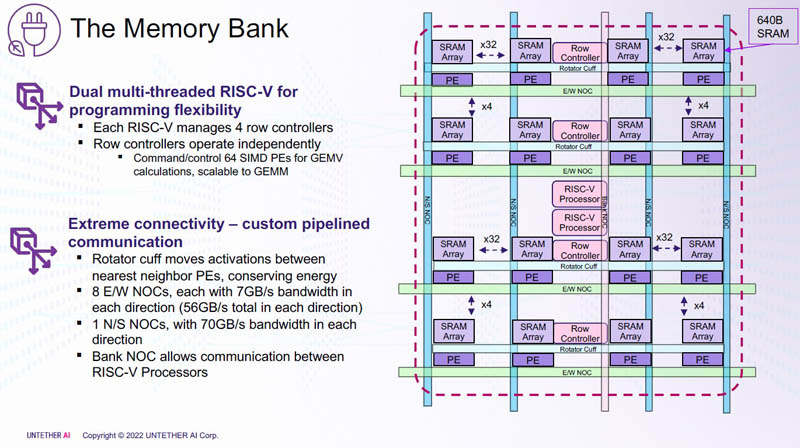

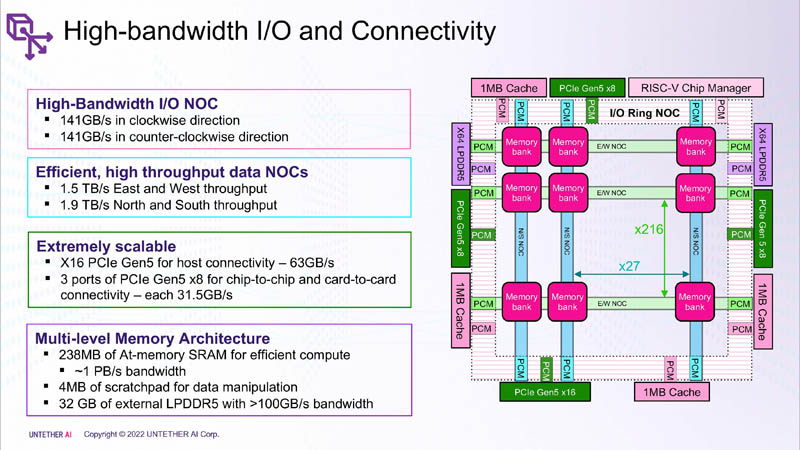

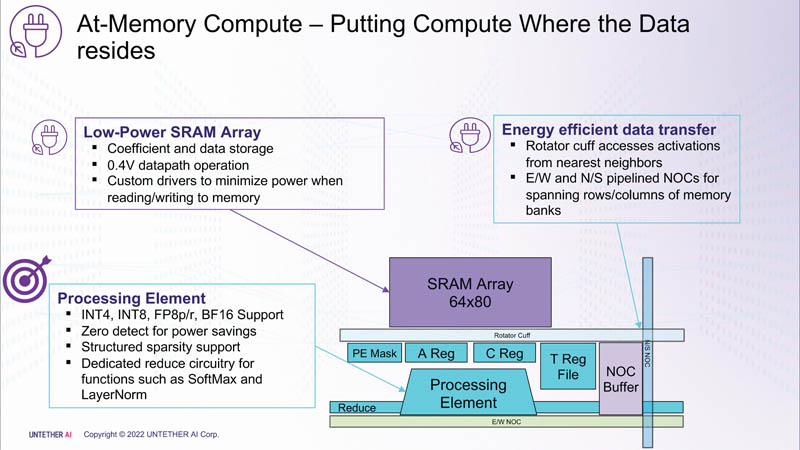

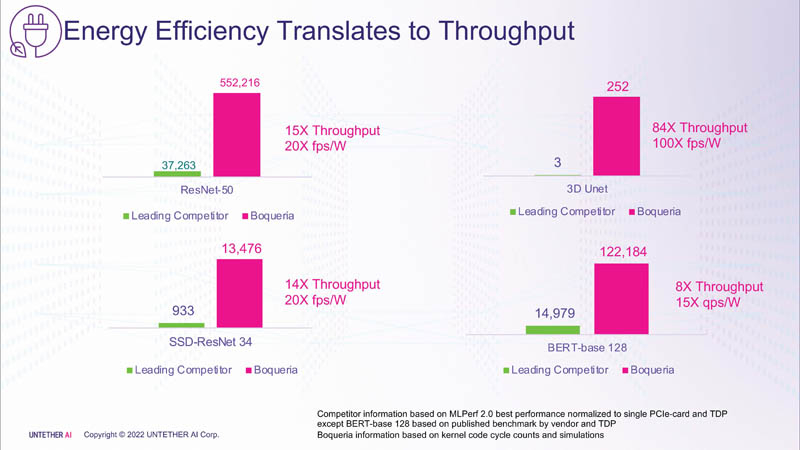

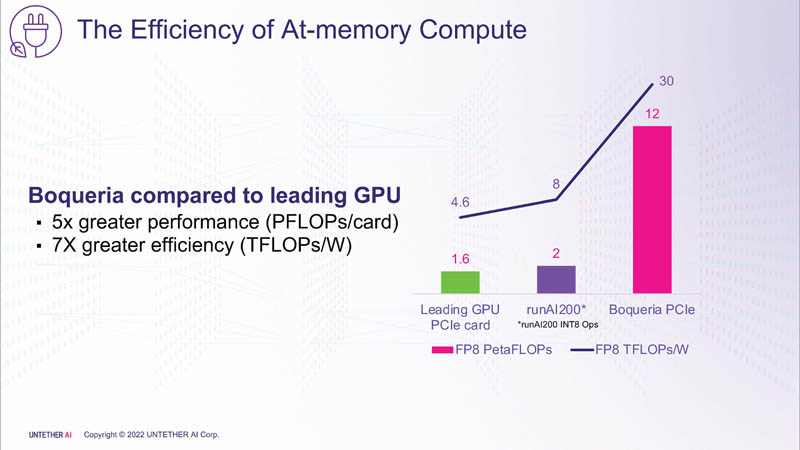

Untether AI представила ИИ-ускоритель speedAI240 — 1,5 тыс. ядер RISC-V и 238 Мбайт SRAM со скоростью 1 Пбайт/сКомпания Untether AI анонсировала ИИ-архитектуру следующего поколения speedAI (кодовое название «Boqueria»), ориентированную на инференс-нагрузки. При энергоэффективности 30 Тфлопс/Вт и производительности до 2 Пфлопс на чип speedAI устанавливает новый стандарт энергоэффективности и плотности вычислений, говорит компания. Поскольку at-memory вычисления в ряде задач значительно энергоэффективнее традиционных архитектур, они могут обеспечить более высокую производительность при одинаковых затратах энергии. Первое поколение устройств runAI в 2020 году Untether AI достигла энергоэффективности на уровне 8 Тфлопс/Вт для INT8-вычислений. Новая архитектура speedAI обеспечивает уже 30 Тфлопс/Вт. .jpg)

Изображения: Untether AI (via ServeTheHome)  Этого удалось добиться благодаря архитектуре второго поколения, использованию более 1400 оптимизированных 7-нм ядер RISC-V (1,35 ГГц) с кастомными инструкциями, энергоэффективному управлению потоком данных и внедрению поддержки FP8. Вкупе это позволило вчетверо поднять эффективность speedAI по сравнению с runAI. Новинка может быть гибко адаптирована к различным архитектурам нейронных сетей. Концептуально speedAI напоминает ещё один тысячеядерный чип RISC-V — Esperanto ET-SoC-1.   Первый член семейства speedAI — speedAI240 — обеспечивает 2 Пфлопс вычислениях в FP8-вычислениях или 1 Пфлопс для BF16-операций. Благодаря этому обеспечивается самая высокая в отрасли эффективность — например, для модели BERT заявленная производительность составляет 750 запросов в секунду на Вт (qps/w), что, по словам компании, в 15 раз выше, чем у современных GPU. Добиться повышения производительности удалось благодаря тесной интеграции вычислительных элементов и памяти.   На каждый блок SRAM объёмом 328 Кбайт приходится 512 вычислительных блоков, поддерживающих работу с форматами INT4, INT8, FP8 и BF16. Каждый вычислительный блок имеет два 32-бит (RV32EMC) кастомных ядра RISC-V с поддержкой четырёх потоков и 64 SIMD. Всего есть 729 блоков, так что суммарно чип несёт 238 Мбайт SRAM и 1458 ядер. Блоки провязаны между собой mesh-сетью, к которой также подключены кольцевая IO-шина, несущая четыре 1-Мбайт блока общего кеша, два контроллера LPDRR5 (64 бит) и порты PCIe 5.0: один x16 для подключения к хосту и три x8 для объединения чипов. Суммарная пропускная способность SRAM составляет около 1 Пбайт/с, mesh-сети — от 1,5 до 1,9 Тбайт/с, IO-шины — 141 Гбайт/c в обоих направлениях, а 32 Гбайт DRAM — чуть больше 100 Гбайт/с. PCIe-интерфейсы позволяют объединить до трёх ускорителей, с шестью speedAI240 чипами у каждого. Решения speedAI будут предлагаться как в виде отдельных чипов, так и в составе готовых PCIe-карт и M.2-модулей. Ожидается, что первые поставки избранным клиентам начнутся в первой половине 2023 года. |

|