Материалы по тегу: risc-v

|

08.02.2022 [00:30], Владимир Мироненко

Ventana, разработчик серверных процессоров RISC-V, объявил о стратегическом партнёрстве с IntelСтартап Ventana Micro Systems Inc., разработчик высокопроизводительных серверных процессоров на базе архитектуры RISC-V, объявил о стратегическом партнёрстве с Intel — ядра и чиплеты Ventana будут доступны в рамках Intel Foundry Services (IFS) для крупных клиентов ЦОД, операторов сетей 5G, потребителей в областях ИИ и машинного обучения, автомобильной индустрии и т. д. Ventana разрабатывает серверные CPU с расширяемыми возможностями, поставляемые в виде SoC с чиплетной компоновкой или IP-блоков. Процессоры предназначены для обеспечения лучшей в своём классе однопоточной производительности и могут быть оптимизированы для высокопроизводительных и облачных вычислений, ЦОД-нагрузок, 5G и периферийных вычислений, выполнения задач ИИ и машинного обучения, автомобильных и клиентских приложений.

Источник изображения: ventanamicro.com Модульная и масштабируемая продуктовая стратегия Ventana, основанная на использовании чиплетов, позволяет обеспечить быстрое коммерческое внедрение со значительной экономией времени и стоимости разработки по сравнению с преобладающими на рынке IP-моделями. Собственные ядра CPU компания намерена выпускать на TSMC по 5-нм нормам, но для остальных блоков могут использоваться сторонние производства. В рамках партнёрства с Intel ядра Ventana можно будет интегрировать в SoC конечных заказчиков. Кроме того, Ventana планирует предложить масштабируемую вычислительную платформу, которая позволит гиперскейлерам и крупным OEM-производителям гибко подбирать и настраивать функциональные блоки у заказываемых чипов, значительно сокращая время и стоимость разработки. Боб Бреннан (Bob Brennan), вице-президент Intel Foundry Services по разработке клиентских решений отметил, что у Ventana «самая совершенная и хорошо разработанная платформа» на базе Open Chiplet, которая полностью соответствует видению Intel. По его словам, чиплеты Ventana позволят IFS предоставлять модульные решения, повышающие производительность, снижающие энергопотребление и затраты на разработку, и ускоряющие время выхода продуктов на рынок.

17.12.2021 [01:35], Алексей Степин

Российский серверный процессор Baikal-S2 получит чиплетную компоновку, 128 ядер Armv9 с частотой 3 ГГц, 8 каналов DDR5, 192 линии PCIe 5.0 и CXL 2.0На ежегодной итоговой конференции Байкал Электроникс состоялся анонс 128-ядерных серверных Arm-процессоров второго поколения Baikal-S2, были показаны результаты тестов 48-ядерных Baikal-S, анонсированы первые же российские серверы и СХД на их основе, а также было объявлено о заключении стратегических сделок и планах на будущее. Если говорить о сделках, то можно смело сказать, что рамками только Arm Байкал себя уже не ограничивает: получение доли в CloudBEAR означает и получение основы для разработки собственных чипов с архитектурой RISC-V, и первым же проектом станет создание сертифицированной системы доверенной загрузки для процессоров Baikal-L и Baikal-S2. Но среди равноправных партнёров значатся не только российские разработчики — заключена сделка с Esperanto Technologies.

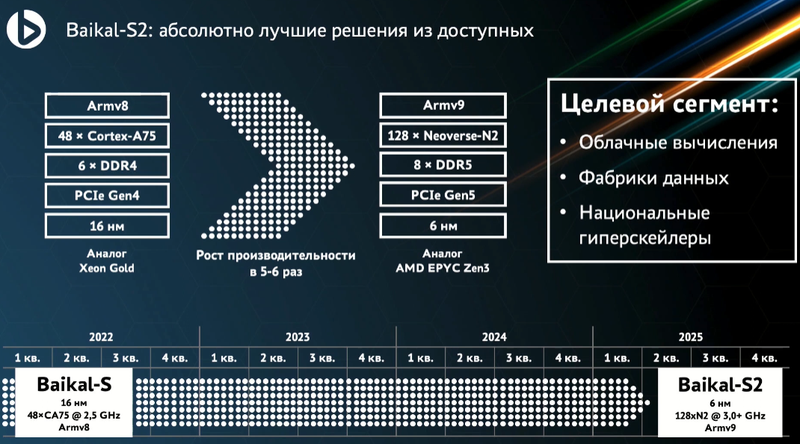

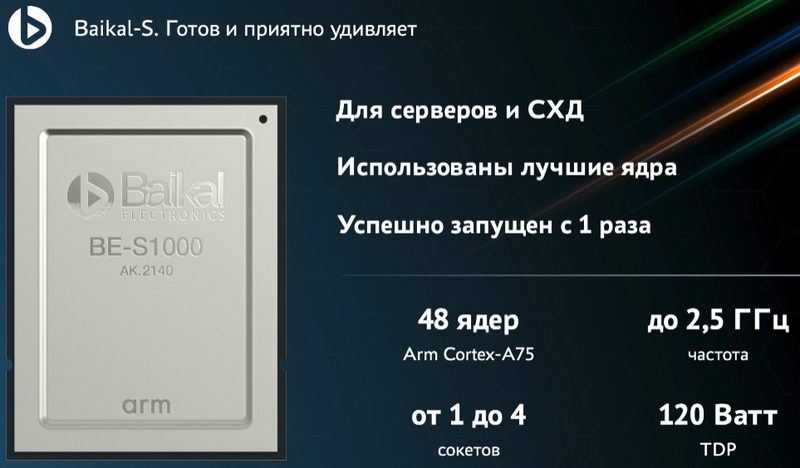

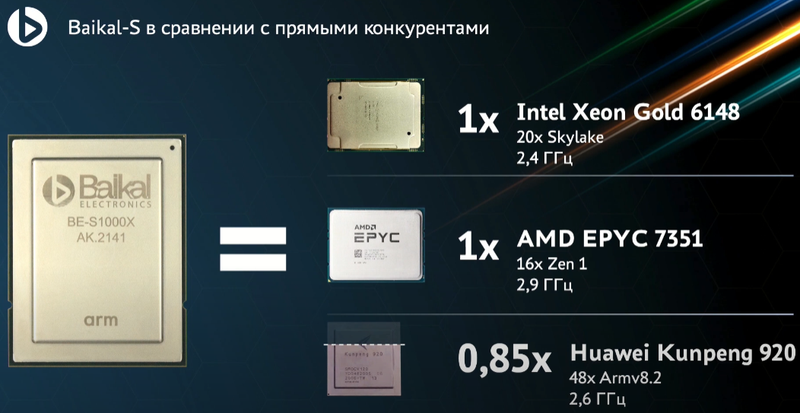

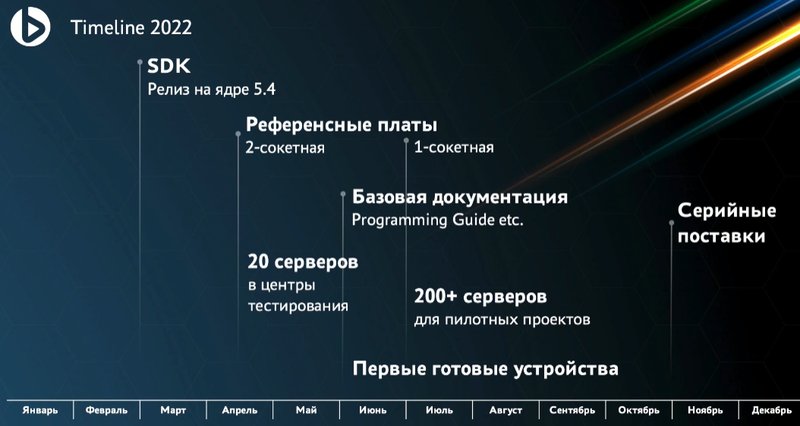

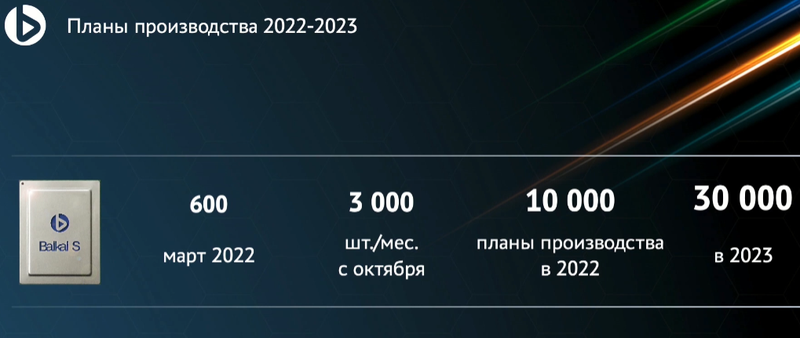

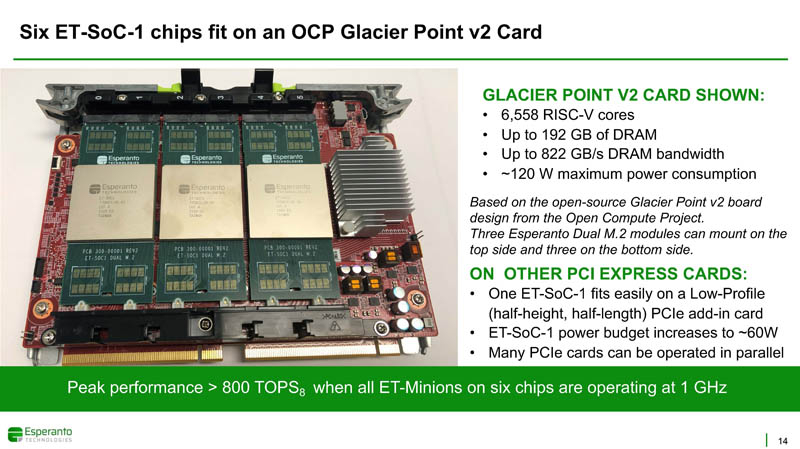

Тестовая плата с процессором Baikal-S (Изображения: Байкал Электроникс) Данная сделка позволит получить доступ к весьма серьёзным разработкам: напомним, Esperanto создала ET-SoC-1, мощнейший ИИ-ускоритель с более чем тысячью ядер RISC-V в составе. Связка из четырёх таких чипов развивает более 800 Топс в задачах инференса, потребляя всего 120 Вт. Надо ли говорить, насколько это важно в эпоху нейросетей, машинного обучения и разнообразных сопроцессоров-ускорителей.  Несмотря на то, что Baikal-S «старичком» назвать никак нельзя, компания анонсировала уже второе поколение чипов — Baikal-S2 базируется на новейшей архитектуре Neoverse-N2 (ARMv9). Процессор будет выполнен по 6-нм техпроцессу с использованием чиплетной компоновки и получит 128 ядер с частотой порядка 3 ГГц, 8 каналов DDR5 (возможно, будет и больше), 192 линии PCIe 5.0, поддержку CXL 2.0 и CCIX 2.0. Ожидается, что он станет аналогом AMD EPYC Milan. Разработку планируется закончить к 2025 году.  Что касается текущего поколения Baikal-S, то осенью этого года была получена первая партия чипов, а также было анонсировано несколько решений на его основе. Как теперь отрапортовали разработчики, первые чипы оказались очень удачными во всех отношениях, так что больших препятствий на пути их внедрения быть не должно. На конференции были представлены одно- и двухсокетные серверы и СХД от российских компаний 3Logic, Aquarius, ICL, iRU, Норси-Транс. Впоследствии появятся и четырёхпроцессорные системы.  Напомним, что Baikal-S содержит в своём составе 48 ядер Arm Cortex-A75 с частотой до 2,5 ГГц и имеет TDP 120 Вт. Шестиканальный контроллер памяти поддерживает до 768 Гбайт DDR4-3200. Современно выглядит и поддержка PCI Express 4.0 (80 линий), и наличие выделенного управляющего ядра для организации доверенных вычислений, и аппаратная виртуализация.  В синтетических тестах новинка показала результаты, сравнимые с Intel Xeon Gold 6148 или AMD EPYC 7351, а своему китайскому «коллеге» в лице HiSilicon Kunpeng 920 процессор уступил лишь в некоторых тестах. Разработчики уверены, что процессор получился универсальным и его можно использовать практически везде: в серверах любых профилей, СХД, суперкомпьютерах, устройствах сетевой безопасности и даже в базовых станциях 5G. Результаты тестов также доступны и на сайте Geekbench.  Ожидается, что SDK для новой платформы будет доступен уже в конце февраля следующего года. Весной появятся двухпроцессорные платы и первые 20 серверов попадут в центры тестирования, а к середине лета 200 с лишним серверов примут своё участие в пилотных проектах. Старт серийного производства CPU намечен на октябрь-ноябрь 2022 года — речь идёт примерно о 10 тыс. процессоров. В 2023 году этот объём будет утроен и при необходимости увеличен.  Таким образом, Байкал Электроникс доказала, что может создавать достойные серверные решения, не уступающие зарубежным, причём, как на базе x86-64, так и на базе Arm. Уже сейчас процессоры Baikal-S могут стать основой для производительных серверов российской разработки, а сделка с Esperanto сделает российские HPC-системы и комплексы машинного обучения по-настоящему мощными.

16.12.2021 [16:59], Сергей Карасёв

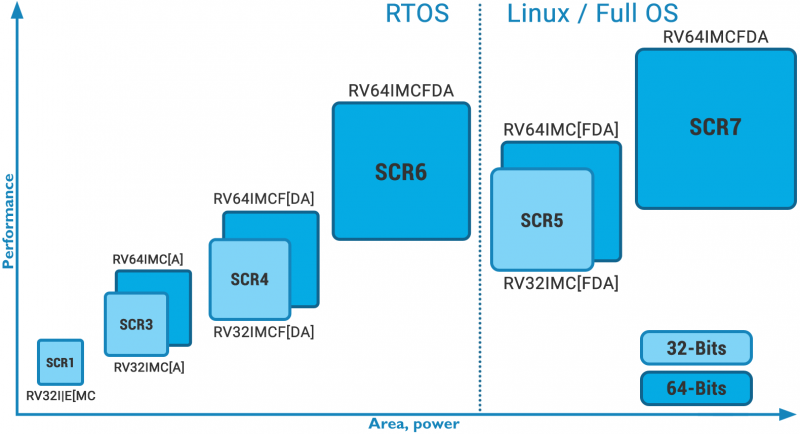

Российская компания Syntacore вошла в состав правления RISC-V InternationalRISC-V International сообщила о том, что российская компания Syntacore, подконтрольная российской же компании YADRO, получила статус премиального участника названной организации. При этом сооснователь и исполнительный директор Syntacore Александр Редькин вошёл состав правления RISC-V International. Syntacore является отечественным разработчиком микропроцессорных ядер и специализированных инструментов на архитектуре RISC-V. Компания входит в число основателей открытого международного консорциума RISC-V. Его цель заключается в разработке и продвижение одноимённой открытой архитектуры.

Изображение: Syntacore «Сегодняшний анонс ещё сильнее укрепляет наше лидирующее положение на рынке интеллектуальной собственности RISC-V в новом году и дальше. Вся наша интеллектуальная собственность полностью совместима с последней версией спецификации RISC-V», — отметил господин Редькин. Компания Syntacore является одним из лидеров экосистемы RISC-V и лицензирует микропроцессорные технологии собственной разработки на базе данной архитектуры клиентам в России и за рубежом. Продукты на основе процессорных технологий компании разрабатываются по нормам от 180 до 7 нм.

22.09.2021 [21:16], Алексей Степин

Выпущена тестовая партия европейских высокопроизводительных RISC-V процессоров EPI EPAC1.0Наличие собственных высокопроизводительных процессоров и сопровождающей их технической инфраструктуры — в современном мире вопрос стратегического значения для любой силы, претендующей на первые роли. Консорциум European Processor Initiative (EPI), в течение долгого времени работавший над созданием мощных процессоров для нужд Евросоюза, наконец-то, получил первые весомые плоды. О проекте EPI мы неоднократно рассказывали читателям в 2019 и 2020 годах. В частности, в 2020 году к консорциуму по разработке мощных европейских процессоров для систем экза-класса присоединилась SiPearl. Но сегодня достигнута первая серьёзная веха: EPI, насчитывающий на данный момент 28 членов из 10 европейских стран, наконец-то получил первую партию тестовых образцов процессоров EPAC1.0.

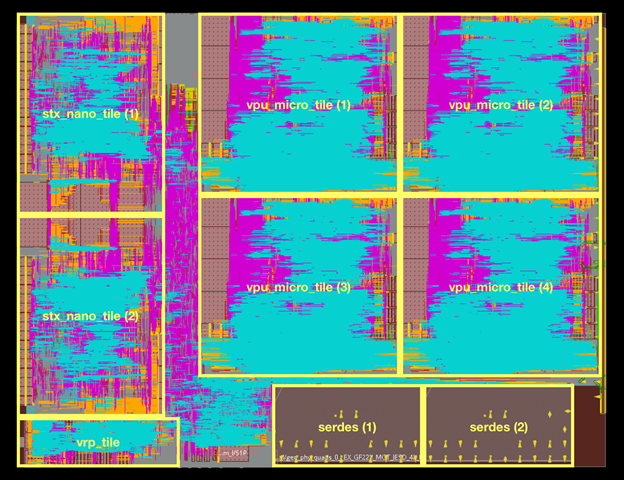

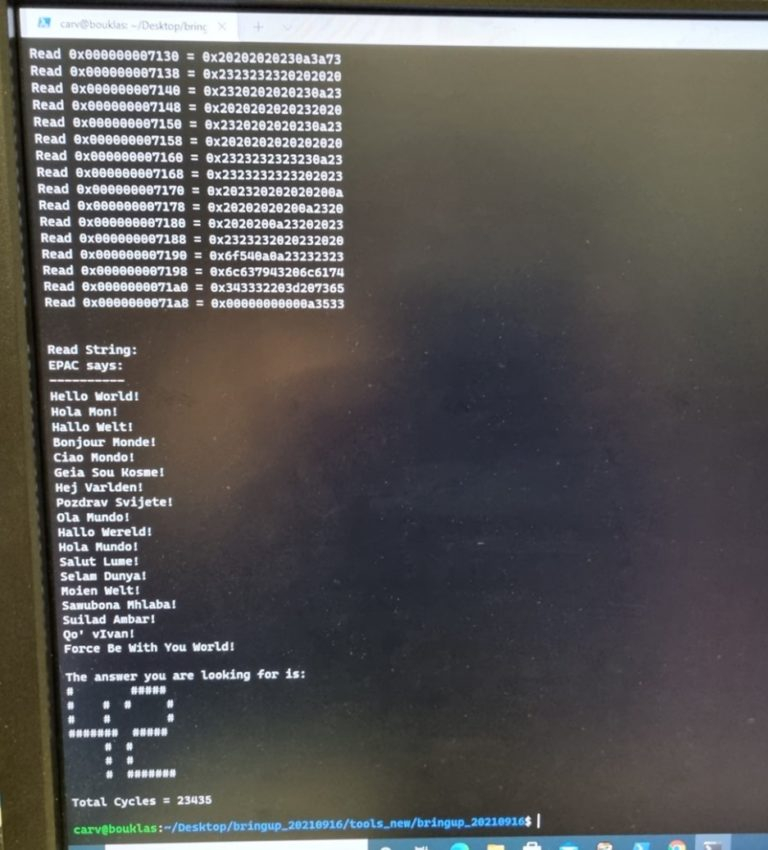

Источник изображений: European Processor Initiative (EPI) По предварительным данным, первичные тесты новых чипов прошли успешно. Процессоры EPAC имеют гибридную архитектуру: в качестве базовых вычислительных ядер общего назначения в них используются ядра Avispado с архитектурой RISC-V, разработанные компанией SemiDynamics. Они объединены в микро-тайлы по четыре ядра и дополнены блоком векторных вычислений (VPU), созданным совместно Барселонским Суперкомпьютерным Центром (Испания) и Университетом Загреба (Хорватия).

Строение кристалла EPAC1.0 Каждый такой тайл содержит блоки Home Node (интерконнект) с кешем L2, обеспечивающие когерентную работу подсистем памяти. Имеется в составе EPAC1.0 и описанный нами ранее тензорно-стенсильный ускоритель STX, к созданию которого приложил руку небезызвестный Институт Фраунгофера (Fraunhofer IIS). Дополняет картину блок вычислений с изменяемой точностью (VRP), за его создание отвечала французская лаборатория CEA-LIST. Все ускорители в составе нового процессора связаны высокоскоростной сетью, использующей SerDes-блоки от EXTOLL.  Первые 143 экземпляра EPAC произведены на мощностях GlobalFoundries с использованием 22-нм техпроцесса FDX22 и имеют площадь ядра 27 мм2. Используется упаковка FCBGA 22x22. Тактовая частота невысока, она составляет всего 1 ГГц. Отчасти это следствие использования не самого тонкого техпроцесса, а отчасти обусловлено тестовым статусом первых процессоров. Но новорожденный CPU жизнеспособен: он успешно запустил первые написанные для него программы, в числе прочего, ответив традиционным «42» на главный вопрос жизни и вселенной. Ожидается, что следующее поколение EPAC будет производиться с использованием 12-нм техпроцесса и получит чиплетную компоновку.

01.09.2021 [23:58], Андрей Галадей

Ветераны индустрии основали стартап Ventana для создания чиплетных серверных процессоров RISC-VСтартап Ventana Micro Systems, похоже, намерен перевернуть рынок серверов. Компания заявила о разработке высокопроизводительных процессоров на архитектуре RISC-V для центров обработки данных. Первые образцы фирменных CPU будут переданы клиентам во второй половине следующего года, а поставки начнутся в первой половине 2023 года. При этом процессоры получат чиплетную компоновку — различные модули и кристаллы на общей подложке. Основные процессорные ядра разработает сама Ventana, а вот остальные чиплеты будут создаваться под нужды определённых заказчиков. CPU-блоки будут иметь до 16 ядер, которые, как обещается, окажутся быстрее любых других реализаций RV64. Использование RISC-V позволит разрабатывать сверхмощные решения в рекордные сроки и без значительного бюджета. Ядра будут «выпекаться» на TSMC по 5-нм нормам, но для остальных блоков могут использовать другие техпроцессы и фабрики.  Ventana будет следить за процессом их создания и упаковывать до полудюжины блоков в одну SoC. Для соединения ядер, кеша и других компонентов будет использоваться фирменная кеш-когерентная шина, которая обеспечит задержку порядка 8 нс и скорость передачи данных 16 Гбит/с на одну линию. Основными заказчиками, как ожидается, станут гиперскейлеры и крупные IT-игроки, которым часто требуется специализированное «железо» для ЦОД, 5G и т.д. Сегодня Ventana объявила о привлечении $38 млн в рамках раунда B. Общий же объём инвестиций составил $53 млн. Компания была основана в 2018 году. Однако это не совсем обычный стартап — и сами основатели, и команда являются настоящими ветеранами индустрии. Все они имеют многолетний опыт работы в Arm, AMD, Intel, Samsung, Xilinx и целом ряде других крупных компаний в области микроэлектроники. Часть из них уже имела собственные стартапы, которые были поглощены IT-гигантами.

26.08.2021 [03:07], Алексей Степин

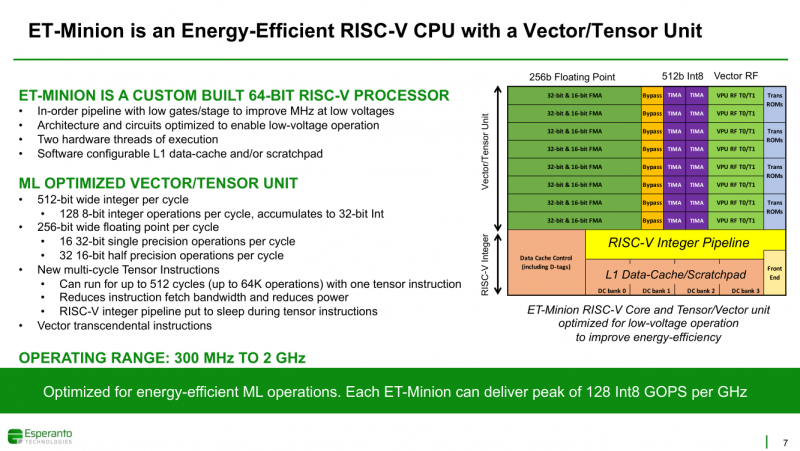

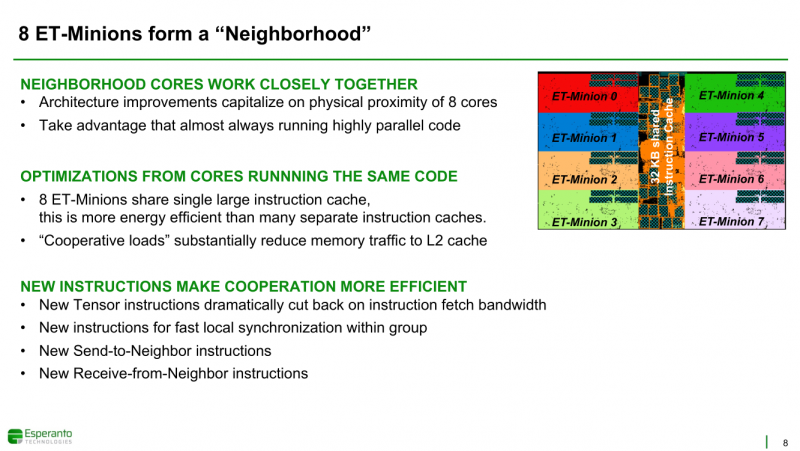

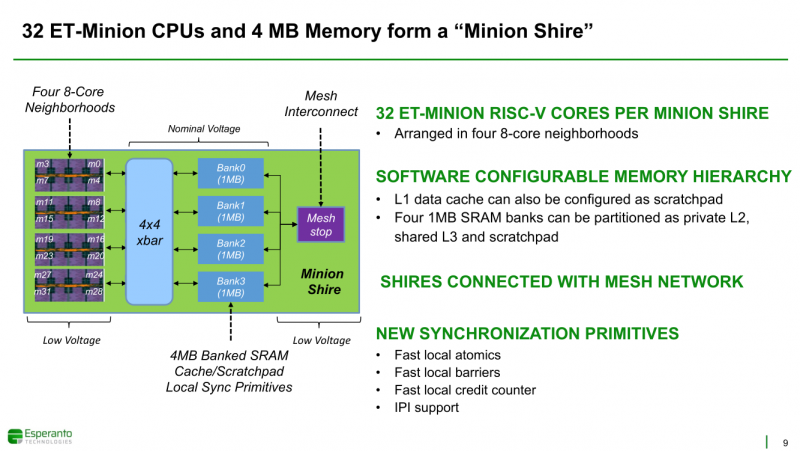

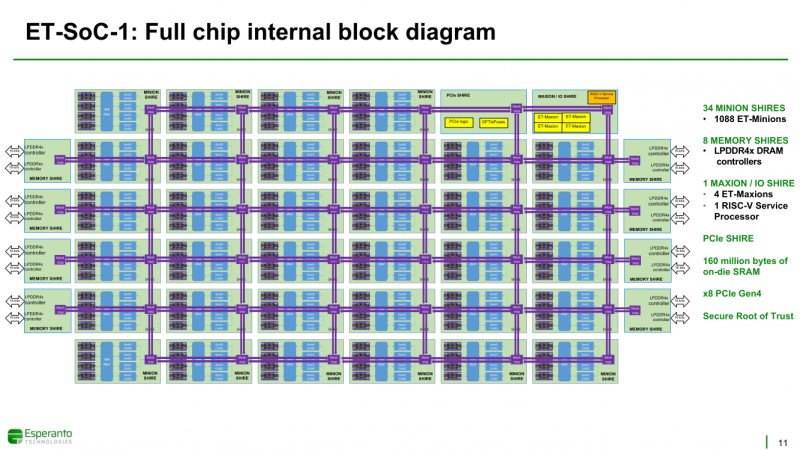

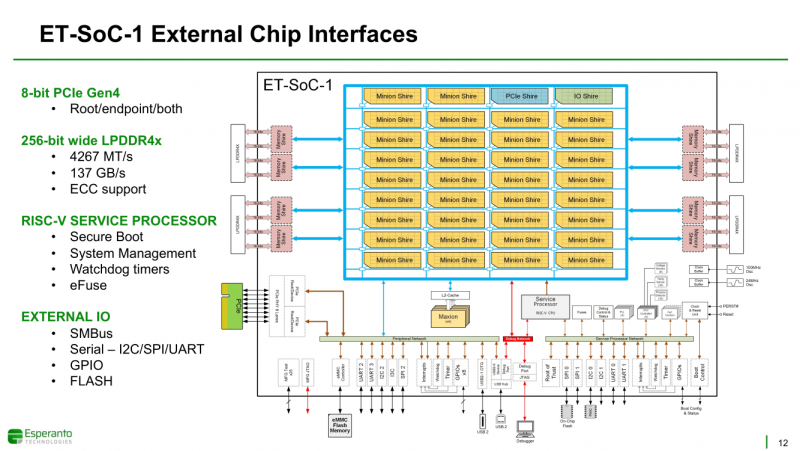

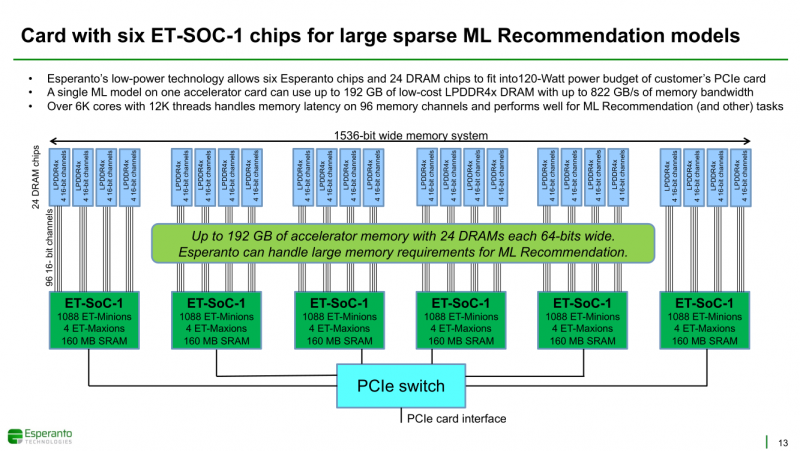

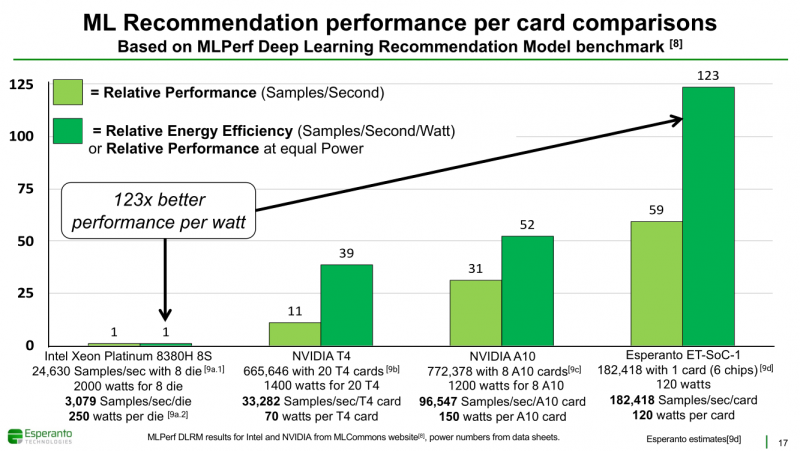

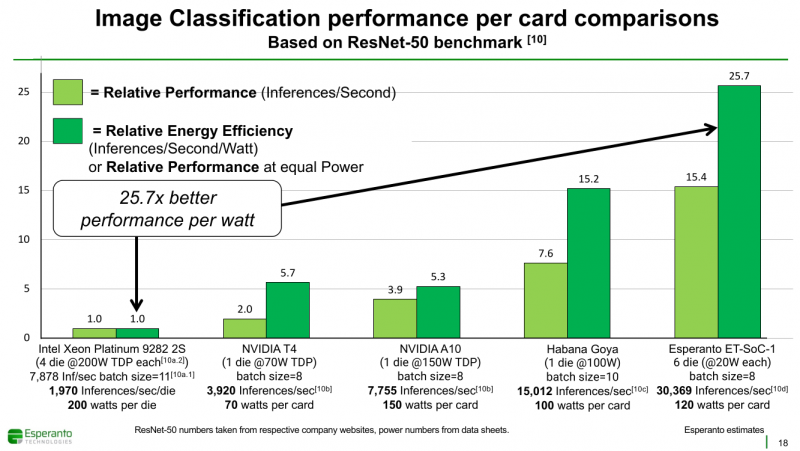

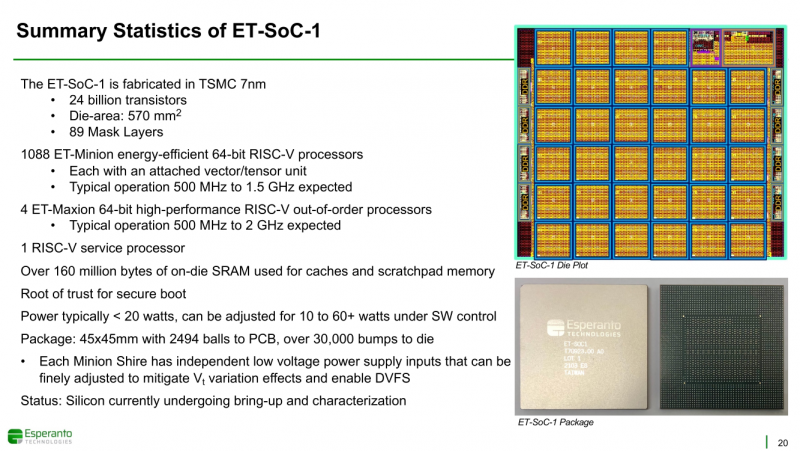

Получены первые образцы 1000-ядерного суперкомпьютера-на-чипе Esperanto ET-SoC-1Рекомендательные системы, активно используемые социальными сетями, рекламными платформами и т.д. имеют специфические особенности. От них требуется высокая скорость отклика, но вместе с тем их ИИ-модели весьма объёмны, порядка 100 Гбайт или более. А для их эффективной работы нужен ещё и довольно большой кеш. Для инференса чаще всего используется либо CPU (много памяти, но относительно низкая скорость) или GPU (высокая скорость, но мало памяти), но они не слишком эффективны для этой задачи. При этом существуют ещё и физические ограничения со стороны гиперскейлеров: в сервере не так много полноценных PCIe-слотов и свободного места + есть жёсткие ограничения по энергопотреблению и охлаждению (чаще всего воздушному). Всё это было учтено компанией Esperanto, чьей специализацией является разработка чипов на базе архитектуры RISC-V. На днях она получила первые образцы ИИ-ускорителя ET-SoC-1, который она сама называет суперкомпьютером-на-чипе (Supercomputer-on-Chip).  Новинка предназначена для инференса рекомендательных систем, в том числе на периферии, где на первый план выходит экономичность. Компания поставила для себя непростую задачу — весь комплекс ускорителей с памятью и служебной обвязкой должен потреблять не более 120 Вт. Для решения этой задачи пришлось применить немало ухищрений. Самое первое и очевидное — создание относительно небольшого, но универсального чипа, который можно было бы объединять с другими такими же чипами с линейным ростом производительности. Для достижения высокой степени параллелизма основой такого чипа должны стать небольшие, но энергоэффективные ядра. Именно поэтому выбор пал на 64-бит ядра RISC-V, поскольку они «просты» не только с точки зрения ISA, но и по транзисторному бюджету. Чип ET-SoC-1 сочетает в себе два типа ядер RISC-V: классических «больших» ядер (ET-Maxion) с внеочередным выполнением у него всего 4, зато «малых» ядер (ET-Minion) с поддержкой тензорных и векторных вычислений — целых 1088. На комплекс ядер ET-Maxion возлагаются задачи общего назначения и в ИИ-вычислениях он напрямую не участвует, зато позволяет быть ET-SoC-1 полностью автономным, так как прямо на нём можно запустить Linux. Помогает ему в этом ещё один служебный RISC-V процессор для периферии. А вот ядра ET-Minion довольно простые: внеочередного исполнения инструкций в них нет, зато есть поддержка SMT2 и целый набор новых инструкций для INT- и FP-операций с векторами и тензорами. За каждый такт ядро ET-Minion способно выполнять 128 INT8-операций с сохранением INT32-результата, 16 FP32-операций или 32 — FP16. «Длинные» тензорные операции могут непрерывно исполняться в течение 512 циклов (до 64 тыс. операций), при этом целочисленные блоки в это время отключаются для экономии питания. Система кешей устроена несколько непривычным образом. На ядро приходится 4 банка памяти, которые можно использовать как L1-кеш для данных и как быструю универсальную память (scratchpad). Восемь ядер ET-Minion формируют «квартал» вокруг общего для них кеша инструкций, так как на таких задачах велика вероятность того, что инструкции для всех ядер действительно будут одни и те же. Кроме того, это энергоэффективнее, чем восемь индивидуальных кешей, и позволяет получать и отправлять данные большими блоками, снижая нагрузку на L2-кеш. Восемь «кварталов» формируют «микрорайон» с коммутатором и четырьмя банками SRAM объёмом по 1 Мбайт, которые можно использовать как приватный L2-кеш, как часть общего L3-кеша или как scratchpad. Посредством mesh-сети «микрорайоны» общаются между собой и с другими блоками: ET-Maxion, восемь двухканальных контроллеров памяти, два root-комплекса PCIe 4.0 x8, аппаратный RoT. Суммарно на чип приходится порядка 160 Мбайт SRAM. Контроллеры оперативной памяти поддерживают модули LPDDR4x-4267 ECC (256 бит, до 137 Гбайт/с). Тактовая частота ET-Minion варьируется в пределах от 500 МГц до 1,5 ГГц, а ET-Maxion — от 500 МГц до 2 ГГц. В рамках OCP-блока Glacier Point V2 компания объединила на одной плате шесть ET-SoC-1 (всего 6558 ядер RISC-V), снабдив их 192 Гбайт памяти (822 Гбайт/с) — это больше, нежели у NVIDIA A100 (80 Гбайт). Такая связка развивает более 800 Топс, требуя всего 120 Вт. В среднем же она составляет 100 ‒ 200 Топс на один чип с потреблением менее 20 Вт. Это позволяет создать компактный M.2-модуль или же наоборот масштабировать систему далее. Шасси Yosemite v2 может вместить 64 чипа, а стойка — уже 384 чипа. В тесте MLPerf для рекомендательных систем производительность указанной выше связки из шести чипов в пересчёте на Ватт оказалась в 123 раза выше, чем у Intel Xeon Platinum 8380H (250 Вт), и в два-три раза выше, чем у NVIDIA A10 (150 Вт) и T4 (70 Вт). В «неудобном» для чипа тесте ResNet-50 разница с CPU и ускорителем Habana Goya уже не так велика, а вот с решениями NVIDIA, напротив, более заметна. При этом о поддержке со стороны ПО разработчики также подумали: чипы Esperanto могут работать с широко распространёнными фреймворками PyTorch, TensorFlow, MXNet и Caffe2, а также принимать готовые ONNX-модели. Есть и SDK для C++, а также драйверы для x86-хостов. Опытные образцы изготовлены на TSMC по 7-нм техпроцессу. Кристалл площадью 570 мм2 содержит 24 млрд транзисторов. Чип имеет упаковку BGA2494 размерами 45 × 45 мм2. Энергопотребление (а вместе с ним и производительность) настраивается в диапазоне от 10 до 60+ Ватт. Потенциальным заказчикам тестовые чипы станут доступны до конца года. Компания также готова адаптировать ET-SoC-1 под другие техпроцессы и фабрики, но демо на базе OCP-платформы и сравнение с Cooper Lake — это недвусмысленный намёк для Facebook✴, что Esperanto будет рада видеть её в числе первых клиентов.

27.07.2019 [15:15], Геннадий Детинич

Alibaba представила 16-ядерный RISC-V процессор XT 910 для «умной» периферии и edge-платформНа днях дочернее подразделение корпорации Alibaba Group компания Pingtouge Semiconductor на тематической конференции в Шанхае представила первый фирменный процессор для «умной» периферии. Китайская разработка XuanTie 910 оказалось уникальной по целому ряду причин, о которых мы поговорим ниже. Но прежде обозначим главное, на чём настаивают китайские источники. Процессор XuanTie 910 поможет китайским компаниям всех уровней сбросить зависимость от ядер ARM и других проприетарных разработок (читай ― сведут на нет опасность санкций со стороны США), поскольку ядра XuanTie 910 используют открытую архитектуру RISC-V с открытым набором команд.  Производительность моделей процессоров семейства XuanTie 910 может варьироваться в широких пределах. 64-бит ядра собираются в кластеры по четыре штуки. В процессоре может быть до четырёх таких кластеров, то есть в максимальной конфигурации XuanTie 910 имеет 16 ядер RISC-V. Больше вряд ли необходимо, но в случае надобности разработчики наверняка смогут увеличить число ядер в процессоре. Относительно небольшое число ядер в процессорах XuanTie 910 объясняется назначением платформы ― стать основой вещей с подключением к Интернету, ассистентов (умных колонок и прочего), самоуправляемых автомобилей, периферии с подключением к сетям 5G, платформ с элементами ИИ и тому подобных решений для перифейрийных (edge) вычислений и платформ. По словам разработчиков, XuanTie 910 сегодня является самым производительным решением на архитектуре RISC-V. Это решение на частоте 2,5 ГГц, изготовленное с использованием 12-нм техпроцесса, как заявлено, обеспечивает производительность на уровне 7,1 CoreMark/МГц, что на 40 % больше, чем для существующих сегодня конкурирующих процессоров на архитектуре RISC-V. Если точнее, то сравнение было с 64-бит ядром SiFive U74, которое достигает 5,1 CoreMark/МГц (на ядро). Оно тоже позиционируется как самое мощное решение RISC-V, способное исполнять полноценные ОС вроде Linux. Для сравнения — отечественный процессор Байкал-Т1, согласно нашим прошлогодним тестам, имеет производительность 5,4 CoreMark/МГц (на ядро).

onties.com Удивительным в этом сообщении наших коллег с EE Times представляется информация о 12-нм техпроцессе, который был задействован для производства XuanTie 910. Этот техпроцесс широко использует только компания GlobalFoundries. В этом случае Alibaba 100-процентно подставляется под санкции США, что нивелирует всякий смысл выбора открытой архитектуры. Впрочем, выводы делать рано, подождём подробности. Из других интересных особенностей ядер XuanTie 910 отметим 12-уровневый конвейер с внеочередным исполнением команд. За один цикл конвейер может исполнять сразу до 8 инструкций, причём и инструкции загрузки (load), и сохранения (store). Важно, что разработчики добавили в архитектуру RISC-V и процессор 50 новых расширенных инструкций для лучшей работы арифметических операций, доступа к памяти и поддержки многоядерности. Эти инструкции и ряд других решений китайцы сделают достоянием сообщества разработчиков с открытым кодом. Всё (или почти всё) будет выложено на GitHub, вероятно, в сентябре. Компании важно получить как можно более широкую поддержку со стороны независимых программистов, чему открытость RISC-V будет только способствовать. Примечательно, что новость о выходе XT 910 исчезла с сайта RISC-V Foundation через несколько часов после выхода.  Среди других заметных китайских участников RISC-V Foundation есть Huawei, MediaTek, Huami (партнёр Xiaomi), а также инвестгруппа Xiamen SIG. Сейчас Китай активно развивает импортозамещение. Согласно планам правительства, в 2020 году 40% спроса на полупроводниковую продукцию должны удовлетворить местные производители. В прошлом году, по данным TrendForce, лишь 15% пришлось на «домашние» процессоры. |

|