Материалы по тегу: cpu

|

24.03.2026 [16:58], Владимир Мироненко

CIX анонсировала Arm-процессоры ClawCore, «заточенные» под OpenClawКитайская компания CIX Technology (Cixin Technology) провела презентацию семейства процессоров ClawCore с архитектурой Armv9.2, специально разработанного для использования ИИ-агента OpenClaw, пишет CNX Software. Семейство на данный момент включает три модели: ClawCore-P, ClawCore-A и ClawCore-E. ClawCore-P — 12-ядерный процессор с тактовой частотой до 3,2 ГГц с GPU Immortalis-G720, обладающий ИИ-производительностью 45 TOPS и поддерживающий до 64 Гбайт LPDDR5. Сообщается, что характеристики ClawCore-P похожи на спецификации анонсированного ранее 6-нм процессора CIX P1 (CD8180) с 12 ядрами с архитектурой CIX P1, включая восемь производительных и четыре энергоэффективных ядра, частота которых немного меньше — до 2,8 ГГц, тоже оснащённого Immortalis-G720. ClawCore-P предназначен для сценариев с высокой степенью параллелизма и большой производительностью. Его поставки должны начаться до конца этого месяца. В июне 2026 года ожидается выпуск процессора ClawCore-A с восемью ядрами с частотой 3,0 ГГц, ИИ-производительностью 80 TOPS (расширяемой до 200 TOPS с помощью карты PCIe AI от Huomo Intelligent Technology) и поддержкой до 64 Гбайт LPDDR5. Он разработан для круглосуточной работы, поддерживает ECC, аппаратную безопасность (шифрование/управление ключами) и позволяет снизить стоимость токенов до 50 % за счёт локального инференса. На практике 80–90 % запросов будет выполняться на устройстве благодаря этой гибридной локально-онлайн реализации — крупные модели можно будет использовать через сервис Alibaba Cloud, партнёра проекта.

Источник изображения: CNX Software Выход ещё одного процессора — ClawCore-E, который предназначен для использования в периферийных устройствах и устройствах IoT, ожидается к декабрю 2026 года. Сообщается, что это «сверхэкономичный» вариант чипа, с ядрами с архитектурой Armv9.2 и NPU с поддержкой голосового управления. Глава CIX Technology заявил, что серия ClawCore охватывает различные сценарии разработки и применения ИИ, включая периферийный ИИ, высокопроизводительный ИИ и многое другое, что позволит удовлетворить потребности отраслевых партнёров в интеллектуальных продуктах для всех сценариев, от AI BOX, AI NAS и AI Mini PC до периферийных ИИ-серверов и встроенного/промышленного ИИ-оборудования: «Чтобы решить различные проблемы, возникающие в разработке ИИ-приложений, мы создали серию CIX ClawCore. Её цель — помочь разработчикам отойти от традиционной фрагментированной модели разработки и сформировать агентно-ориентированный подход к переосмыслению разработки и внедрения ИИ». Компания CIX также планирует создать полноценную экосистему вокруг OpenClaw. Она намерена предложить готовые Linux-образы и обеспечить программную поддержку с пятью ключевыми предложениями:

Процессоры будут ориентированы на платформу Arm SystemReady и поддерживать операционные системы Windows, Android, Ubuntu, Tongxin/UnionTech и Kylin.

17.03.2026 [10:21], Сергей Карасёв

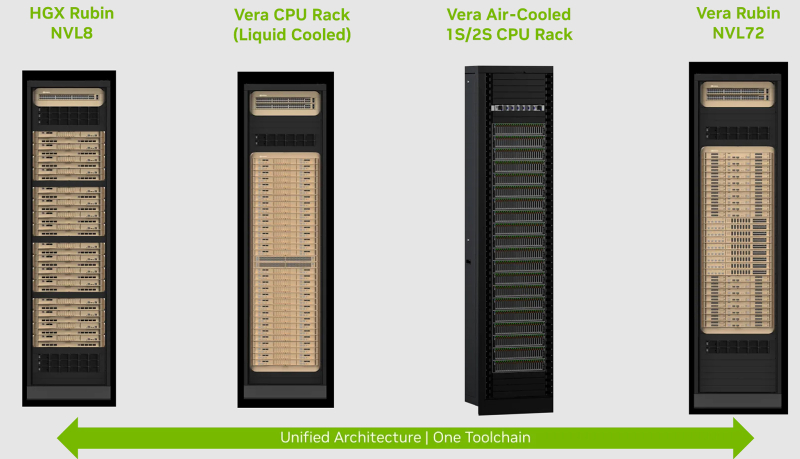

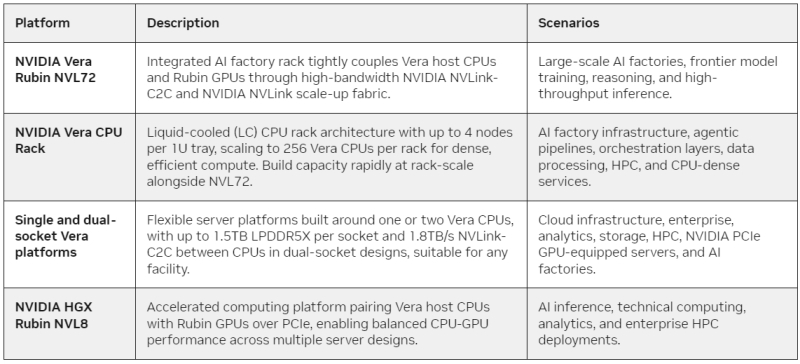

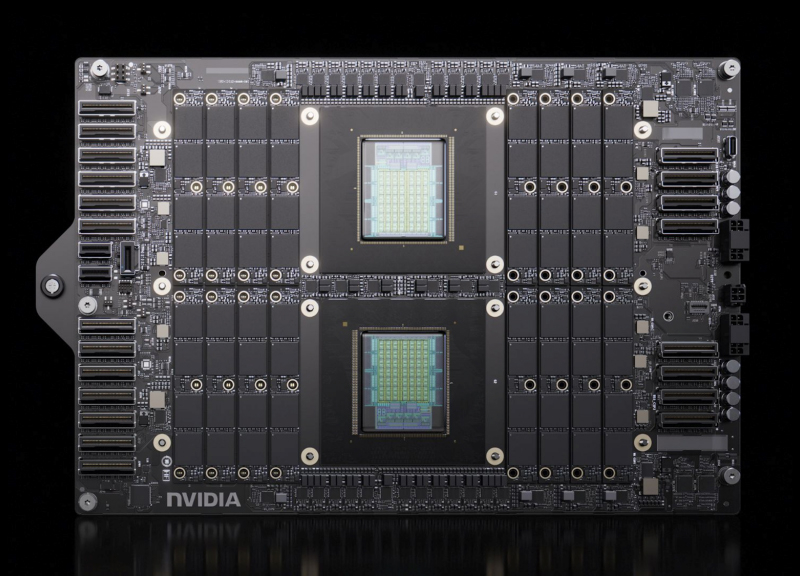

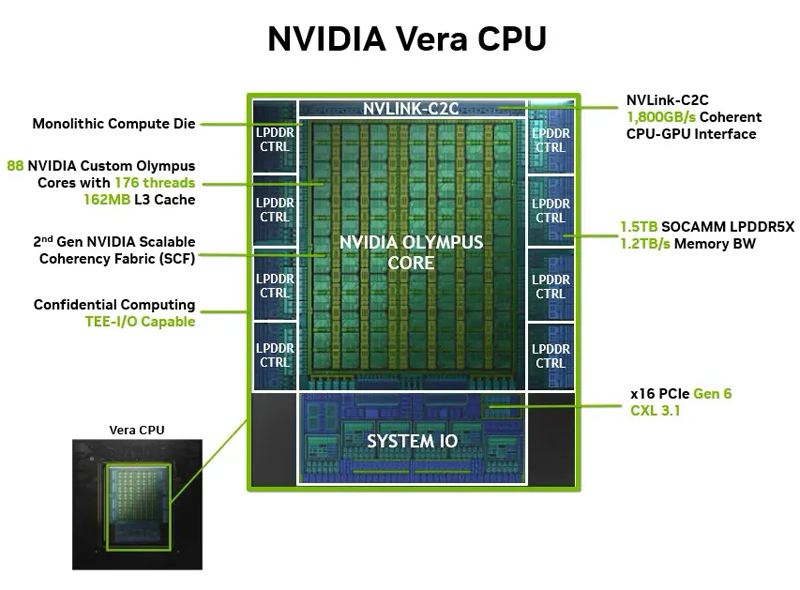

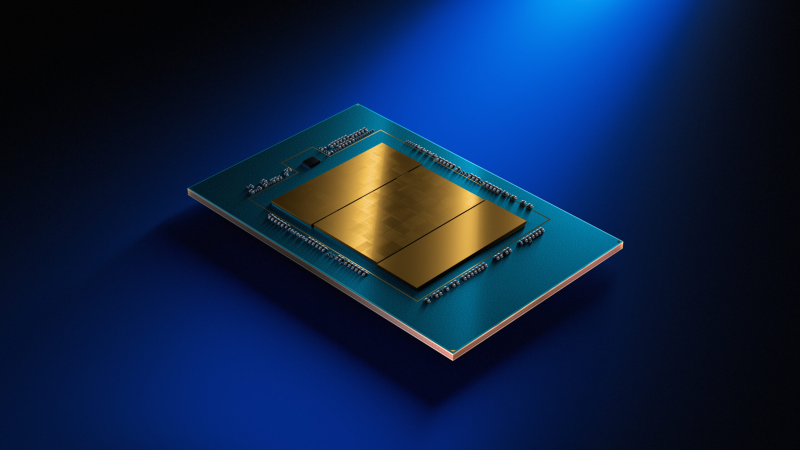

NVIDIA представила серверные Arm-процессоры Vera с 88 ядрами Olympus для ИИ и не толькоNVIDIA анонсировала процессоры Vera, спроектированные с прицелом на современные ресурсоёмкие задачи в области ИИ. Изделия, как утверждается, обеспечивают исключительную производительность каждого ядра, а также высокую пропускную способность памяти и коммутационной сети. В основу Vera положены ядра Olympus — это первые CPU-решения NVIDIA, специально разработанные для дата-центров. Olympus используют интерфейс выборки и декодирования шириной в 10 инструкций, а также нейронный алгоритм предсказания ветвлений, позволяющий оценивать два варианта ветвления за каждый цикл. Изделие полностью совместимо с набором инструкций Arm v9.2 и существующим ПО.

Источник изображений: NVIDIA Конфигурация Vera предусматривает наличие 88 ядер Olympus с возможностью одновременной обработки до 176 потоков инструкций. Объём кеша L3 составляет 162 Мбайт. Задействована шина NVIDIA Scalable Coherency Fabric (SCF) второго поколения, первоначально разработанная для CPU Grace. В составе процессора SCF отвечает за связь вычислительных ядер Olympus с общим кешем L3 и подсистемой памяти, обеспечивая стабильную задержку и пропускную способность на уровне 3,4 Тбайт/с: это позволяет использовать более 90 % пиковой пропускной способности памяти под нагрузкой. Каждому ядру Olympus доступна полоса до 14 Гбайт/с, что примерно в три раза превышает пропускную способность на ядро в традиционных CPU для дата-центров, говорит NVIDIA.  В составе Vera применяется подсистема памяти LPDDR5X на основе модулей SOCAMM. Суммарная ёмкость может составлять до 1,5 Тбайт, что втрое больше по сравнению с решениями предыдущего поколения. Пропускная способность памяти достигает 1,2 Тбайт/с, тогда как энергопотребление составляет менее 50% по сравнению с традиционными конфигурациями DDR. При этом модули SOCAMM являются заменяемыми, что упрощает модернизацию и обслуживание систем. Процессор Vera выполнен на основе единого монолитного вычислительного кристалла. Каждое ядро обеспечивается единообразной пропускной способностью. Большинство операций, чувствительных к задержкам, выполняются локально, что позволяет минимизировать межкристальный трафик, который обычно присутствует в традиционных CPU. В целом, как утверждается, реализованные архитектурные особенности позволяют чипам Vera демонстрировать до 1,5 раз более высокую производительность одного ядра по сравнению с конкурирующими решениями x86 при выполнении задач в песочнице с максимальной нагрузкой на сокет. NVIDIA разработала семейство платформ на базе Vera для решения разнообразных задач в сфере ИИ. Это, в частности, CPU-стойки с жидкостным охлаждением, а также системы с ускорителями Rubin. Устройства на базе Vera будут поставляться крупными OEM-производителями, включая Cisco, Dell, HPE, Lenovo и Supermicro. Такие машины станут доступны во II половине текущего года.

11.03.2026 [09:25], Сергей Карасёв

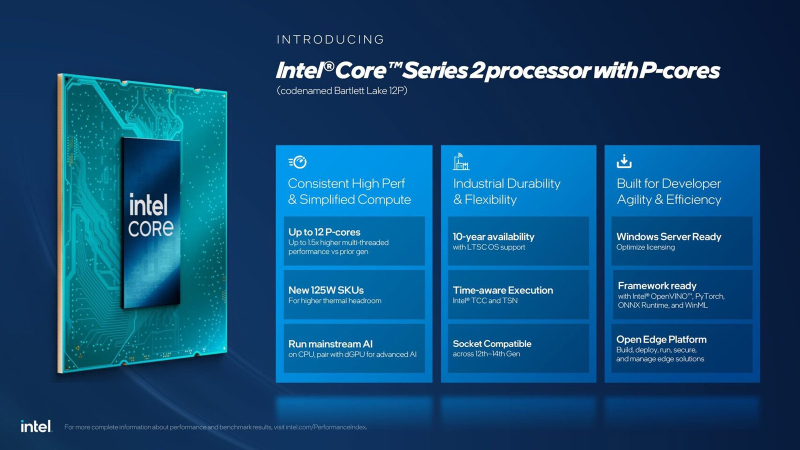

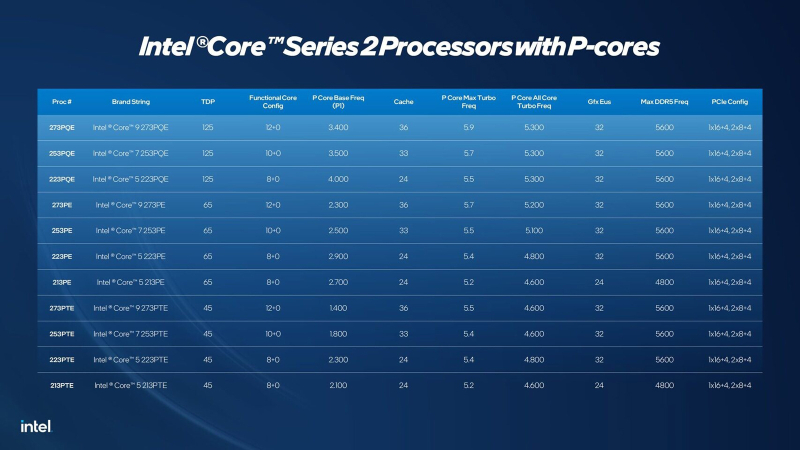

Intel выпустила Bartlett Lake — LGA 1700-процессоры исключительно на P-ядрах Raptor Cove для периферийных системКорпорация Intel в ходе конференции Embedded World 2026, которая с 10 по 12 марта проходит в Нюрнберге (Германия), анонсировала процессоры Core Series 2 семейства Bartlett Lake, рассчитанные на использование в критически важных периферийных системах и промышленном оборудовании. Представленные чипы используют исключительно производительные Р-ядра, количество которых варьируется от 8 до 12 (с возможностью обработки до 24 потоков инструкций). Показатель TDP в зависимости от модификации составляет 45, 65 или 125 Вт. На сегодняшний день в семейство Core Series 2 входят 11 процессоров (см. технические характеристики ниже). Их базовая тактовая частота варьируется от 1,4 до 3,5 ГГц, максимальная частота — от 5,2 до 5,9 ГГц (в турбо-режиме). Объём кеша — от 24 до 36 Мбайт. Чипы могут использовать до 192 Гбайт оперативной памяти DDR5-5600 или DDR4-3200 с поддержкой ECC. В состав изделий входит ускоритель UHD Graphics 770; возможен вывод изображения одновременно на четыре дисплея (вплоть до 4К). Процессоры предлагают до 20 линий PCIe (16 × PCIe 5.0 и 4 × PCIe 4.0). Упомянута поддержка высокоскоростной шины DMI 4.0 (Direct Media Interface 4.0). Кроме того, говорится о совместимости с чипами Core 12-го, 13-го и 14-го поколений для периферийных устройств, что должно упростить модернизацию существующих встраиваемых систем на базе LGA1700. По заявлениям Intel, процессоры Core Series 2 обеспечивают прирост производительности до 1,8 раза (TOPS) по сравнению с решениями предыдущего поколения. Новые чипы оптимизированы для работы с операционными системами реального времени (RTOS). Сопутствующий чипсет Intel PCH обеспечивает поддержку до 12 линий PCIe 4.0 и до 16 линий PCIe 3.0, Wi-Fi 7 и Bluetooth 5.4, 2.5GbE и пр.

10.03.2026 [12:50], Сергей Карасёв

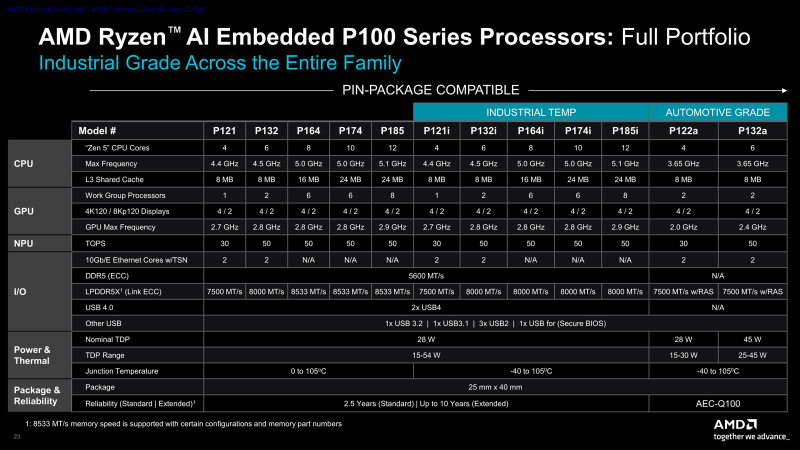

AMD пополнила семейство процессоров Ryzen AI Embedded P100 моделями, насчитывающими до 12 ядерКомпания AMD расширила ассортимент процессоров Ryzen AI Embedded P100, анонсировав модели, насчитывающие до 12 вычислительных ядер. Изделия оптимизированы для применения в промышленном секторе: они подходят для решения широкого спектра ИИ-задач на периферии, включая машинное зрение, автоматизацию, 3D-визуализацию и пр. Чипы Ryzen AI Embedded P100 дебютировали в январе нынешнего года. Изначально были выпущены модели с четырьмя и шестью ядрами. Теперь к ним добавились более производительные решения — процессоры P164/P164i, P174/P174i и P185/P185i с 8, 10 и 12 ядрами соответственно. Используется архитектура Zen 5. Номинальный показатель TDP находится на уровне 28 Вт, величина cTDP варьируется от 15 до 54 Вт. Диапазон рабочих температур простирается от 0 до +105 °C, а у версий с индексом «i» — от -40 до +105 °C. В состав изделий входят графический блок AMD RDNA 3.5 и нейронный узел (NPU) на архитектуре AMD XDNA 2 для ускорения выполнения задач ИИ. Суммарная ИИ-производительность (на уровне процессора) достигает 80 TOPS. Максимальная тактовая частота у новых процессоров составляет 5,0–5,1 ГГц, объём кеша L3 — 16 или 24 Мбайт (см. технические характеристики ниже). Возможно использование оперативной памяти LPDDR5X-8533 или DDR5-5600. Говорится о поддержке 16 линий PCIe 4.0, интерфейсов USB4, USB 3.2, USB 3.1 и USB 2.0. Упомянута совместимость с открытой программной экосистемой AMD ROCm. Процессоры Ryzen AI Embedded P100 рассчитаны на эксплуатацию в круглосуточном режиме. Пробные поставки изделий уже начались, а массовые отгрузки запланированы на июль нынешнего года.

09.03.2026 [16:39], Владимир Мироненко

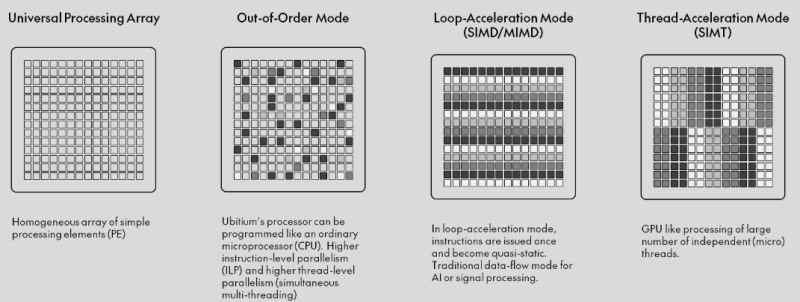

Ubitium стала на шаг ближе к выпуску универсального RISC-V процессора, заменяющего CPU, GPU, DSP и FPGAНемецкий стартап Ubitium объявил о завершении стадии tape-out (финальный этап проектирования) универсального RISC-V-процессора, изготовленного по 8-нм техпроцессу Samsung Foundry и предназначенного для рынка встроенных вычислительных систем автомобилей, промышленного оборудования и бытовой электроники, включая радарные и многосенсорные сигнальные цепи, аудио и голосовую связь в реальном времени, компьютерное зрение, периферийный ИИ, промышленный человеко-машинный интерфейс (HMI) и т.д. В основе процессора Ubitium лежит «универсальный процессорный массив» (Universal Processing Array) — программно-определяемая система с 256 элементами, объединяющая функции CPU, GPU, DSP и FPGA и способная мгновенно менять режимы выполнения во время работы. Такая унификация позволяет чипу переключаться между режимом работы в качестве CPU общего назначения для обслуживания ОС и режимом работы в качестве ИИ-ускорителя, избегая задержек при передаче данных между отдельными чипами.

Источник изображения: Ubitium Завершение tape-out на 8-нм техпроцессе Samsung подтверждает работоспособность основного процессорного массива и интерфейса LPDDR5. Для Ubitium доказательство того, что один процессор может обрабатывать общие вычислительные задачи, задачи обработки в реальном времени и задачи ИИ на одном кристалле, является важным шагом на пути к коммерческой жизнеспособности, отметил EE Times. «Это решение претворяет давно существующую концепцию в жизнь», — заявил Мартин Форбах (Martin Vorbach), технический директор Ubitium. «Встроенные системы переросли архитектуры, на которые сегодня опирается отрасль. Консолидация больше не является необязательной. Она неизбежна», — добавил он. Технология, лежащая в основе этого проекта, совершенствовалась более 15 лет. Для её воплощения в жизнь Форбахом совместно с рядом специалистов была создана в 2024 году компания Ubitium. Ускорить разработку позволило привлечение $3,7 млн в рамках посевного раунда в конце прошлого года, который совместно возглавили Runa Capital, Inflection и KBC Focus Fund. Инвестиции позволили Ubitium проверить архитектуру и подготовить наборы для разработки (IDK) для первых клиентов. «Индустрия процессоров объёмом $500 млрд построена на жёстких границах между вычислительными задачами», — сказал Хён Шин Чо (Hyun Shin Cho), генеральный директор Ubitium и соучредитель. — Мы стираем эти границы. Наш универсальный процессор делает всё — CPU, GPU, DSP, FPGA — на одном чипе, в одной архитектуре. Это не просто постепенное улучшение. Это смена парадигмы. Это архитектура процессора, которую требует эпоха ИИ». Как отметил EE Times, завершение tape-out продукта — это не просто большая победа для Ubitium. Это также поворотный момент для экосистемы RISC-V. Открытая архитектура RISC-V используется большей частью для создания обычных ядер, которые полагаются на внешние ускорители для сложных рабочих нагрузок. Ubitium расширяет границы использования архитектуры, сохраняя полную совместимость с RISC-V. Процессор поддерживает стандартные наборы инструментов RISC-V для разработки ПО и может работать под управлением Linux и RTOS. Кроме того, унифицированный программный стек устраняет необходимость в компиляторах для конкретного поставщика или проприетарных языках, что позволяет быстро внедрять инновации и сократить время разработки. Компания сотрудничает с Samsung Foundry и ADTechnology для завершения проектирования и с Siemens Digital Industries Software — для проверки микросхемы (pre-silicon validation). Вторая стадия tape-out запланирована на конец этого года, а серийное производство начнётся в 2027 году, сообщила компания.

26.02.2026 [10:12], Сергей Карасёв

AMD анонсировала процессоры EPYC 8005 Sorano для телеком- и периферийного оборудованияКомпания AMD анонсировала процессоры EPYC 8005 с кодовым именем Sorano. Эти чипы предназначены для применения в телекоммуникационном оборудовании, а также в системах на периферии. Изделия EPYC 8005 придут на смену процессорам EPYC 8004 Siena, выпущенным в 2023 году. Эти CPU насчитывают от 8 до 64 вычислительных ядер с поддержкой многопоточности. Показатель TDP варьируется от 80 до 200 Вт. Технические характеристики EPYC 8005 пока полностью не раскрываются. Известно, что новые чипы получат до 84 ядер на архитектуре Zen 5. Максимальный показатель TDP составит 225 Вт. В Sorano реализованы средства оптимизации для операций декодирования с малой плотностью проверок на чётность (LDPC), направленные на снижение задержки и ускорение коррекции ошибок в сетях 5G. Как отмечает ресурс The Register, в конструктивном плане решения EPYC 8005 могут состоять из шести чиплетов Zen 5c с оптимизацией по плотности, в которых будут активированы по 14 из 16 ядер. Альтернативный вариант — 12 чиплетов Zen 5 с оптимизацией по частоте, в каждом из которых будут активны семь ядер из восьми. Новые процессоры ориентированы на односокетные серверы. По заявлениям AMD, чипы обеспечивают высокую производительность при низком энергопотреблении. Изделия спроектированы для сложных условий эксплуатации на периферии сети: они имеют широкий диапазон рабочих температур. Решения EPYC 8005 могут применяться в рамках следующей фазы развития открытых и виртуализированных сетей радиодоступа (RAN). О поддержке процессоров сообщили такие компании, как Ericsson, Samsung Electronics, Supermicro и Wind River.

17.02.2026 [13:57], Владимир Мироненко

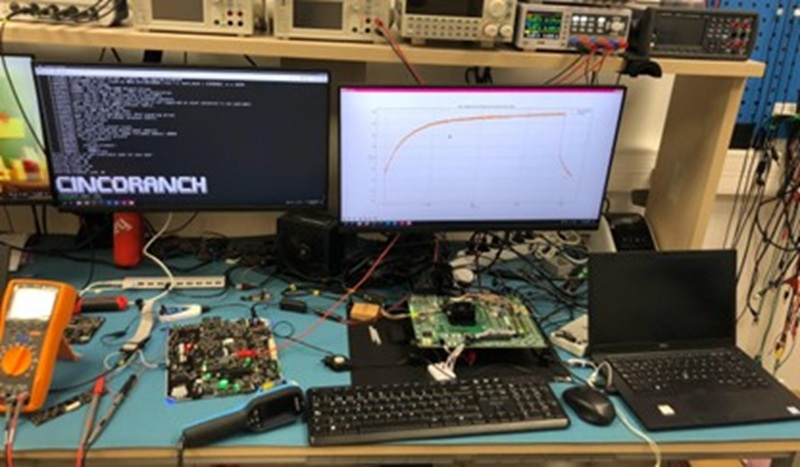

Первый европейский суверенный RISC-V-процессор Cinco Ranch изготовлен по техпроцессу Intel 3Лаборатория суперкомпьютерных вычислений (BZL) Национального центра суперкомпьютерных вычислений Барселоны (BSC-CNS) сообщила об успешном запуске тестового чипа Cinco Ranch TC1 на архитектуре RISC-V, изготовленного по передовому техпроцессу Intel 3. В заявлении отмечено, что результаты подтверждают надёжность конструкции и жизнеспособность вычислительной архитектуры на базе открытой платформы RISC-V. «Это достижение является ключевым этапом в процессе разработки чипа и качественным скачком на пути к суверенным суперкомпьютерным технологиям в Европе», — подчеркнула BZL, отметив, что готовый чип предлагает открытую, гибкую альтернативу, свободную от зависимости от проприетарных архитектур крупных транснациональных корпораций. Проект связан с Европейской инициативой по процессорам (EPI), целью которой является разработка отечественных процессоров для будущих европейских суперкомпьютеров и промышленных систем. «Успешная стабильная загрузка Linux и проверка достижения чипом ожидаемых частот подтверждают зрелость конструкции и качество работы, проделанной командами BZL», — говорит исследователь BSC и координатор аппаратной части лаборатории Zettascale в Барселоне. Cinco Ranch TC1 — это первый чип, произведенный в академической среде с использованием 3-нм техпроцесса Intel 3. На этапе проектирования, из-за невозможности прямого доступа к этой технологии, BZL провела внутренние оценки на сопоставимом техпроцессе TSMC N7, что позволило оценить конструкцию перед окончательной реализацией. Сообщается, что структура Cinco Ranch TC1 основана на трёх взаимодополняющих процессорных блоках, предназначенных для совместной работы и охвата различных вычислительных профилей. В чипе используются три блока RISC-V на одном кристалле, каждый из которых ориентировано на специализированные рабочие нагрузки. Три ядра используют микроархитектуры Sargantana, Lagarto Ka и Lagarto Ox, с основным упором на эффективность, векторные нагрузки и скалярную обработку соответственно. Подсистема CPU занимает всего 3,2 мм² на крошечном кристалле площадью 15,2 мм², который также включает высокоскоростные интерфейсы, такие как PCIe 5.0 и DDR5. Для сравнения, площадь CCD восьмиядерного процессора AMD Zen 5 составляет около 71 мм², и для этого чиплета также требуется отдельный кристалл I/O, отметил ресурс HotHardware.com.  Cinco Ranch TC1 был протестирован на оценочной плате Hawk Canyon V2, разработанной Intel для первоначальной проверки чипа после его производства. Следующим этапом станет функциональное тестирование и тестирование производительности, оптимизация ПО и полная проверка системы. В мае 2025 года на Cinco Ranch TC1 (Test Chip 1) была успешно загружена ОС Linux, а в июле 2025 года, после получения партии из 500 чипов, начались работы по характеризации и проверке. Вся партия продемонстрировала высокую функциональную производительность, при этом большинство устройств успешно запустили все три интегрированных процессора чипа. Также результаты тестов подтверждают, что Cinco Ranch TC1 работает на частоте до 1,25 ГГц, что превышает консервативные оценки, сделанные на этапе проектирования. Для BZL и её партнёров это достижение является важной вехой и доказательством того, что разработанные в Европе процессоры с открытой ISA могут быть реализованы на передовых технологиях производства и воплощены в реальных кремниевых решениях. Для Европы — это значимый шаг к технологической автономии в HPC. А для Intel это демонстрация того, что её бизнес может оказывать всестороннюю поддержку передовым внешним клиентам в сложных гетерогенных проектах.

16.02.2026 [10:11], Сергей Карасёв

Китайская Montage Technology выпустила серверные процессоры Jintide на базе Intel Xeon 6Китайская компания Montage Technology, на днях осуществившая первичное публичное размещение акций (IPO) на Гонконгской фондовой бирже, выпустила серверные процессоры Jintide следующего поколения, в основу которых положена архитектура Intel Xeon 6, доработанная под требования заказчиков в КНР. В частности, вышли изделия Jintide C6P, которые фактически представляют собой процессоры Intel Xeon 6 семейства Granite Rapids-SP на базе производительных ядер P-core. Их количество в китайских чипах достигает 86 с возможностью одновременной обработки до 172 потоков инструкций, а максимальный объем кеша L3 составляет 336 Мбайт. Реализована 8-канальная подсистема памяти DDR5 с поддержкой модулей RDIMM-6400 и MRDIMM-8000. Процессоры Jintide C6P могут применяться в одно- и двухсокетных конфигурациях. Говорится о поддержке 88 линий PCIe 5.0 и протокола CXL 2.0. Пропускная способность шины UPI достигает 24 ГТ/с. Обеспечивается полная совместимость с набором инструкций x86. Чипы ориентированы на дата-центры и облачные инфраструктуры с высокой вычислительной нагрузкой. Кроме того, дебютировали решения Jintide C6E — это модифицированные изделия Intel Xeon 6 Sierra Forest-SP с энергоэффективными ядрами E-core: их количество достигает 144. Размер кеша L3 составляет до 108 Мбайт. Процессоры имеют восемь каналов памяти DDR5-6400 и до 88 линий PCIe 5.0. Упомянута поддержка CXL 2.0 и шины UPI с пропускной способностью до 24 ГТ/с. Решения Jintide C6E могут устанавливаться в одно-и двухсокетные системы. Компания также анонсировала чип Jintide M88STAR5(N), на основе которого реализуются различные функции безопасности. Изделие, использующее технологию Mont-TSSE (Trust & Security System Extension), отвечает за аппаратное шифрование/дешифрование данных в соответствии с местными стандартами и доверенные вычисления. На кристалле присутствуют нескольких генераторов случайных чисел, а общая пропускная способность достигает 160 Гбит/с через PCIe 5.0 х8. Упомянута поддержка стандартов TPM, TCM и TPCM, а также интерфейсов SMBus, I3C, UART, SPI и GPIO. Наконец, Montage Technology представила чип Jintide M88IO3032 IOH (I/O Hub), предназначенный для использования с CPU нового поколения. Изделие обеспечивает поддержку PCIe 3.0, SATA 3.2 (до 20 портов; RAID 0/1/5/10), USB 3.2/2.0 и пр.

05.02.2026 [12:31], Руслан Авдеев

Omdia прогнозирует рост цен на всё более дефицитные серверные CPUВ 2026 году дата-центры могут столкнуться не только с уже имеющимся дефицитом памяти, но и не менее серьёзной проблемой, связанной с ограничением поставок классических серверных процессоров, сообщает The Register со ссылкой на аналитику Omdia. Тем не менее, эксперты ожидают, что поставки будут расти двузначными темпами. В обзоре Cloud and Datacenter Market Snapshot компания Omdia сообщила, что серверных CPU тоже не хватает и это, вероятно, приведёт к росту цен и увеличению общей стоимости вычислительных систем. По мнению экспертов, как минимум отчасти это связано со сложностью переноса объёмов производства между разными техпроцессами. По мере масштабирования планов производителям CPU приходится выпускать продукцию на разных техпроцессах, например 3 нм и 5 нм. При этом перераспределение объёмов производства между разными технологическими линиями — процесс довольно сложный и трудоёмкий. Дефициту может способствовать и более высокий, чем ожидалось, процент брака готовой продукции.

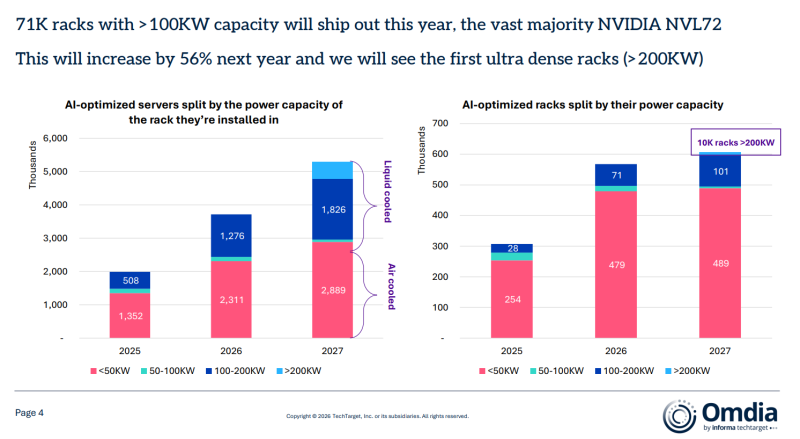

Источник изображения: Intel Как считает Omdia, в результате цены на серверные процессоры, возможно, вырастут на 10–15 % из-за дефицита предложения. Стоит учесть, что крупнейшие клиенты имеют долгосрочные соглашения с производителями с фиксированными ценами, иначе прогнозы были бы ещё хуже. Вместе с тем акции AMD и Intel упали из-за слабого, по мнению инвесторов, прогноза. Любые проблемы с CPU усугубят непростую ситуацию в цепочке поставок IT-оборудования. На фоне дефицита цены на DRAM-модули в данном квартале, вероятно, почти удвоятся, а цены на память NAND вырастут более чем на 30 %. Обычная DRAM оказалась в дефиците не в последнюю очередь потому, что производители перепрофилировали свои мощности на выпуск высокорентабельных продуктов — HBM-модулей для ИИ-ускорителей. Omdia обеспокоена тем, что дефицит оперативной памяти может сказаться на темпах производства серверов, что способно повлиять на сроки завершения уже реализуемых проектов ЦОД. Тем не менее, эксперты прогнозируют рост поставок серверов в 2026 году на 12 %. Основным драйвером выступает «цикл обновления» — необходимость закупки новых серверов общего назначения, что будет способствовать увеличению их поставок. При этом дефицит памяти называется большей угрозой, чем нехватка процессоров. Что касается стоек с серверами на базе ИИ-ускорителей, Omdia предполагает, что в 2026 году будет поставлено не менее 71 тыс. единиц с IT-нагрузкой более 100 кВт, в основном на базе систем NVIDIA NVL72. Благодаря высокому спросу на ИИ-инфраструктуру, Omdia ожидает, что в следующем году спрос увеличится ещё на 56 %, появятся и первые «сверхплотные» стойки мощностью более 200 кВт и дело на этом, вероятно, не закончится.

03.02.2026 [11:33], Сергей Карасёв

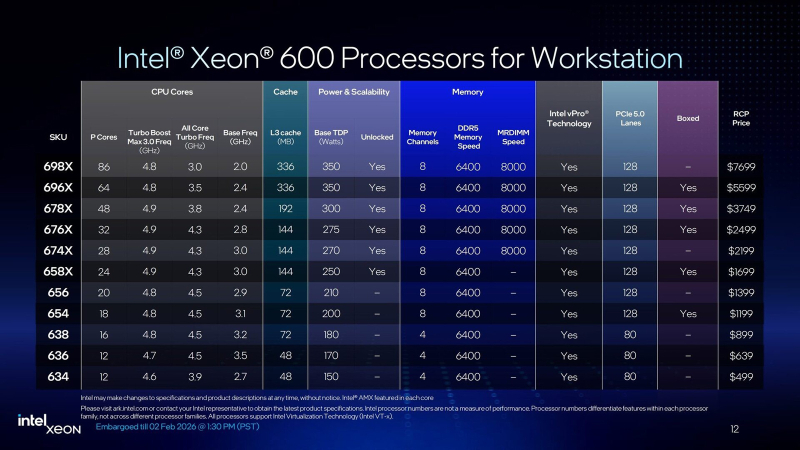

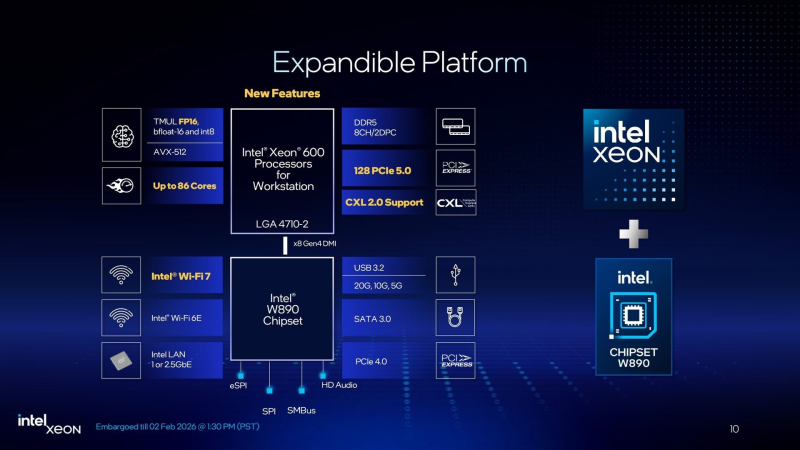

86 P-ядер, 128 линий PCIe 5.0 и 8 каналов DDR5-6400/8800: Intel представила чипы Xeon 600 для рабочих станцийКорпорация Intel представила процессоры семейства Xeon 600 для рабочих станций. В основу чипов положена архитектура Xeon 6700P Granite Rapids. Изделия приходят на смену Xeon W-2500/W-3500 (Sapphire/Emerald Rapids), которые дебютировали летом 2024 года. Процессоры Xeon 600 содержат вычислительные ядра Redwood Cove, количество которых варьируется от 12 до 86. Для сравнения, решения Xeon W-3500 насчитывают максимум 60 ядер. Важно отметить, что задействованы исключительно производительные Р-ядра (энергоэффективные Е-ядра в конструкцию не входят). Благодаря технологии многопоточности возможна обработка одновременно до 172 потоков инструкций. Базовая тактовая частота у новых CPU варьируется от 2,0 ГГц до 3,5 ГГц, а частота в турбо-режиме — от 4,6 до 4,9 ГГц. Объём кеша третьего уровня составляет от 48 до 336 Мбайт, показатель TDP — от 150 до 350 Вт. В серию вошли модели с разблокированным множителем для разгона («Х» в обозначении). Чипы Xeon 630 начального уровня предлагает четыре канала памяти DDR5 и 80 линий PCIe 5.0, в то время как более мощные процессоры Xeon 650/670/690 содержат восемь каналов памяти и 128 линий PCIe 5.0. Говорится о возможности использования модулей RDIMM-6400 и MRDIMM-8000 (только Xeon 670/690). Максимально допустимый объём ОЗУ составляет 4 Тбайт. Реализована поддержка CXL 2.0, что позволяет формировать дополнительны пулы памяти. По заявлениям Intel, по сравнению с процессорами для рабочих станций предыдущего поколения прирост производительности в однопоточном режиме у Xeon 600 составляет до 9 %, в многопоточном режиме — до 61 %. Улучшения затронули встроенный аппаратный ускоритель Intel AMX (Advanced Matrix Extensions), предназначенный для повышения производительности в задачах ИИ, глубокого обучения и анализа данных. Если ранее он поддерживал операции INT8 и BFloat16, то теперь добавлен режим FP16. Среди прочего упомянуты технологии Intel vPro Enterprise и Intel Deep Learning Boost.

В паре с процессорами Xeon 600 будет использоваться новый набор логики Intel W890. Для подключения к CPU служит канал DMI 4.0 x8, обеспечивающий пропускную способность немногим менее 16 Гбайт/с. Чипсет предусматривает поддержку интерфейса USB 3.2 Gen 2×2 (20 Гбит/с), портов SATA-3, дополнительных линий PCIe 4.0, сетевых интерфейсов 1GbE и 2,5GbE, а также Wi-Fi 7. При заказе процессоров Xeon 600 корпорация Intel призывают клиентов убедиться, что новая платформа подходит для их рабочих нагрузок. Чипы поступят в продажу в конце марта по цене от $499 до $7699. Некоторые модели будут доступны в коробочной версии: это изделия Xeon 654 (18 ядер), Xeon 658X (24 ядра), Xeon 676X (32 ядра), Xeon 678X (48 ядер) и Xeon 696X (64 ядра). Материнские платы на чипсете W890 готовят такие компании, как ASUS, Supermicro и Gigabyte. Готовые системы на основе Xeon 600 предложат Dell, HP, Supermicro, Boxx, Pudget Systems и другие поставщики. Вместе с тем, как отмечает The Register, время для анонса Xeon 600 выбрано не совсем удачно. Чипы выходят на рынок на фоне проблем с цепочками поставок, из-за которых резко подскочили цены на память. Так, комплект из восьми модулей DDR5 RDIMM на 32 Гбайт каждый обойдётся более чем в $4000: это примерно на $1500 больше, чем шестью месяцами ранее. Сформировавшаяся ситуация может негативно отразиться на спросе на Xeon 600 среди потребителей. |

|