Материалы по тегу: cpu

|

10.06.2022 [03:30], Игорь Осколков

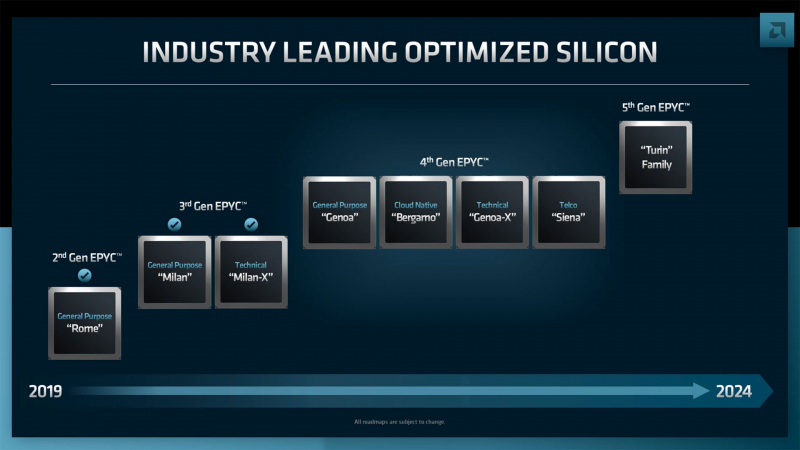

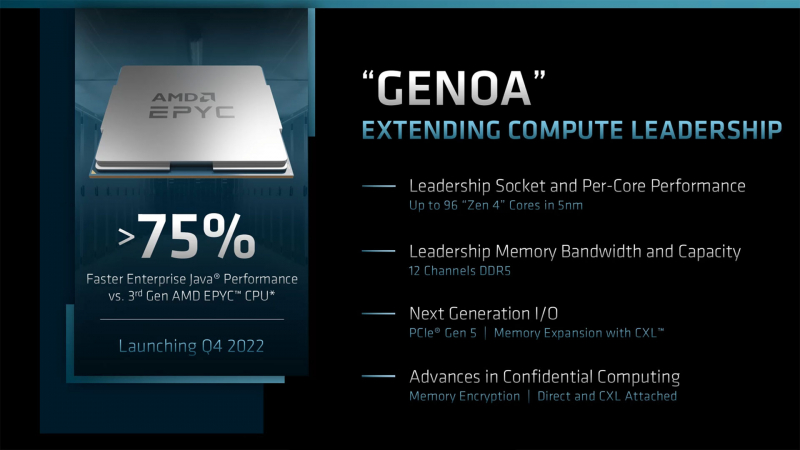

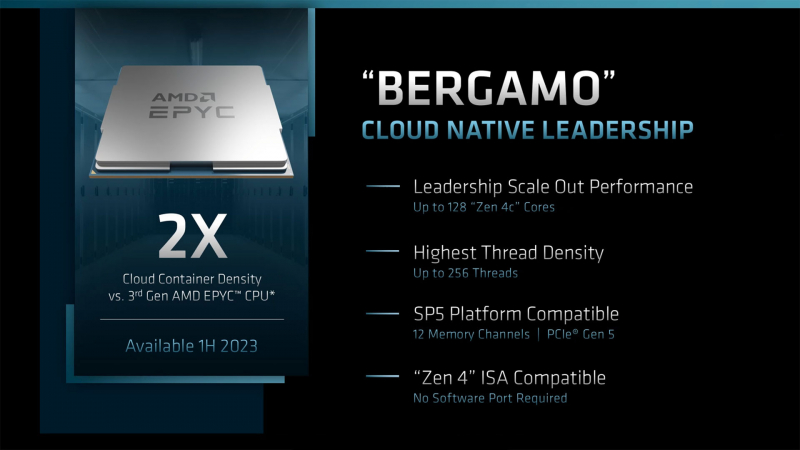

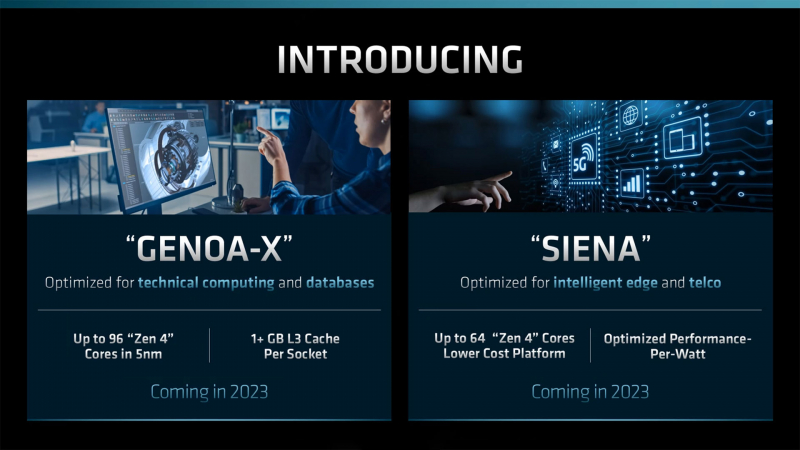

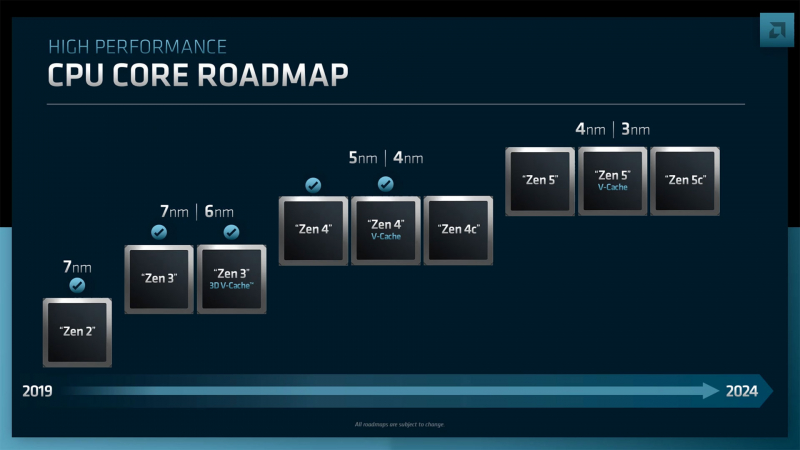

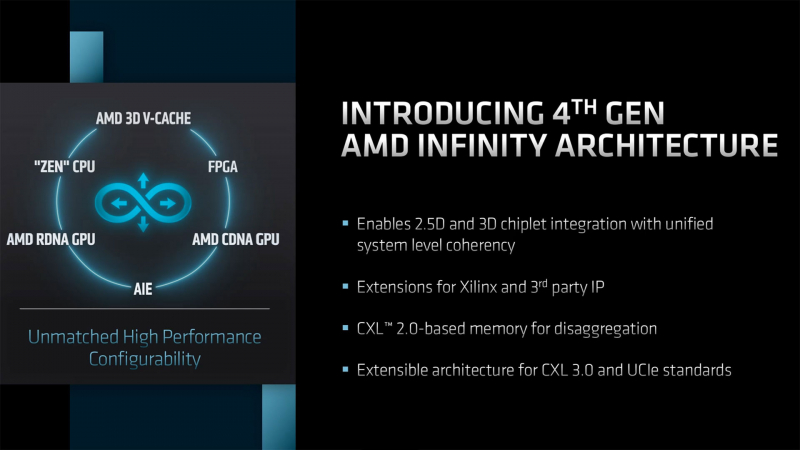

AMD анонсировала серверные процессоры EPYC Genoa-X, Siena и TurinНа прошедшем этим вечером отчётном мероприятии Financial Analysts Day 2022 компания AMD поделилась планами по дальнейшему развитию серверных процессоров EPYC. Речь шла как об уже анонсированных продуктах, так и о совершенно новых, предназначенных для неосвоенных ранее компанией сегментов. Наиболее значимым, хотя и наименее детальным, стал официальный анонс пятого поколения AMD EPYC под кодовым именем Turin (EPYC 7005), которое должно появиться до конца 2024 года. Они будут основаны на существенно переработанной архитектуре Zen 5 и изготавливаться по смешанному 3- и 4-нм техпроцессу. Обещано три разновидности кристаллов: обычные, с 3D V-Cache и «облачные» (Zen 5c), оптимизированные для повышения плотности размещения. Важно тут то, что таким образом сохранится преемственность между поколениями, что определённо порадует заказчиков. Но в ближайшее время нас ждёт выход AMD EPYC Genoa, который должен состояться в IV квартале текущего года. Эти 5-нм процессоры получат до 96 ядер Zen 4, 12 каналов DDR5, поддержку PCIe 5.0 и CXL. Причём сейчас уже явно говорится о возможности расширения системной памяти с помощью CXL. Переход на новый техпроцесс и увеличившееся в 1,5 раза количество ядер дали прирост производительности до +75% (в пример приводится тест Java SPECjbb). Для Genoa потребуется новый сокет SP5 (LGA6096). Он же будет готов принять ещё два варианта процессоров. Первый — это новенький Genoa-X, по названию которого легко догадаться, что это тот же Genoa (тоже до 96 ядер), снабжённый расширенным L3-кешем 3D V-Cache (от 1 Гбайт и более). Как и Milan-X, он будет ориентирован на специфический класс нагрузок, которые выигрывают от увеличения доступного объёма кеша. Это, например, расчётные задачи и СУБД. Genoa-X появятся в 2023 году. Тогда же стоит ждать и особую серию Bergamo. Эти процессоры, как и было обещано ранее, получат до 128 ядер (и 256 потоков), сохранив совместимость с сокетом SP5. Основаны они будут на 5-нм ядрах Zen 4c, который чем-то напоминают E-ядра в исполнении Intel. Однако набор команд у Zen 4c будет одинаков с Zen 4. Деталей устройства c-ядер AMD снова не раскрыла, но можно предположить, что у них переработана иерархия кешей. Предназначены они для гиперскейлеров, которым важна плотность размещения ресурсов, а не только производительность В 2023 году появятся и «малые» EPYC’и под кодовым названием Siena. Они оптимизированы с точки зрения энергоэффективности и предлагают до 64 ядер Zen 4. Siena ориентированы на периферийные вычисления и телеком-сегмент. Подробностей о них пока тоже мало. Не исключено, что мы увидим и гибриды наподобие Ice Lake-D, включающие интегрированные «умные» сетевые контроллеры. Существенным для всех новинок станет использование архитектуры Zen 4 (4 и 5 нм), которая, помимо ожидаемого прироста производительности, получит новые возможности. Среди них — поддержка AVX-512 (возможно, не самого полного набора) и новых инструкций для ИИ-нагрузок, которыми Intel хвасталась в течение нескольких лет. Но что ещё более важно, Zen 4 получат четвёртое поколение интерконнекта Infinity Architecture, который позволит более плотно связать различные чиплеты, причём и на уровне «кремния» (2.5D- и 3D-упаковка). А это открывает путь к эффективной компоновке различных функциональных модулей с поддержкой когерентности на уровне всего чипа — AMD подтвердила возможность интеграции FPGA Xilinx и IP-блоков сторонних компаний. Новый интерконнект также совместим с CXL 2.0, что важно для работы с памятью, а будущие версии получат поддержку CXL 3.0 и UCIE. Именно четвёртое поколение Infinity позволило AMD создать свои первые серверные APU Instinct MI300.

09.06.2022 [21:00], Алексей Степин

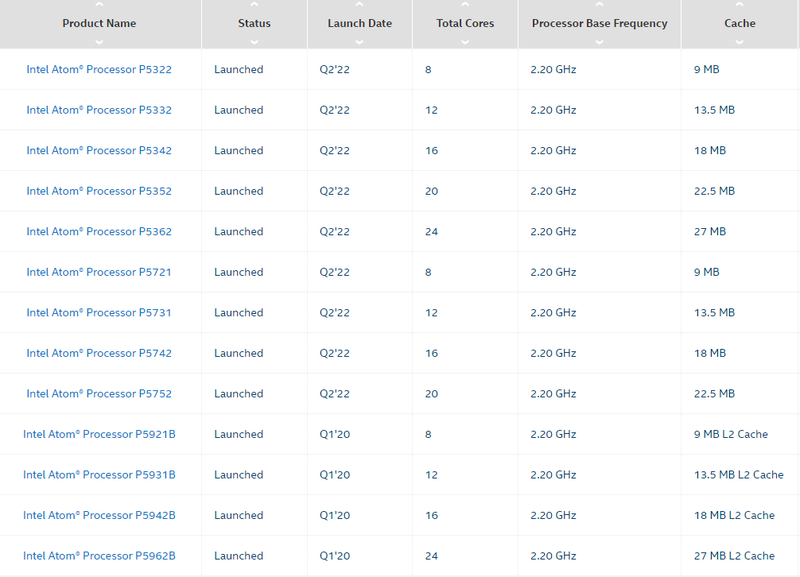

Серия процессоров Intel Atom P5000 Snow Ridge пополнилась новыми моделямиКорпорация Intel на этой неделе уделила немало внимания серии экономичных процессоров Atom. Помимо новых моделей в серии C5000 Parker Ridge появились и новые чипы в семействе P5000 Snow Ridge. Эта 10-нм SoC-платформа дебютировала в 2020 году, её главное назначение — использование в беспроводном 5G-оборудовании, а главной отличительной особенностью можно назвать развитую сетевую подсистему. Последняя предлагает тесную интеграцию со 100GbE-контроллером Intel Ethernet 800 с поддержкой коммутации и технологии QAT. Изначально в серии было всего четыре модели с номерами серии P5900, количеством ядер Tremont от 8 до 24 и литерой B в названии — от «Base Station». Теперь семейство пополнилось девятью новыми моделями с индексами от P5300 до P5700. Сравнить характеристики всех чипов P5000 можно на сайте Intel, воспользовавшись этой ссылкой.

Модельный ряд Intel Atom P5000. Источник: Intel Хотя базовая частота у всех новинок осталась прежней и составляет 2,2 ГГц, объём кеша на кластер из четырёх ядер равен 4,5 Мбайт, а количество линий PCIe составляет 32 шт., есть и отличия. Для новых моделей заявлена поддержка вдвое большего максимального объёма оперативной памяти, 256 Гбайт против 128 Гбайт у чипов с литерой B. Есть и некоторые изменения в подсистеме памяти: младшие версии с номерами P5300 поддерживают либо DDR4-2400, либо 2666, тогда как для P5700 сохранена поддержка DDR4-2933.

Intel NetSec Accelerator card. Источник: Intel (via ServeTheHome) Теплопакеты достаточно высокие, от 48 до 83 Вт, что отчасти продиктовано наличием продвинутой сетевой подсистемы. Она может быть сконфигурирована в различных режимах, у P5300 это от 8×10GbE до 1×100GbE, P5700 может поддерживать от 8 портов 25GbE с шифрованием, а в режиме 2×100GbE один порт обязательно будет резервным. Сетевой движок QAT третьего поколения сохранился у всех моделей. Режим коммутатора доступен только для P5700.

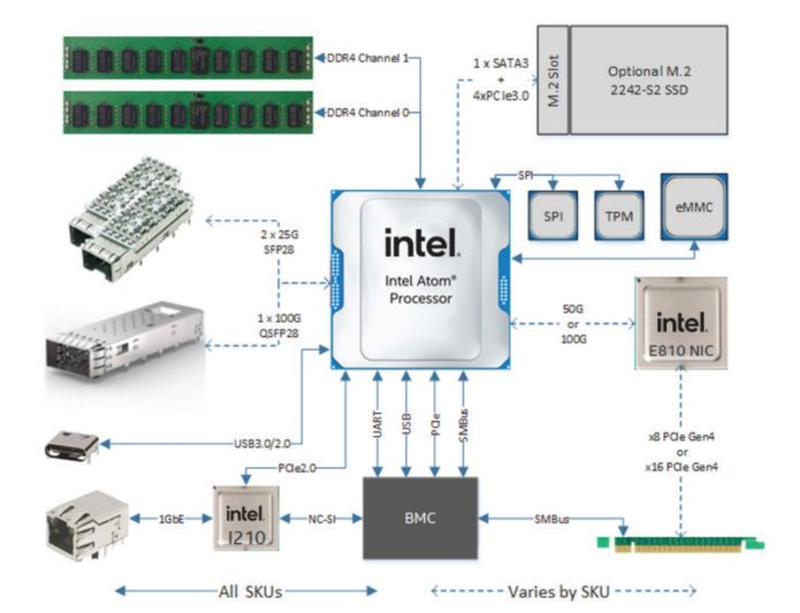

Intel NetSec — полноценная x86-система в виде PCIe-адаптера. Источник: Intel (via ServeTheHome) Новые процессоры Intel Atom P5000 могут служить и основой для современных сетевых ускорителей — компания продемонстрировала плату NetSec Accelerator, спроектированную Silicom и несущую на борту 8-ядерный P5721 или 16-ядерный P5742. Ускоритель имеет либо 2 корзины SFP28 (25GbE), либо корзину QSFP28 (100GbE), свой BMC и опциональный накопитель M.2 2242 в дополнение к 256 Гбайт набортной eMMC. По сути, это полноценная x86-платформа в форм-факторе PCIe-платы. Интерфейс, в зависимости от модели, PCIe 4.0 x8, либо x16, теплопакет у старшего варианта может достигать 115 Вт, поэтому плата использует дополнительное питание. Производительность в дуплексном режиме с полноценным шифрованием в реальном времени — 25 и 50 Гбит/с. Интересно, что новинка не позиционируется как IPU, но и термин DPU компанией не используется.

09.06.2022 [16:37], Сергей Карасёв

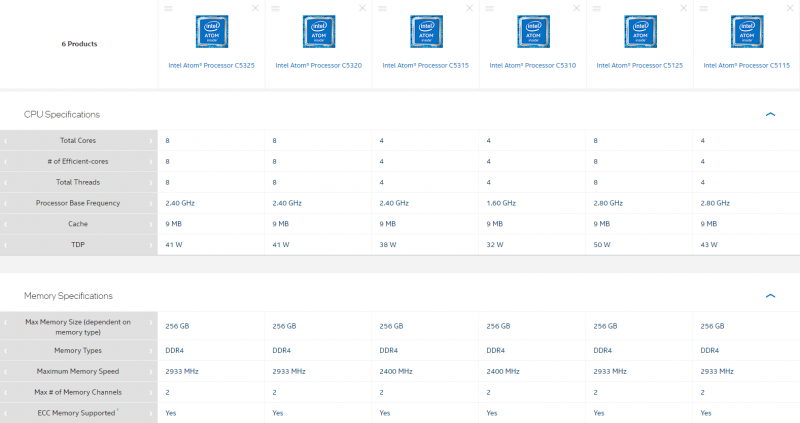

Intel представила первые процессоры серии Atom C5000 Parker RidgeКорпорация Intel анонсировала первые шесть процессоров семейства Atom C5000 (Parker Ridge), предназначенных для применения в серверном и сетевом оборудовании. Дебютировали изделия с обозначениями C5325, C5320, C5315, C5310, C5125 и C5115, которые изготавливаются по 10-нм техпроцессу. В зависимости от модификации чипы содержат четыре или восемь ядер (Tremont). Технология многопоточности не поддерживается. Тактовая частота модели C5310 составляет 1,6 ГГц. Версии C5325, C5320 и C5315 функционируют на частоте 2,4 ГГц, а C5125 и C5115 — 2,8 ГГц. Поддерживается работа с двухканальной оперативной памятью DDR4, частота которой может составлять 2400 или 2933 МГц (см. характеристики отдельных моделей в таблице ниже). Максимально поддерживаемый объём ОЗУ у всех решений равен 256 Гбайт. Все изделия наделены 9 Мбайт кеша второго уровня. Показатель TDP варьируется от 32 до 50 Вт. Это, как отмечает ресурс ServeTheHome, заметивший появление новинок в базе Intel, довольно много для изделий такого класса. Процессоры различаются количеством поддерживаемых линий PCIe — 12, 16 или 32. Чипы позволяют задействовать 12 или 16 портов SATA и восемь USB-портов в конфигурации 4 × USB 2.0 и 4 × USB 3.0. Все процессоры поддерживают технологию Intel QuickAssist (QAT) второго поколения (шифрование 20 Гбит/с), средства виртуализации Virtualization Technology (VT-x), инструкции AES, технологии Intel Trusted Execution и Enhanced Intel SpeedStep. Отличительной же чертой серии являются встроенные сетевые интерфейсы (до 8 шт., до 50GbE), которые есть в четырёх из шести представленных моделей.

22.03.2022 [18:48], Игорь Осколков

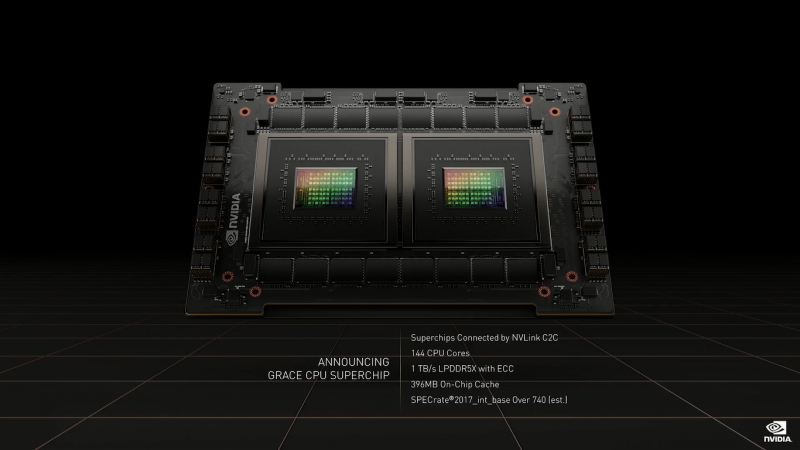

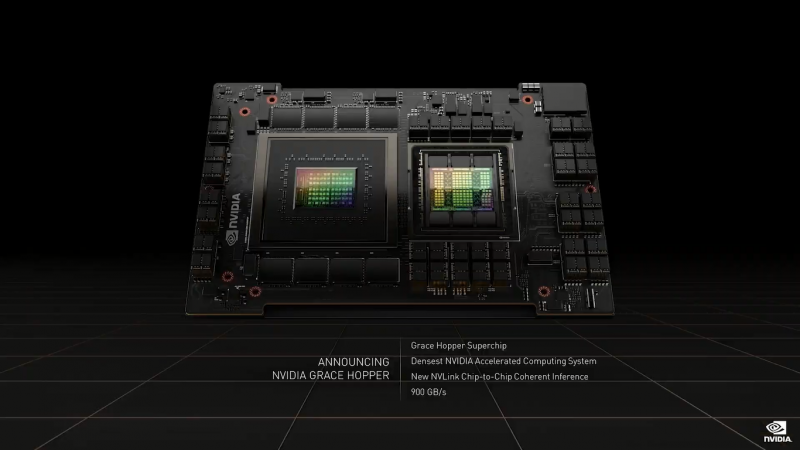

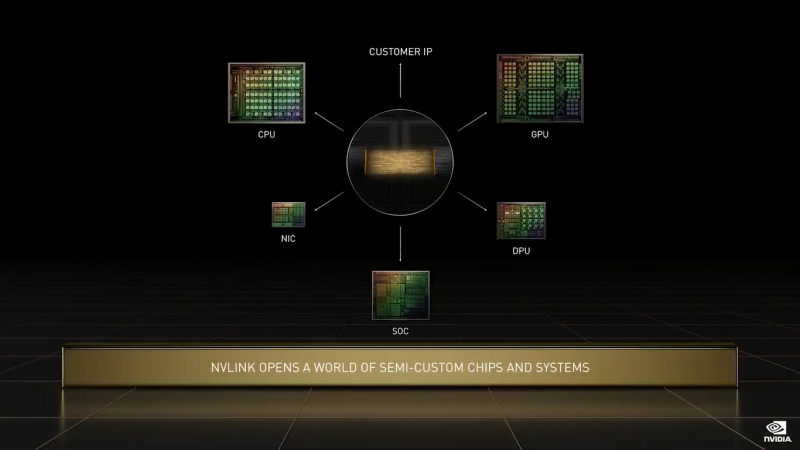

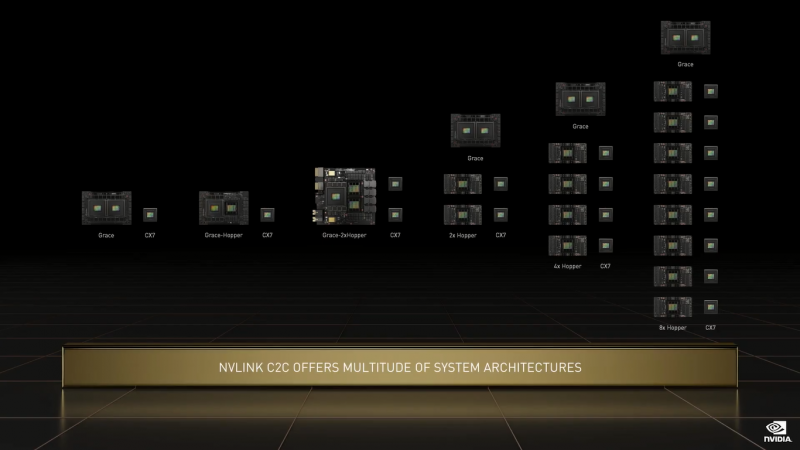

NVIDIA анонсировала 144-ядерные Arm-процессоры Grace и гибрид Grace HopperГлавным событием GTC 2022 стал анонс новых ускорителей H100 (Hopper), которые станут доступны в III квартале 2022 года. Вслед за ними в первой половине 2023 года появятся давно обещанные CPU Grace и гибридная система Grace Hopper, сочетающие, как понятно из названия, процессоры Grace (ARMv9) и ускорители Hopper. Как и было сказано ранее, для связи всех компонентов между собой будет использоваться mesh-сеть на базе всё той же шины NVLink 4.0 (900 Гбайт/с) с кеш-когерентностью. А сочетание LPDDR5X (с ECC, конечно) и HBM даст суммарный объём памяти до 600 Гбайт с общей полосой пропускания порядка 2 Тбайт/с. Для Grace Hopper компания подготовит полный стек ПО, благо портированием на Arm она начала заниматься ещё 3 года назад. Двухчиповый процессор Grace Superchip для ИИ- и HPC-нагрузок имеет 144 ядра, результат которых в SPECrate2017_int_base составляет 740, что, по словам компании, в полтора раза выше, чему у пары AMD EPYC, использующихся в DGX A100. И это, честно говоря, не такой уж и впечатляющий результат. Но NVIDIA утверждает, что новые CPU вдвое лучше по отношению производительности к энергопотреблению, чем «традиционные серверы» — использование LPDDR5X позволяет добиться пропускной способности памяти в 1 Тбайт/с, а вся сборка CPU+RAM будет потреблять менее 500 Вт. Чипы (или чиплеты, если хотите) в Grace Superchip тоже объединены посредством NVLink, только в данном случае этот интерконнект называется NVLink-C2C (Chip-to-Chip). И его NVIDIA предлагает использовать другим компаниям для создания кастомных сборок, объединяющих необходимые кристаллы, да и сама готова масштабировать и адаптировать свои решения под нужды заказчика. По словам NVIDIA, NVLink-C2C в 25 раз энергоэффективнее PCIe 5.0, а для его реализации нужна в 90 раз меньшая площадь кремния. Шина предлагает высокую скорость (да-да, всё те же 900 Гбайт/с), низкий уровень задержек, поддержку атомарных операций и совместимость с Arm AMBA CHI, CXL и UCIe.

24.02.2022 [19:00], Алексей Степин

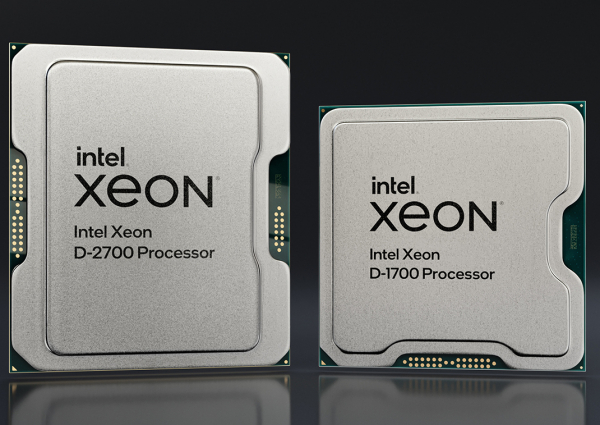

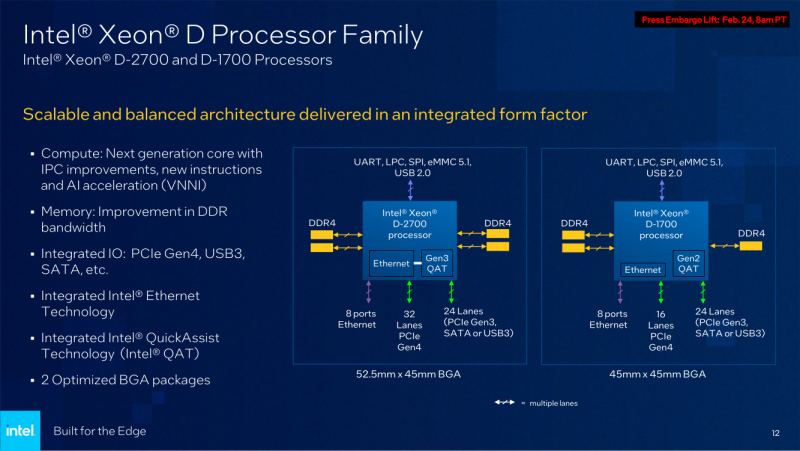

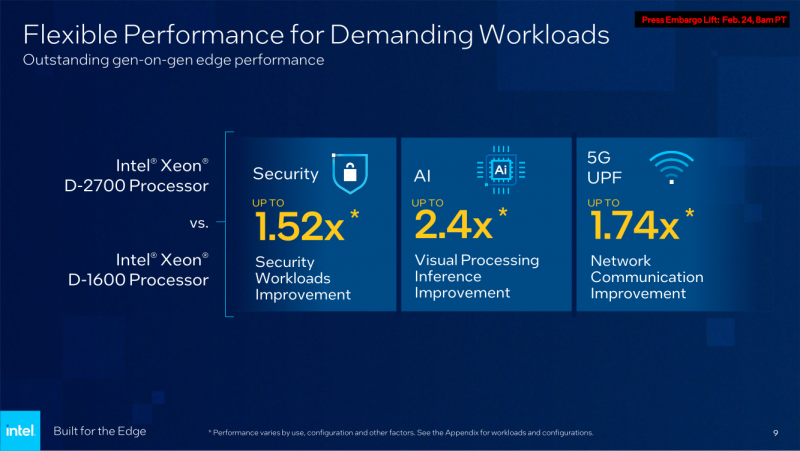

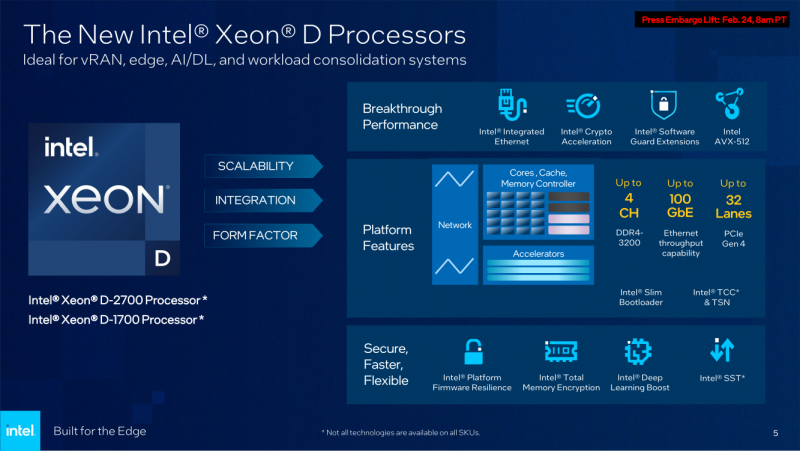

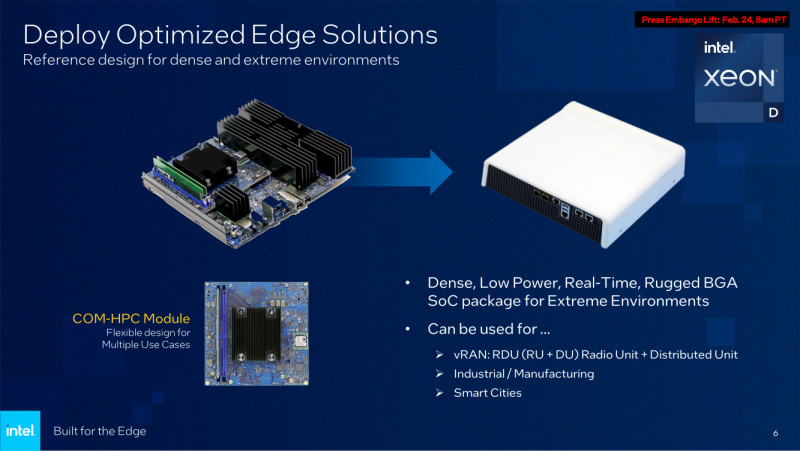

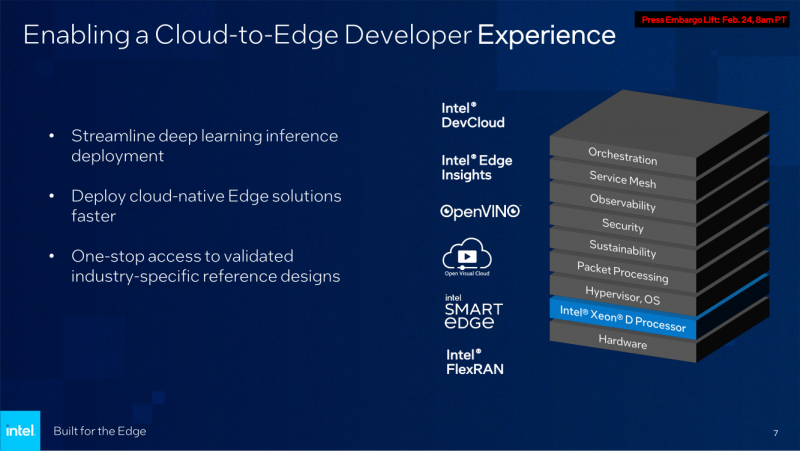

Intel анонсировала процессоры Xeon D-1700 и D-2700: Ice Lake-SP + 100GbEКонцепция периферийных вычислений сравнительно молода и до недавнего времени зачастую её реализации были вынуждены обходиться стандартными процессорами, разработанными для применения в серверах, или даже в обычных ПК и ноутбуках. Intel, достаточно давно имеющая в своём арсенале серию процессоров Xeon D, обновила модельный ряд этих CPU, которые теперь специально предназначены для использования на периферии. Анонс выглядит очень своевременно, поскольку по оценкам Intel, к 2025 году более 50% всех данных будет обрабатываться вне традиционных ЦОД. Новые серии процессоров Xeon D-1700 и D-2700 обладают рядом свойств, востребованных именно на периферии — особенно на периферии нового поколения. Новинки имеют следующие особенности:

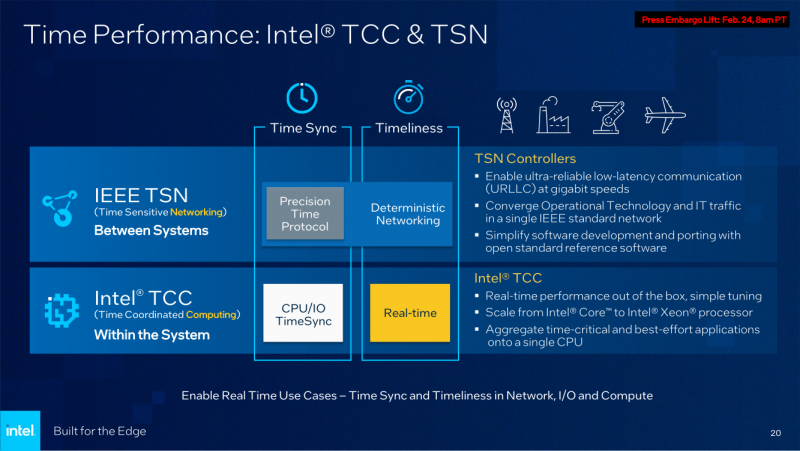

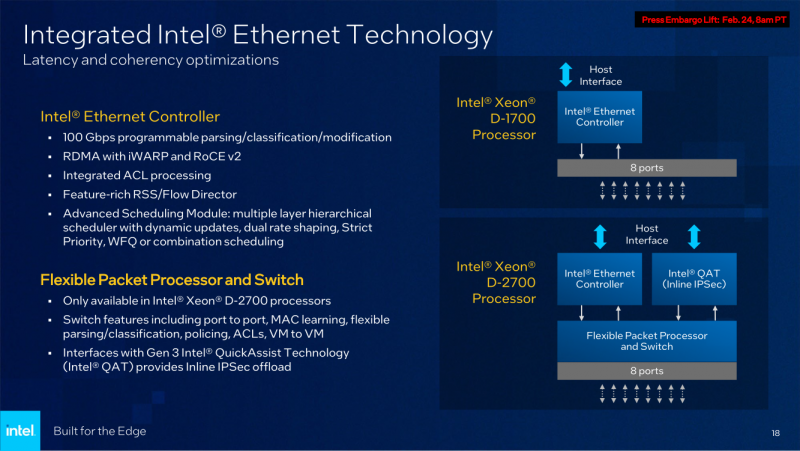

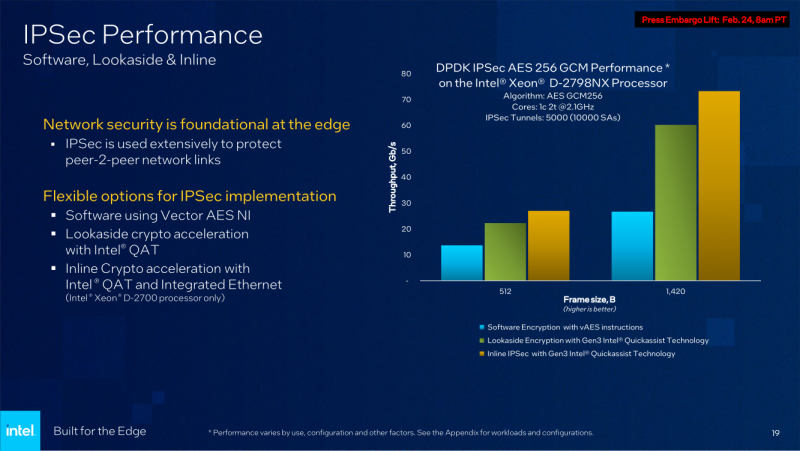

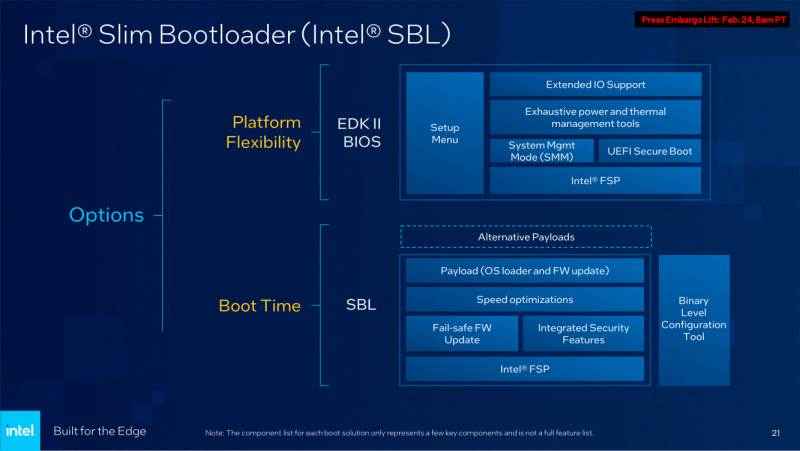

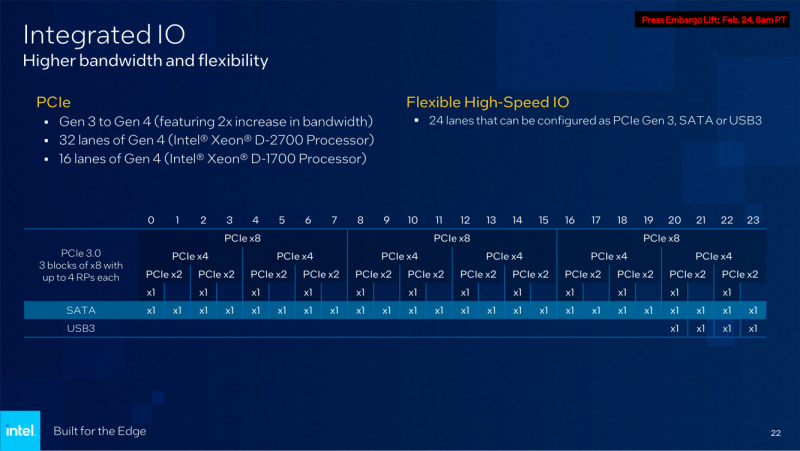

Последний пункт ранее был реализован в процессорах серий Atom x6000E, Xeon W-1100E и некоторых процессорах Core 11-го поколения. Вкратце это технология, позволяющая координировать вычисления с точностью менее 200 мкс в режиме TCC за счёт точной синхронизации таймингов внутри платформы. И здесь у Xeon D, как у высокоинтегрированной SoC, есть преимущество в реализации подобного класса точности. Помогает этому и наличие специального планировщика для общего кеша L3, позволяющего добиться более консистентного доступа к кешу и памяти. Это незаменимая возможность для систем, обслуживающих сверхточные промышленные процессы, тем более что Intel предлагает хорошо документированный набор API и средств разработки для извлечения из режима TCC всех возможностей. Важной также выглядит наличие поддержки пакета технологий Intel QuickAssist (QAT) для ускорения задач (де-)шифрования и (де-)компрессии. Третье поколение QAT, доступное, правда, только в Xeon D-2700, в отличие от второго (и это случай D-1700), связано в новых SoC непосредственно с контроллером Ethernet и встроенным программируемым коммутатором. В частности, поддерживается, и IPSec-шифрование на лету (inline) на полной скорости, и классификация (QoS) трафика. Также реализована поддержка новых алгоритмов, таких, как Chacha20-Poly1305 и SM3/4, имеется собственный движок для публичных ключей, улучшены алгоритмы компрессии. Но QAT может работать и совместно с CPU (lookaside-разгрузка), а можно и вовсе обойтись без него, воспользовавшись AES-NI. Поддержке безопасности помогает и полноценная поддержка защищённых вычислительных анклавов SGX, существенно ограничивающая векторы атак как со стороны ОС и программного обеспечения, так и со стороны гипервизора виртуальных машин. Это важно, поскольку на периферии уровень угрозы обычно выше, чем в контролируемом окружении в ЦОД, но для использования SGX требуется модификация ПО. В целом, «ядерная» часть новых Xeon-D — это всё та же архитектура Ice Lake-SP. Так что Intel в очередной раз напомнила про поддержку DL Boost/VNNI для работы с форматами пониженной точности и возможности эффективного выполнения инференс-нагрузок — новинки почти в 2,5 раза превосходят Xeon D-1600. Есть и прочие стандартные для платформы функции вроде PFR или SST. Из важных дополнений можно отметить поддержку Intel Slim BootLoader. Масштабируемость у новой платформы простирается от 2 до 10 (D-1700) или 20 (D-2700) ядер, а TDP составляет 25–90 и 65–129 Вт соответственно. В зависимости от модели поддерживается работа в расширенном диапазоне температур (до -40 °C). У обоих вариантов упаковка BGA, но с чуть отличными размерами — 45 × 45 мм против 45 × 52,5 мм. На этом различия не заканчиваются. У младших Xeon D-1700 поддержка памяти ограничена тремя каналами DDR4-2933, а вот у D-2700 четыре полноценных канала DDR4-3200. Однако возможности работы с Optane PMem обе модели лишены, несмотря на то, что контроллер памяти их поддерживать должен. Представитель Intel отметил, что если будет спрос со стороны заказчиков, то возможен выпуск вариантов CPU с поддержкой PMem. Дело в том, что прошлые поколения Xeon-D использовались и для создания СХД, а наличие 100GbE-контроллера с RDMA делает новинки не менее интересными для этого сегмента. Кроме того, есть и поддержка NTB, да и VROC с VMD вряд ли исчезли. Для подключения периферии у D-2700 доступно 32 линии PCIe 4.0, а у D-1700 — 16. У обоих серий CPU также есть 24 линии HSIO, которые на усмотрение производителя можно использовать для PCIe 3.0, SATA или USB 3.0. Впрочем, пока Intel предлагает использовать всё это разнообразие интерфейсов для подключения ускорителей и различных адаптеров. Поскольку в качестве одной из основных задач для новых процессоров компания видит их работу в качестве контроллеров программно-определяемых сетей, включая 5G, она разработала для этой цели референсную платформу. В ней предусматривается отдельный модуль COM-HPC с процессором и DIMM-модулями, что позволяет легко модернизировать систему. А базовая плата предусматривает наличие радиотрансиверов, что актуально для сценария vRAN. Поскольку речь идёт не столько о процессорах, сколько о полноценной платформе, Intel серьезное внимание уделила программной поддержке, причём, в основе лежат решения с открытым программным кодом. Это позволит заказчикам систем на базе новых Xeon D разворачивать новые точки и комплексы периферийных вычислений быстрее и проще. Многие производители серверного аппаратного обеспечения уже готовы представить свои решения на базе Xeon D-1700 и 2700.

08.02.2022 [00:30], Владимир Мироненко

Ventana, разработчик серверных процессоров RISC-V, объявил о стратегическом партнёрстве с IntelСтартап Ventana Micro Systems Inc., разработчик высокопроизводительных серверных процессоров на базе архитектуры RISC-V, объявил о стратегическом партнёрстве с Intel — ядра и чиплеты Ventana будут доступны в рамках Intel Foundry Services (IFS) для крупных клиентов ЦОД, операторов сетей 5G, потребителей в областях ИИ и машинного обучения, автомобильной индустрии и т. д. Ventana разрабатывает серверные CPU с расширяемыми возможностями, поставляемые в виде SoC с чиплетной компоновкой или IP-блоков. Процессоры предназначены для обеспечения лучшей в своём классе однопоточной производительности и могут быть оптимизированы для высокопроизводительных и облачных вычислений, ЦОД-нагрузок, 5G и периферийных вычислений, выполнения задач ИИ и машинного обучения, автомобильных и клиентских приложений.

Источник изображения: ventanamicro.com Модульная и масштабируемая продуктовая стратегия Ventana, основанная на использовании чиплетов, позволяет обеспечить быстрое коммерческое внедрение со значительной экономией времени и стоимости разработки по сравнению с преобладающими на рынке IP-моделями. Собственные ядра CPU компания намерена выпускать на TSMC по 5-нм нормам, но для остальных блоков могут использоваться сторонние производства. В рамках партнёрства с Intel ядра Ventana можно будет интегрировать в SoC конечных заказчиков. Кроме того, Ventana планирует предложить масштабируемую вычислительную платформу, которая позволит гиперскейлерам и крупным OEM-производителям гибко подбирать и настраивать функциональные блоки у заказываемых чипов, значительно сокращая время и стоимость разработки. Боб Бреннан (Bob Brennan), вице-президент Intel Foundry Services по разработке клиентских решений отметил, что у Ventana «самая совершенная и хорошо разработанная платформа» на базе Open Chiplet, которая полностью соответствует видению Intel. По его словам, чиплеты Ventana позволят IFS предоставлять модульные решения, повышающие производительность, снижающие энергопотребление и затраты на разработку, и ускоряющие время выхода продуктов на рынок.

24.01.2022 [20:09], Алексей Степин

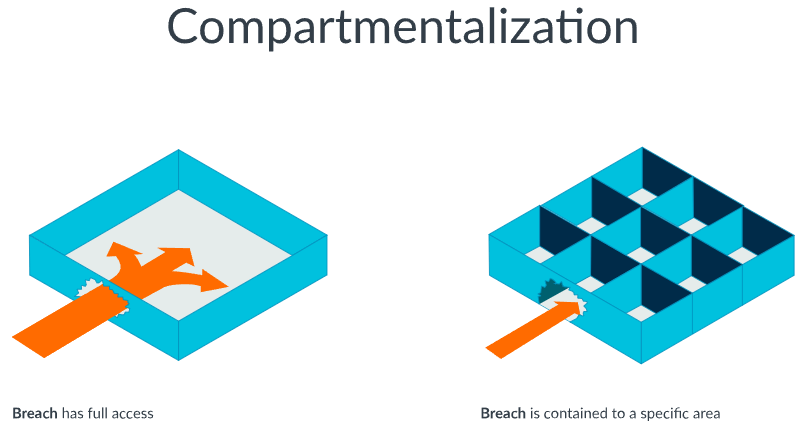

Arm выпустила прототип платы с процессором повышенной безопасности MorelloВ современном мире процессоров уже никого не удивляет нахождение очередной уязвимости, а иногда тропинкой для злоумышленника становятся технологии, изначально призванные повысить уровень безопасности. Ряд исследователей небезосновательно считает, что «заплатками» отделаться не получится и надо менять глубинные принципы, лежащие в основе процессорных архитектур. Один из таких проектов, развиваемый с 2010 года усилиями SRI International и Кембриджского университета — это CHERI. В 2019 к нему присоединилась Arm, недавно представившая первый прототип платы с процессором Morello, который базируется на двух ключевых принципах, заложенных в CHERI — масштабируемая компартментализация и тонко настраиваемая защита содержимого памяти. Оба принципа реализованы аппаратно и сами по себе не новы.

Изображения: Arm По сути речь идёт о расширении стандартного набора инструкций, с помощью которого даже написанное с использованием языков, позволяющих относительно легко сделать ошибки при работе с памятью (а это обычно C/C++), ПО можно заставить работать без образования серьёзных дыр в защите. Тщательная компартментализация (т.е. разделение) кода ОС и приложений хотя и не исключает наличие уязвимостей, но серьёзно ограничивает область возможного нанесения вреда.  В частности, любая инструкция типа load/store и любая операция выборки должны быть авторизованы на аппаратном уровне со стороны процессора. Разумеется, это не высокоуровневая защита, а скорее набор базовых блоков для построения таковой. Принцип компартментализации ещё проще: если в классической архитектуре взломщик может получить контроль над всей системой, то в изолированных друг от друга ОС и приложениях, он лишь проникнет в одну из множества небольших «ячекк», а его действия послужат сигналом для защитных механизмов.

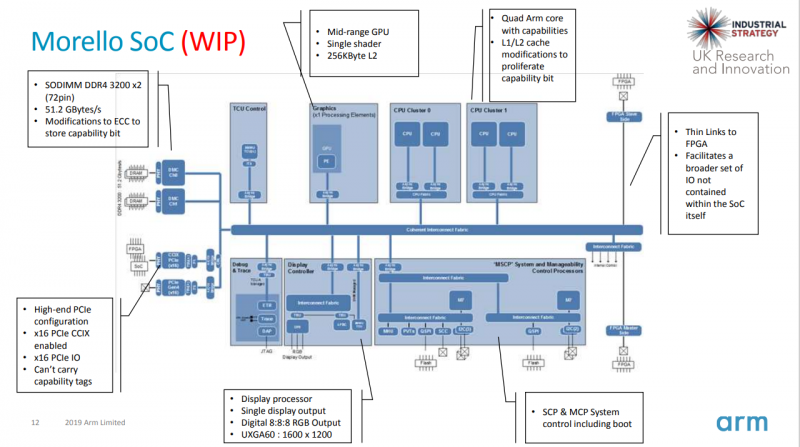

Блок-схема Arm Morello Arm Morello — первый чип на базе CHERI. Текущая аппаратная реализация использует модифицированные ядра Neoverse N1 (ARMv8.2) с частотой 2,5 ГГц. Первые платы с новым процессором предназначены таким IT-гигантам как Google и Microsoft, а также заинтересованным партнёрам образовательным учреждениям. На текущий момент разработчики предлагают модифицированное ядро FreeBSD, часть стандартных UNIX-программ, а также некоторые другие приложения. С появлением готовых плат и процессоров процесс адаптации ПО должен значительно ускориться.

07.01.2022 [00:05], Алексей Степин

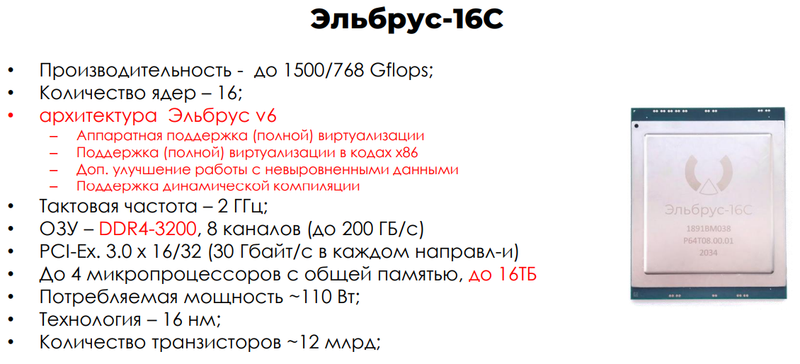

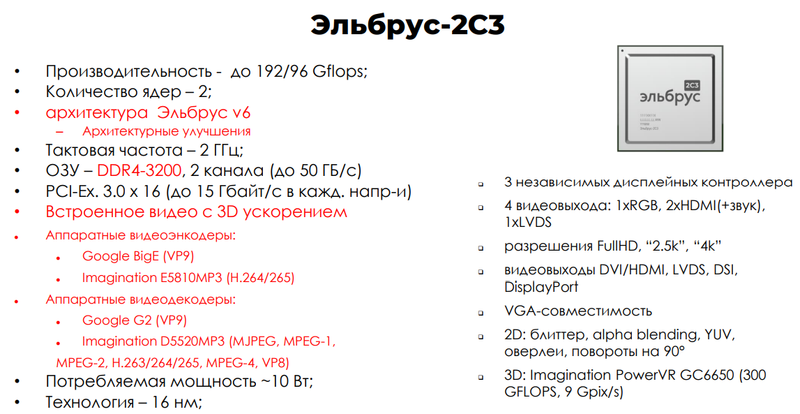

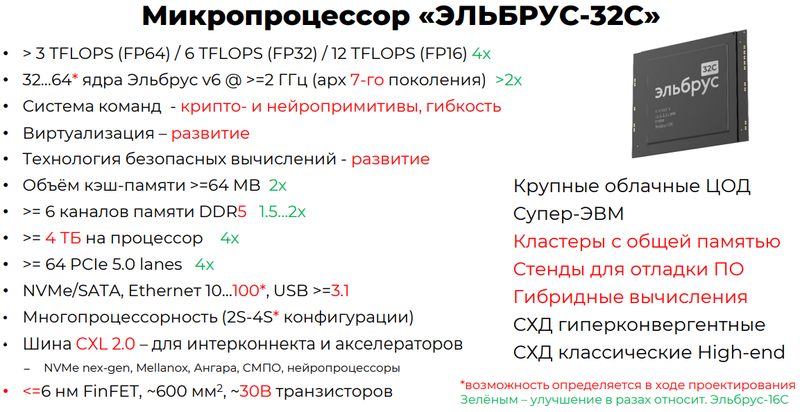

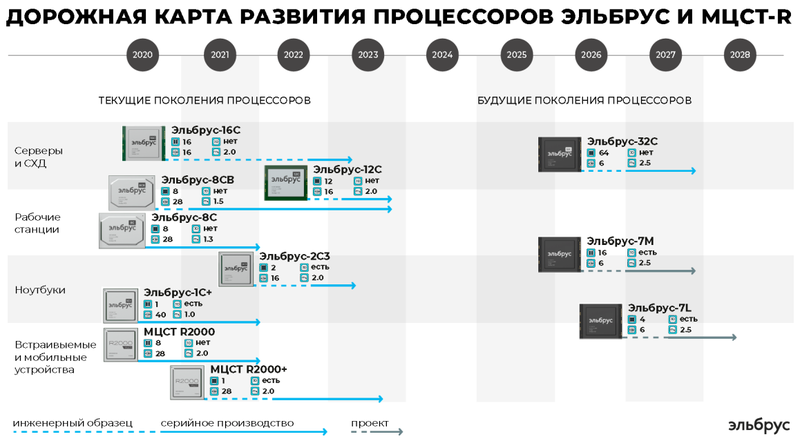

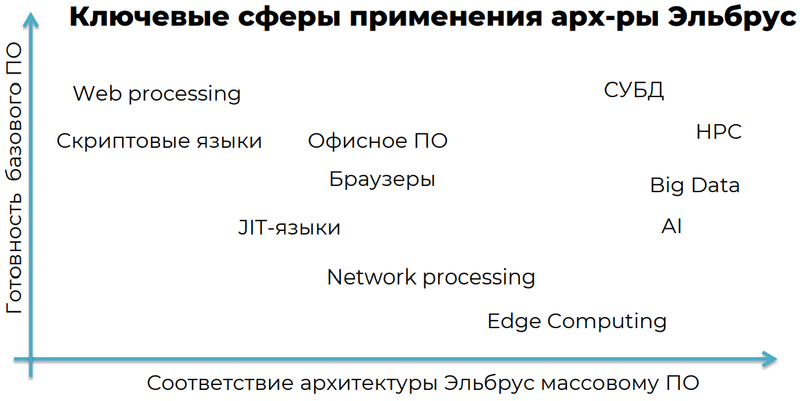

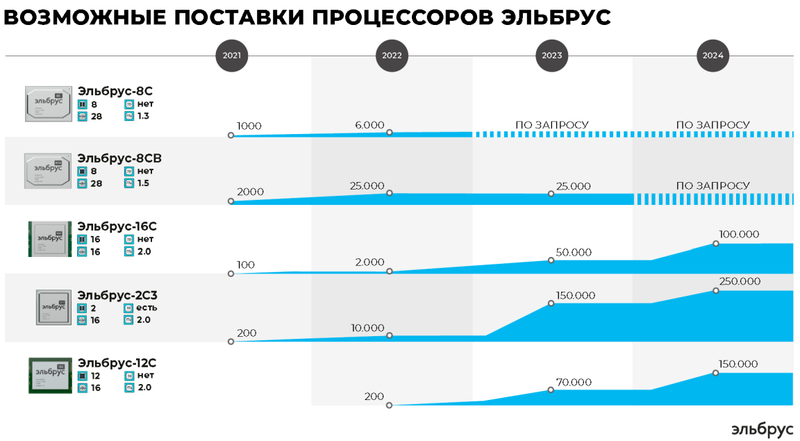

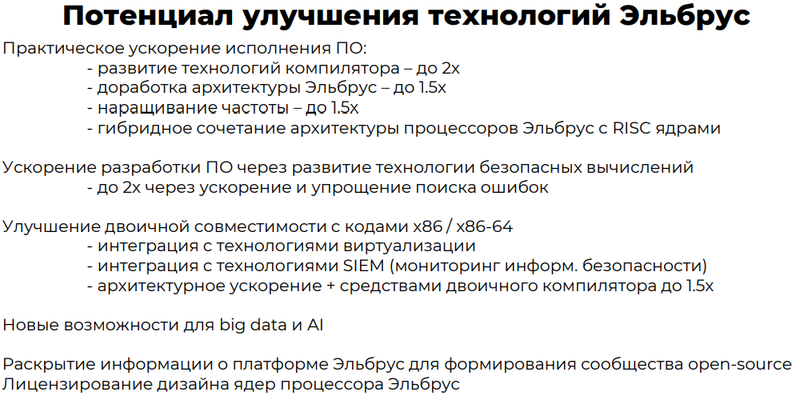

Серийное производство Эльбрус-16С и 2С3 начнётся в этом годуРоссийские процессоры Эльбрус, разрабатываемые компанией МЦСТ, вызывают немало споров вокруг самой архитектуры и доступности изделий на её основе. Но платформа продолжает жить и развиваться, несмотря на все трудности. Для всех процессоров разработан типовой ряд модулей и системных плат, от простых вариантов с одним CPU до высокоплотных четырёхсокетных. Есть решения и для обычных настольных ПК, а также модули для встраиваемых и терминальных систем. В конце прошлого года на очередной партнёрской конференции МЦСТ были опубликованы новые доклады, в том числе, освещающие изменения в ситуации с доступностью процессоров и решений на их основе. А изменений этих немало. Во-первых, окончательно устаревшими можно признать чипы Эльбрус-8. Им на смену пришла усовершенствованная версия Эльбрус-8СВ. Крупная партия этих чипов в настоящее время уже получена и находится в процессе таможенного оформления. Этот чип, напомним, лишён целого ряда недостатков, присущих Эльбрус-8С.  Однако 28-нм техпроцесс себя исчерпал, и в 2022 году на смену придут 16-нм процессоры Эльбрус-16С, Эльбрус-12С и Эльбрус-2С3. В их основу легла новая, шестая версия VLIW-архитектуры МЦСТ. Она сопровождается отказом от уже устаревшей и медленной схемотехники подсистем ввода-вывода, реализованной в предыдущем поколении Эльбрус на базе моста КПИ-2 и переходом на интегрированный контроллер PCI Express.  Старший 16-ядерный вариант получил 8-канальный контроллер DDR4-3200, что вполне отвечает требованиям современности. Планка максимального объёма оперативной памяти поднята до 16 Тбайт в четырёхпроцессорной системе (4х4 Тбайт). Благодаря новому техпроцессу удалось удержать в приличных рамках теплопакет, выросший с 80 до 110 ватт при вдвое большем количестве ядер.  Современный серверный процессор немыслим без виртуализации, и в новых решениях МЦСТ её аппаратная поддержка реализована в полном объёме, в том числе, для кода x86. Появилась поддержка динамической компиляции, дополнительно оптимизирована работа с невыровненными данными. Но главное, что образцы Эльбрус-16С и 2С3 получены и успешно прошли тесты. Подготовлена вторая ревизия, данные по ней уже переданы контрактному производителю.  Младший Эльбрус-2С3 в дополнение к интегрированному GPU получил продвинутый набор аппаратных кодеков, который включает VP9 и H.264/H.265. Процессор пойти в серию в течение этого года, а рабочие прототипы систем на его базе уже есть. 12-ядерный Эльбрус-12С наиболее интересный, как платформа для рабочих станций разработки ПО для данной архитектуры, пока ждёт второй ревизии, которая должна быть готова в течение первой половины 2022 года.  Не забывает МЦСТ и о корнях — разработке архитектур на базе SPARC. Образцы процессора R2000+ также получены и прошли инженерные тесты. Это чип, ориентированный на сверхэкономичные системы — его теплопакет составляет всего 5 Ватт, но при этом он имеет встроенное графическое ядро с функциями 3D-ускорения.  Что касается приверженности самой архитектуре VLIW, то МЦСТ продолжает настаивать на преимуществах явного параллелизма команд, осознавая, разумеется, необходимость качественного компилятора. Интерес представляет диаграмма применимости архитектуры Эльбрус: она не очень подходит для веб-задач и скриптовых языков, а лучше всего, по мнению разработчиков, раскрывает себя в задачах HPC/Big Data, СУБД и ИИ-системах.  Что касается внедрения, то серверы на базе процессоров Эльбрус активно внедряются в государственных учреждениях: ЦОД для ГИС «Мир» содержит порядка 200 серверов, а МВД России недавно закупило более 400 серверов для автоматизированной системы фиксации нарушений. РЖД внедряет тонкие клиенты на базе Эльбрус, а также использует его в системах автоматики управления стрелочным хозяйством. Силами Ростелеком создано первое облако на базе Эльбрус-8С/СВ.  Но, пожалуй, наибольшего успеха в импортозамещении добились энергетики: удалось разработать и внедрить самый широкий спектр решений на базе Эльбрус, от систем автоматики для подстанций до полноценной АСУ ТП «ПАК МАРС» для компании Россети. В последнем случае Эльбрус используется во всех компонентах, от клиентских рабочих мест до серверов и СХД.  С точки зрения программной экосреды наиболее интересна система двоичной трансляции, позволяющая запускать ПО, разработанное для х86-64, которое затем постепенно можно оптимизировать и переводить в «родной режим». Начаты работы по внедрению механизмов динамической оптимизации на базе LCC и LLVM. Также стоит отметить появление поддержки LLVM 13-ой ветки и бета-версию систем виртуализации на базе KVM + QEMU + libvirt.  МЦСТ заботится о разработчиках: первые 100 экземпляров плат на базе Эльбрус-16С и 2С3 уже разосланы партнёрам для реализации пилотных проектов. Компания готовится сертифицировать дизайн-центры и контрактные производства, а также сообщает о том, что появились первые дистрибьюторы, работающие с продукцией на базе Эльбрус.  Весьма интересны как планы МЦСТ по выпуску новых процессоров на базе VLIW-архитектуры седьмого поколения, так и данные относительно нововведений в этой архитектуре. В планах создание процессора с числом ядер до 64 и с системой команд, включающей крипто- и нейропримитивы, продвинутыми средствами виртуализации и безопасных вычислений, и, что немаловажно, поддержкой прогрессивного универсального стандарта CXL 2.0.  Запланировано использование 6-нм техпроцесса, а также выпуск чипов с меньшим количеством ядер для рабочих станций и ноутбуков. Также рассматривается возможность создания гибридного процессора, сочетающего ядра Эльбрус и RISC-V. Такой чип с учётом поддержки бинарной трансляции сможет претендовать на звание самого универсального ЦП в мире.  Ознакомиться полнее с материалами конференции можно на сайте МЦСТ. В целом, архитектура Эльбрус выглядит живой и развивающейся, решения на базе уже освоенных 8-ядерных процессоров активно внедряются в России, а более новые 12 и 16-ядерные CPU гораздо лучше соответствуют современным требованиям. Что касается Эльбрус-32С, то это амбициозный проект, в котором сочетаются как новейшие технологии (DDR5 и CXL 2.0), так и уникальные архитектурные особенности.

17.12.2021 [01:35], Алексей Степин

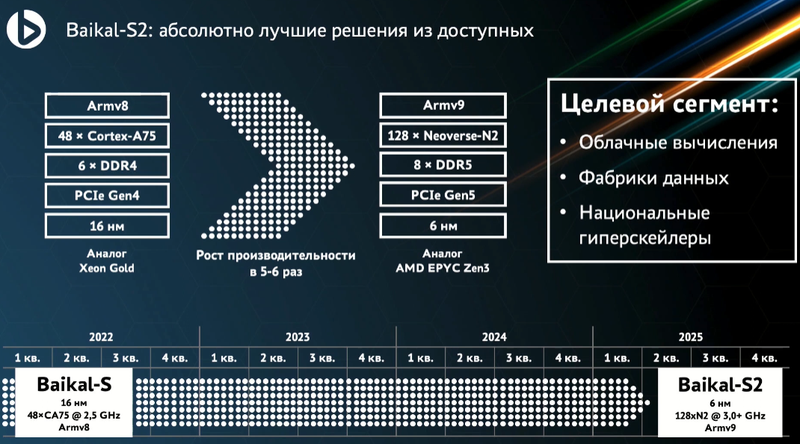

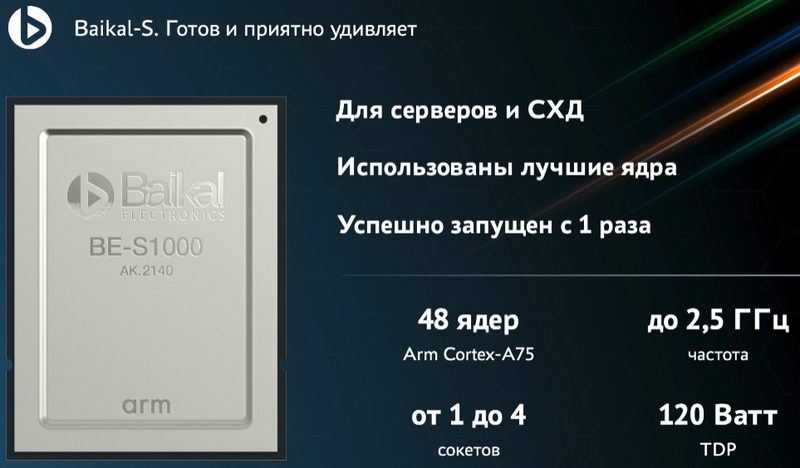

Российский серверный процессор Baikal-S2 получит чиплетную компоновку, 128 ядер Armv9 с частотой 3 ГГц, 8 каналов DDR5, 192 линии PCIe 5.0 и CXL 2.0На ежегодной итоговой конференции Байкал Электроникс состоялся анонс 128-ядерных серверных Arm-процессоров второго поколения Baikal-S2, были показаны результаты тестов 48-ядерных Baikal-S, анонсированы первые же российские серверы и СХД на их основе, а также было объявлено о заключении стратегических сделок и планах на будущее. Если говорить о сделках, то можно смело сказать, что рамками только Arm Байкал себя уже не ограничивает: получение доли в CloudBEAR означает и получение основы для разработки собственных чипов с архитектурой RISC-V, и первым же проектом станет создание сертифицированной системы доверенной загрузки для процессоров Baikal-L и Baikal-S2. Но среди равноправных партнёров значатся не только российские разработчики — заключена сделка с Esperanto Technologies.

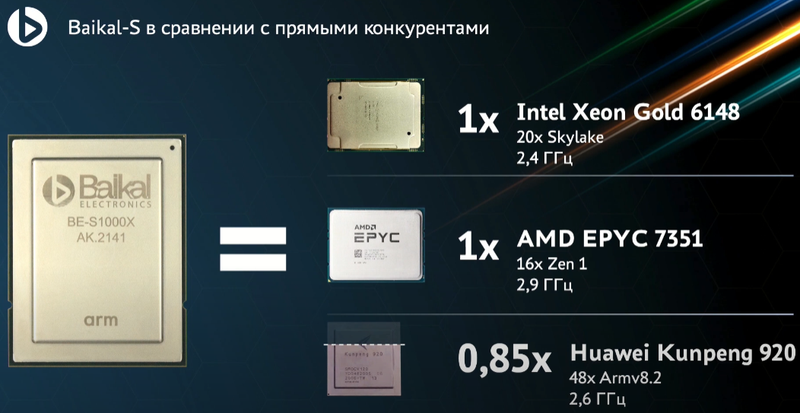

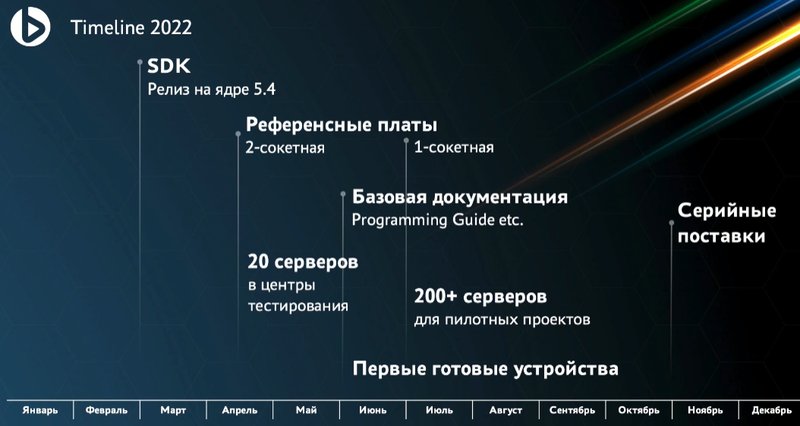

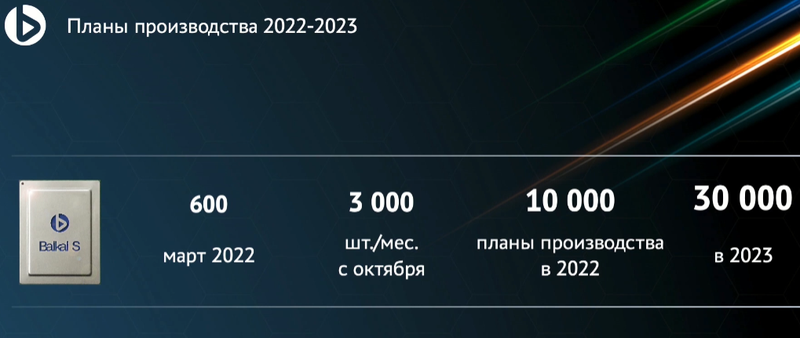

Тестовая плата с процессором Baikal-S (Изображения: Байкал Электроникс) Данная сделка позволит получить доступ к весьма серьёзным разработкам: напомним, Esperanto создала ET-SoC-1, мощнейший ИИ-ускоритель с более чем тысячью ядер RISC-V в составе. Связка из четырёх таких чипов развивает более 800 Топс в задачах инференса, потребляя всего 120 Вт. Надо ли говорить, насколько это важно в эпоху нейросетей, машинного обучения и разнообразных сопроцессоров-ускорителей.  Несмотря на то, что Baikal-S «старичком» назвать никак нельзя, компания анонсировала уже второе поколение чипов — Baikal-S2 базируется на новейшей архитектуре Neoverse-N2 (ARMv9). Процессор будет выполнен по 6-нм техпроцессу с использованием чиплетной компоновки и получит 128 ядер с частотой порядка 3 ГГц, 8 каналов DDR5 (возможно, будет и больше), 192 линии PCIe 5.0, поддержку CXL 2.0 и CCIX 2.0. Ожидается, что он станет аналогом AMD EPYC Milan. Разработку планируется закончить к 2025 году.  Что касается текущего поколения Baikal-S, то осенью этого года была получена первая партия чипов, а также было анонсировано несколько решений на его основе. Как теперь отрапортовали разработчики, первые чипы оказались очень удачными во всех отношениях, так что больших препятствий на пути их внедрения быть не должно. На конференции были представлены одно- и двухсокетные серверы и СХД от российских компаний 3Logic, Aquarius, ICL, iRU, Норси-Транс. Впоследствии появятся и четырёхпроцессорные системы.  Напомним, что Baikal-S содержит в своём составе 48 ядер Arm Cortex-A75 с частотой до 2,5 ГГц и имеет TDP 120 Вт. Шестиканальный контроллер памяти поддерживает до 768 Гбайт DDR4-3200. Современно выглядит и поддержка PCI Express 4.0 (80 линий), и наличие выделенного управляющего ядра для организации доверенных вычислений, и аппаратная виртуализация.  В синтетических тестах новинка показала результаты, сравнимые с Intel Xeon Gold 6148 или AMD EPYC 7351, а своему китайскому «коллеге» в лице HiSilicon Kunpeng 920 процессор уступил лишь в некоторых тестах. Разработчики уверены, что процессор получился универсальным и его можно использовать практически везде: в серверах любых профилей, СХД, суперкомпьютерах, устройствах сетевой безопасности и даже в базовых станциях 5G. Результаты тестов также доступны и на сайте Geekbench.  Ожидается, что SDK для новой платформы будет доступен уже в конце февраля следующего года. Весной появятся двухпроцессорные платы и первые 20 серверов попадут в центры тестирования, а к середине лета 200 с лишним серверов примут своё участие в пилотных проектах. Старт серийного производства CPU намечен на октябрь-ноябрь 2022 года — речь идёт примерно о 10 тыс. процессоров. В 2023 году этот объём будет утроен и при необходимости увеличен.  Таким образом, Байкал Электроникс доказала, что может создавать достойные серверные решения, не уступающие зарубежным, причём, как на базе x86-64, так и на базе Arm. Уже сейчас процессоры Baikal-S могут стать основой для производительных серверов российской разработки, а сделка с Esperanto сделает российские HPC-системы и комплексы машинного обучения по-настоящему мощными.

14.12.2021 [19:41], Алексей Степин

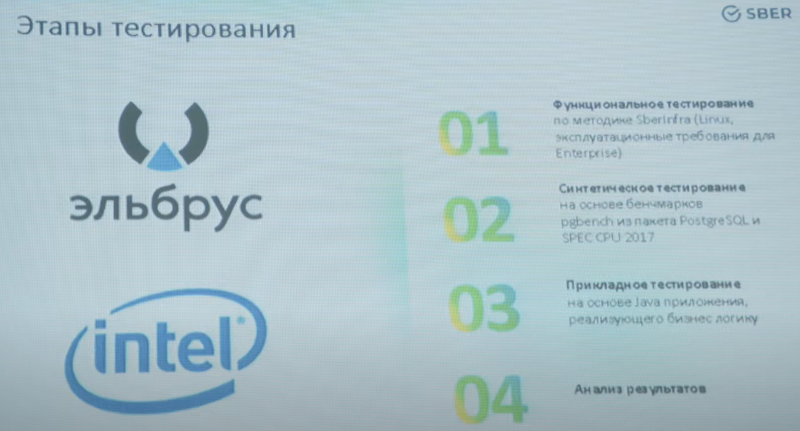

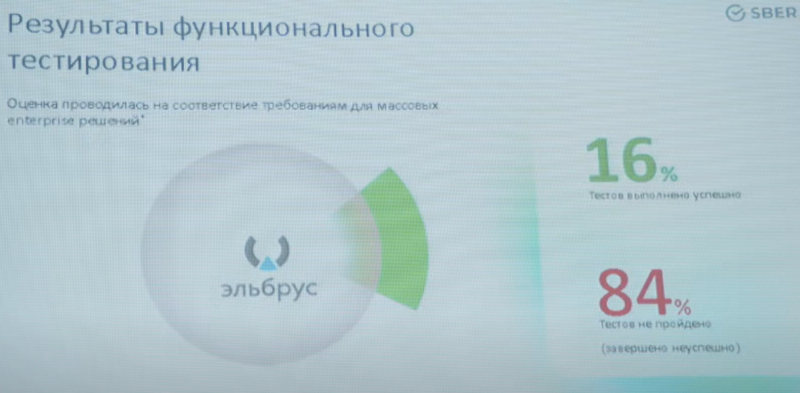

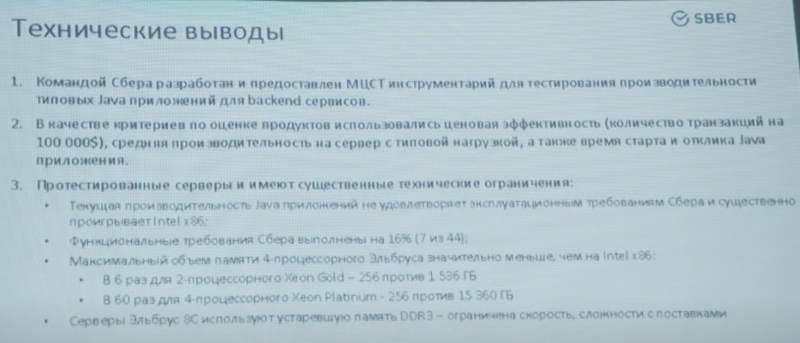

Серверы на базе «Эльбрус» не прошли тесты Сбербанка, но не всё потеряноВ рамках программы импортозамещения СберТех провёл тестирование серверов на базе процессоров Эльбрус-8С. По результатам системы признаны работоспособными, но не отвечающими предъявляемым требованиям по целому ряду параметров. Все пожелания и замечания переданы МЦСТ, разработчику Эльбрус. Банковские информационные системы — критически важная часть любого государства. Поэтому неудивительно стремление использовать в них решения собственной разработки, дабы меньше зависеть от чужих чипов и серверов. Примеры Huawei это подтверждают, но в данной заметке речь пойдёт не о китайских процессорах, а о российских. Лаборатория СберТех провела полноценное тестирование серверов на базе процессоров Эльбрус-8С, результаты которого, к сожалению, трудно назвать удовлетворительными.

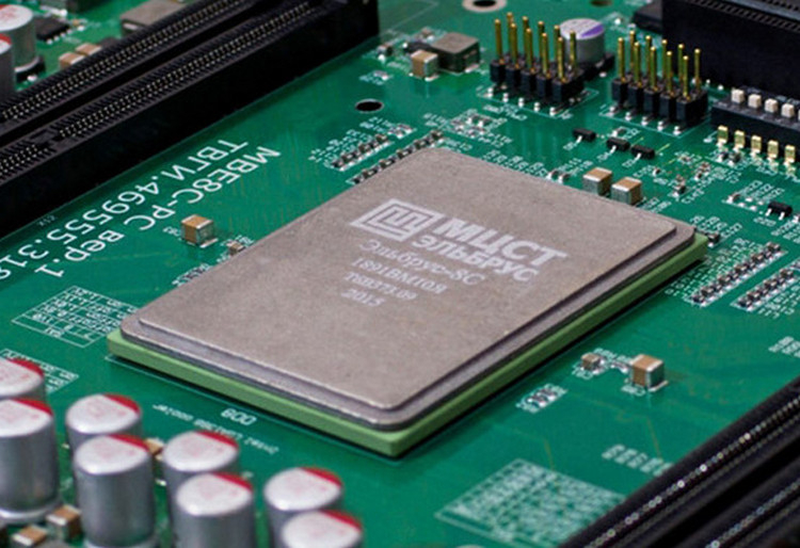

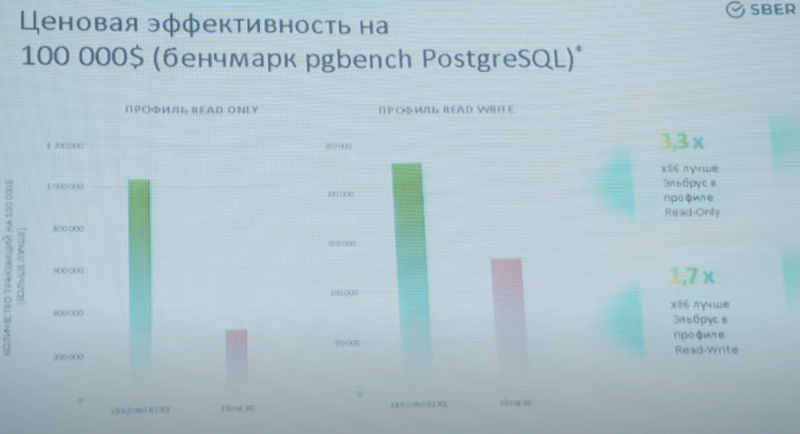

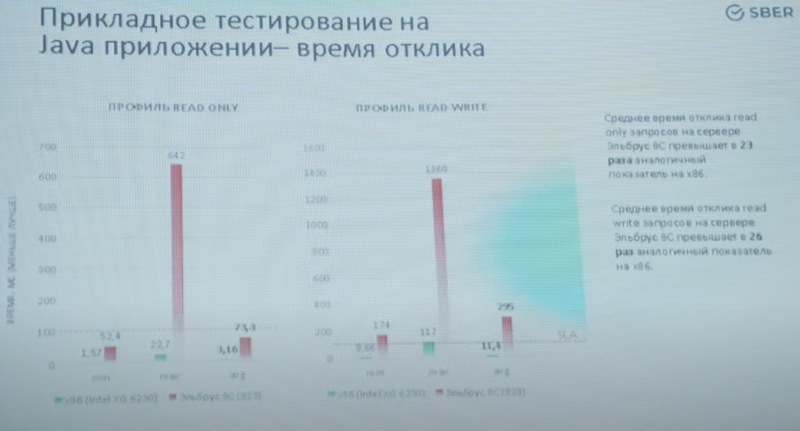

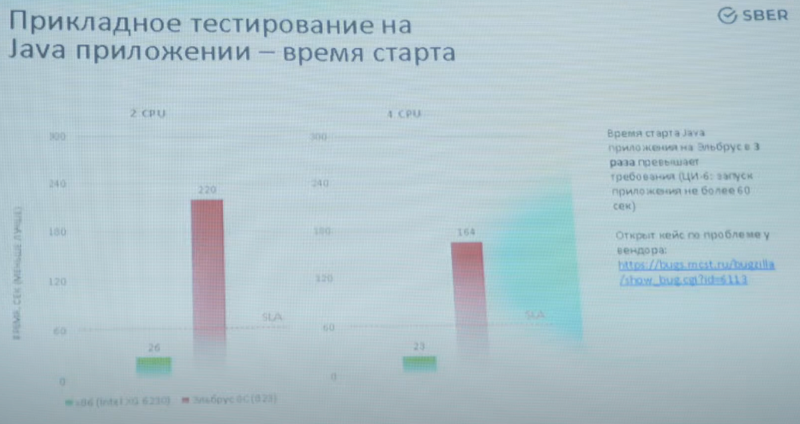

Фото: МЦСТ Это первое полномасштабное испытание процессоров Эльбрус в «полевых условиях», то есть, на уровне реальных серверов и задач, которые эти серверы должны выполнять. В испытаниях приняли участие платформы с двумя и четырьмя чипами Эльбрус-8С (VLIW, 8C/8T, 1,3 ГГц, 16 Мбайт L3-кеш, 70 Вт TDP, 28 нм). В качестве оппонентов выступили «типичные системы» на базе Intel Xeon Gold 6230 (x86-64, Cascade Lake-SP, 20C/40T, 2,1-3,9 ГГц, 27,5 Мбайт кеш, 125 Ватт TDP, 14 нм), которых в Сбере тысячи и тысячи.

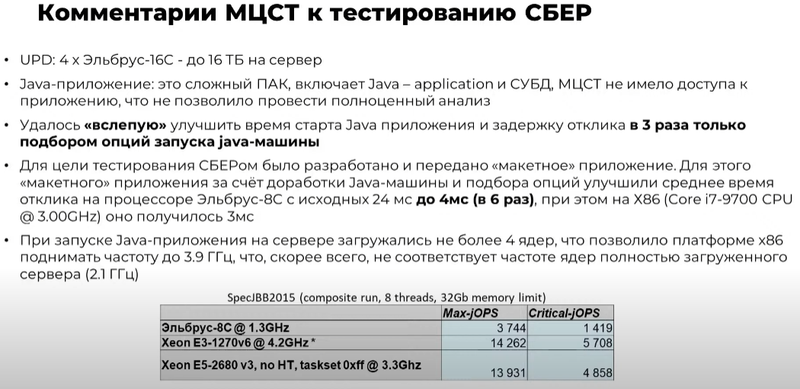

Изображения: YouTube/ElbrusTV По итогам тестирования серверы признаны работоспособными, но показавшими неудовлетворительный уровень производительности. Озвучены основные выводы: «мало памяти, медленная и устаревшая память, мало ядер, низкая тактовая частота». Особенно низкой оказалась производительность в приложениях, использующих Java.  Если в тестах PGbench/PostreSQL Xeon опередил Эльбрус в 1,7-3,3 раза, то в тестах на время отклика Java-приложения разница составила 23-26 раз. Запуск приложения, который по нормативам СберТеха должен укладываться в 60 секунд, занял у серверов Эльбрус 220 секунд в двухпроцессорном варианте и 164 секунды — в четырёхпроцессорном.  Кроме того, в рамках стандартных спецификаций компании системы на базе Эльбрус-8С смогли пройти всего по 7 параметрам из 44 предъявляемых. Если отсутствие монтажных стоечных рельсов можно отнести к «мелким претензиям», которые легко решаются, то отсутствие системы удалённого управления — недоработка весьма серьёзная, поскольку затраты на увеличение штата ИТ-специалистов окажутся непомерно велики.  Стоит, однако, отметить, что Эльбрус-8С уже устарел в рамках собственной экосистемы: МЦСТ обещает представить на тестирование усовершенствованные варианты серверов на базе Эльбрус-8СВ с более высокой частотой (1,5 против 1,3 ГГц), удвоенной производительностью в операциях над числами с плавающей запятой, а также использующие память DDR4-2400 (до 1 Тбайт на сервер) вместо окончательно устаревшей DDR3-1600. Однако массовые поставки таких серверов при заказе 1-5 тыс. единиц возможны не ранее IV квартала 2022 года при заказе в III квартале 2021 года.  Признана необходимость проведения тестов систем на базе Эльбрус под управлением ОС, сертифицированных ФСТЭК по профилю не ниже ОС.А4 (использование для обработки персональных данных и ГИС). Также отмечена необходимость введения полноценной поддержки технологий виртуализации, а не только контейнеризации.  Отметим также, что МЦСТ успешно завершила разработку Эльбрус-16С, в котором ряд фундаментальных недостатков, присущих процессорам Эльбрус-8С/8СВ успешно устранён. Новый чип будет иметь 16 ядер с возросшей до 2 ГГц частотой, восьмиканальный контроллер памяти DDR4-3200 (до 16 Тбайт на сервер), контроллер 10GbE и интегрированный контроллер PCIe 3.0 (32 линии). Последний снимает серьёзные ограничения по пропускной способности чипов Эльбрус-8C/CB к периферийным устройствам. Также с 8 до 48 Гбайт/с возрастёт скорость межпроцессорного обмена данными.  Представитель МЦСТ отметил, что низкие результаты в Java-тестах отчасти обусловлены «слепым тестированием», в котором разработчикам не были предоставлены данные, необходимые для полноценной оптимизации Java-машины. Простым подбором опций МЦСТ удалось улучшить показатели в три раза, а «макет» оптимизированного приложения СберТеха позволил сократить время отклика с 24 до 4 мс, что практически равнозначно показателям систем на базе процессоров Intel (Core i7-9700, 3 мс). |

|