Материалы по тегу: cpu

|

08.11.2021 [20:00], Игорь Осколков

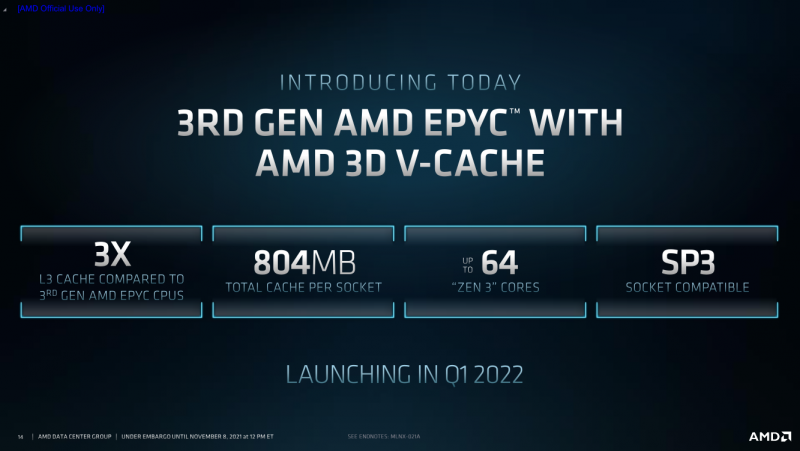

AMD анонсировала процессоры EPYC Milan-X с 3D V-Cache: 804 Мбайт кеша и 64 ядра Zen3AMD анонсировала серию своих серверных процессоров под кодовым названием Milan-X. Новинки являются развитием EPYC 7003 (Milan), представленных весной этого года, и рассчитаны в первую очередь на высокопроизводительные вычисления (HPC). Главным же отличием от «обычных» Milan станет резко увеличенный объём кеш-памяти, что позволило AMD снова назвать свои процессоры самими быстрыми в мире.

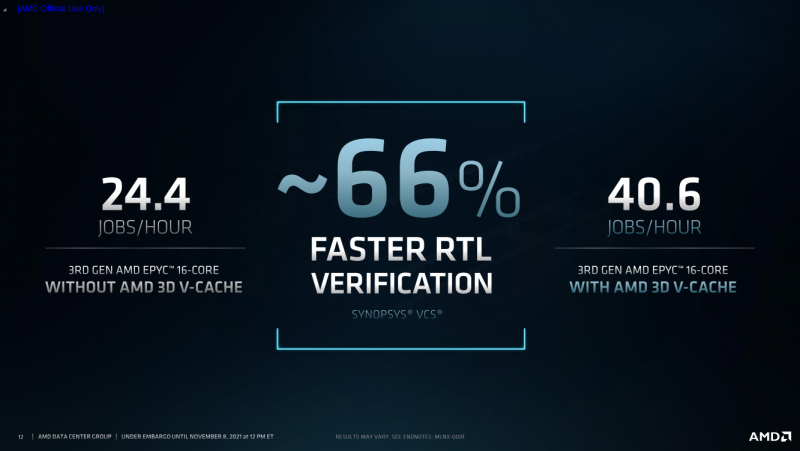

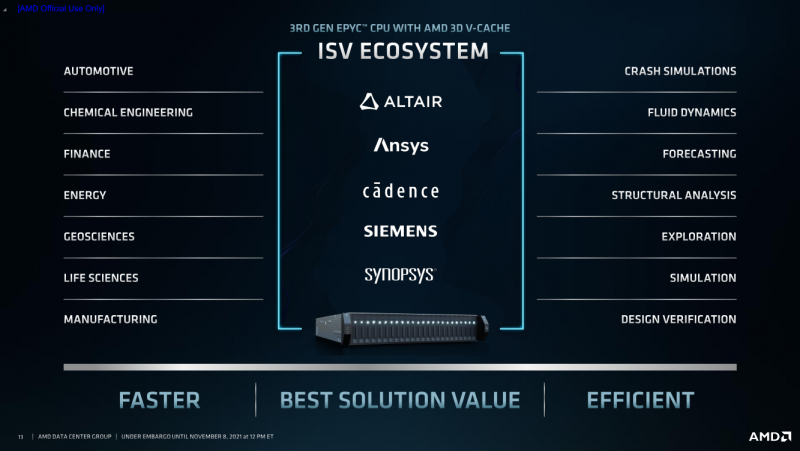

AMD EPYC Milan-X с 3D V-Cache (Здесь и ниже изобржаения AMD) Откуда берётся цифра в 804 Мбайт? Математика простая. На каждое ядро Zen3 приходится по 32 Кбайт L1-кеша для инструкций и данных + 512 Кбайт L2-кеша. На восемь ядер в CCX-комплексе приходится 32 Мбайт общего L3-кеша. И вот к ним добавляются ещё 64 Мбайт 3D V-Cache — в максимальной конфигурации на 8 CCX получается суммарно 768 Мбайт 3D V-Cache в дополнение к иерархии нижележащих кешей. Таким образом, конкретно по этому показателю побит рекорд IBM z15, хотя данный CPU ориентирован на совсем другие задачи. А вот среди x86-64 равных Milan-X сейчас нет. Более того, по словам AMD, реализация 3D V-Cache на текущий момент является уникальной в индустрии. Дополнительный кеш имеет непосредственно подключение к CCX по медным каналами, что позволяет значительно повысить плотность упаковки и энергоэффективность, снизить задержки и улучшить температурный режим. Правда, детальные характеристики V-Cache пока не приводятся.  Что важно, новинки будут совместимы с имеющимися SP3-платформами для Milan, что упростит тестирование и валидацию — для них будет выпущено обновление BIOS. Увы, пока данные по частотам, TDP и цене компания не приводит — выпуск Milan-X запланирован на I квартал 2022 года. Но в сносках к презентации, в частности, упоминаются не только 64-ядерные Milan-X, но и 16-ядерные. Надо полагать, что такие «бутерброды» будут дороже обычных CCX, поскольку здесь цена брака будет выше. Также заявлена совместимость с имеющимся ПО, но и с разработчиками уже ведётся активная работа по дополнительной оптимизации их решений. Наибольшую выгоду от увеличенного кеша получат нагрузки, для которых критична скорость работы с памятью и задержки доступа. Среди таковых AMD упоминает метод конечных элементов, структурный анализ, вычислительную гидродинамику и автоматизированные системы проектирования электроники (EDA). Для последних на примере Synopsys VCS рост производительности составил 66%.

26.10.2021 [22:45], Игорь Осколков

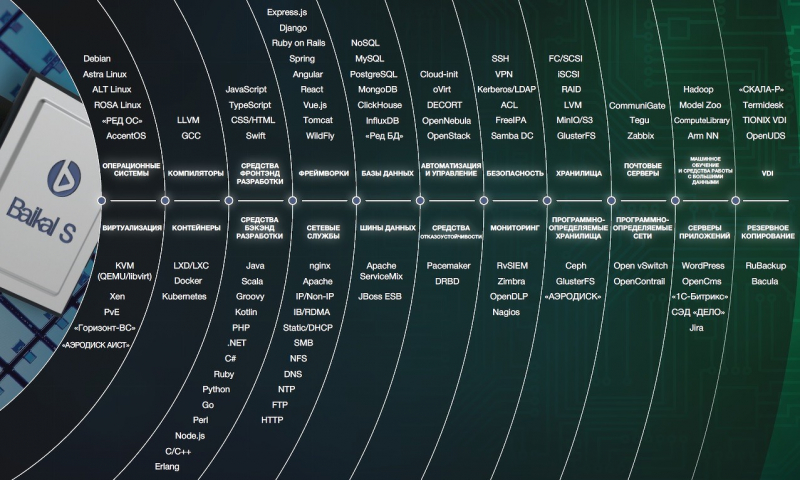

Получена первая партия российских серверных Arm-процессоров Baikal-S: 48 ядер, 6 каналов DDR4-3200 и 80 линий PCIe 4.0Компания «Байкал Электроникс» сообщила о получении первой партии инженерных образцов серверных Arm-процессоров Baikal-S объёмом 400 шт. Следующую партию компания ожидает получить в первом квартале следующего года, а первые массовые поставки (партия более 10 тыс. шт.) должны начаться до конца третьего квартала. Инженерные платы для разработчиков, созданы «Гаоди рус» (Dannie Group) и выпущены компанией «Рутек». Baikal-S, изготавливаемый по 16-нм техпроцессу на TSMC, имеет 48 ядер Arm Cortex-A75 на базе достаточно свежей 64-бит архитектуры ARMv8.2-A, которая была анонсирована в 2017 году. Частота составляет до 2,2 ГГц, а уровень TDP равен 120 Вт. Заявленный диапазон рабочих температур простирается от 0 до +70 °C. Производительность в HPL составляет 385 Гфлопс, а рейтинг в SPEC CPU2006 INT — до 600. Ориентировочная цена одного процессора ожидается на уровне $3 тыс.  L1-кеш имеет объём по 64 Кбайт для данных и инструкций, а L2 — 512 Кбайт на ядро. Любопытно, что в дополнение к L3-кешу (по 2 Мбайт на кластер) есть ещё и L4-кеш на 32 Мбайт. Контроллер памяти имеет шесть каналов DDR4-3200 ECC и обслуживает до 128 Гбайт на канал (суммарно 768 Гбайт на сокет). Кроме того, каждый процессор имеет 80 линий PCIe 4.0, из которых 48 линий делятся тремя интерфейсами CCIX x16. Также есть пара 1GbE-интерфейсов. При этом новинка поддерживает аппаратную виртуализацию, Arm TrustZone и позволяет создавать четырёхсокетные платформы. Всё это делает её привлекательным решением не только для традиционных серверов и СХД, но и для и HCI- и HPC-систем. С экосистемой ПО проблемы вряд ли будут. Во-первых, для «малого» Байкал-М уже сейчас есть отечественные ОС и другие продукты. Во-вторых, серверные платформы Arm в мире развивают сразу несколько игроков, да и сама Arm стимулирует процесс разработки и портирования ПО. Кроме того, «Байкал Электроникс» имеет тесные связи с ГК Astra Linux.

19.10.2021 [19:39], Алексей Степин

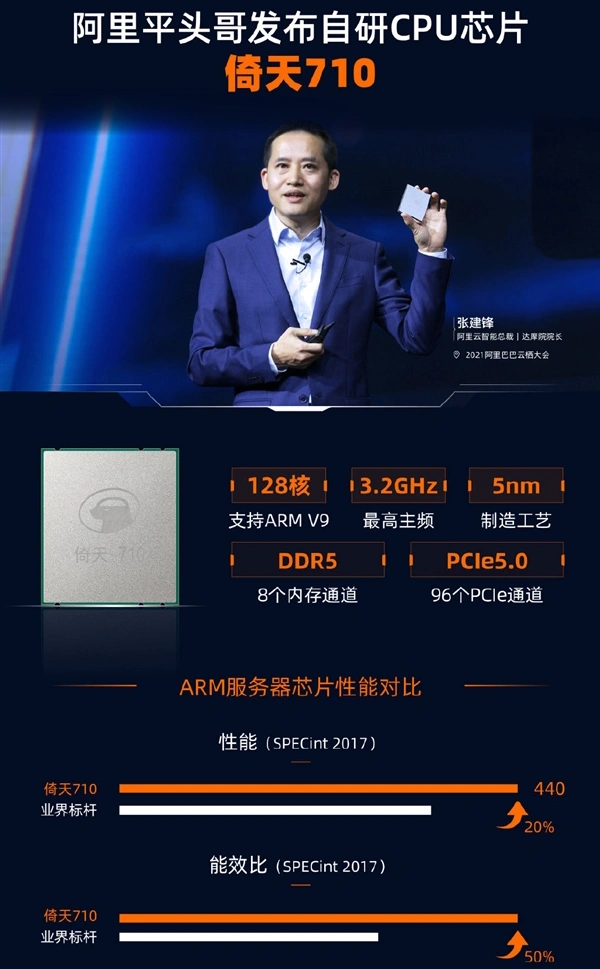

Alibaba Cloud представила серверный 128-ядерный Armv9-процессор Yitian 710Эпоха неоспоримого господства x86-64 в серверах, похоже, постепенно всё же подходит к концу. Ampere, AWS, Fujitsu, HiSilicon, Phytium и другие производители Arm-процессоров дают бой x86-64 и выигрывает его, пусть и не во всех областях. Эффективность серверных Arm-решений уже неоспорима, количество ядер уже перевалило за сотню, а теперь ещё один крупный провайдер облачных услуг, китайская компания Alibaba Cloud, анонсировала свой вариант высокопроизводительного CPU на базе Arm. Первые попытки Arm проникнуть на рынок серверов или рабочих станций были робкими и неуверенными, но за последние несколько лет ситуация сильно изменилась: уверенно показывают себя такие интересные чипы, как Ampere Altra, недавно доросшие уже до 128 ядер, Amazon активно предлагает инстансы на базе Graviton2, а Huawei даже открывает первый в России ЦОД на базе своих чипов Kunpeng 920.  Более того, мощные многоядерные Arm-процессоры обрастают собственной инфраструктурой: появляются собственные процессорные разъёмы, системные платы, не уступающие x86-моделям, и даже варианты в виде рабочих станций для разработчиков программного обеспечения, без которого любая платформа мертва. Тем интереснее выглядит анонс Alibaba Cloud. Компания сообщила о выпуске нового процессора, который послужит основой для её облачных. И по ряду характеристик можно видеть, что это весьма передовые решения. Новинка носит название Yitian 710, она имеет собственный процессорный сокет и инфраструктуру сопутствующей «обвязки» (есть и референс-дизайн сервера, Panjiu). Впрочем, интереснее то, что эти процессоры — как и Altra Max — могут иметь до 128 ядер.  Но если текущее поколение Ampere Altra базируется на наборе инструкций Armv8.2 с некоторыми заимствованиями из v8.3 и v8.4, то китайский гигант использует более новый вариант, Armv9. Эта версия архитектуры была анонсирована только весной этого года, она, как минимум, на треть быстрее v8, поддерживает аппаратную ускорение работы контейнеров и виртуальных машин, а также наделена востребованными нынче векторными инструкциями со средствами ускорения машинного обучения (SVE2). 5-нм процессоры Yitian 710 поставляются с июля этого года. Они содержат примерно 60 млрд транзисторов и могут иметь тактовую частоту до 3,2 ГГц, а также включают 128 Мбайт L3-кеша, восьмиканальный контроллер DDR5-4400 и 96 линий PCIe 5.0. TDP равен 250 Вт. Так что это один из самых передовых на сегодня серверных процессоров не только в плане чистой производительности. Сама Alibaba называет свое детище универсальным, одинаково хорошо подходящим для нагрузок общего назначения, развёртывания СХД и ИИ-нагрузок, но, разумеется, приоритет отдаётся задачам, характерным для облачных сред.

Alibaba Cloud: Yitian 710 превосходит всех ARM-соперников и в своём классе является лучшим Ввиду санкционных трений решение Alibaba Cloud разработать собственный мощный процессор выглядит вполне обоснованно, как и принятое ранее решение о создании собственной ИИ-платформы Hanguang 800. И это не единственные разработки Alibaba Cloud. Компания собирается сделать открытым дизайн не только четырёх чипов XuanTie (RISC-V), но и некоторых будущих ядер. Открыт будет и сопутствующий набор ПО, так что Alibaba Cloud всерьёз намеревается вырастить вокруг своего «кремния» развитую инфраструктуру аппаратного и программного обеспечения.

30.09.2021 [16:15], Сергей Карасёв

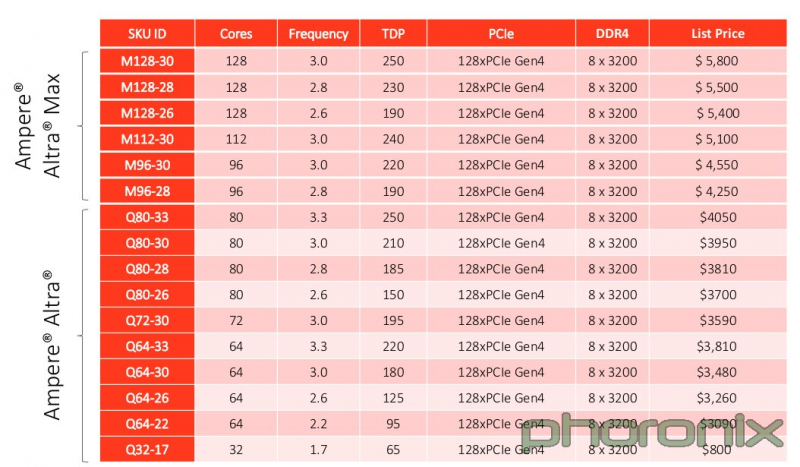

128-ядерный Arm-процессор Ampere Altra Max оказался на треть дешевле флагманских Xeon и EPYCРесурс Phoronix раскрыл стоимость многоядерных процессоров Ampere Altra Max, предназначенных для использования в высокопроизводительных серверах. Наблюдатели отмечают, что эти изделия, насчитывающие до 128 вычислительных ядер, предлагаются по цене ниже флагманских серверных чипов Intel Xeon и AMD EPYC. Arm-процессоры Ampere Altra Max M128-30 с частотой 3,0 ГГц изготавливаются по 7-нм технологии и предлагают 128 линий PCIe 4.0 и восемь каналов оперативной памяти DDR4-3200. Тесты Phoronix показывают, что в целом ряде задач чипы Ampere Altra Max M128-30 могут вполне конкурировать со старшими моделями Intel Xeon Ice Lake и AMD EPYC Milan. Итак, сообщается, что цена Ampere Altra Max M128-30 составляет $5800. Для сравнения: чип Intel Xeon Platinum 8380 сейчас предлагается за $8099, тогда как AMD EPYC 7763 стоит $8600. Процессор Ampere Altra Q80-30 с 80 вычислительными ядрами можно приобрести по цене $3950, а самая младшая 32-ядерная модель Ampere Altra Q32-17 стоит всего $800. Правда, надо учитывать, что всё это рекомендованные цены, а у AMD с Intel намного больше возможностей по их снижению для конечных заказчиков.

22.09.2021 [21:16], Алексей Степин

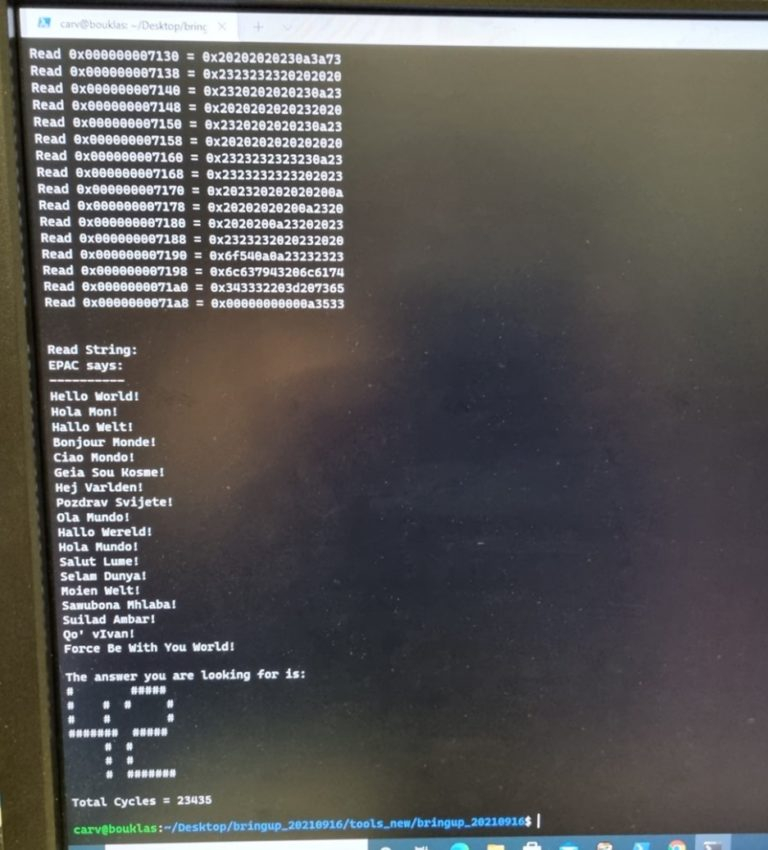

Выпущена тестовая партия европейских высокопроизводительных RISC-V процессоров EPI EPAC1.0Наличие собственных высокопроизводительных процессоров и сопровождающей их технической инфраструктуры — в современном мире вопрос стратегического значения для любой силы, претендующей на первые роли. Консорциум European Processor Initiative (EPI), в течение долгого времени работавший над созданием мощных процессоров для нужд Евросоюза, наконец-то, получил первые весомые плоды. О проекте EPI мы неоднократно рассказывали читателям в 2019 и 2020 годах. В частности, в 2020 году к консорциуму по разработке мощных европейских процессоров для систем экза-класса присоединилась SiPearl. Но сегодня достигнута первая серьёзная веха: EPI, насчитывающий на данный момент 28 членов из 10 европейских стран, наконец-то получил первую партию тестовых образцов процессоров EPAC1.0.

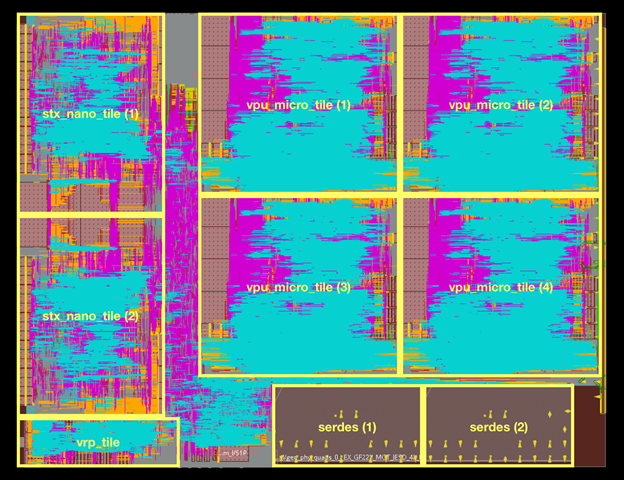

Источник изображений: European Processor Initiative (EPI) По предварительным данным, первичные тесты новых чипов прошли успешно. Процессоры EPAC имеют гибридную архитектуру: в качестве базовых вычислительных ядер общего назначения в них используются ядра Avispado с архитектурой RISC-V, разработанные компанией SemiDynamics. Они объединены в микро-тайлы по четыре ядра и дополнены блоком векторных вычислений (VPU), созданным совместно Барселонским Суперкомпьютерным Центром (Испания) и Университетом Загреба (Хорватия).

Строение кристалла EPAC1.0 Каждый такой тайл содержит блоки Home Node (интерконнект) с кешем L2, обеспечивающие когерентную работу подсистем памяти. Имеется в составе EPAC1.0 и описанный нами ранее тензорно-стенсильный ускоритель STX, к созданию которого приложил руку небезызвестный Институт Фраунгофера (Fraunhofer IIS). Дополняет картину блок вычислений с изменяемой точностью (VRP), за его создание отвечала французская лаборатория CEA-LIST. Все ускорители в составе нового процессора связаны высокоскоростной сетью, использующей SerDes-блоки от EXTOLL.  Первые 143 экземпляра EPAC произведены на мощностях GlobalFoundries с использованием 22-нм техпроцесса FDX22 и имеют площадь ядра 27 мм2. Используется упаковка FCBGA 22x22. Тактовая частота невысока, она составляет всего 1 ГГц. Отчасти это следствие использования не самого тонкого техпроцесса, а отчасти обусловлено тестовым статусом первых процессоров. Но новорожденный CPU жизнеспособен: он успешно запустил первые написанные для него программы, в числе прочего, ответив традиционным «42» на главный вопрос жизни и вселенной. Ожидается, что следующее поколение EPAC будет производиться с использованием 12-нм техпроцесса и получит чиплетную компоновку.

08.09.2021 [19:00], Алексей Степин

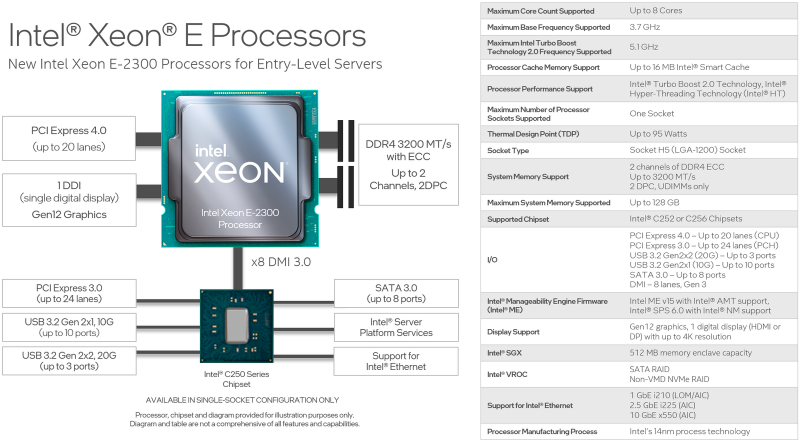

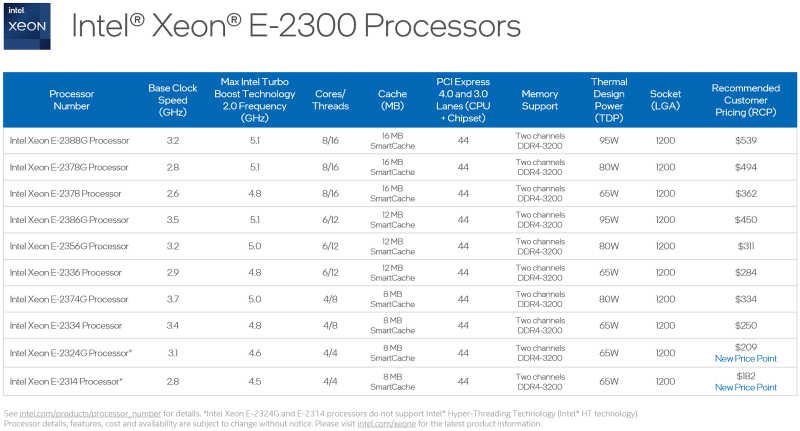

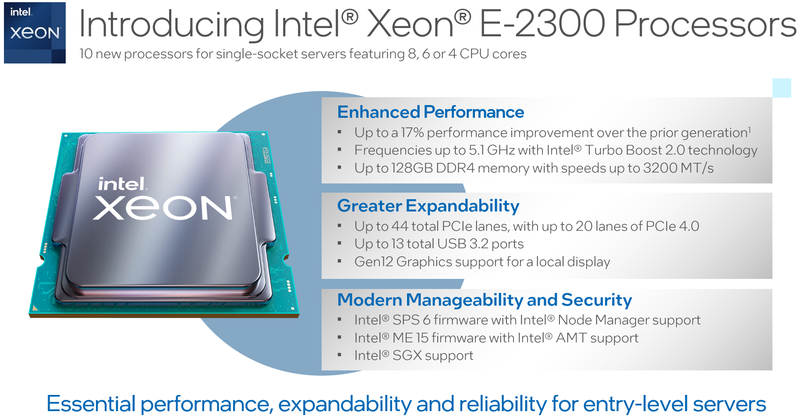

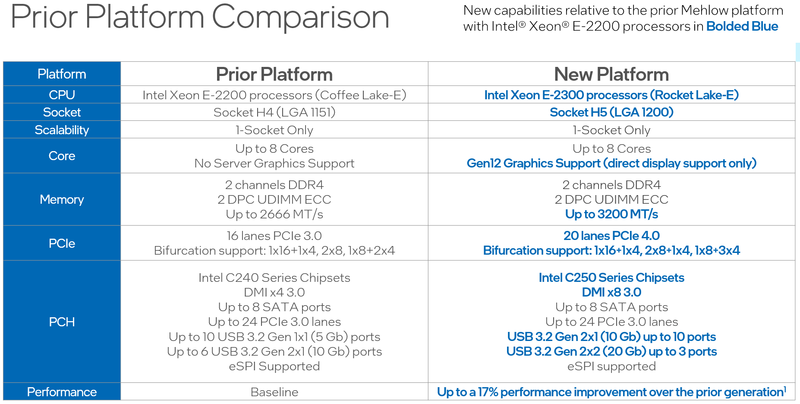

Intel представила процессоры Xeon E-2300: Rocket Lake-E для серверов и рабочих станций начального уровняВ современном мире нагрузки на процессор год от года становятся всё сложнее и объёмнее, и не только крупные ЦОД нуждаются в архитектурных новшествах и новых наборах инструкций — малому бизнесу также требуются чипы нового поколения. Корпорация Intel ответила на это выпуском новых процессоров Xeon серии E-2300 и соответствующей платформы для них. Новинки стали быстрее и получили долгожданную поддержку PCI Express 4.0. Платформа Xeon E-2x00 не обновлялась достаточно давно: процессоры серии E-2200 были представлены ещё в 2019 году. На тот момент это был действительно прорыв в сегменте чипов Intel начального уровня — они впервые получили до 8 ядер Coffee Lake-S, а поддерживаемый объём памяти вырос с 64 до 128 Гбайт. Однако на сегодня таких возможностей уже может оказаться недостаточно: у E-2200 нет AVX-512 с VNNI, шина PCIe ограничена версией 3.0, а графическое ядро HD Graphics P630 и по меркам 2019 года быстрым назвать было нельзя.

Источник изображений: Intel 10 новых процессоров Xeon E-2300, анонсированных Intel сегодня, должны заполнить пустующую нишу младших бизнес-решений. Нововведений в новой платформе не так уж мало, как может показаться на первый взгляд, ведь максимальное количество процессорных ядер у Xeon E-2300 по-прежнему восемь. Однако их максимальная частота выросла до 5,1 ГГц. Изменился процессорный разъём, теперь это LGA1200.  Ядра 11-го поколения Rocket Lake-E (Cypress Cove) по-прежнему используют 14-нм техпроцесс, но оптимизированная микроархитектура позволила Xeon E-2300 быть быстрее соответствующих моделей предыдущего поколения на 17%, и это без учёта качественных нововведений — теперь у них есть AVX-512 с поддержкой инструкций VNNI, ускоряющих работу нейросетей. Нововведения касаются и вопросов информационной безопасности, в которой малый бизнес нуждается не меньше крупного. Как и «большие» Xeon на базе Ice Lake-SP, процессоры Xeon E-2300 получили «взрослую» поддержку защищённых анклавов SGX объёмом до 512 Мбайт, что существенно выше максимально доступных для прошлого поколения Xeon E 64 Мбайт. Максимальный объём памяти остался прежним, но скорость подросла — до 128 Гбайт DDR4-3200 ECC UDIMM в двух каналах (2DPC). Весьма важно также появление нового графического ядра с архитектурой Xe-LP. Конечно, высокой 3D-производительности от него ждать не стоит, но даже в этом оно на шаг впереди устаревшей архитектуры. К этому стоит добавить поддержку HDMI 2.0b и DP 1.4a, аппаратное декодирование 12-бит HEVC и VP9 и 10-бит AV1, а также кодирование в 8-бит AVC и 10-бит HEVC и VP9. Поддержка PCIe 4.0 пришла и на платформу Xeon E — новые процессоры могут предложить 20 линий PCIe 4.0, причём с поддержкой бифуркации. Ещё 24 линии PCIe 3.0 включает чипсет серии C250. В нём же имеется поддержка 8 портов SATA-3 и USB 3.2 Gen 2x2 — до трёх портов со скоростью 20 Гбит/с. Сетевая часть может быть реализована как на базе недорогих чипов i210, так и более производительных i225 (2,5 Гбит/с) или x550 (10 Гбит/с).  В новой серии, как уже было сказано, представлено 10 процессоров, стоимостью от $182 до $539 и теплопакетами от 65 до 95 Вт. Лишь две младшие модели в списке не имеют поддержки Hyper-Threading. Все Xeon E-2300 располагают встроенным движком Manageability Engine 15 и поддержкой Intel Server Platform Services 6, облегчающей развёртывание и удалённое управление. Свои решения на базе новой платформы представят все ведущие производители серверного оборудования.

01.09.2021 [23:58], Андрей Галадей

Ветераны индустрии основали стартап Ventana для создания чиплетных серверных процессоров RISC-VСтартап Ventana Micro Systems, похоже, намерен перевернуть рынок серверов. Компания заявила о разработке высокопроизводительных процессоров на архитектуре RISC-V для центров обработки данных. Первые образцы фирменных CPU будут переданы клиентам во второй половине следующего года, а поставки начнутся в первой половине 2023 года. При этом процессоры получат чиплетную компоновку — различные модули и кристаллы на общей подложке. Основные процессорные ядра разработает сама Ventana, а вот остальные чиплеты будут создаваться под нужды определённых заказчиков. CPU-блоки будут иметь до 16 ядер, которые, как обещается, окажутся быстрее любых других реализаций RV64. Использование RISC-V позволит разрабатывать сверхмощные решения в рекордные сроки и без значительного бюджета. Ядра будут «выпекаться» на TSMC по 5-нм нормам, но для остальных блоков могут использовать другие техпроцессы и фабрики.  Ventana будет следить за процессом их создания и упаковывать до полудюжины блоков в одну SoC. Для соединения ядер, кеша и других компонентов будет использоваться фирменная кеш-когерентная шина, которая обеспечит задержку порядка 8 нс и скорость передачи данных 16 Гбит/с на одну линию. Основными заказчиками, как ожидается, станут гиперскейлеры и крупные IT-игроки, которым часто требуется специализированное «железо» для ЦОД, 5G и т.д. Сегодня Ventana объявила о привлечении $38 млн в рамках раунда B. Общий же объём инвестиций составил $53 млн. Компания была основана в 2018 году. Однако это не совсем обычный стартап — и сами основатели, и команда являются настоящими ветеранами индустрии. Все они имеют многолетний опыт работы в Arm, AMD, Intel, Samsung, Xilinx и целом ряде других крупных компаний в области микроэлектроники. Часть из них уже имела собственные стартапы, которые были поглощены IT-гигантами.

24.08.2021 [04:11], Алексей Степин

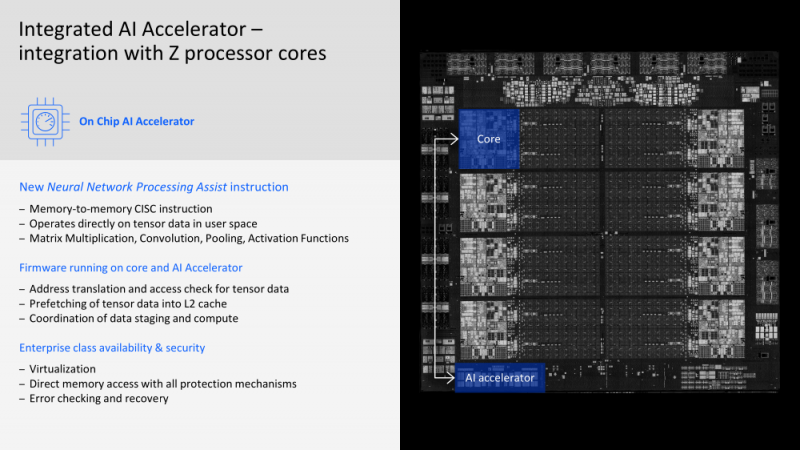

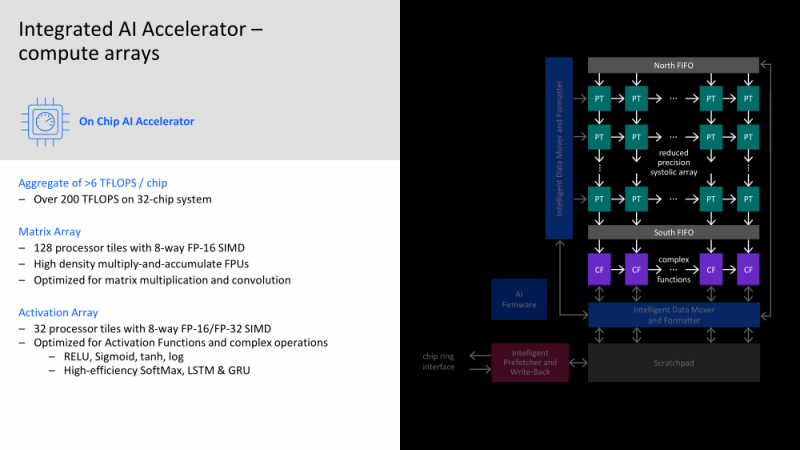

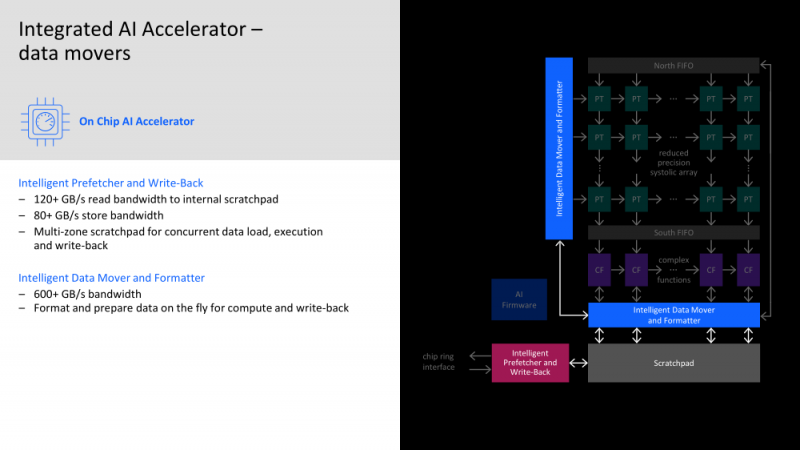

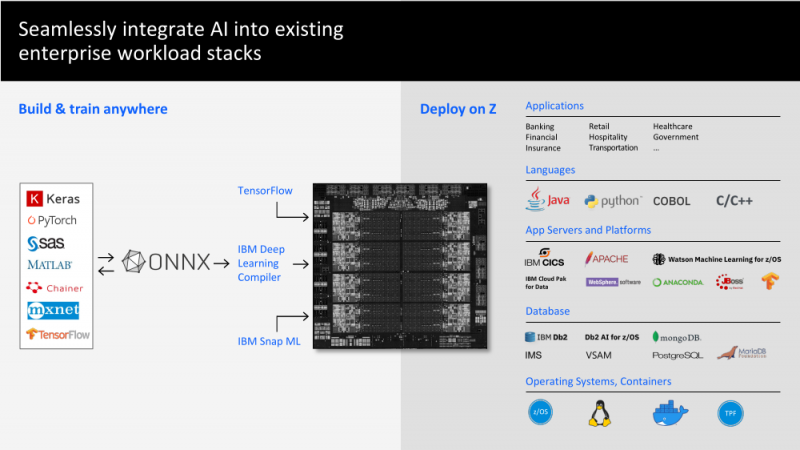

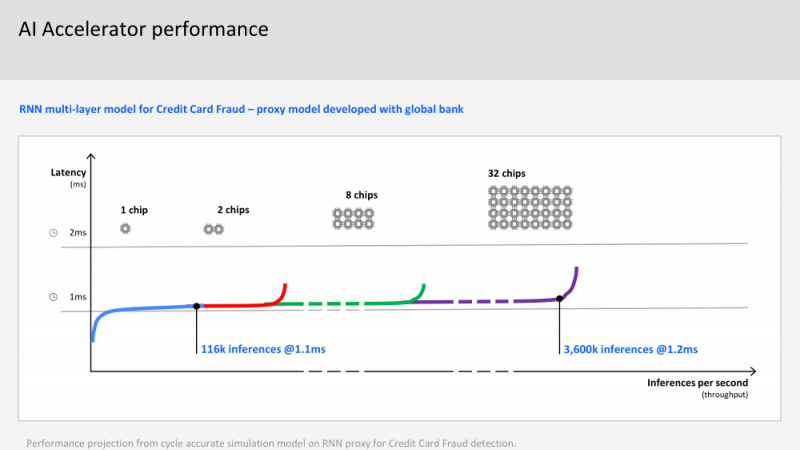

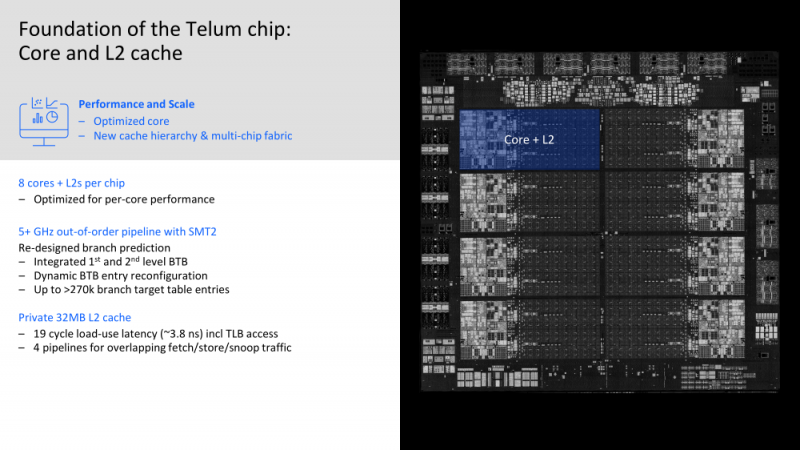

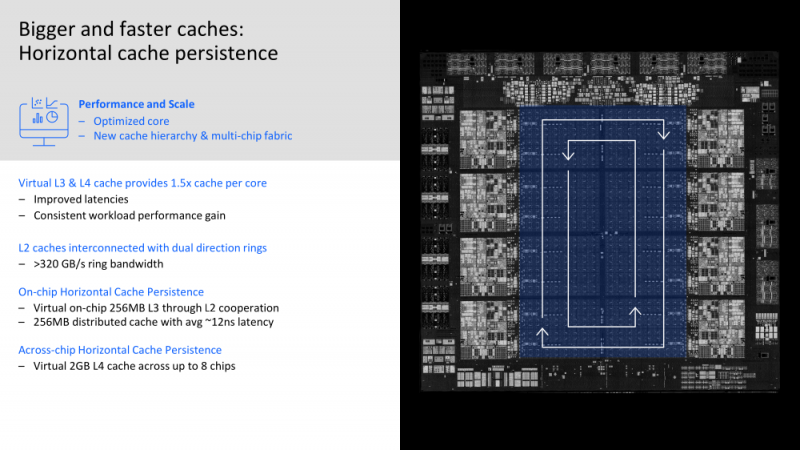

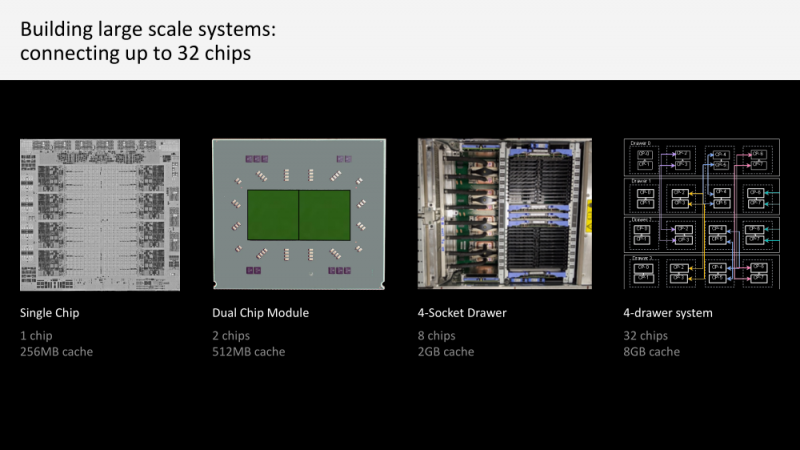

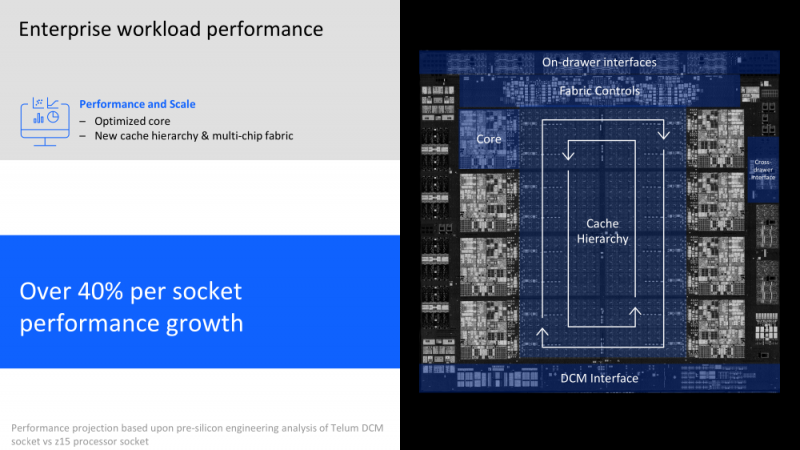

IBM представила процессоры Telum: 8 ядер, 5+ ГГц, L2-кеш 256 Мбайт и ИИ-ускорительФинансовые организации, системы бронирования и прочие операторы бизнес-критичных задач любят «большие машины» IBM за надёжность. Недаром литера z в названии систем означает Zero Downtime — нулевое время простоя. На конференции Hot Chips 33 компания представила новое поколение z-процессоров, впервые в истории получившее собственное имя Telum (дротик в переводе с латыни). «Оружейное» название выбрано неспроста: в новой архитектуре IBM внедрила и новые, ранее не использовавшиеся в System z решения, предназначенные, в частности, для борьбы с фродом. Одни из ключевых заказчиков IBM — крупные финансовые корпорации и банки — давно ждали встроенных ИИ-средств, поскольку их системы должны обрабатывать тысячи и тысячи транзакций в секунду, и делать это максимально надёжно. Одной из целей при разработке Telum было внедрение инференс-вычислений, происходящих в реальном времени прямо в процессе обработки транзакции и без отсылки каких-либо данных за пределы системы. Поэтому инференс-ускоритель в Telum соединён напрямую с подсистемой кешей и использует все механизмы защиты процессора и памяти z/Architecture. И сам он тоже несёт ряд характерных для z подходов. Так, управляет работой акселератора отдельная «прошивка» (firmware), которую можно менять для оптимизации задач конкретного клиента. Она выполняется на одном из ядер и собственно ускорителе, который общается с данным ядром, и отвечает за обращения к памяти и кешу, безопасность и целостность данных и управление собственно вычислениями. Акселератор включает два вида движков. Первый имеет 128 SIMD-блоков для MAC-операций с FP16-данными и нужен для перемножения и свёртки матриц. У второго всего 32 SIMD-блока, но он может работать с FP16/FP32-данными и оптимизирован для функций активации сети и других, более комплексных задач. Дополняет их блок сверхбыстрой памяти (scratchpad) и «умный» IO-движок, ответственный за перемещение и подготовку данных, который умеет переформатировать их на лету. Scratchpad подключён к блоку, который подкачивает данные из L2-кеша и отправляет обратно результаты вычислений. IBM отдельно подчёркивает, что наличие выделенного ИИ-ускорителя позволяет параллельно использовать и обычные SIMD-блоки в ядрах, явно намекая на AVX-512 VNNI. Впрочем, в Sapphire Rapids теперь тоже есть отдельный AMX-блок в ядре, который однако скромнее по функциональности. Доступ к ускорителю возможен из пространства пользователя, в том числе в виртуализированном окружении. Для работы с новым ускорителем компания предлагает IBM Deep Learning Compiler, который поможет оптимизировать импортируемые ONNX-модели. Также есть готовая поддержка TensorFlow, IBM Snap ML и целого ряда популярных средств разработки. На процессор приходится один ИИ-ускоритель производительностью более 6 Тфлопс FP16. На тестовой RNN-модели для защиты от фрода чип может выполнять 116 тыс. инференс-операций с задержкой в пределах 1,1 мс, а для системы из 32 процессоров этот показатель составляет уже 3,6 млн инференс-операций, а латентность при этом возрастает всего лишь до 1,2 мс. Помимо ИИ-акселератора также имеется общий для всех ядер ускоритель (де-)компрессии (gzip) + у каждого ядра есть ещё и движок для CSMP. Ну и ускорители для сортировки и шифрования тоже никуда не делись. За надёжность отвечают сотни различных механизмов проверки и перепроверки работоспособности. Так, например, регистры и кеш дублируются, позволяя в случае сбоя ядра сделать его полную перезагрузку и продолжить выполнение задач ровно с того места, где оно прервалось. А для оперативной памяти, которая в обязательном порядке шифруется, используется режим Redundant Array of Memory (RAIM), своего рода RAID-массив, где одна кеш-линия «размазывается» сразу между восемью модулями. Telum, унаследовав многое от своего предшественника z15, всё же кардинально отличается от него. Процессор содержит восемь ядер с поддержкой «умного» глубокого внеочередного исполнения и SMT2, работающих на частоте более 5 ГГц. Каждому ядру полагается 32 Мбайт L2-кеша, так что на его фоне другие современные CPU выглядят блекло. Но не всё так просто. Между собой кеши общаются посредством двунаправленной кольцевой шины с пропускной способностью более 320 Гбайт/с, формируя таким образом виртуальный L3-кеш объёмом 256 Мбайт и со средней задержкой в 12 нс. Каждый чип Telum может содержать один (SCM) или два (DCM) процессора. А в одном узле может быть до четырёх чипов, то есть до восьми CPU, объединённых по схеме каждый-с-каждым с той же скоростью 320 Гбайт/с. Таким образом, в рамках узла формируется виртуальный L4-кеш объёмом уже 2 Гбайт. Плоская топология кешей, по данным IBM, обеспечивает новым процессорам меньшую латентность в сравнении с z15. Масштабирование возможно до 32 процессоров, но отдельные узлы связаны несколькими подключениями со скоростью «всего» 45 Гбайт/с в каждую сторону. В целом, IBM говорит о 40% прироста производительности в сравнении с z15 в пересчёте на сокет. Telum содержит 22 млрд транзисторов и имеет TDP на уровне 400 Вт в нормальном режиме работы. Процессор будет производиться на мощностях Samsung с использованием 7-нм техпроцесса EUV. Он станет основной для мейнфреймов IBM z16 и LinuxNOW. Программной платформой всё так же будут как традиционная z/OS, так и Linux.

19.08.2021 [16:00], Игорь Осколков

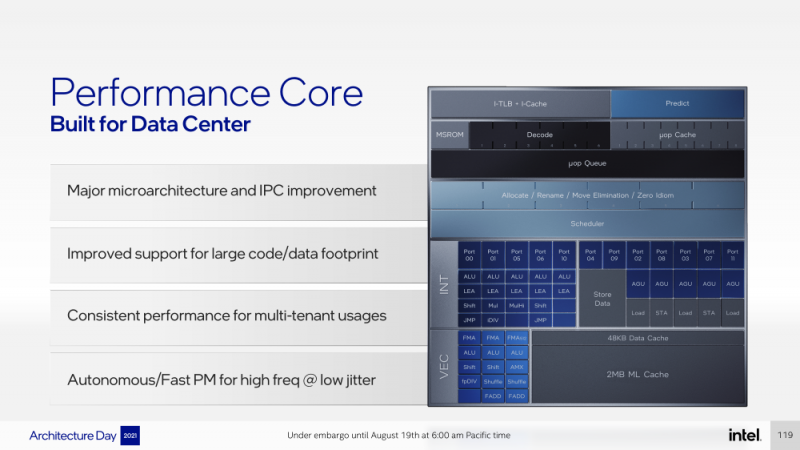

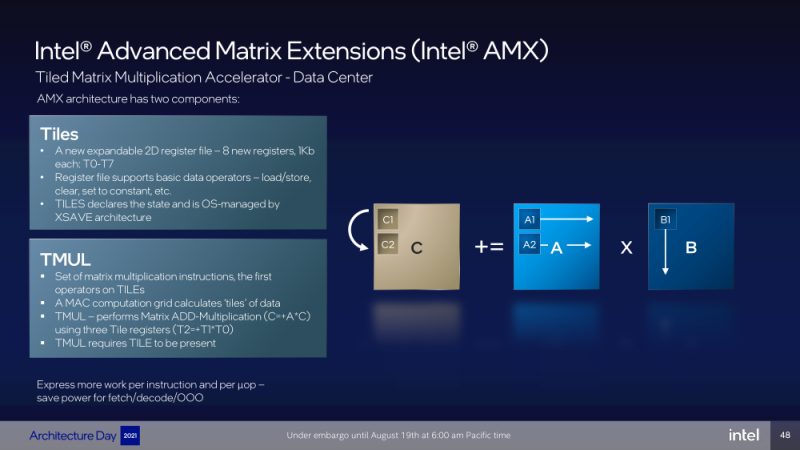

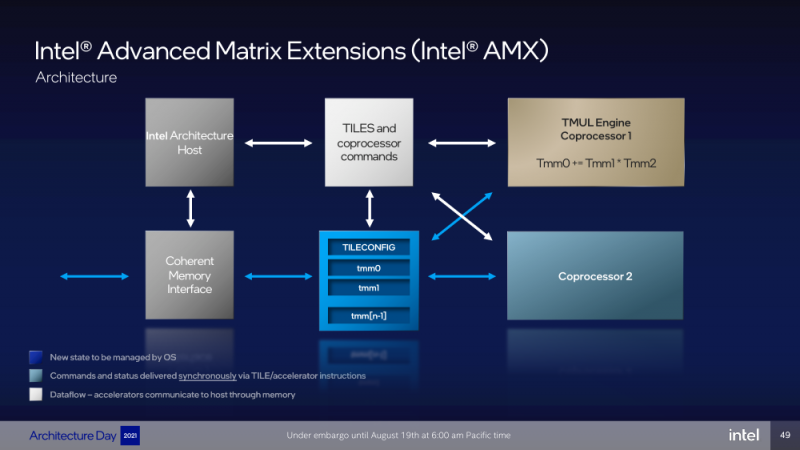

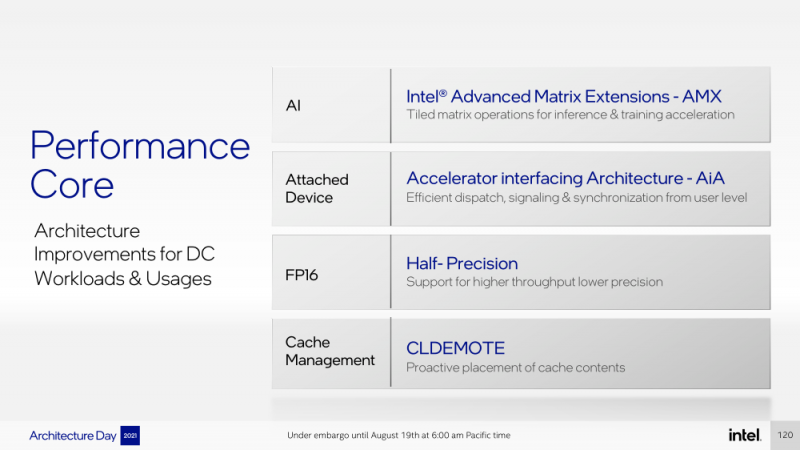

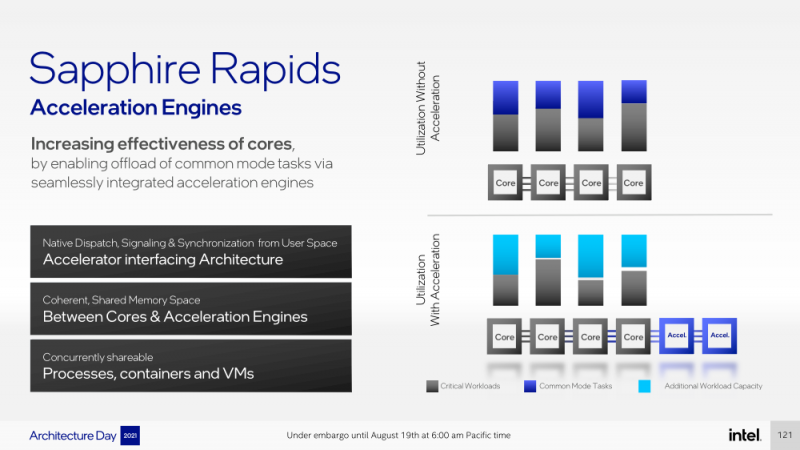

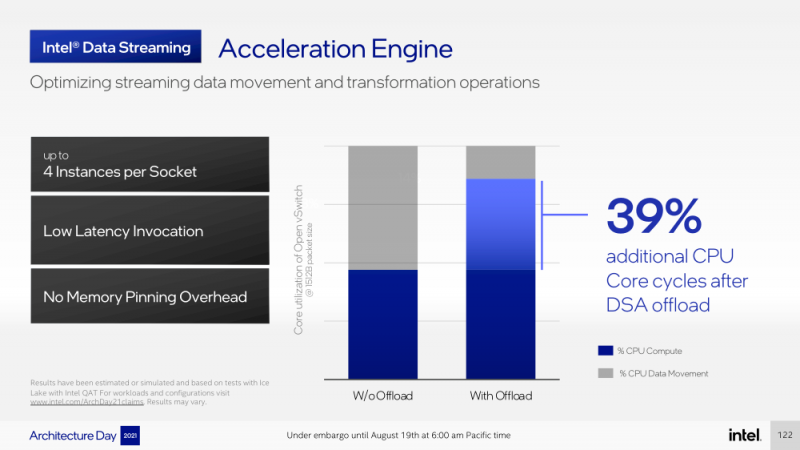

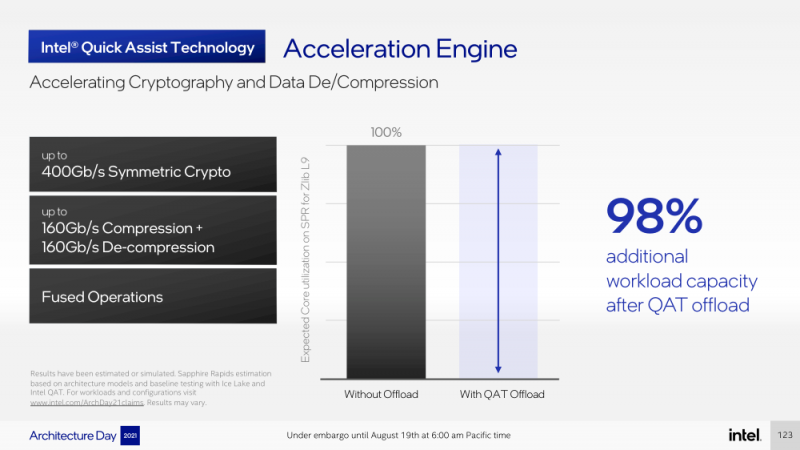

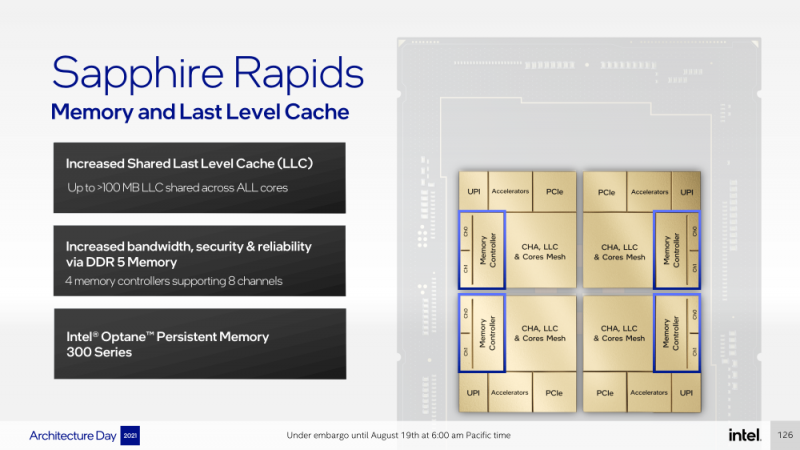

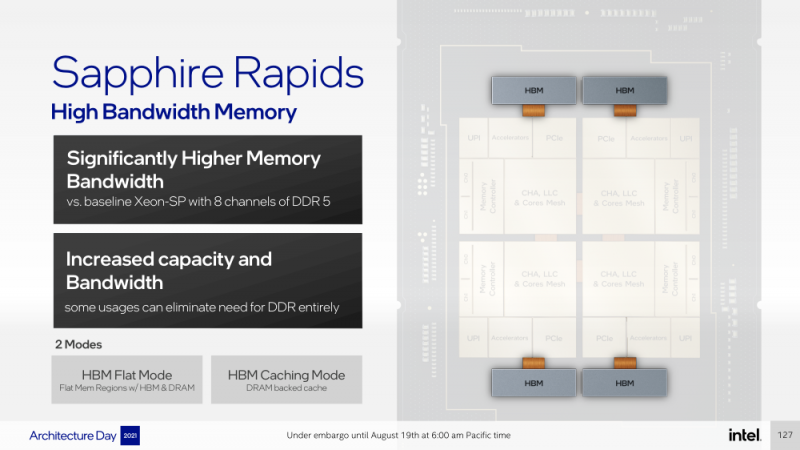

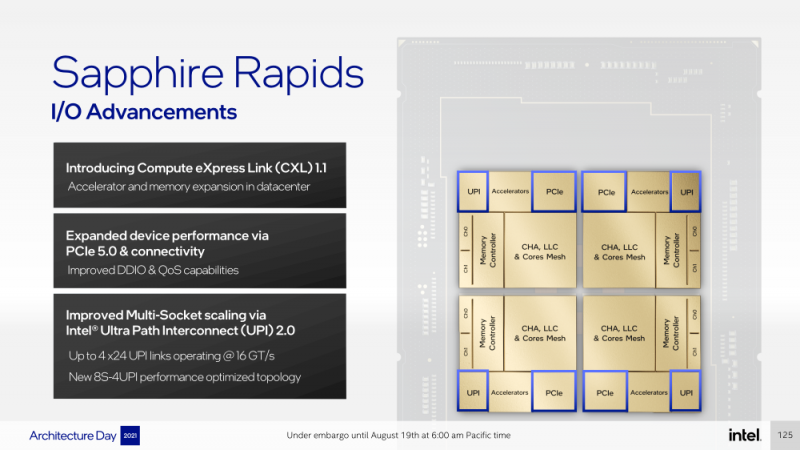

Intel представила Xeon Sapphire Rapids: четырёхкристалльная SoC, HBM-память, новые инструкции и ускорителиВ рамках Architecture Day компания Intel рассказала о грядущих серверных процессорах Sapphire Rapids, подтвердив большую часть опубликованной ранее информации и дополнив её некоторыми деталями. Intel позиционирует новинки как решение для более широкого круга задач и рабочих нагрузок, чем прежде, включая и популярные ныне микросервисы, контейнеризацию и виртуализацию. Компания обещает, что CPU будут сбалансированы с точки зрения вычислений, работой с памятью и I/O. Новые процессоры, наконец, получили чиплетную, или тайловую в терминологии Intel, компоновку — в состав SoC входят четыре «ядерных» тайла на техпроцессе Intel 7 (10 нм Enhanced SuperFIN). Каждый тайл объединён с соседом посредством EMIB. Их системные агенты, включающие общий на всех L3-кеш объём до 100+ Мбайт, образуют быструю mesh-сеть с задержкой порядка 4-8 нс в одну сторону. Со стороны процессор будет «казаться» монолитным. Каждые ядро или поток будут иметь свободный доступ ко всем ресурсам соседних тайлов, включая кеш, память, ускорители и IO-блоки. Потенциально такой подход более выгоден с точки зрения внутреннего обмена данными, чем в случае AMD с общим IO-блоком для всех чиплетов, которых в будущих EPYC будет уже 12. Но как оно будет на самом деле, мы узнаем только в следующем году — выход Sapphire Rapids запланирован на первый квартал 2022-го, а массовое производство будет уже во втором квартале. Ядра Sapphire Rapids базируются на микроархитектуре Golden Cove, которая стала шире, глубже и «умнее». Она же будет использована в высокопроизводительных ядрах Alder Lake, но в случае серверных процессоров есть некоторые отличия. Например, увеличенный до 2 Мбайт на ядро объём L2-кеша или новый набор инструкций AMX (Advanced Matrix Extension). Последний расширяет ИИ-функциональность CPU и позволяет проводить MAC-операции над матрицами, что характерно для такого рода нагрузок. Для AMX заведено восемь выделенных 2D-регистров объёмом по 1 Кбайт каждый (шестнадцать 64-байт строк). Отдельный аппаратный блок выполняет MAC-операции над тремя регистрами, причём делаться это может параллельно с исполнением других инструкций в остальной части ядра. Настройкой параметров и содержимого регистров, а также перемещением данных занимается ОС. Пока что в процессорах представлен только MAC-блок, но в будущем могут появиться блоки и для других, более сложных операций. В пике производительность AMX на INT8 составляет 2048 операций на цикл на ядро, что в восемь раз больше, чем при использовании традиционных инструкций AVX-512 (на двух FMA-портах). На BF16 производительность AMX вдвое ниже, но это всё равно существенный прирост по сравнению с прошлым поколением Xeon — Intel всё так же пытается создать универсальные ядра, которые справлялись бы не только с инференсом, но и с обучением ИИ-моделей. Тем не менее, компания говорит, что возможности AMX в CPU будут дополнять GPU, а не напрямую конкурировать с ними. К слову, именно Sapphire Rapids должен, наконец, сделать BF16 более массовым, поскольку Cooper Lake, где поддержка этого формата данных впервые появилась в CPU Intel, имеет довольно узкую нишу применения. Из прочих архитектурных обновлений можно отметить поддержку FP16 для AVX-512, инструкции для быстрого сложения (FADD) и более эффективного управления данными в иерархии кешей (CLDEMOTE), целый ряд новых инструкций и прерываний для работы с памятью и TLB для виртуальных машин (ВМ), расширенную телеметрию с микросекундными отсчётами и так далее. Последние пункты, в целом, нужны для более эффективного и интеллектуального управления ресурсами и QoS для процессов, контейнеров и ВМ — все они так или иначе снижают накладные расходы. Ещё больше ускоряют работу выделенные акселераторы. Пока упомянуты только два. Первый, DSA (Data Streaming Accelerator), ускоряет перемещение и передачу данных как в рамках одного хоста, так и между несколькими хостами. Это полезно при работе с памятью, хранилищем, сетевым трафиком и виртуализацией. Второй упомянутый ускоритель — это движок QAT (Quick Assist Engine), на который можно возложить операции или сразу цепочки операций (де-)компрессии (до 160 Гбит/с в обе стороны одновременно), хеширования и шифрования (до 400 Гбитс/с) в популярных алгоритмах: AES GCM/XTS, ChaChaPoly, DH, ECC и т.д. Теперь блок QAT стал частью самого процессора, тогда как прежде он был доступен в составе некоторых чипсетов или в виде отдельной карты расширения. Это позволило снизить задержки и увеличить производительность блока. Кроме того, QAT можно будет задействовать, например, для виртуализации или Intel Accelerator Interfacing Architecture (AiA). AiA — это ещё один новый набор инструкций, предназначенный для более эффективной работы с интегрированными и дискретными ускорителями. AiA помогает с управлением, синхронизацией и сигнализацией, что опять таки позволит снизить часть накладных расходов при взаимодействии с ускорителями из пространства пользователя. Подсистема памяти включает четыре двухканальных контроллера DDR5, по одному на каждый тайл. Надо полагать, что будут доступные четыре же NUMA-домена. Больше деталей, если не считать упомянутой поддержки следующего поколения Intel Optane PMem 300 (Crow Pass), предоставлено не было. Зато было официально подтверждено наличие моделей с набортной HBM, тоже по одному модулю на тайл. HBM может использоваться как в качестве кеша для DRAM, так и независимо. В некоторых случаях можно будет обойтись вообще без DRAM. Про PCIe 5.0 и CXL 1.1 (CXL.io, CXL.cache, CXL.memory) добавить нечего, хотя в рамках другого доклада Intel ясно дала понять, что делает ставку на CXL в качестве интерконнекта не только внутри одного узла, но и в перспективе на уровне стойки. Для объединения CPU (бесшовно вплоть до 8S) всё так же будет использоваться шина UPI, но уже второго поколения (16 ГТ/с на линию) — по 24 линии на каждый тайл. Конкретно для Sapphire Rapids Intel пока не приводит точные данные о росте IPC в сравнении с Ice Lake-SP, ограничиваясь лишь отдельными цифрами в некоторых задачах и областях. Также не был указан и ряд других важных параметров. Однако AMD EPYC Genoa, если верить последним утечкам, даже по чисто количественным характеристикам заметно опережает Sapphire Rapids.

30.07.2021 [21:05], Алексей Степин

Конец эпохи: Intel окончательно прекратила поставки процессоров ItaniumПервая попытка Intel покорить рынок массовых 64-бит систем окончилась неудачей — любопытная сама по себе архитектура Itanium (IA64) была несовместима со сложившейся экосистемой x86. Однако лишь сегодня в истории можно окончательно поставить точку: компания прекратила последние отгрузки процессоров Itanium. Сейчас поддержка 64-бит вычислений привычна и является частью любого достаточно современного процессора. Но так было не всегда: в конце 90-х и начале 2000-х ограничения, накладываемые 32-бит разрядностью хотя и были очевидны, рынок высокопроизводительных 64-бит процессоров для серверов и рабочих станций принадлежал компаниям Sun, Silicon Graphics, DEC и IBM. Все они имели RISC-архитектуру и не имели совместимости с x86.

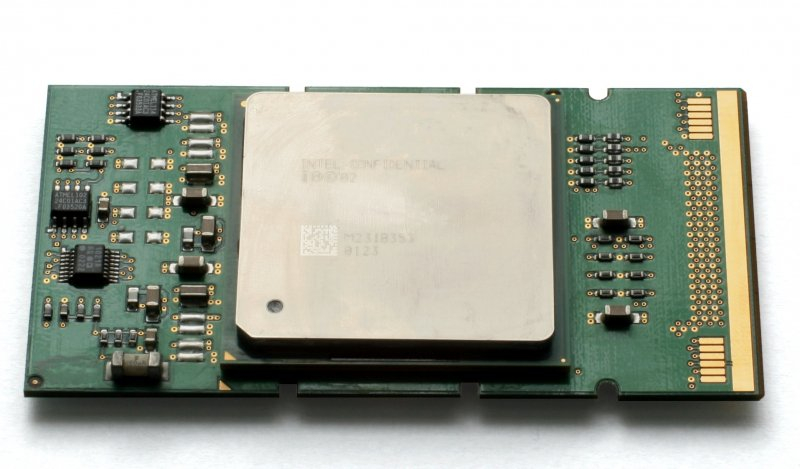

Форм-фактор Itanium: нечто среднее между слотовыми Pentium II/III и привычным PGA/LGA Itanium, или IA64, совместная разработка Intel и Hewlett-Packard, должна была вернуть этим компаниям первенство в сфере мощных CPU. И ставка была сделана на уникальную архитектуру EPIC (разновидность VLIW) с явным параллелизмом команд. Сама по себе IA64 обладала рядом преимуществ, однако требовала тонкой проработки ПО на уровне компилятора, поскольку процессоры EPIC во многом полагаются именно на него, а не на аппаратный планировщик.

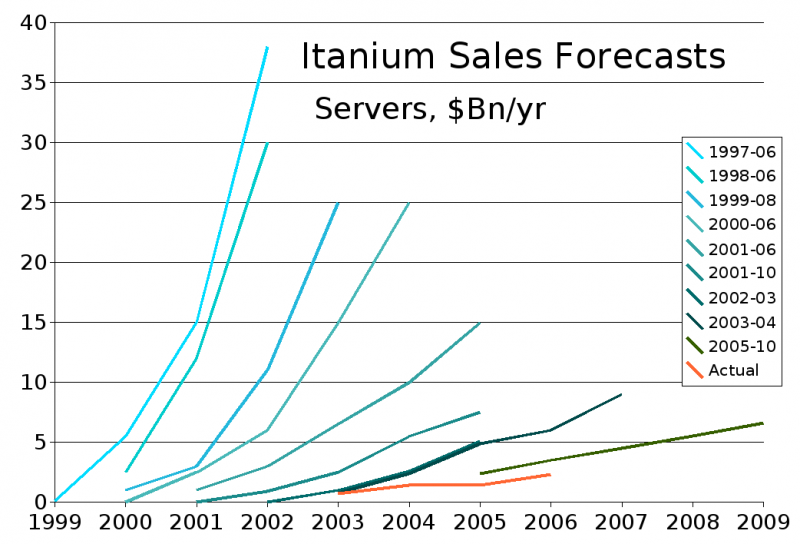

Itanium: радужные надежды и суровая реальность (красная линия) Отказ от последнего позволял потратить освободившийся транзисторный бюджет на более важные, по мнению Intel и HP, цели — например, на увеличение производительности вычислений с плавающей запятой. Но инфраструктура программного обеспечения к моменту анонса Itanium уже была весьма развитой. При этом новое, 64-бит ПО ещё надо было создать и, что гораздо важнее и сложнее, правильным образом оптимизировать, а уже имевшееся на новых CPU работало медленно из-за необходимости эмуляции x86. Компании пытались развивать IA64 до 2017 года, когда были представлены чипы Itanium Kittson с 8 ядрами и частотой до 2,66 ГГц, но то, что затея с новой архитектурой оказалась неудачной, было понятно уже после анонса первых процессоров AMD x86-64, полностью совместимых как с 32-бит, так и с 64-бит приложениями x86. В начале 2021 года Линус Торвальдс объявил о фактической смерти архитектуры и поддержка IA64 была исключена из новых ядер Linux. А сегодня можно говорить об окончательном завершении эры Itanium.

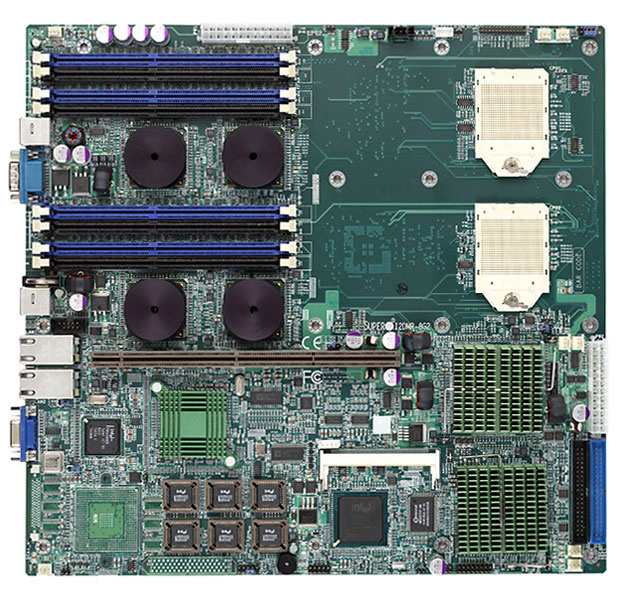

Раритет: Supermicro i2DML-iG2 в форм-факторе EATX с поддержкой Itanium 2. Найти такую плату почти невозможно Сама Intel ещё в 2019-ом официально поставила на Itanium крест, но из-за сложившейся экосистемы заказы на процессоры принимались вплоть до 30 января 2020 года. А вчера компания официально объявила о прекращении поставок последних партий Itanium. Теперь ещё одна процессорная архитектура стала достоянием истории, хотя HPE формально будет поддерживать её до 2025 года. Сами CPU нередко встречаются на онлайн-аукционах, например, на Ebay, но даже для энтузиастов они малоинтересны — найти подходящую системную плату невероятно сложно, а стоить она может намного дороже самих процессоров, да и форм-фактор имеет специфический. |

|