Материалы по тегу: arm

|

29.11.2022 [17:12], Алексей Степин

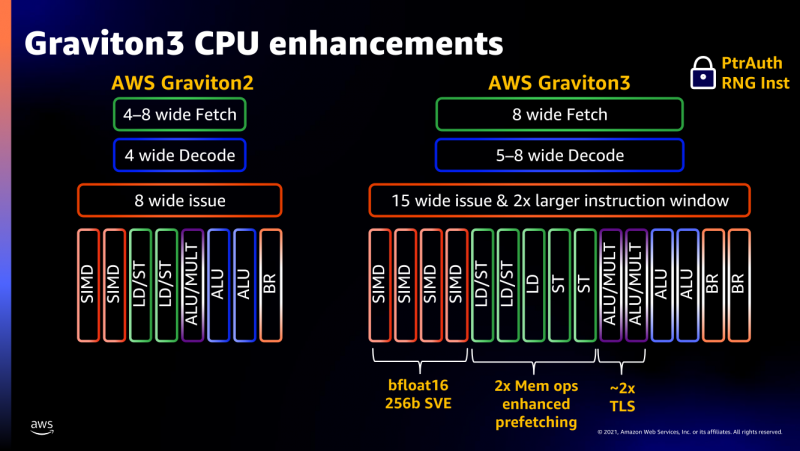

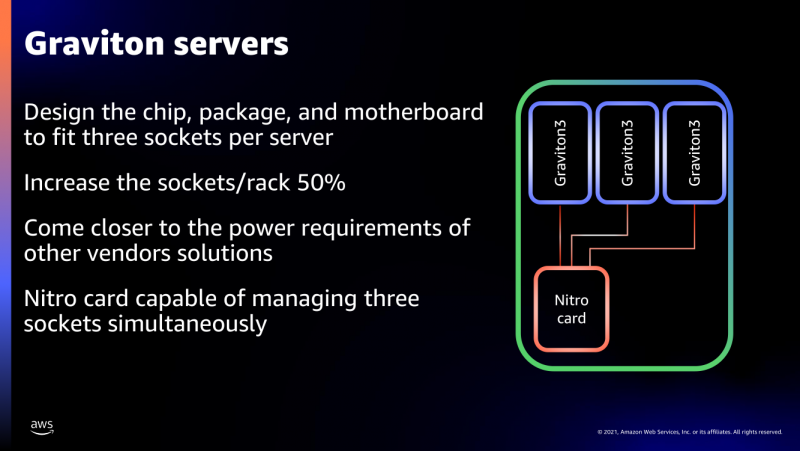

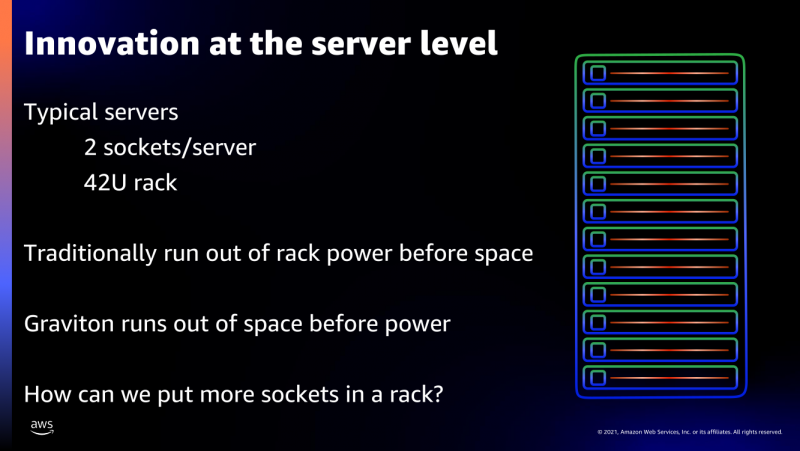

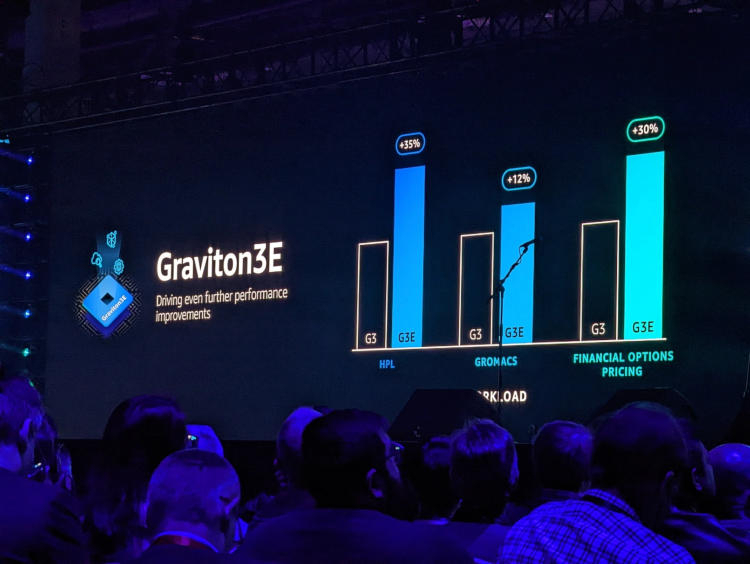

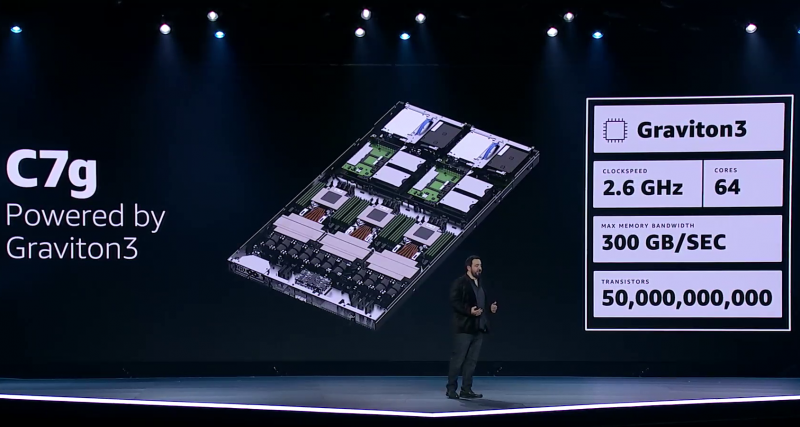

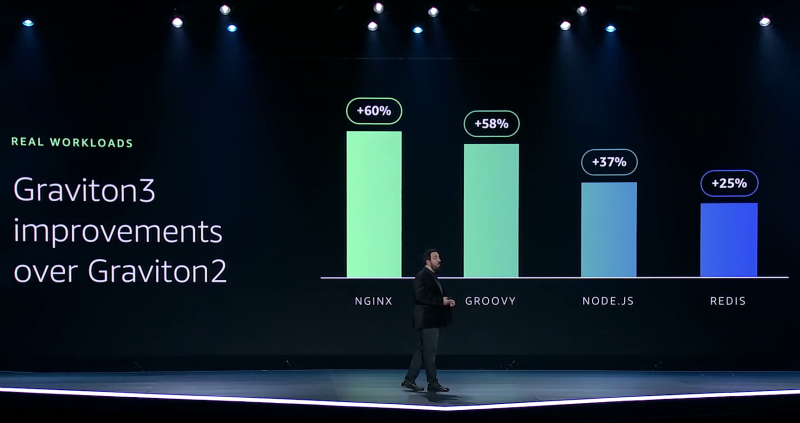

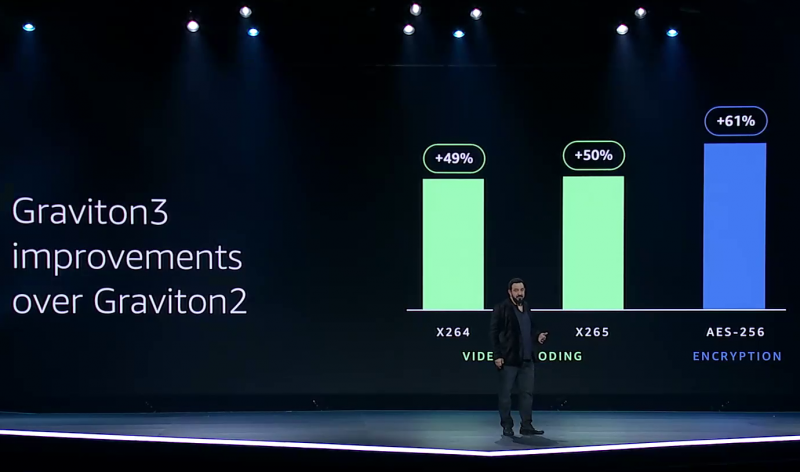

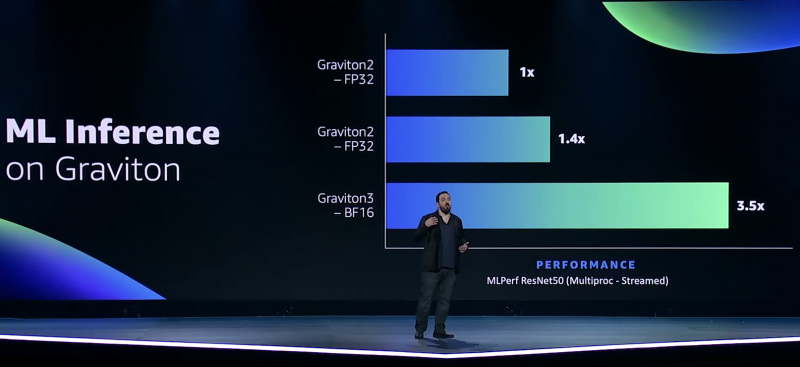

AWS представила Arm-процессор Graviton3E, оптимизированный для задач ИИ и HPCОдин из крупнейших облачных провайдеров, компания Amazon Web Services объявила о доступности новых инстансов EC2 на базе процессора Graviton3E. Новый чип — наследник анонсированного в конце 2021 года Graviton3, 5-нм 64-ядерного процессора на дизайне Arm Neoverse V1 (Zeus) с поддержкой DDR5 и PCI Express 5.0. Graviton3 использует набор команд Armv8.4 c расширениями Neon (4×128 бит) и SVE (2×256 бит) и поддерживает работу с популярными в сфере машинного обучения форматами данных INT8 и BF16. В сравнении c Graviton2 процессор быстрее на 25-60 % при сохранении аналогичного уровня тепловыделения. Дизайн серверов AWS предусматривает наличие трёх процессоров на узел высотой 1U.

Изображения: AWS Новый процессор Graviton3E представляет собой дальнейшее развитие Graviton3. Чип оптимизирован с учётом потребностей рынка высокопроизводительных вычислений и основное внимание в его архитектуре уделено повышению производительности на операциях с плавающей запятой и вычислениях с использованием векторной математики. AWS, к сожалению, пока не раскрывает деталей относительно архитектуры Graviton3E, но прирост производительности на векторных операциях относительно обычного Graviton3 может достигать 35 %. Помимо классического теста HPL новый процессор хорошо проявляет себя в тестах, имитирующих медико-биологические и финансовые задачи.  Сценарии нагрузок, характерные для HPC, как правило, активно оперируют перемещением крупных объемов данных. Чтобы оптимизировать этот процесс, в новых инстансах AWS использует сеть на базе Elastic Fabric с новыми адаптерами Elastic Network Adapter (ENA). Такая сеть оперирует т. н. Scalable Reliable Datagram (SRD) вместо всем привычных TCP-пакетов. SRD позволяет организовать повторную отправку пакетов за микросекунды вместо миллисекунд в классическом Ethernet. Сердцем же новых инстансов AWS стало пятое поколение аппаратных гипервизоров Nitro 5. В сравнении с предыдущим поколением, Nitro 5 обладает вдвое более высокой вычислительной производительностью, на 50 % повышенной пропускной способностью памяти, а также позволяет обрабатывать на 60 % больше сетевых пакетов при сниженной на 30 % латентности.

Здесь и далее источник изображений: AWS Инстансы Hpc7g с процессорами Graviton3E получат внутреннюю сеть с пропускной способностью 200 Гбит/с и станут доступны в различных конфигурациях вплоть до 64 vCPU и 128 ГиБ памяти. Аналогичные параметры имеют инстансы C7gn, предназначенные для задач с интенсивным сетевым трафиком: виртуальных маршрутизаторов, сетевых экранов, балансировщиков нагрузки и т.п. Также компания анонсировала инстансы R7iz, в которых используются процессоры Intel Xeon Scalable четвёртого поколения (Sapphire Rapids) с постоянной частотой всех ядер 3,9 ГГц. Они могут иметь конфигурацию до 128 vCPU с 1 ТиБ памяти.

14.09.2022 [22:28], Игорь Осколков

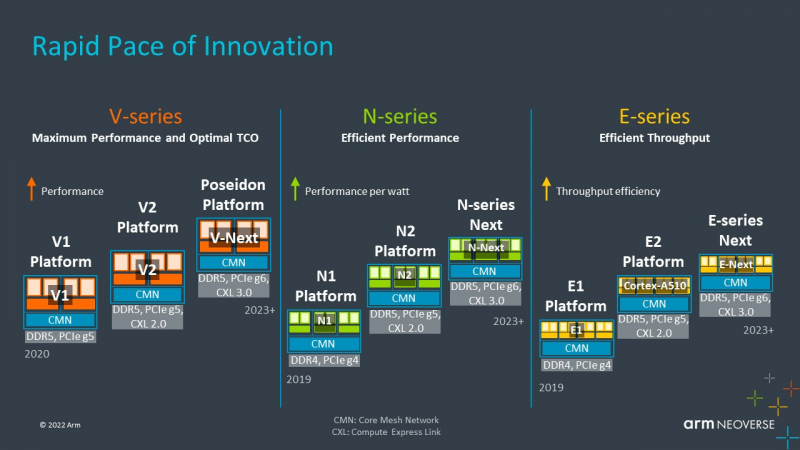

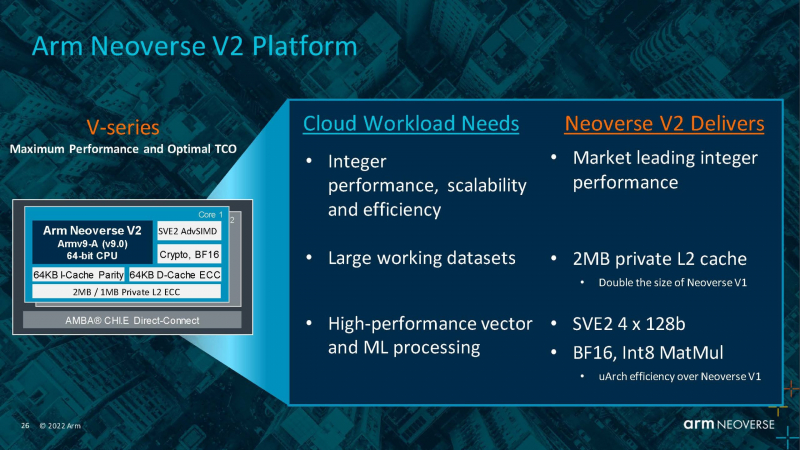

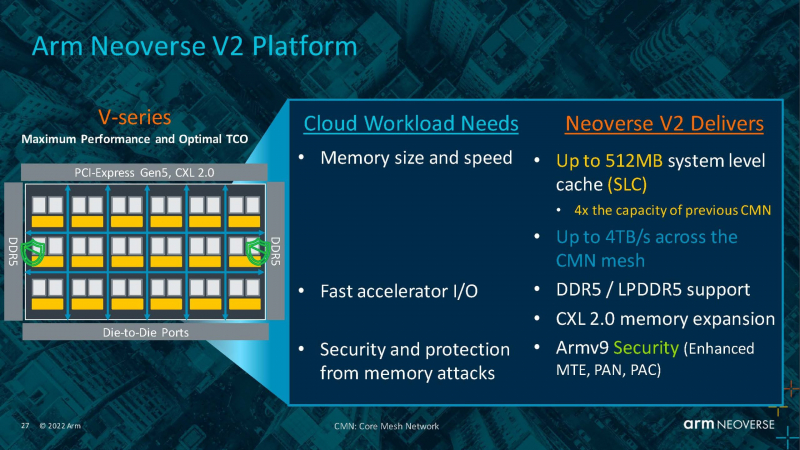

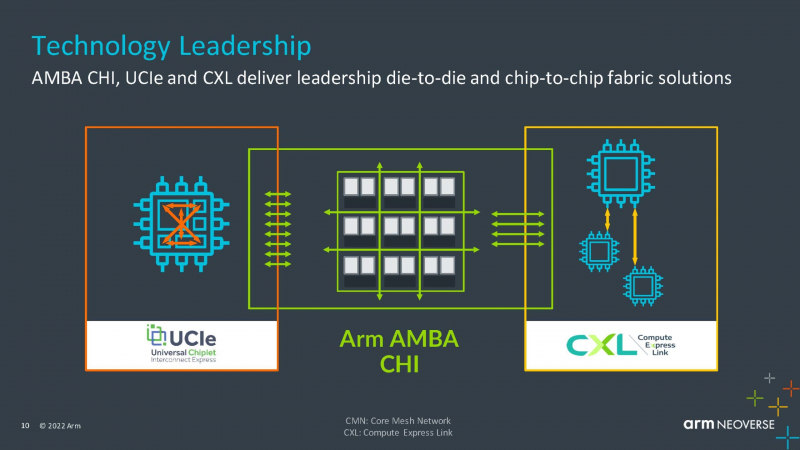

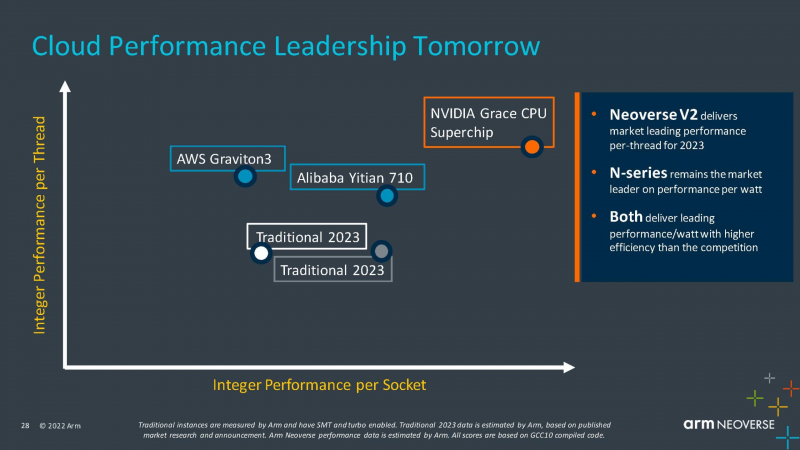

Arm анонсировала серверные ядра Neoverse V2 Demeter, именно они легли в основу процессоров NVIDIA GraceArm анонсировала новые ядра в серии Neoverse, принадлежащие к семейству Armv9 — Neoverse V2 с кодовым названием Demeter (Деметра). В семействе Neoverse V-ядра относятся к высокопроизводительным решениям, ориентированным на гиперскейлеров, облачных провайдеров и поставщиков HPC-решений. Одним из первых продуктов на базе новой платформы станет 72-ядерный серверный процессор NVIDIA Grace, выход которого запланирован на следующий год. Arm пока что не приводит точные характеристики V2-ядер, но говорит о возросшей производительности как целочисленных вычислений, так и вычислений с плавающей запятой. Для новинок заявлена поддержка SVE2-инструкций, наличие четырёх 128-бит векторных блоков, а также блоки для работы с матрицами и поддержка BF16/INT8. Кроме того, ядра получат увеличенный до 2 Мбайт L2-кеш, а также новые механизмы аппаратной защиты и, по-видимому, улучшенные криптографические движки. Объединять ядра и кеши будет когерентная mesh-шина CMN-700 с суммарной пропускной способностью до 4 Тбайт/с, которая может обслуживать до 512 Мбайт кеш-памяти. А за обслуживание связей с другими кристаллами всё так же будет отвечать шина AMBA CHI. Будет предложена поддержка (LP)DDR5(X), CXL 2.0, PCIe 5.0 и UCIe. Также Arm пообещала и далее вкладываться в развитие инициативы SystemReady и совместную с партнёрами оптимизацию системного и прикладного ПО — всё ради упрощения перехода конечных пользователей с x86 на Arm. Впрочем, как отмечает ServeTheHome, в ходе презентации Arm напирала скорее на прирост эффективности с точки зрения именно целочисленных вычислений, что актуально для облаков. x86-лагерь сдавать позиции в этой области не хочет — конкуренцию Arm составят AMD EPYC Bergamo и Intel Xeon Sierra Forest. Но в 2023 году Arm представит следующее поколение высокопроизводительных ядер Neoverse V3 (Poseidon) c PCIe 6.0 и CXL 3.0, а также «сбалансированную» платформу Neoverse N3 и энергоэффективные ядра Neoverse E следующего поколения.

20.08.2022 [22:30], Алексей Степин

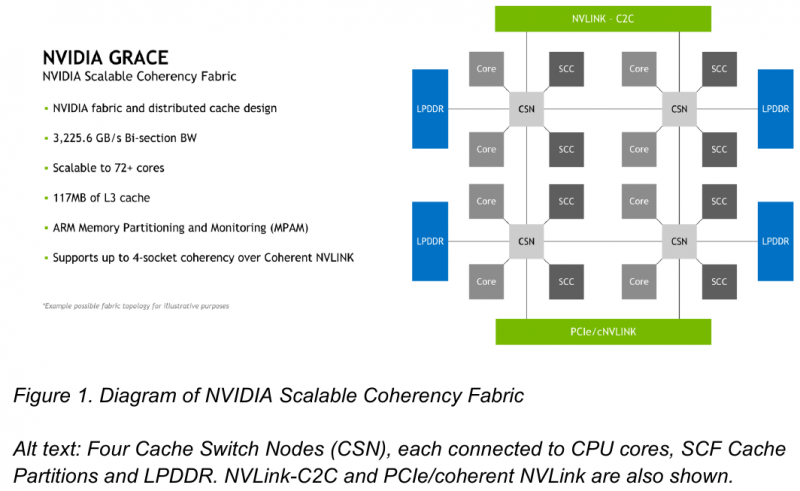

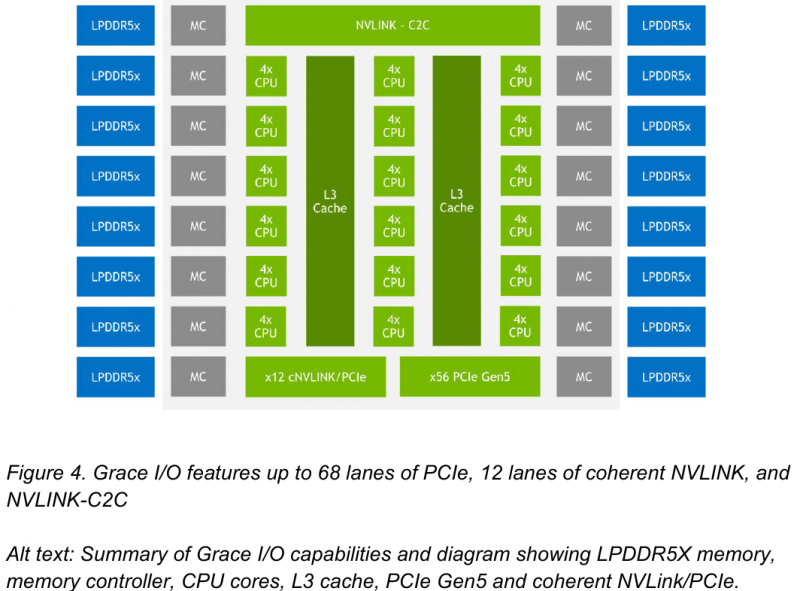

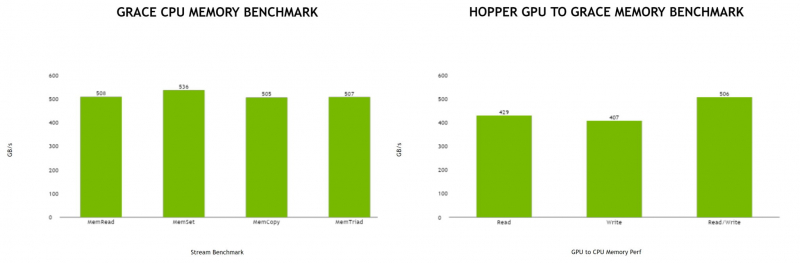

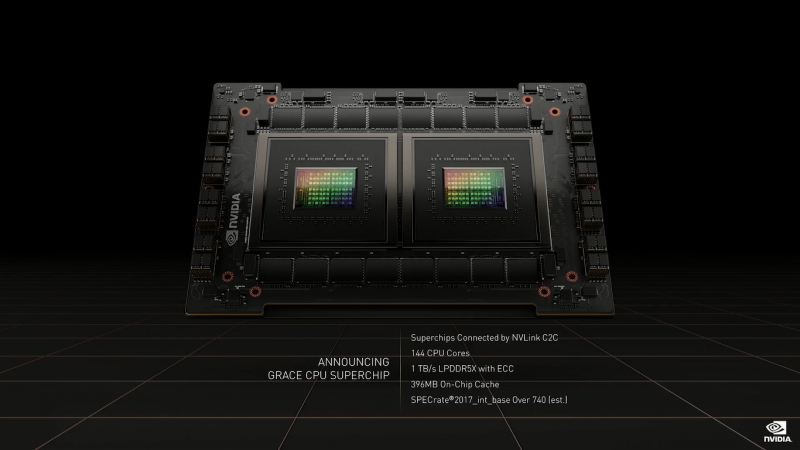

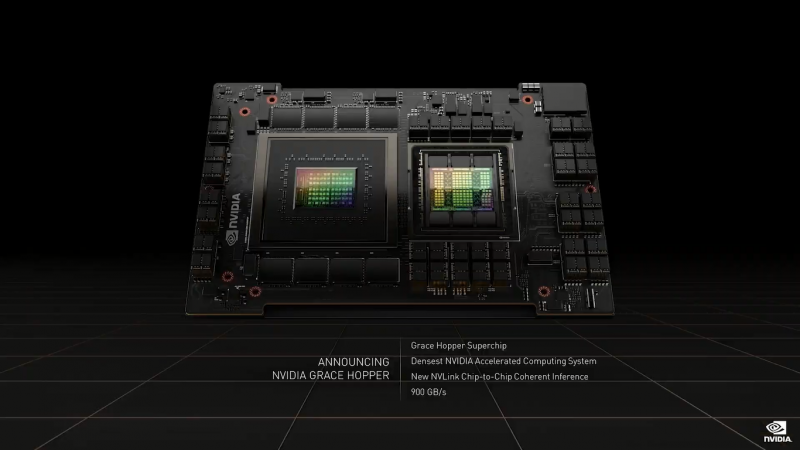

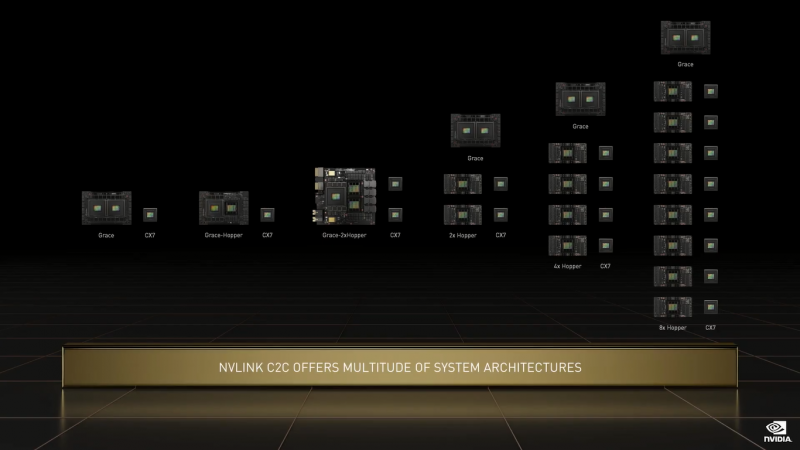

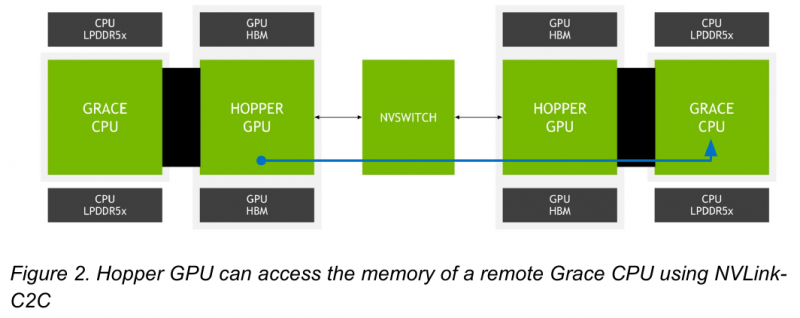

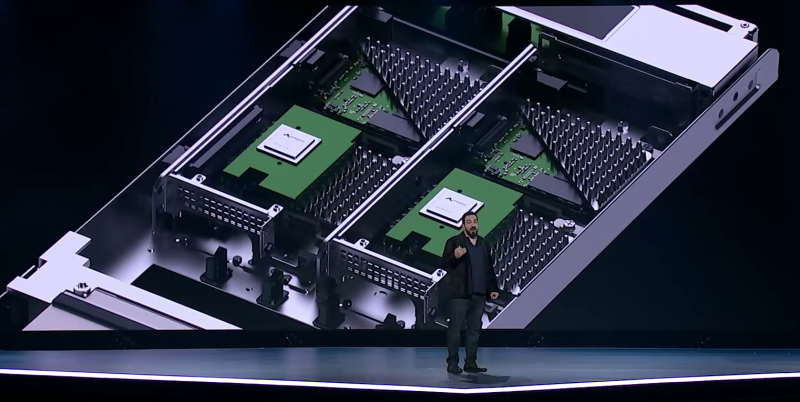

NVIDIA поделилась некоторыми деталями о строении Arm-процессоров Grace и гибридных чипов Grace HopperНа GTC 2022 весной этого года NVIDIA впервые заявила о себе, как о производителе мощных серверных процессоров. Речь идёт о чипах Grace и гибридных сборках Grace Hopper, сочетающих в себе ядра Arm v9 и ускорители на базе архитектуры Hopper, поставки которых должны начаться в первой половине следующего года. Многие разработчики суперкомпьютеров уже заинтересовались новинками. В преддверии конференции Hot Chips 34 компания раскрыла ряд подробностей о чипах. Grace производятся с использованием техпроцесса TSMC 4N — это специально оптимизированный для решений NVIDIA вариант N4, входящий в серию 5-нм процессов тайваньского производителя. Каждый кристалл процессорной части Grace содержит 72 ядра Arm v9 с поддержкой масштабируемых векторных расширений SVE2 и расширений виртуализации с поддержкой S-EL2. Как сообщалось ранее, NVIDIA выбрала для новой платформы ядра Arm Neoverse. Процессор Grace также соответствует ряду других спецификаций Arm, в частности, имеет отвечающий стандарту RAS v1.1 контроллер прерываний (Generic Interrupt Controller, GIC) версии v4.1, блок System Memory Management Unit (SMMU) версии v3.1 и средства Memory Partitioning and Monitoring (MPAM). Базовых кристаллов у Grace два, что в сумме даёт 144 ядра — рекордное количество как в мире Arm, так и x86. Внутренние блоки Grace соединяются посредством фабрики Scalable Coherency Fabric (SCF), вариации NVIDIA на тему сети CMN-700, применяемой в дизайнах Arm Neoverse. Производительность данного интерконнекта составляет 3,2 Тбайт/с. В случае Grace он предполагает наличие 117 Мбайт кеша L3 и поддерживает когерентность в пределах четырёх сокетов (посредством новой версии NVLink). Но SCF поддерживает масштабирование. Пока что в «железе» она ограничена двумя блоками Grace, а это уже 144 ядра и 234 Мбайт L3-кеша. Ядра и кеш-разделы (SCC) рапределены по внутренней mesh-фабрике SCF. Коммутаторы (CSN) служат интерфейсами для ядер, кеш-разделов и остальными частями системы. Блоки CSN общаются непосредственно друг с другом, а также с контроллерами LPDDR5X и PCIe 5.0/cNVLink/NVLink C2C. В чипе реализована поддержка PCI Express 5.0. Всего контроллер поддерживает 68 линий, 12 из которых могут также работать в режиме cNVLink (NVLink с когерентностью). x16-интерфейс посредством бифуркации может быть превращен в два x8. Также на приведённой NVIDIA диаграмме можно видеть целых 16 двухканальных контроллеров LPDDR5x. Заявлена ПСП на уровне свыше 1 Тбайт/с для сборки (до 546 Гбайт/с на кристалл CPU). Основной же межчиповой связи NVIDIA видит новую версию NVLink — NVLink-C2C, которая в семь раз быстрее PCIe 5.0 и способна обеспечить двунаправленную скорость передачи данных на уровне до 900 Гбайт/с, будучи при этом в пять раз экономичнее. Удельное потребление у новинки составляет 1,3 пДж/бит, что меньше, нежели у AMD Infinity Fabric с 1,5 пДж/бит. Впрочем, существуют и более экономичные решения, например, UCIe (~0,5 пДж/бит).

Новый вариант NVLink обеспечит кластер на базе Grace Hopper единым пространством памяти. Источник: NVIDIA NVLink-C2C позволяет реализовать унифицированный «плоский» пул памяти с общим адресным пространством для Grace Hopper. В рамках одного узла возможно свободное обращение к памяти соседей. А вот для объединения нескольких узлов понадобится уже внешний коммутатор NVSwitch. Он будет занимать 1U в высоту, и предоставлять 128 портов NVLink 4 с агрегированной пропускной способностью до 6,4 Тбайт/с в дуплексе.

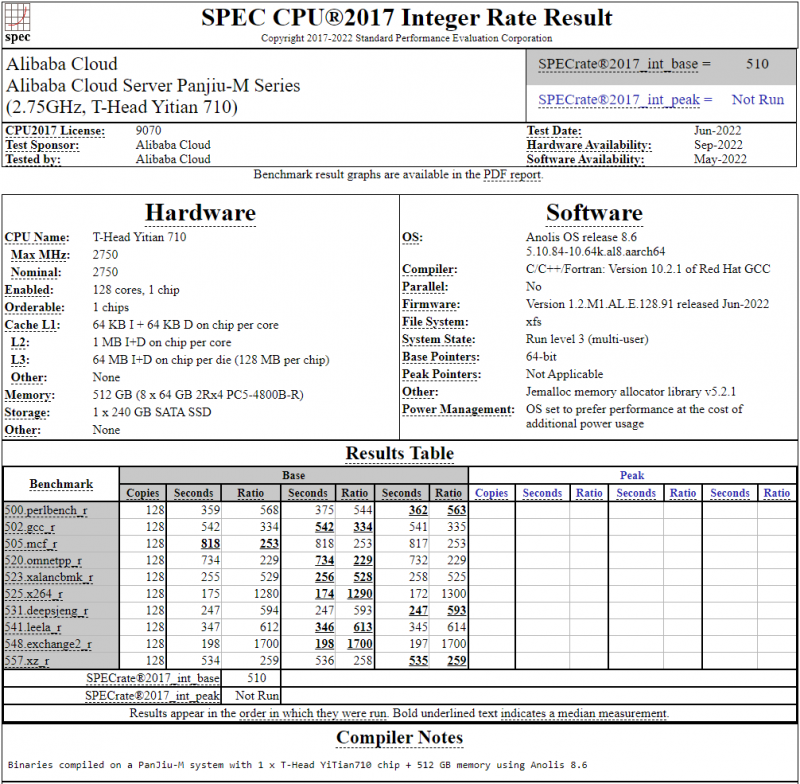

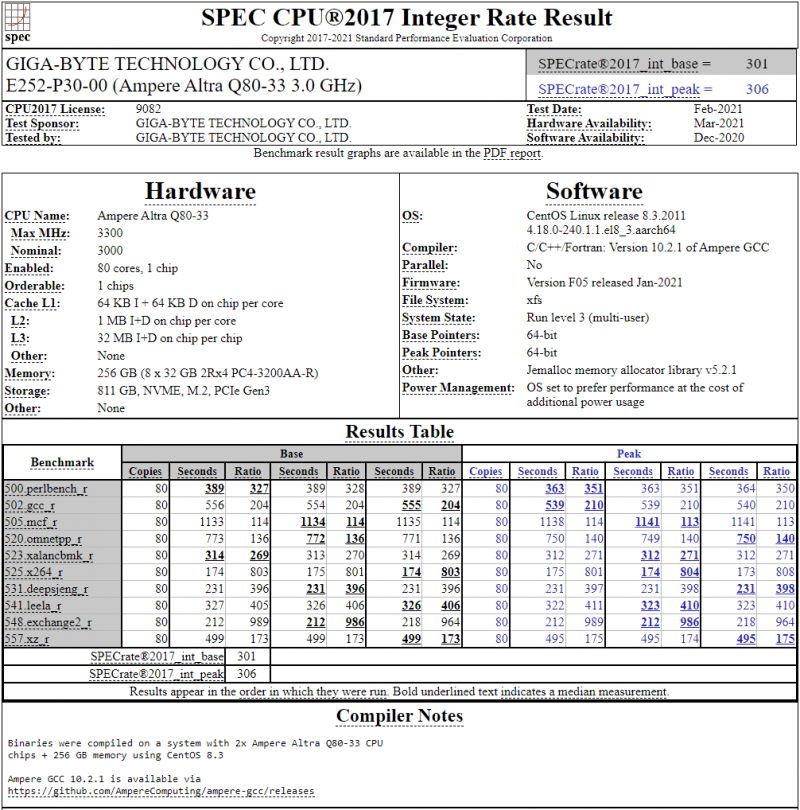

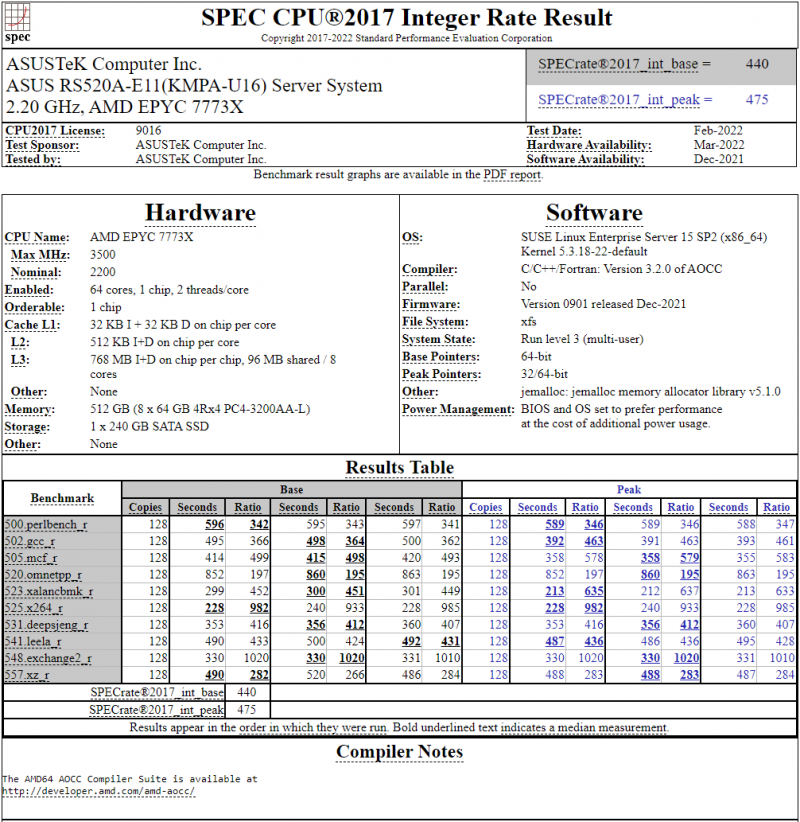

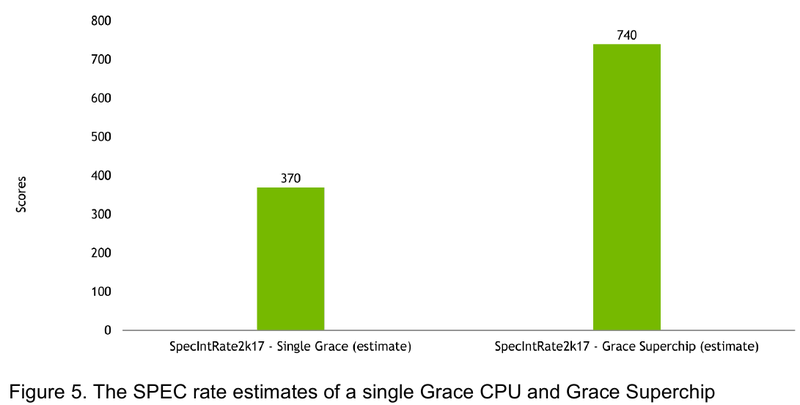

Источник: NVIDIA Производительность Grace также обещает быть рекордно высокой благодаря оптимизированной архитектуре и быстрому интерконнекту. Даже по предварительным цифрам, опубликованным NVIDIA, речь идёт о 370 очках SPECrate2017_int_base для одного кристалла Grace и 740 очках для 144-ядерной сборки из двух кристаллов — и это с использованием обычного компилятора GCC без тонких платформенных оптимизаций. Последняя цифра существенно выше результатов, показанных 128-ядерными Alibaba T-Head Yitian 710, также использующим архитектуру Arm v9, и 64-ядерными AMD EPYC 7773X.

13.07.2022 [16:13], Алексей Степин

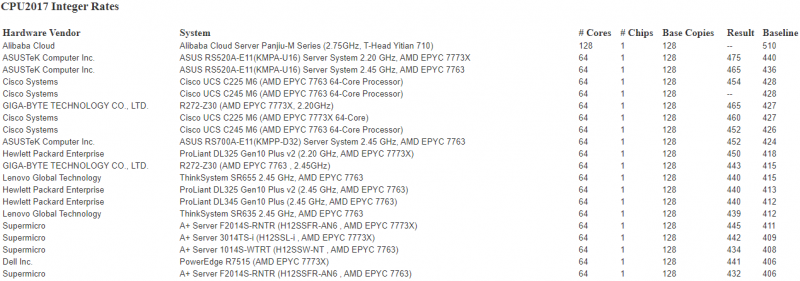

128-ядерный Arm-процессор Alibaba T-Head Yitian 710 показал отличные результаты в SPEC CPU2017Не секрет, что китайские гиганты, такие, как Huawei и Alibaba Cloud, разрабатывают собственные серверные процессоры на базе архитектуры Arm. Однако информации об этих чипах, как правило, не очень много и пользоваться общепринятыми на западе тестами и рейтингами разработчики не спешат, что, к слову, характерно и для китайских суперкомпьютеров. Alibaba Cloud представила чип Yitian 710 ещё осенью прошлого года. Этот процессор построен на базе архитектуры Armv9 и максимально может иметь 128 ядер с частотой до 3,2 ГГц. Однако результаты проверки чипа в популярном тесте SPEC CPU2017 были опубликованы только сейчас. Процессор тестировался в составе референс-сервера Panjiu. Применялась 128-ядерная версия с частотой 2,75 ГГц, 1 Мбайт кеша L2 на ядро и 64 Мбайт кеша L3 на кристалл (128 Мбайт на сборку). Последнее позволяет говорить о том, что Alibaba также использует в своих процессорах чиплетную компоновку. Результаты оказались существенно более высокими, нежели у Ampere Altra Q80-33; правда, стоит сделать скидку на то, что у Ampere использовалась 80-ядерная версия, а не более новая 128-ядерая Altra Max. Но в аутсайдерах оказался также и AMD EPYC 7773X (64 ядер/128 потоков, 2,2-3,5 ГГц, 768 Мбайт L3), показавший 440 очков против 510 у Yitian 710. Увеличенный объём кеша не слишком помог детищу «красных». Таким образом, процессор на базе архитектуры Armv9 занял первое место там, где традиционно господствовали решения с архитектурой x86 — достаточно взглянуть на Топ-20 в рейтинге CPU2017 Integer. Можно сказать, что 128-ядерный процессор не вполне корректно сравнивать с 64-ядерным с поддержкой SMT, однако если технологии и архитектура позволяют разместить вдвое больше полноценных ядер в сопоставимом по размеру с AMD EPYC корпусе, так ли это важно? К сожалению, пока речь идёт только о целочисленных вычислениях. По неизвестной причине, Alibaba Cloud не опубликовала результаты CPU2017 Floating Point, где сравнение вышло бы существенно интереснее. В любом случае, монополия AMD на первые места пошатнулась; что же касается Intel, то в классе однопроцессорных систем самым мощным вариантом является 36-ядерный Xeon Platinum 8351N, который заведомо проиграет 64-128 ядерным монстрам AMD, Ampere, а теперь уже и Alibaba Cloud.

20.06.2022 [23:39], Игорь Осколков

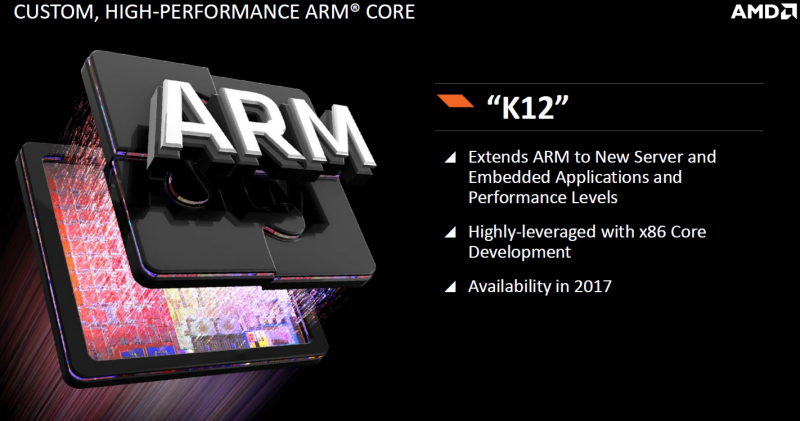

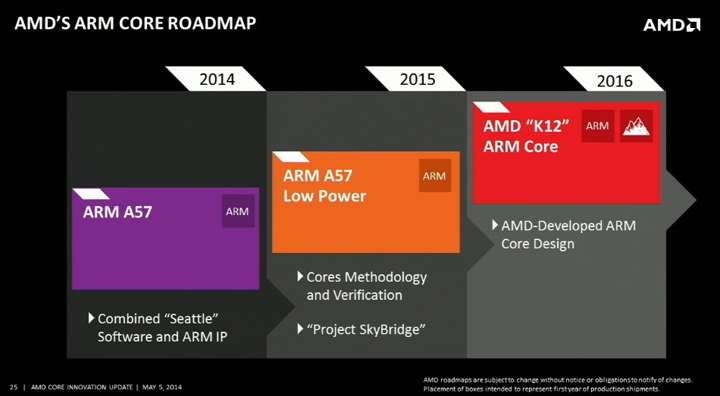

Джим Келлер назвал глупостью отказ AMD от развития серверных Arm-процессоровМы уже рассказывали краткую историю развития серверных Arm-процессоров в обзоре Ampere Altra. Среди неудачных проектов был и AMD Opteron A1100 (Seattle), выход которого задержался на два года. Но вместе с анонсом этого CPU компания AMD озвучила планы по дальнейшему развитию Arm-решений, которые включали Project SkyBridge (ARM Cortex-A57) и K12 (кастомная реализация ARMv8-A). Над последним параллельно с разработкой x86-ядер Zen трудился Джим Келлер (Jim Keller).

Изображения: AMD В своём майском докладе на конференции Future of Compute Келлер сообщил, что во время планирования Zen 3 он и другие инженеры обратили внимание на значительное сходство в реализации архитектур x86 и Arm, поскольку «внутри все современные компьютеры на самом деле являются RISC-машинами». По словам Келлера, отличия по большому счёту кроятся в декодерах инструкций, так что он с командой постарался сделать решение, которое могло бы работать с обоими архитектурами. «Они [AMD] по глупости отменили этот проект» — приводит слова Келлера The Register. Сам Келлер в своё время назвал работу над Zen более приоритетной, но после его ухода из AMD в 2016 году компания полностью забросила K12. K12 должен был стать процессором, ориентированным на энергоэффективность и способным работать на высоких частотах. Он был предназначен для высокоплотных систем, а также для встраиваемых решений и заказных чипов. В конце концов, AMD добьётся этого с помощью, например, Zen 4c (EPYC Bergamo), но к этому моменту появится очередное поколение Arm-чипов Ampere Computuing, CPU которой уже доступны в облаках Oracle, Microsoft и других крупных игроков. А Amazon с Alibaba и вовсе пошли по пути создания собственных Arm-процессоров. Впрочем, и без подобных чипов сейчас дела на серверном рынке у AMD идут прекрасно.

24.05.2022 [07:00], Игорь Осколков

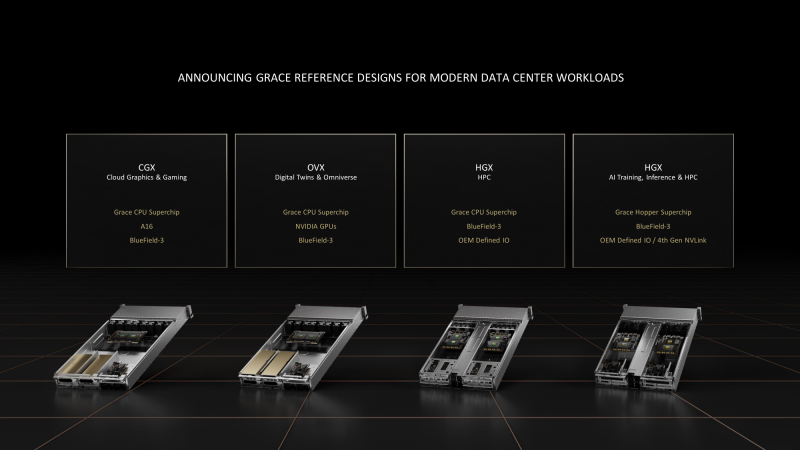

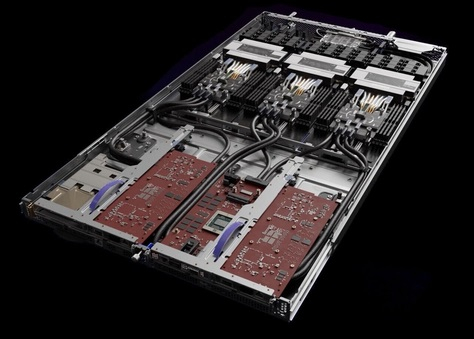

NVIDIA представила референсные платформы CGX, OVX и HGX на базе собственных Arm-процессоров GraceНа весенней конференции GTC 2022 NVIDIA поделилась подробностями о грядущих серверных Arm-процессорах Grace Superchip и гибридах Grace Hopper Superchip, а на Computex 2022 представила первые референсные платформы на базе этих чипов для OEM-производителей и объявила о расширении программы NVIDIA Certified. Последнее, впрочем, не означает отказ от x86-систем, поскольку программа будет просто расширена. Да и портирование стороннего и собственного ПО займёт некоторое время. Первые несколько десятков моделей серверов от ASUS, Foxconn, GIGABYTE, QCT, Supermicro и Wiwynn появятся в первой половине 2023 года. Представлены они будут в трёх категориях, причём все, за исключением одной, базируются на «сдвоенных» процессорах Grace Superchip, насчитывающих до 144 ядер. Системы серии OVX, представленной ранее, всё так же будут предназначены для цифровых двойников и Omniverse — NVIDIA продолжает наставить на том, что любое современное производство или промышленное предприятие должно быть интеллектуальным. Arm-версия OVA получит неназванные ускорители NVIDIA и DPU Bluefield-3. Новая платформа NVIDIA CGX очень похожа на OVX — она тоже получит DPU Bluefield-3 и до четырёх ускорителей NVIDIA A16. CGX создана специального для облачных гейминга и работы с графикой. А вот новое поколение платформы NVIDIA HGX гораздо интереснее. Оно заметно отличается от предыдущих, которые в основном представляли собой различные комбинации базовых плат NVIDIA с четырьмя или восемью ускорителями, вокруг которых OEM-партнёры строили системы в меру своих умений и фантазий. Нынешняя инкарнация NVIDIA HGX всё же несколько более комплексная, поскольку сейчас предлагается два варианта узлов, специально спроектированных для высокоплотных систем и явно ориентированных на высокопроизводительные вычисления (HPC). Первый вариант — это 1U-лезвие (до 84 шт. в стандартной стойке), которое включает один процессор Grace Superchip, до 1 Тбайт LPDDR5x-памяти с пропускной способностью (ПСП) до 1 Тбайт/с и DPU BlueField-3. Иные варианты сетевого подключения оставлены на усмотрение конечного производителя. Заявленный уровень TDP составляет 500 Вт, так что на выбор доступны системы с воздушным и жидкостным охлаждением. Второй вариант базируется на гибридных чипах Grace Hopper Superchip, объединяющих в себе посредством шины NVLink-C2C процессорную часть с 512 Гбайт LPDDR5x-памяти и ускоритель NVIDIA H100 c 80 Гбайт HBM3-памяти (ПСП до 3,5 Тбайт/с). Помимо DPU BlueField-3 опционально доступен и интерконнект NVLink 4.0, но и здесь вендору оставлена свобода выбора. Уровень TDP для данной платформы составляет 1 кВт, но вот обойтись одним только воздушным охлаждением (а такой вариант есть) при полном заполнении стойки всеми 42-мя 2U-лезвиями будет трудно.

22.03.2022 [18:48], Игорь Осколков

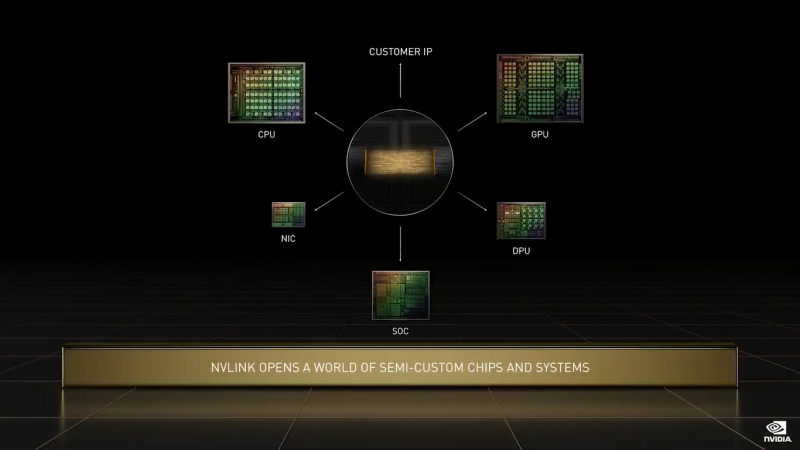

NVIDIA анонсировала 144-ядерные Arm-процессоры Grace и гибрид Grace HopperГлавным событием GTC 2022 стал анонс новых ускорителей H100 (Hopper), которые станут доступны в III квартале 2022 года. Вслед за ними в первой половине 2023 года появятся давно обещанные CPU Grace и гибридная система Grace Hopper, сочетающие, как понятно из названия, процессоры Grace (ARMv9) и ускорители Hopper. Как и было сказано ранее, для связи всех компонентов между собой будет использоваться mesh-сеть на базе всё той же шины NVLink 4.0 (900 Гбайт/с) с кеш-когерентностью. А сочетание LPDDR5X (с ECC, конечно) и HBM даст суммарный объём памяти до 600 Гбайт с общей полосой пропускания порядка 2 Тбайт/с. Для Grace Hopper компания подготовит полный стек ПО, благо портированием на Arm она начала заниматься ещё 3 года назад. Двухчиповый процессор Grace Superchip для ИИ- и HPC-нагрузок имеет 144 ядра, результат которых в SPECrate2017_int_base составляет 740, что, по словам компании, в полтора раза выше, чему у пары AMD EPYC, использующихся в DGX A100. И это, честно говоря, не такой уж и впечатляющий результат. Но NVIDIA утверждает, что новые CPU вдвое лучше по отношению производительности к энергопотреблению, чем «традиционные серверы» — использование LPDDR5X позволяет добиться пропускной способности памяти в 1 Тбайт/с, а вся сборка CPU+RAM будет потреблять менее 500 Вт. Чипы (или чиплеты, если хотите) в Grace Superchip тоже объединены посредством NVLink, только в данном случае этот интерконнект называется NVLink-C2C (Chip-to-Chip). И его NVIDIA предлагает использовать другим компаниям для создания кастомных сборок, объединяющих необходимые кристаллы, да и сама готова масштабировать и адаптировать свои решения под нужды заказчика. По словам NVIDIA, NVLink-C2C в 25 раз энергоэффективнее PCIe 5.0, а для его реализации нужна в 90 раз меньшая площадь кремния. Шина предлагает высокую скорость (да-да, всё те же 900 Гбайт/с), низкий уровень задержек, поддержку атомарных операций и совместимость с Arm AMBA CHI, CXL и UCIe.

24.01.2022 [20:09], Алексей Степин

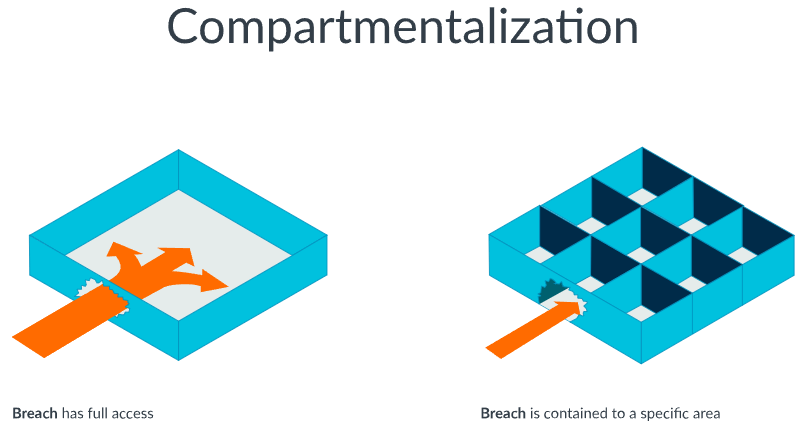

Arm выпустила прототип платы с процессором повышенной безопасности MorelloВ современном мире процессоров уже никого не удивляет нахождение очередной уязвимости, а иногда тропинкой для злоумышленника становятся технологии, изначально призванные повысить уровень безопасности. Ряд исследователей небезосновательно считает, что «заплатками» отделаться не получится и надо менять глубинные принципы, лежащие в основе процессорных архитектур. Один из таких проектов, развиваемый с 2010 года усилиями SRI International и Кембриджского университета — это CHERI. В 2019 к нему присоединилась Arm, недавно представившая первый прототип платы с процессором Morello, который базируется на двух ключевых принципах, заложенных в CHERI — масштабируемая компартментализация и тонко настраиваемая защита содержимого памяти. Оба принципа реализованы аппаратно и сами по себе не новы.

Изображения: Arm По сути речь идёт о расширении стандартного набора инструкций, с помощью которого даже написанное с использованием языков, позволяющих относительно легко сделать ошибки при работе с памятью (а это обычно C/C++), ПО можно заставить работать без образования серьёзных дыр в защите. Тщательная компартментализация (т.е. разделение) кода ОС и приложений хотя и не исключает наличие уязвимостей, но серьёзно ограничивает область возможного нанесения вреда.  В частности, любая инструкция типа load/store и любая операция выборки должны быть авторизованы на аппаратном уровне со стороны процессора. Разумеется, это не высокоуровневая защита, а скорее набор базовых блоков для построения таковой. Принцип компартментализации ещё проще: если в классической архитектуре взломщик может получить контроль над всей системой, то в изолированных друг от друга ОС и приложениях, он лишь проникнет в одну из множества небольших «ячекк», а его действия послужат сигналом для защитных механизмов.

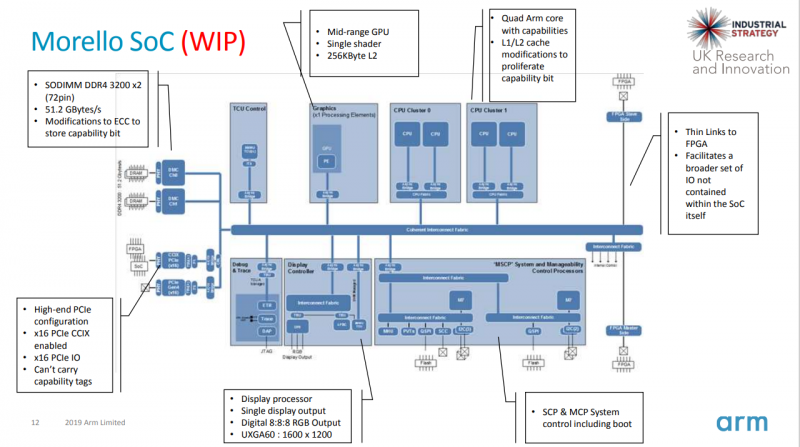

Блок-схема Arm Morello Arm Morello — первый чип на базе CHERI. Текущая аппаратная реализация использует модифицированные ядра Neoverse N1 (ARMv8.2) с частотой 2,5 ГГц. Первые платы с новым процессором предназначены таким IT-гигантам как Google и Microsoft, а также заинтересованным партнёрам образовательным учреждениям. На текущий момент разработчики предлагают модифицированное ядро FreeBSD, часть стандартных UNIX-программ, а также некоторые другие приложения. С появлением готовых плат и процессоров процесс адаптации ПО должен значительно ускориться.

17.12.2021 [01:35], Алексей Степин

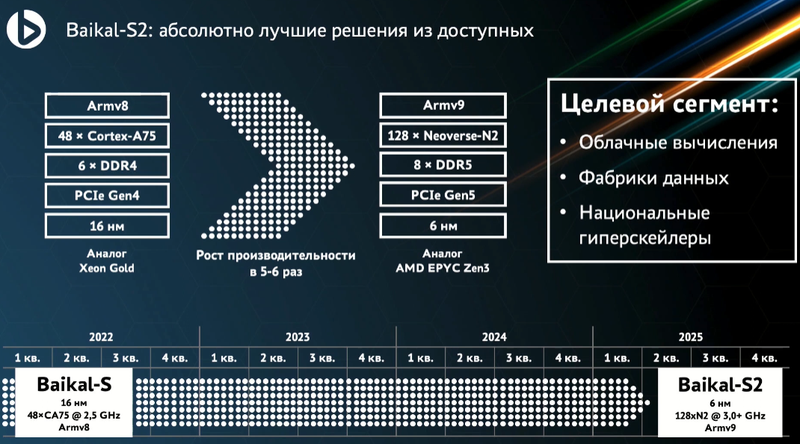

Российский серверный процессор Baikal-S2 получит чиплетную компоновку, 128 ядер Armv9 с частотой 3 ГГц, 8 каналов DDR5, 192 линии PCIe 5.0 и CXL 2.0На ежегодной итоговой конференции Байкал Электроникс состоялся анонс 128-ядерных серверных Arm-процессоров второго поколения Baikal-S2, были показаны результаты тестов 48-ядерных Baikal-S, анонсированы первые же российские серверы и СХД на их основе, а также было объявлено о заключении стратегических сделок и планах на будущее. Если говорить о сделках, то можно смело сказать, что рамками только Arm Байкал себя уже не ограничивает: получение доли в CloudBEAR означает и получение основы для разработки собственных чипов с архитектурой RISC-V, и первым же проектом станет создание сертифицированной системы доверенной загрузки для процессоров Baikal-L и Baikal-S2. Но среди равноправных партнёров значатся не только российские разработчики — заключена сделка с Esperanto Technologies.

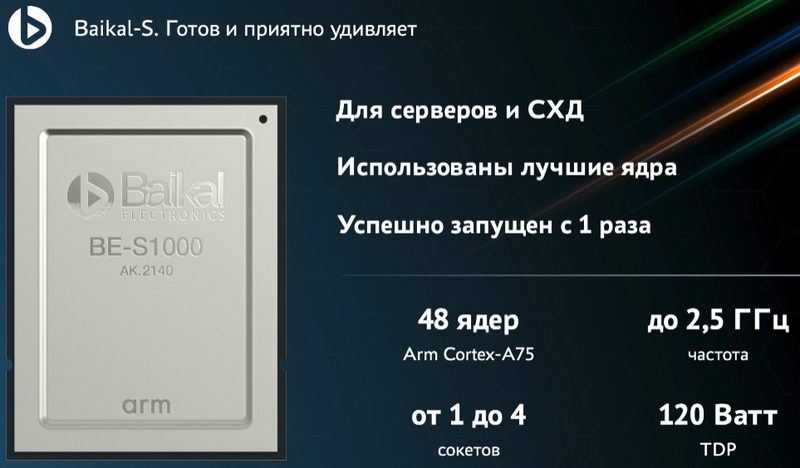

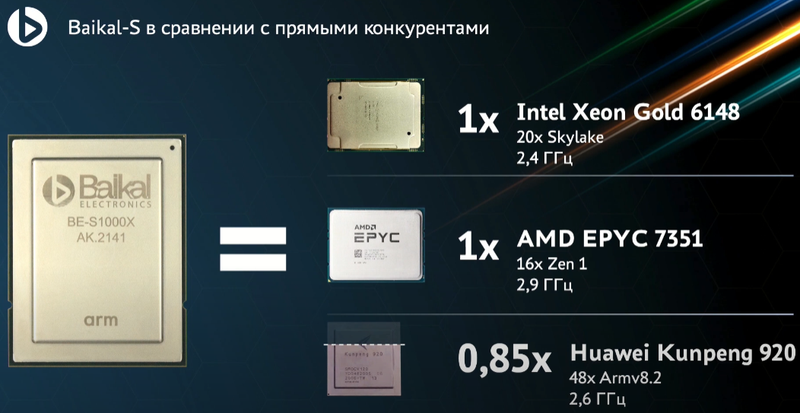

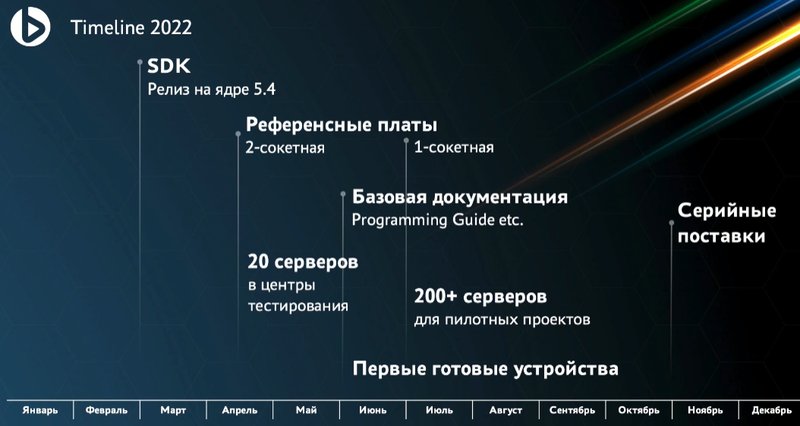

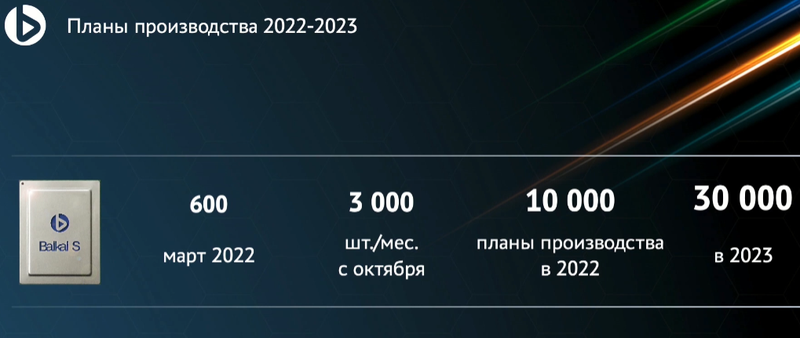

Тестовая плата с процессором Baikal-S (Изображения: Байкал Электроникс) Данная сделка позволит получить доступ к весьма серьёзным разработкам: напомним, Esperanto создала ET-SoC-1, мощнейший ИИ-ускоритель с более чем тысячью ядер RISC-V в составе. Связка из четырёх таких чипов развивает более 800 Топс в задачах инференса, потребляя всего 120 Вт. Надо ли говорить, насколько это важно в эпоху нейросетей, машинного обучения и разнообразных сопроцессоров-ускорителей.  Несмотря на то, что Baikal-S «старичком» назвать никак нельзя, компания анонсировала уже второе поколение чипов — Baikal-S2 базируется на новейшей архитектуре Neoverse-N2 (ARMv9). Процессор будет выполнен по 6-нм техпроцессу с использованием чиплетной компоновки и получит 128 ядер с частотой порядка 3 ГГц, 8 каналов DDR5 (возможно, будет и больше), 192 линии PCIe 5.0, поддержку CXL 2.0 и CCIX 2.0. Ожидается, что он станет аналогом AMD EPYC Milan. Разработку планируется закончить к 2025 году.  Что касается текущего поколения Baikal-S, то осенью этого года была получена первая партия чипов, а также было анонсировано несколько решений на его основе. Как теперь отрапортовали разработчики, первые чипы оказались очень удачными во всех отношениях, так что больших препятствий на пути их внедрения быть не должно. На конференции были представлены одно- и двухсокетные серверы и СХД от российских компаний 3Logic, Aquarius, ICL, iRU, Норси-Транс. Впоследствии появятся и четырёхпроцессорные системы.  Напомним, что Baikal-S содержит в своём составе 48 ядер Arm Cortex-A75 с частотой до 2,5 ГГц и имеет TDP 120 Вт. Шестиканальный контроллер памяти поддерживает до 768 Гбайт DDR4-3200. Современно выглядит и поддержка PCI Express 4.0 (80 линий), и наличие выделенного управляющего ядра для организации доверенных вычислений, и аппаратная виртуализация.  В синтетических тестах новинка показала результаты, сравнимые с Intel Xeon Gold 6148 или AMD EPYC 7351, а своему китайскому «коллеге» в лице HiSilicon Kunpeng 920 процессор уступил лишь в некоторых тестах. Разработчики уверены, что процессор получился универсальным и его можно использовать практически везде: в серверах любых профилей, СХД, суперкомпьютерах, устройствах сетевой безопасности и даже в базовых станциях 5G. Результаты тестов также доступны и на сайте Geekbench.  Ожидается, что SDK для новой платформы будет доступен уже в конце февраля следующего года. Весной появятся двухпроцессорные платы и первые 20 серверов попадут в центры тестирования, а к середине лета 200 с лишним серверов примут своё участие в пилотных проектах. Старт серийного производства CPU намечен на октябрь-ноябрь 2022 года — речь идёт примерно о 10 тыс. процессоров. В 2023 году этот объём будет утроен и при необходимости увеличен.  Таким образом, Байкал Электроникс доказала, что может создавать достойные серверные решения, не уступающие зарубежным, причём, как на базе x86-64, так и на базе Arm. Уже сейчас процессоры Baikal-S могут стать основой для производительных серверов российской разработки, а сделка с Esperanto сделает российские HPC-системы и комплексы машинного обучения по-настоящему мощными.

04.12.2021 [03:42], Игорь Осколков

Процессор Amazon Graviton3: 64 ядра Arm, 5-нм техпроцесс, чиплетная компоновка и DDR5 с PCIe 5.0Анонсированный на днях Arm-процессор Graviton3, создававшийся специально для нужд Amazon и AWS, неожиданно оказался по ряду параметров на голову выше ещё даже не вышедших EPYC и Xeon следующего поколения. И это не самый хороший сигнал для AMD, Intel, Qualcomm и прочих производителей.

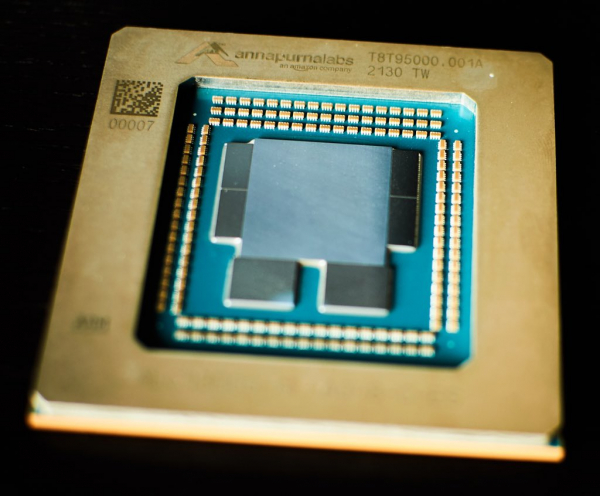

Amazon Graviton3. Фото: Ian Colle Graviton3 — первый массовый (самой Amazon и рядом избранных клиентов он используется уже не один месяц) серверный процессор с поддержкой DDR5 и PCIe 5.0. CPU выполнен по 5-нм техпроцессу TSMC и содержит примерно 55 млрд транзисторов. Для удешевления он использует BGA-корпусировку и чиплетную компоновку из семи отдельных кристаллов — два PCIe-контроллера и четыре двухканальных контроллера DDR5 вынесены за пределы собственно CPU.

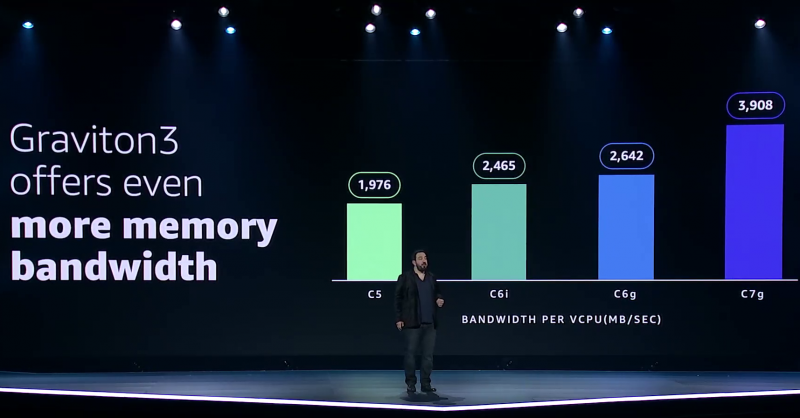

Узел EC2 C7g. Здесь и ниже изображения Amazon AWS Более того, их упаковка использует передовые решения с каналами длиной менее 55 мкм, что вдвое меньше, чем у других серверных CPU. Уменьшение длины проводников положительно сказывается на энергоэффективности, которая очень важна для любого гиперскейлера. Этим же объясняется и относительно небольшое по современным меркам число ядер (всего 64) и их частота (2,6 ГГц). Всё это позволило добиться энергопотребления примерно в 100 Вт.  Есть и ещё один важный плюс в сохранении числа ядер — переход на DDR5-4800 позволил не только достичь пиковой суммарной пропускной способности памяти в 300 Гбайт/с на чип, но и повысить реальную скорость работы с памятью каждого vCPU (фактически ядра) в полтора раза по сравнению с прошлым поколением. Та же ситуация и с PCIe 5.0 — для достижения той же пропускной способности, что ранее, нужно вдвое меньше линий.  Для удешевления используются готовые IP-блоки сторонних компаний и, судя по всему, ядра тоже несильно отличаются от референсов Arm. А вот какие именно, узнаем не сразу, поскольку Amazon явно не указала, будут ли это Neoverse V1 (Zeus) или N2 (Perseus). Вероятно, это всё же V1 (ARMv8.5-A), поскольку по описанию Graviton3 похожи именно на эту архитектуру. Новые ядра стали значительно «шире» прежних — они забирают 8 инструкций, декодируют от 5 до 8 из них и отправляют на исполнение сразу 15 инструкций. Соответственно и число исполнительных блоков по сравнению с Neoverse-N1 (Graviton2) практически удвоилось.  Кроме того, они обзавелись поддержкой 256-бит векторных инструкций SVE, что повысило не только скорость выполнения «классических» FP-операций (например, для задач медиакодирования и шифрования), но и благодаря поддержке bfloat16 позволило утверждать Amazon, что новые чипы годятся и для инференса. Среди упомянутых ранее мер защиты есть, например, принудительное шифрование оперативной памяти, изолированные кеши для каждого vCPU (ядра), аппаратная защита стека.

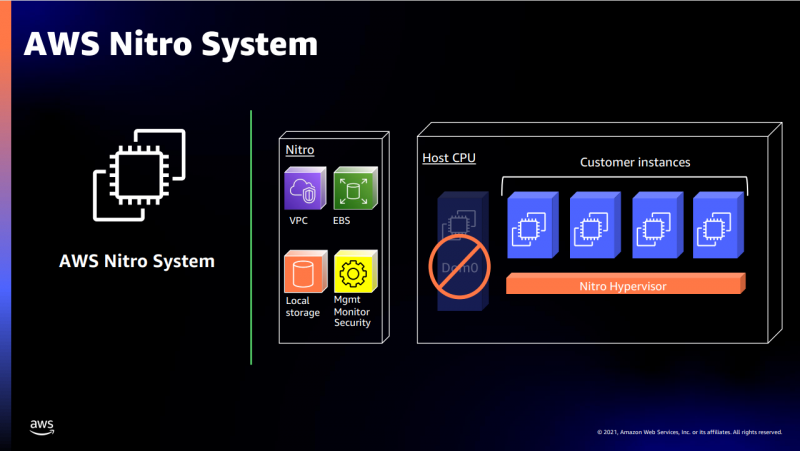

В подписи второго столбца явная опечатка В целом, средний прирост производительности Graviton3 по сравнению с Graviton2 составил 25 %, но в некоторых задачах он достигает 60 %. И всё это при сохранении того же уровня энергопотребления и тепловыделения. Всё это позволило уместить в одном 1U-узле с воздушным охлаждением сразу три процессора Graviton3. И они разительно отличаются от грядущих 128-ядерных процессоров Altra Max и EPYC Bergamo, которые Ampere и AMD позиционируют как решения для гиперскейлеров. Зато в чём-то похожи на Yitian 710 от Alibaba Cloud.  Но CPU — это лишь часть платформы, фундамент для которой несколько лет назад заложило появление чипов Nitro. Их сейчас стоило бы назвать DPU/IPU, хотя на момент их появления такого понятия, можно сказать, и не было. Nitro берёт на себя все задачи по обслуживанию гипервизора, обеспечению безопасности, работе с хранилищем и сетью и т.д., высвобождая, с одной стороны, все ресурсы CPU, памяти и SSD для обработки задачи клиента, а с другой — позволяя практически полностью дезагрегировать всю инфраструктуру.

Узел с Nitro SSD Впрочем, Amazon пошла ещё дальше — теперь она самостоятельно закупает NAND-чипы и производит SSD, тоже под управлением Nitro. То есть у компании под контролем практически полный стек современных аппаратных решений: CPU, DPU, SSD, ИИ-ускорители для обучения (Trainium) и инференса (Inferentia). Она активно переносит на него собственные сервисы и предлагает их клиентам. И именно это и должно обеспокоить крупных вендоров, поскольку их решения вряд ли позволят добиться такого же уровня TCO, а гиперскейлеров, желающих перейти на аналогичную модель, немало. UPD 06.12.21: презентация новых процессоров стала доступна публично, поэтому в материал добавлены некоторые иллюстрации, а в галерее ниже приведены результаты тестов производительности.

|

|