Материалы по тегу: инференс

|

16.05.2024 [01:05], Игорь Осколков

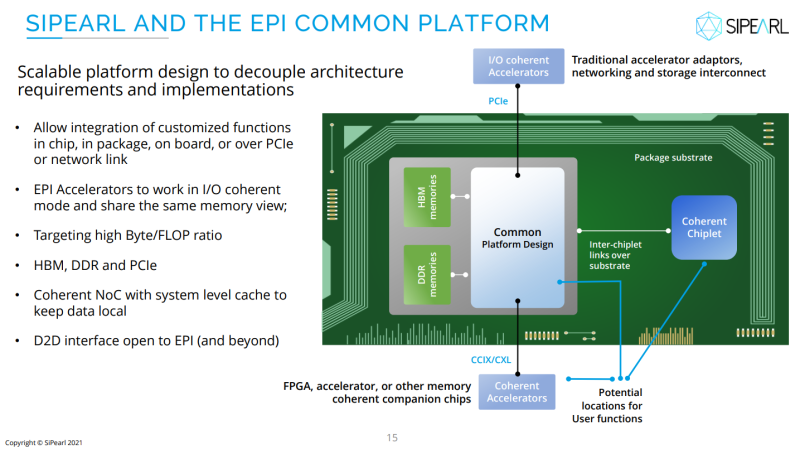

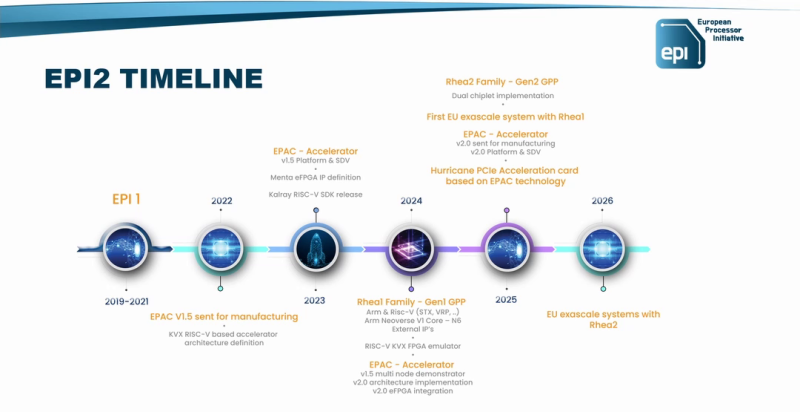

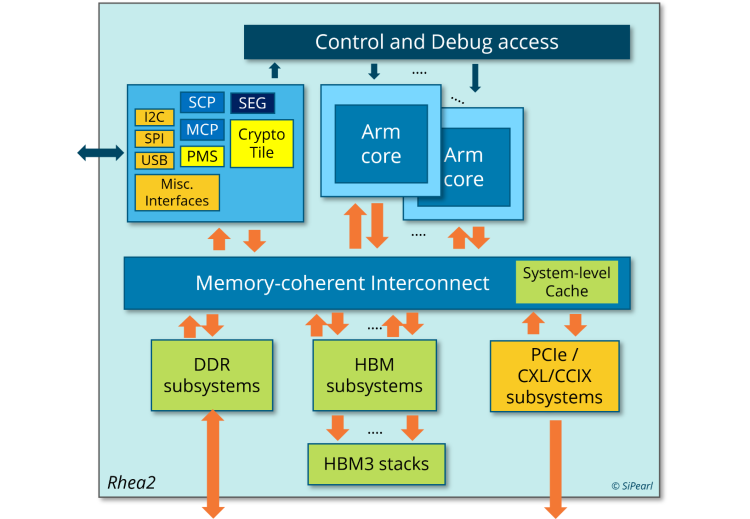

И для ИИ, и для HPC: первые европейские серверные Arm-процессоры SiPearl Rhea1 получат HBM-памятьКомпания SiPearl уточнила спецификации разрабатываемых ею серверных Arm-процессоров Rhea1, которые будут использоваться, в частности, в составе первого европейского экзафлопсного суперкомпьютера JUPITER, хотя основными чипами в этой системе будут всё же гибридные ускорители NVIDIA GH200. Заодно SiPearl снова сдвинула сроки выхода Rhea1 — изначально первые образцы планировалось представить ещё в 2022 году, а теперь компания говорит уже о 2025-м. При этом существенно дизайн процессоров не поменялся. Они получат 80 ядер Arm Neoverse V1 (Zeus), представленных ещё весной 2020 года. Каждому ядру полагается два SIMD-блока SVE-256, которые поддерживают, в частности, работу с BF16. Объём LLC составляет 160 Мбайт. В качестве внутренней шины используется Neoverse CMN-700. Для связи с внешним миром имеются 104 линии PCIe 5.0: шесть x16 + две x4. О поддержке многочиповых конфигураций прямо ничего не говорится. Очень похоже на то, что SiPearl от референсов Arm особо и не отдалялась, поскольку Rhea1 хоть и получит четыре стека памяти HBM, но это будет HBM2e от Samsung. При этом для DDR5 отведено всего четыре канала с поддержкой 2DPC, а сам процессор ожидаемо может быть поделён на четыре NUMA-домена. И в такой конфигурации к общей эффективности работы с памятью могут быть вопросы. Именно наличие HBM позволяет говорить SiPearl о возможности обслуживать и HPC-, и ИИ-нагрузки (инференс). На примере Intel Xeon Max (Sapphire Rapids c 64 Гбайт HBM2e) видно, что наличие сверхбыстрой памяти на борту даёт прирост производительности в означенных задачах, хотя и не всегда. Однако это другая архитектура, другой набор инструкций (AMX), другая же подсистема памяти и вообще пока что единичный случай. С Fujitsu A64FX сравнения тоже не выйдет — это кастомный, дорогой и сложный процессор, который, впрочем, доказал эффективность и в HPC-, и даже в ИИ-нагрузках (с оговорками). В MONAKA, следующем поколении процессоров, Fujitsu вернётся к более традиционному дизайну. Пожалуй, единственный похожий на Rhea1 чип — это индийский 5-нм C-DAC AUM, который тоже базируется на Neoverse V1, но предлагает уже 96 ядер (48+48, два чиплета), восемь каналов DDR5 и до 96 Гбайт HBM3 в четырёх стеках, а также поддержку двухсокетных конфигураций. AWS Graviton3E, который тоже ориентирован на HPC/ИИ-нагрузки, вообще обходится 64 ядрами Zeus и восемью каналами DDR5. Наконец, NVIDIA Grace и Grace Hopper в процессорной части тоже как-то обходятся интегрированной LPDRR5x, да и ядра у них уже Neoverse V2 (Demeter), и своя шина для масштабирования имеется. В любом случае в 2025 году Rhea1 будет выглядеть несколько устаревшим чипом. Но в этом же году SiPearl собирается представить более современные чипы Rhea2 и обещает, что их разработка будет не столь долгой как Rhea1. Компанию им должны составить европейские ускорители EPAC, тоже подзадержавшиеся. А пока Европа будет обходиться преимущественно американскими HPC-технологиями, от которых стремится рано или поздно избавиться.

07.05.2024 [21:26], Руслан Авдеев

Apple работает над собственными серверными ИИ-ускорителямиКомпания Apple занимается разработкой собственных ИИ-полупроводников для дата-центров, передаёт The Wall Street Journal. В перспективе это поможет ей в «гонке вооружений», развернувшейся на рынке ИИ-решений. И у Apple есть ресурсы для создания передовых ИИ-чипов. В последние десять лет компания уже выбилась в лидеры полупроводниковой индустрии, представляя всё новые чипсеты для мобильных устройств и компьютеров Mac-серии. Как свидетельствуют источники СМИ, серверный проект Project ACDC (Apple Chips in Data Center) задействует компетенции компании в деле создания решений для ЦОД. Недавно сообщалось, что Apple наняла создателя ИИ-кластеров Google. Реализацию проекта Apple начала несколько лет назад, но данных о том, когда будут готовые первые чипы, пока нет. По имеющимся данным, компания уже тесно сотрудничает с TSMC. Предполагается, что чипы для серверов Apple будут оптимизированы для запуска ИИ-моделей, а не их обучения — на этом рынке по-прежнему будет доминировать NVIDIA. Время поджимает, поскольку Google и Microsoft уже имеют собственные ИИ-ускорители, хотя и разных классов — TPU и Maia 100. Обе компании имеют компетенции в области LLM, а Microsoft весьма дружна с OpenAI, которая тоже не прочь заняться «железом». Такое положение дел не устраивает инвесторов Apple, поскольку компания не продемонстрировала никаких впечатляющих успехов в соответствующей сфере, в то время как цена акций конкурентов продолжает расти на фоне новостей об их достижениях. В Apple пытаются убедить инвесторов, что это лишь временное явление и скоро грядут анонсы, связанные с ИИ. Опыт Apple в сфере разработки современных полупроводников должен помочь в создании ИИ-чипов. Сегодня компания представила 3-нм процессор M4 с самым мощным, по её словам, NPU в мире. Хотя компания добилась определённых успехов в разработке чипов для потребительской и профессиональной электроники, определённые задачи даются ей с трудом. Например, она всё ещё бьётся над созданием собственного беспроводного модуля. Хотя в Apple предпочли бы, чтобы большинство ИИ-вычислений осуществлялись силами самих чипов, некоторые задачи будут по-прежнему выполняться в облаке, где и пригодятся новые полупроводники. Это позволит компании лучше контролировать свою стратегию развития в сфере ИИ.

30.04.2024 [12:39], Сергей Карасёв

Утилита llamafile для быстрого запуска ИИ-моделей получила расширенную поддержку ускорителей AMD и свежих LLMКомпания Mozilla анонсировала обновлённую версию инструмента llamafile с индексом 0.8.1. В данном релизе устранены ошибки, из-за которых происходило некорректное распознавание ускорителей AMD на базе GPU. Кроме того, реализованы некоторые другие изменения. Напомним, llamafile даёт возможность упаковать веса большой языковой модели (LLM) в исполняемый файл, который без установки можно запустить практически на любой современной платформе. Поддерживаются архитектуры x86-64 и ARM64, а также системы macOS, Windows, Linux, FreeBSD, OpenBSD и NetBSD. Как отмечается, изначально в llamafile корректно определялись только числовые идентификаторы графических блоков AMD GFX, из-за чего возникали сбои при использовании определённого оборудования AMD Instinct/Radeon. Например, ускоритель Instinct MI250 имеет обозначение GFX90A IP, и символ «A» ранее не распознавался должным образом. В результате, при работе с такими GPU происходили ошибки. Теперь данная проблема устранена.

Источник изображения: AMD Кроме того, в llamafile 0.8.1 имеется поддержка модели Phi-3 Mini 4k, а также LLaMA3, Grok, Mixtral 8x22b и Command-R. Производительность F16 повышена приблизительно на 20 % на платформе Raspberry Pi 5, примерно на 30 % — на Intel Skylake и на 60 % — на Apple M2.

30.04.2024 [11:24], Сергей Карасёв

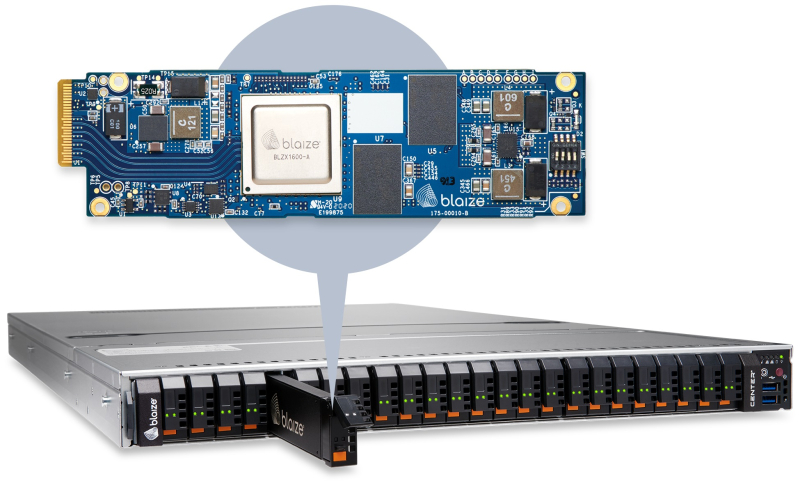

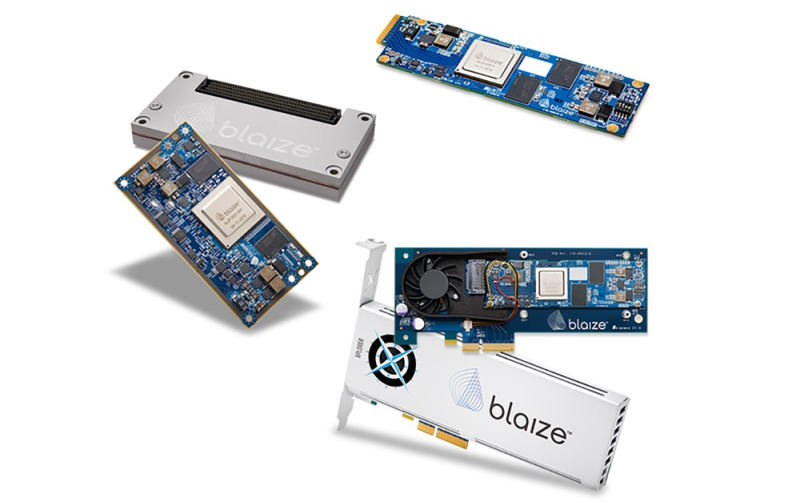

Разработчик ИИ-чипов для ЦОД и периферийных систем Blaize получил на развитие $106 млнСтартап в области ИИ Blaize объявил о проведении раунда финансирования, в ходе которого привлечено $106 млн. Деньги предоставили существующие и новые инвесторы, включая Bess Ventures, Franklin Templeton, DENSO, Mercedes Benz, Temasek, Rizvi Traverse, Ava Investors и BurTech LP LLC. Blaize разрабатывает специализированные чипы, предназначенные для ускорения выполнения ИИ-задач в дата-центрах и на периферии. Утверждается, что по сравнению с традиционными ускорителями на базе GPU и FPGA устройства Blaize обеспечивают более высокую энергетическую эффективность. В основе архитектуры решений Blaize лежит обработка графов, а многие модели ИИ можно как раз представить представить в виде графов. Платформа Blaize включает специализированное ПО Blaize AI Studio и Blaize Picasso SDK, предоставляющее клиентам удобные средства для быстрого создания и развёртывания ИИ-приложений. В ассортименте Blaize присутствуют различные ИИ-устройства на основе чипа Blaize 1600 SoC, содержащего 16 ядер GSP (Graph Streaming Processor). Заявленная ИИ-производительность достигает 16 TOPS. В частности, доступны модуль Blaize Xplorer X600M M.2 (PCIe 3.0 х4; 2 Гбайт LPDDR4), ускоритель Blaize Xplorer X1600E EDSFF (PCIe 3.0 х4; 4 Гбайт LPDDR4), карта расширения Blaize Xplorer X1600P PCIe (PCIe 3.0 х4; 4 Гбайт LPDDR4), ускоритель Xplorer X1600P-Q PCIe на базе четырёх чипов Blaize 1600 SoC (PCIe 3.0 х16; 16 Гбайт LPDDR4), встраиваемое решение Blaize Pathfinder P1600 Embedded System on Module, а также сервер Blaize Inference Server на базе 24 ускорителей Blaize Xplorer X1600E EDSFF. Привлечённые средства Blaize будет использовать для дальнейшей разработки и коммерциализации продуктов. В декабре 2023-го стартап сообщил о намерении выйти на биржу посредством SPAC-сделки с BurTech Acquisition Corp. Ожидается, что это позволит получить $71 млн при оценке компании в $894 млн.

15.03.2024 [22:43], Алексей Степин

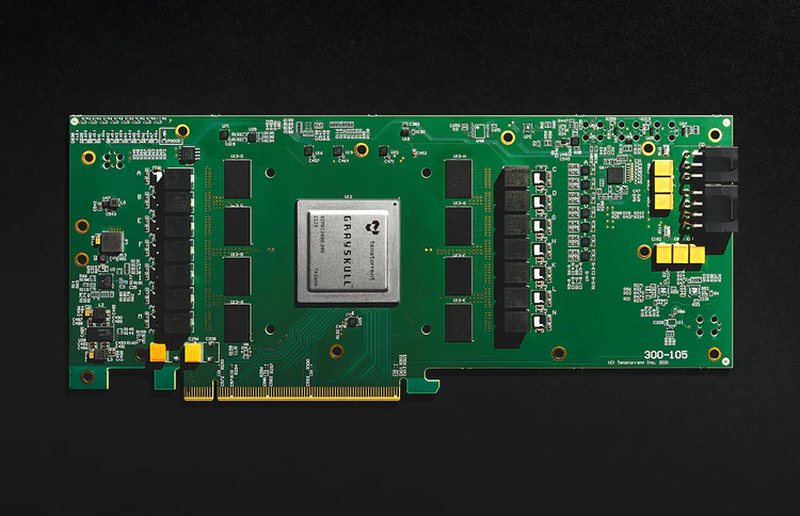

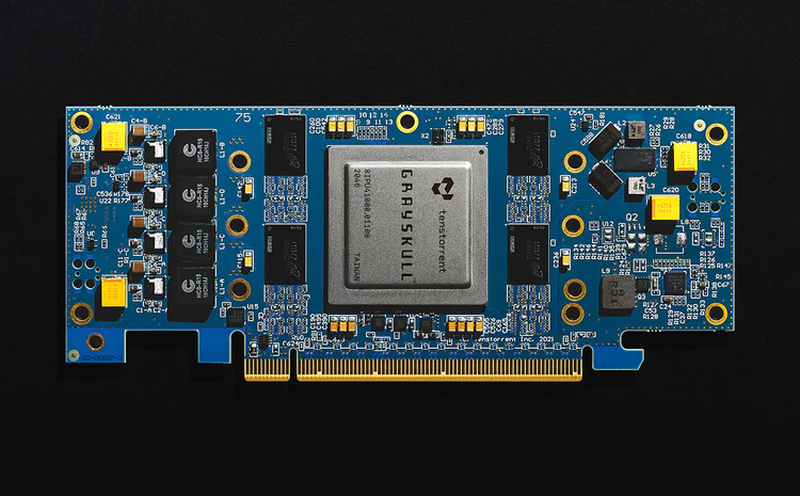

Tenstorrent под руководством Джима Келлера представила свои первые ИИ-ускорители Grayskull на базе RISC-VКанадский разработчик микрочипов Tenstorrent, возглавляемый легендарным Джимом Келлером (Jim Keller), наконец, представил свои первые решения на базе архитектуры RISC-V — ИИ-процессоры Grayskull и ускорители на их основе, Grayskull e75 и e150. Оба варианта доступны для приобретения уже сейчас по цене $599 за младшую версию и $799 за старшую. Данные решения предназначены для инференс-систем, разработки и отладки ПО. В комплект разработчика входят инструменты TT-Buda и TT-Metalium. В первом случае речь идёт о высокоуровневом стеке, предназначенном для компиляции и запуска ИИ-моделей на аппаратном обеспечении Tenstorrent, а во втором — о низкоуровневой программной платформе, обеспечивающей прямой доступ к аппаратным ресурсам. Поддерживается PyTorch, ONNX и другие фреймворки. Создатели делают особенный упор на простоте программирования в сравнении с классическими GPU. Поддерживается широкий спектр ИИ-моделей, но Tenstorrent особенно выделяет BERT, ResNet, Whisper, YOLOv5 и U-Net.

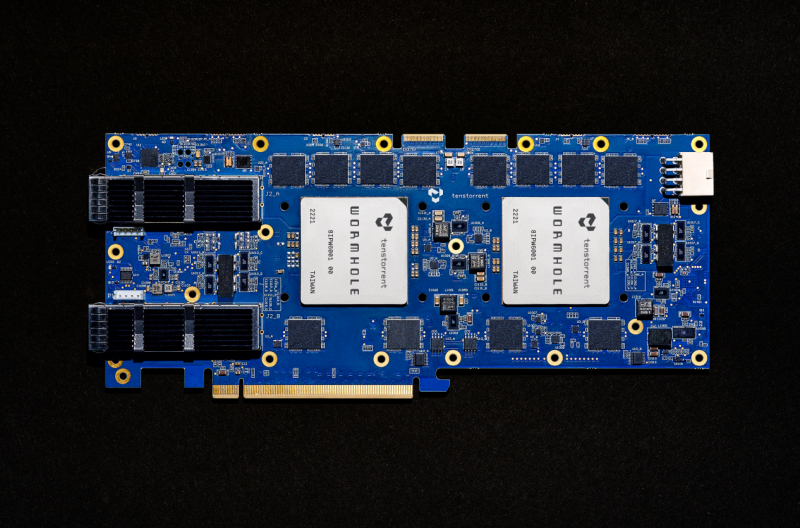

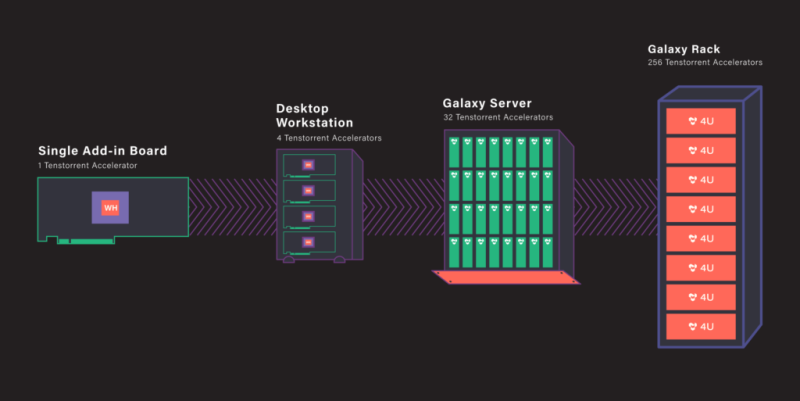

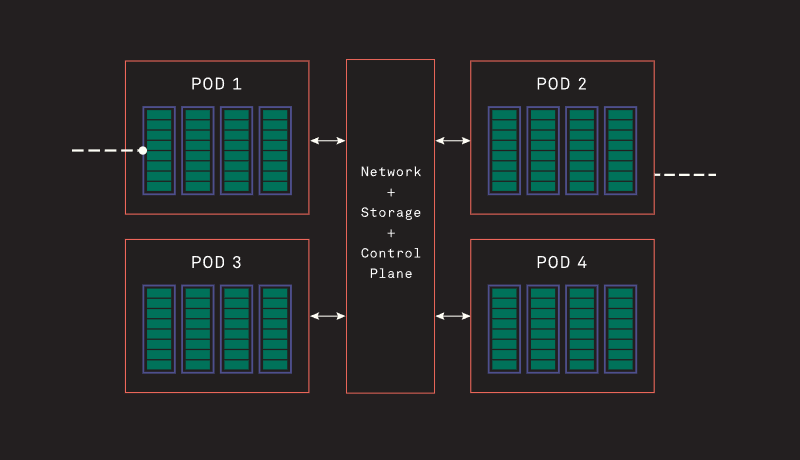

Источник изображений здесь и далее: Tenstorrent Архитектура Grayskull базируется на RISC-V, в настоящий момент максимальное количество фирменных ядер Tensix достигает 120, работают они на частотах вплоть до 1,2 ГГц. Каждое такое ядро содержит пять полноценных ядер RISC-V, блок тензорных операций, блок SIMD для векторных операций, а также ускорители сетевых операций и сжатия/декомпрессии данных. Дополнительно каждое ядро может иметь до 1,5 Мбайт сверхбыстрой памяти SRAM. Между собой ядра общаются напрямую.  В случае Grayskull e150 процессор работает в полной конфигурации со 120 ядрами и 120 Мбайт SRAM, объём внешней памяти LPDDR4 составляет 8 Гбайт (ПСП 118,4 Гбайт/с). Ускоритель выполнен в формате полноразмерной платы расширения с теплопакетом 200 Вт и интерфейсом PCIe 4.0 x16. У младшей модели, Grayskull e75, активных ядер только 96, их частота снижена до 1 ГГц, а пропускная способность внешней памяти при том же объёме снижена до 102,4 Гбайт/с. При этом теплопакет составляет всего 75 Вт, что позволило выполнить ускоритель в виде низкопрофильной платы расширения и обойтись без дополнительного питания. Чипы Wormhole тоже используют Tensix. В составе Wormhole n300 таких ядер 128 (2 × 64), частота равна 1 ГГц при теплопакете 300 Вт. Объём SRAM составляет 1,5 Мбайт на ядро, а внешняя подсистема памяти включает 24 Гбайт GDDR6 и с ПСП 576 Гбайт/с. Wormhole n150 оснащены 72 ядрами Tensix, 108 Мбайт SRAM и 12 Гбайт GDDR6 с ПСП 288 Гбайт/с. TDP составляет 160 Вт. От Grayskull эти решения отличаются возможностью масштабирования путём прямого объединения плат. Также есть по паре сетевых интерфейсов 200GbE. Возможна работа с форматами FP8/16/32, TF32, BFP2/4/8, INT8/16/32 и UINT8. Чипы Tenstorrent Grayskull и Wormhole лежат в основе уникальных масштабируемых платформ собственной разработки — AICloud и Galaxy. В первом случае используются процессоры Grayskull, поскольку Wormhole на рынке должен появиться позже. Платформа предназначена в качестве аппаратной для ИИ и HPC-нагрузок в облаке Tenstorrent.  Каждый 4U-узел AICloud высотой содержит восемь карт (16 чипов) и способен предоставить в распоряжение пользователей от 30 до 60 vCPU и от 256 до 1024 Гбайт памяти, вкупе с дисковым пространством объёмом 100–400 Гбайт. Восемь таких узлов составляют стойку, а четыре стойки — кластер Server Pod. Четыре таких кластера объединены общей системой интерконнекта, управления и СХД (до 200 Тбайт), дальнейшее масштабирование уже выходит на уровень ЦОД. В Tenstorrent Galaxy упор сделан на возможность создания высокопроизводительных ИИ-систем с быстрым интерконнектом на базе Ethernet. Строительным блоком здесь являются 80-ядерные модули Wormhole. 4U-сервер вмещает 32 таких модуля, что в совокупности даёт 2560 ядер Tensix и 384 Гбайт глобально адресуемой GDDR6. Наличие 16 каналов 200GbE в каждом модуле обеспечивает производительность интерконнекта на уровне 3,2 Тбитс. На уровне стойки высотой 48U это дает 256 чипов Wormhole, общий объём SRAM в этом случае достигает 30,7 Гбайт, а GDDR6 — 3 Тбайт. Производительность стойки оценивается разработчиками в 20 Попс (Петаопс), а совокупная скорость интерконнекта — в 76,8 Тбит/с. Расплатой за универсальность и производительность станет энергопотребление, достигающее 60 КВт.

04.02.2024 [21:02], Сергей Карасёв

Meta✴ намерена активно внедрять собственные ИИ-ускорители Artemis (MTIA) в качестве альтернативы решениям NVIDIA и AMDВ 2024 году компания Meta✴, по сообщению The Register, после многих лет разработки может начать массовое внедрение собственных ИИ-чипов. Они станут альтернативой ускорителям NVIDIA и AMD, что поможет снизить зависимость от продукции сторонних поставщиков. В 2024 году компания намерена потратить до $37 млрд на развитие своей инфраструктуры. В настоящее время для поддержания ИИ-нагрузок Meta✴ применяет такие решения, как NVIDIA H100. Ожидается, что к концу 2024 года компания будет иметь в своём распоряжении 350 тыс. этих ускорителей. Вместе с тем Meta✴ проявляет интерес и к изделиям AMD Instinct MI300. Ранее компания высоко оценила возможности Qualcomm Cloud AI 100, но отказалась от них из-за несовершенства ПО. Не приглянулись Meta✴ и чипы Esperanto. Сейчас Meta✴ ведёт разработку собственных ИИ-ускорителей.

Источник изображения: Meta✴ Весной 2023 года стало известно, что компания создала свой первый ИИ-процессор. Чип под названием MTIA (Meta✴✴ Training and Inference Accelerator; на изображении) представляет собой ASIC в виде набора блоков, функционирующих в параллельном режиме. Задействованы 64 вычислительных элемента в виде матрицы 8 × 8, каждый из которых объединяет два ядра с архитектурой RISC-V. Конструкция включает 128 Мбайт памяти SRAM, а также до 64/128 Гбайт памяти LPDDR5. Показатель TDP равен 25 Вт. Заявленная производительность на операциях INT8 достигает 102,4 TOPS, на операциях FP16 — 51,2 Тфлопс. Процессор производится по 7-нм технологии TSMC.

Источник изображения: Meta✴ Как теперь сообщается, в 2024-м Meta✴ намерена начать активное использование собственных ИИ-ускорителей с кодовым именем Artemis. В их основу лягут компоненты MTIA первого поколения. Чип Artemis, оптимизированный для инференса, будет применяться наряду с ускорителями сторонних поставщиков. При этом, как отметили представители компании, изделия Artemis обеспечат «оптимальное сочетание производительности и эффективности при рабочих нагрузках, специфичных для Meta✴».

Источник изображения: Meta✴ Компания пока не раскрывает ни архитектуру Artemis, ни конкретные рабочие нагрузки, которые будет поддерживать чип. Участники рынка полагают, что Meta✴ будет запускать готовые ИИ-модели на собственных специализированных ASIC, чтобы высвободить ресурсы ускорителей для развивающихся приложений. По данным SemiAnalysis, Artemis получит улучшенные ядра, а компоненты LPDDR5 уступят место более быстрой памяти, использующей технологию TSMC CoWoS. Нужно добавить, что Amazon и Google уже несколько лет используют собственные чипы для ИИ-задач. Например, Amazon недавно ИИ-ускорители Trainium2 и Inferenetia2, тогда как Google в 2023 году представила сразу два новых ускорителя: Cloud TPU v5p и TPU v5e. А Microsoft сообщила о создании ИИ-ускорителя Maia 100.

19.11.2023 [03:00], Сергей Карасёв

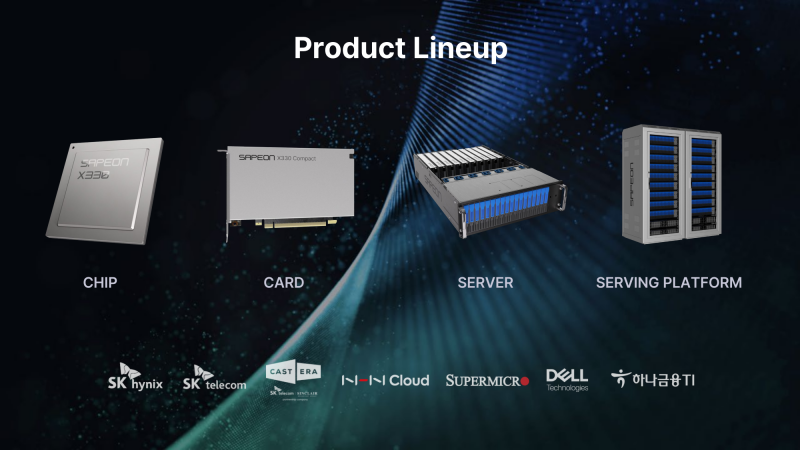

Южнокорейский стартап Sapeon представил 7-нм ИИ-чип X330ИИ-стартап Sapeon, поддерживаемый южнокорейским телекоммуникационным гигантом SK Group, анонсировал чип X330, предназначенный для инференса и обслуживания больших языковых моделей (LLM). Изделие ляжет в основу специализированных ускорителей для дата-центров. Sapeon заявляет, что новый нейропроцессор (NPU) обеспечивает примерно вдвое более высокую производительность и в 1,3 раза лучшую энергоэффективность, чем продукты конкурентов, выпущенные в этом году. По сравнению с предыдущим решением самой компании — Sapeon X220 — достигается увеличение быстродействия в четыре раза и повышение энергоэффективности в два раза. Новинка будет изготавливаться на TSMC по 7-нм технологии. Массовое производство запланировано на I полугодие 2024 года. На базе чипа будут предлагаться два ускорителя — X330 Compact Card и X330 Prime Card. Оба имеют однослотовое исполнение и оснащаются системой пассивного охлаждения. Для подключения применяется интерфейс PCIe 5.0 х16. Карты могут осуществлять вычисления INT8, FP8 и FP16. Модель X330 Compact Card уменьшенной длины несёт на борту 16 Гбайт памяти GDDR6 с пропускной способностью до 256 Гбайт/с. Заявленная производительность на операциях FP8 и FP16 достигает соответственно 367 и 184 Тфлопс. Энергопотребление варьируется в диапазоне от 75 до 120 Вт. Полноразмерная модификация X330 Prime Card получила 32 Гбайт памяти GDDR6 с пропускной способностью до 512 Гбайт/с. Заявленное быстродействие FP8 и FP16 составляет до 734 и 368 Тфлопс. Энергопотребление — 250 Вт. Группа SK в последнее время активно вкладывается в развитие ИИ, инвестируя напрямую или через дочерние структуры как в софт, так и в железо. С ней, в частности, связан ещё один южнокорейский разработчик ИИ-чипов Rebellions, также поддерживаемый правительством страны, которое намерено к 2030 году довести долю отечественных ИИ-чипов в местных дата-центрах до 80 %. Делается это для того, чтобы снизить зависимость от иностранных решений и избежать дефицита. Сама же Sapeon готовит ещё минимум два поколения своих чипов.

20.09.2023 [20:05], Алексей Степин

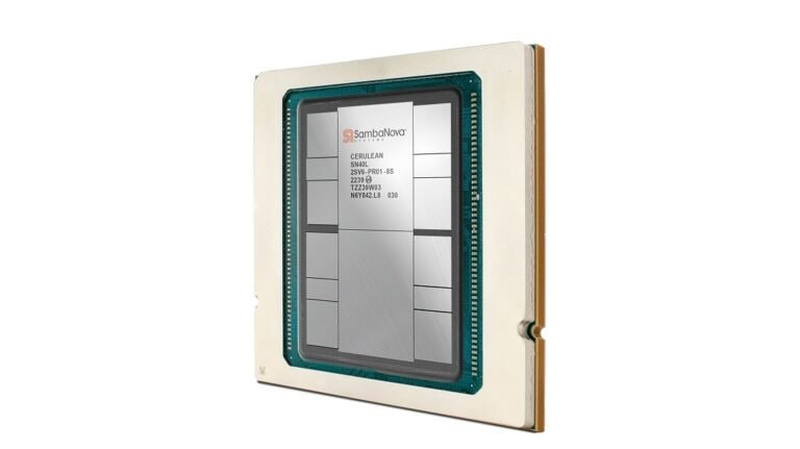

SambaNova представила ИИ-ускоритель SN40L с памятью HBM3, который в разы быстрее GPUБум больших языковых моделей (LLM) неизбежно порождает появление на рынке нового специализированного класса процессоров и ускорителей — и нередко такие решения оказываются эффективнее традиционного подхода с применением GPU. Компания SambaNova Systems, разработчик таких ускорителей и систем на их основе, представила новое, третье поколение ИИ-процессоров под названием SN40L. Осенью 2022 года компания представила чип SN30 на базе уникальной тайловой архитектуры с программным управлением, уже тогда вполне осознавая тенденцию к увеличению объёмов данных в нейросетях: чип получил 640 Мбайт SRAM-кеша и комплектовался оперативной памятью объёмом 1 Тбайт.

Источник изображений здесь и далее: SambaNova (via EE Times) Эта наработка легла и в основу новейшего SN40L. Благодаря переходу от 7-нм техпроцесса TSMC к более совершенному 5-нм разработчикам удалось нарастить количество ядер до 1040, но их архитектура осталась прежней. Впрочем, с учётом реконфигурируемости недостатком это не является. Чип SN40L состоит из двух больших чиплетов, на которые приходится 520 Мбайт SRAM-кеша, 1,5 Тбайт DDR5 DRAM, а также 64 Гбайт высокоскоростной HBM3. Последняя была добавлена в SN40L в качестве буфера между сверхбыстрой SRAM и относительно медленной DDR. Это должно улучшить показатели чипа при работе в режиме LLM-инференса. Для эффективного использования HBM3 программный стек SambaNova был соответствующим образом доработан.

Тайловая архитектура SambaNova состоит из вычислительных тайлов PCU, SRAM-тайлов PMU, управляющей логики и меш-интерконнекта По сведениям SambaNova, восьмипроцессорная система на базе SN40L сможет запускать и обслуживать ИИ-модель поистине титанических «габаритов» — с 5 трлн параметров и глубиной запроса более 256к. В описываемой модели речь идёт о наборе экспертных моделей с LLM Llama-2 в качестве своеобразного дирижёра этого оркестра. Архитектура с традиционными GPU потребовала бы для запуска этой же модели 24 сервера с 8 ускорителями каждый; впрочем, модель ускорителей не уточняется. Как и прежде, сторонним клиентам чипы SN40L и отдельные вычислительные узлы на их основе поставляться не будут. Компания продолжит использовать модель Dataflow-as-a-Service (DaaS) — расширяемую платформу ИИ-сервисов по подписке, включающей в себя услуги по установке оборудования, вводу его в строй и управлению в рамках сервиса. Однако SN40L появится в рамках этой услуги позднее, а дебютирует он в составе облачной службы SambaNova Suite.

15.09.2023 [20:52], Алексей Степин

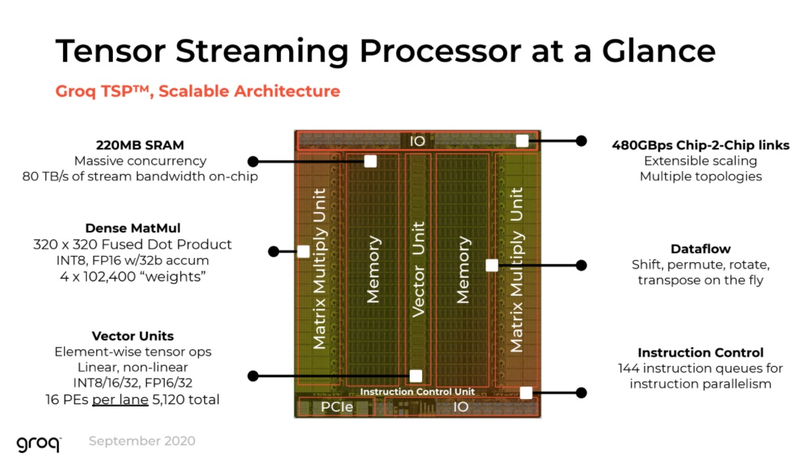

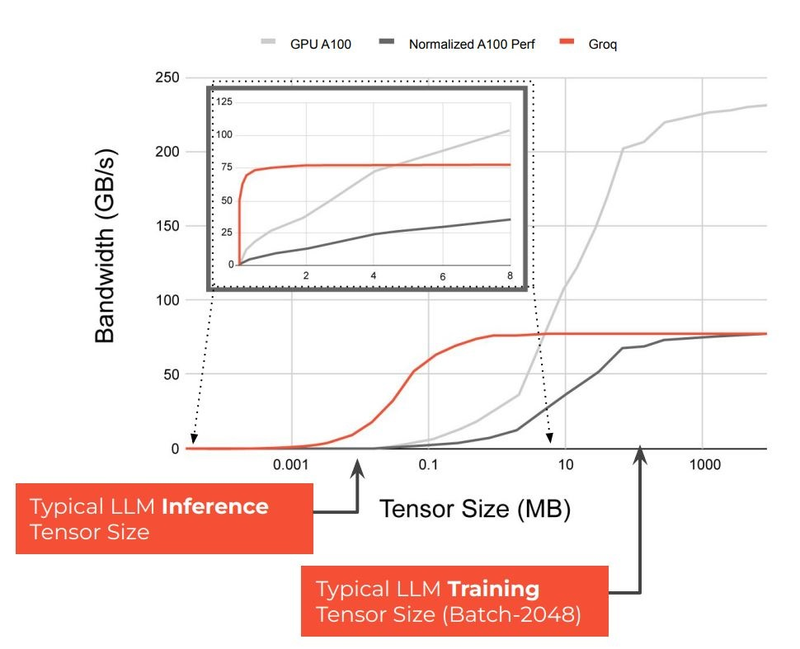

Groq назвала свои ИИ-чипы TSP четырёхлетней давности идеальными для LLM-инференсаТензорный процессор TSP, разработанный стартапом Groq, был анонсирован ещё осенью 2019 года и его уже нельзя назвать новым. Тем не менее, как сообщает Groq, TSP всё ещё является достаточно мощным решением для инференса больших языковых моделей (LLM). Теперь Groq позиционирует своё детище как LPU (Language Processing Unit) и продвигает его в качестве идеальной платформы для запуска больших языковых моделей (LLM). Согласно имеющимся данным, в этом качестве четырёхлетний процессор проявляет себя весьма неплохо. Groq открыто хвастается своим преимуществом над GPU, но в последних раундах MLPerf участвовать не желает.

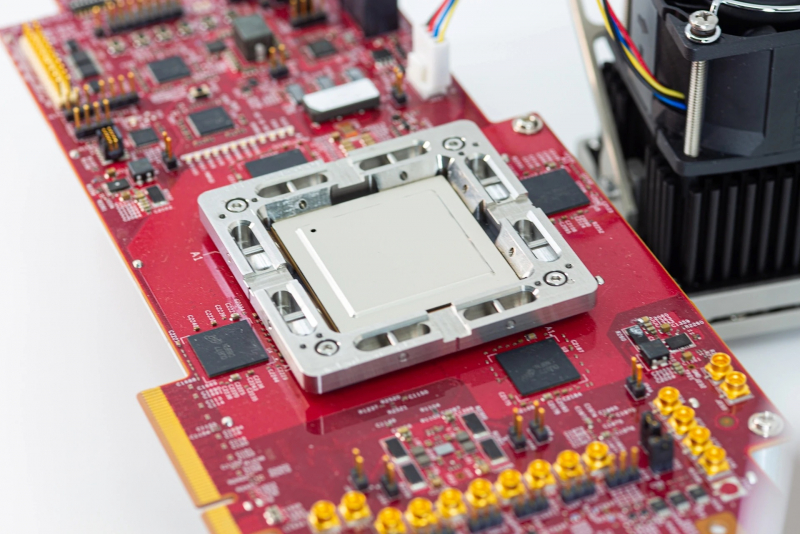

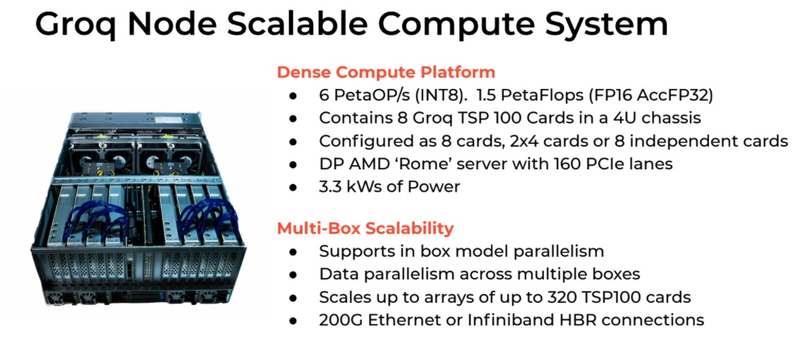

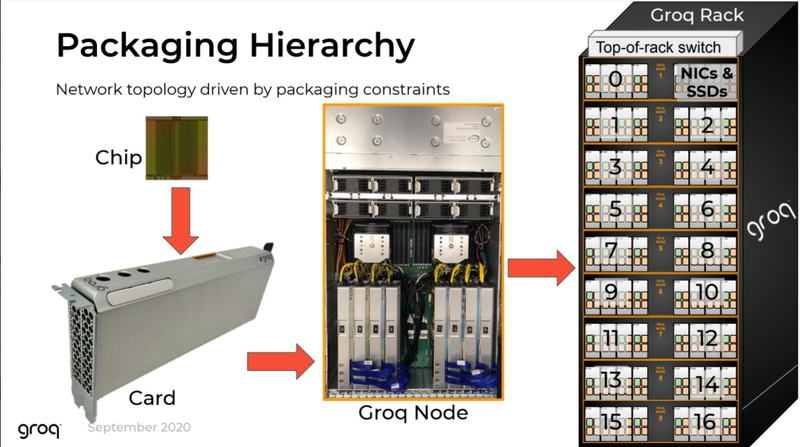

Источник изображений здесь и далее: Groq В своё время Groq разработала не только сам тензорный процессор, но и дизайн ускорителя на его основе, а также продумала вопрос взаимодействия нескольких TSP в составе вычислительного узла с дальнейшим масштабированием до уровня мини-кластера. Именно для такого кластера и опубликованы свежие данные о производительности Groq в сфере LLM.  Система разработки, содержащая в своём составе 640 процессоров Groq TSP, была успешно использована для запуска модели Meta✴ Llama-2 с 70 млрд параметров. Как показали результаты тестов, модель на данной платформе работает с производительностью 240 токенов в секунду на пользователя. Для адаптации и развёртывания Llama-2, по словам создателей Groq, потребовалось всего несколько дней. В настоящее время усилия Groq будут сконцентрированы на адаптации имеющейся платформы в сфере LLM-инференса, поскольку данный сектор рынка растёт быстрее, нежели сектор обучения ИИ-моделей. Для LLM-инференса важнее умение эффективно масштабировать потоки небольших блоков (8–16 Кбайт) на большое количество чипов.  В этом Groq TSP превосходит NVIDIA A100: если в сравнении двух серверов выиграет решение NVIDIA, то уже при 40 серверах показатели латентности у Groq TSP будут намного лучше. В распоряжении Groq имеется пара 10-стоечных кластеров с 640 процессорами, один из которых используется для разработки, а второй — в качестве облачной платформы для клиентов Groq в области финансовых услуг. Работает система Groq и в Аргоннской национальной лаборатории (ALCF), где она используется для исследований в области термоядерной энергетики.  В настоящее время Groq TSP производятся на мощностях GlobalFoundries, а упаковка чипов происходит в Канаде, но компания работает над вторым поколением своих процессоров, которое будет производиться уже на заводе Samsung в Техасе. Параллельно Groq работает над созданием 8-чипового ускорителя на базе TSP первого поколения. Это делается для уплотнения вычислений, а также для более полного использования проприетарного интерконнекта и обхода ограничений, накладываемых шиной PCIe 4.0. Также ведётся дальнейшая оптимизация ПО для кремния первого поколения.  Простота и скорость разработки ПО для платформы Groq TSP объясняется историей создания этого процессора — начала Groq с создания компилятора и лишь затем принялась за проектирование кремния с учётом особенностей этого компилятора. Перекладывание на плечи компилятора всех задач оркестрации вычислений позволило существенно упростить дизайн TSP, а также сделать предсказуемыми показатели производительности и латентности ещё на этапе сборки ПО. При этом архитектура Groq TSP вообще не предусматривает использования «ядер» (kernels), то есть не требует блоков низкоуровневого кода, предназначенного для общения непосредственно с аппаратной частью. В случае с TSP любая задача разбивается на набор небольших инструкций, реализованных в кремнии и выполняемых непосредственно чипом.

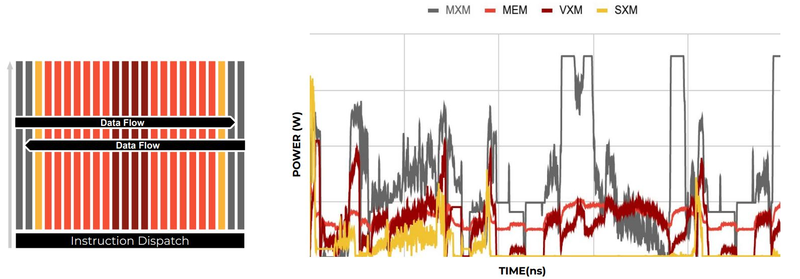

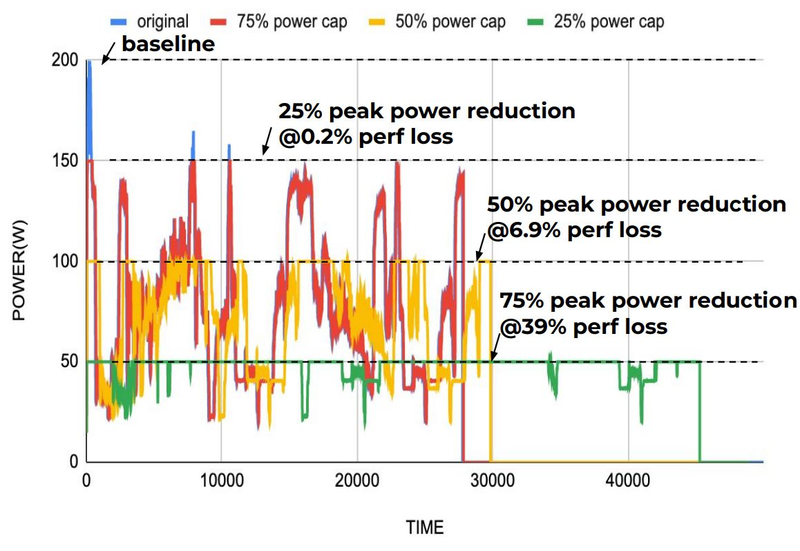

Компилятор Groq позволяет визуализировать и предсказывать энергопотребление с точностью до наносекунд. Источник: Groq Предсказуемость Groq TSP распространяется и на энергопотребление: оно полностью профилируется ещё на этапе компиляции, так что пики и провалы можно спрогнозировать с точностью вплоть до наносекунд. Это позволяет добиться от платформы более надёжного функционирования, избежав так называемой «тихой» порчи данных — сбоев, происходящих в результате резких всплесков энергетических и тепловых параметров кремния.

Энергопотребление Groq TSP поддаётся тонкой настройке на уровне программного обеспечения. Источник: Groq Что касается будущего LLM-инференса, то Groq считает, что этой отрасли есть, куда расти. В настоящее время LLM дают ответ на запрос сразу, и затем пользователи могут уточнить его в последующих итерациях, но в будущем они начнут «рефлексировать» — то есть, «продумывать» несколько вариантов одновременно, используя совокупный результат для более точного «вывода» и ответа. Разумеется, такой механизм потребует больших вычислительных мощностей, и здесь масштабируемая и предсказуемая архитектура Groq TSP может прийтись как нельзя более к месту.

21.03.2023 [19:45], Игорь Осколков

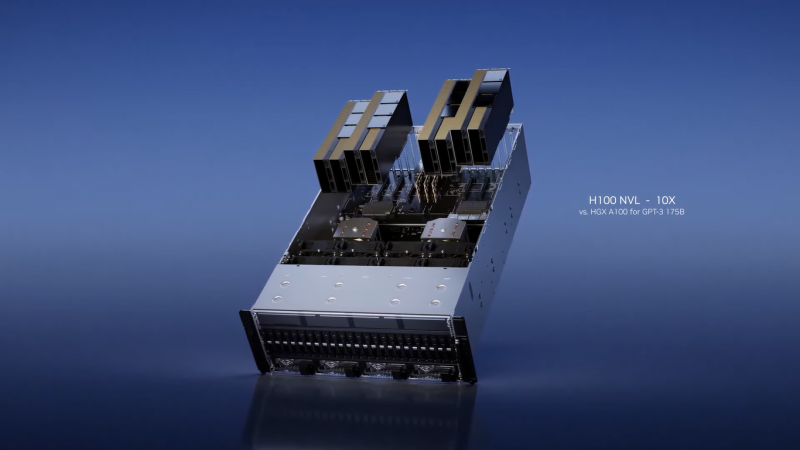

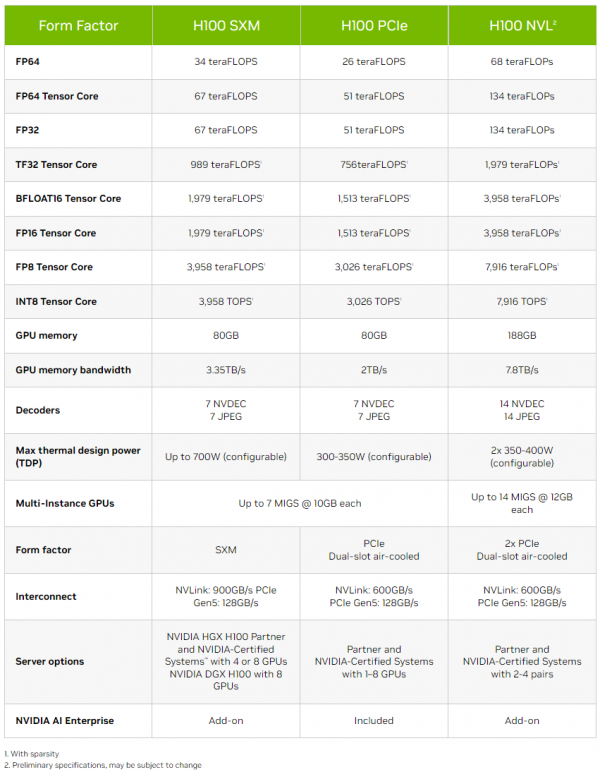

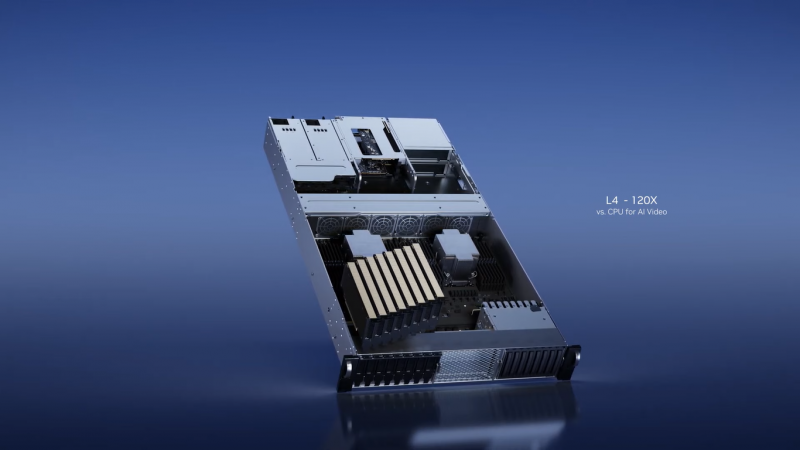

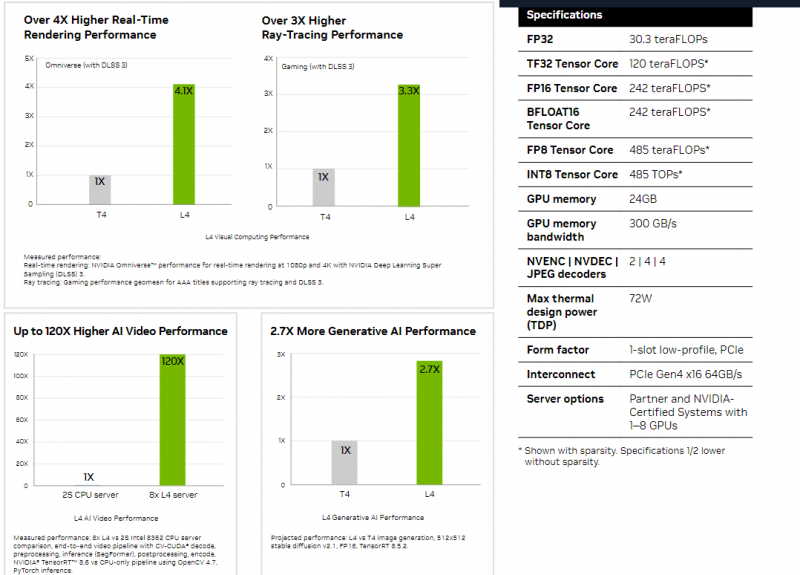

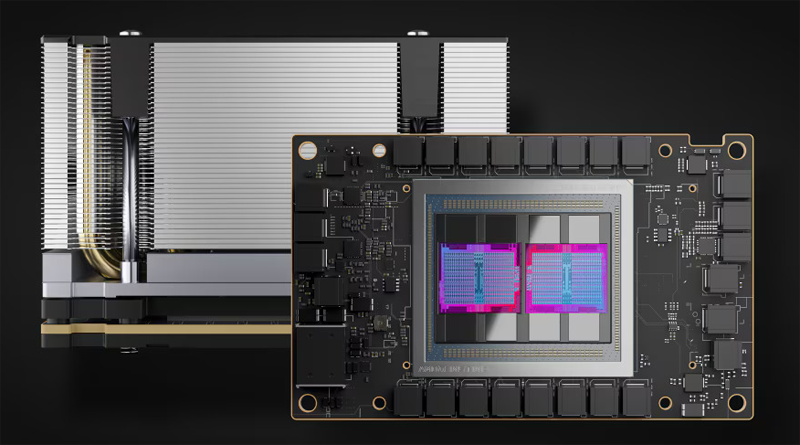

Толстый и тонкий: NVIDIA представила самый маленький и самый большой ИИ-ускорители L4 и H100 NVLНа весенней конференции GTC 2023 компания NVIDIA представила два новых ИИ-ускорителя, ориентированных на инференес: неприличной большой H100 NVL, фактически являющийся парой обновлённых ускорителей H100 в формате PCIe-карты, и крошечный L4, идущий на смену T4. NVIDIA H100 NVL действительно выглядит как пара H100, соединённых мостиками NVLink. Более того, с точки зрения ОС они выглядят как пара независимых ускорителей, однако ПО воспринимает их как единое целое, а обмен данными между двумя картам идёт в первую очередь по мостикам NVLink (600 Гбайт/с). Новинка создана в первую очередь для исполнения больших языковых ИИ-моделей, в том числе семейства GPT, а не для их обучения. Однако аппаратно это всё же не просто пара обычных H100 PCIe. По уровню заявленной производительности NVL-вариант вдвое быстрее одиночного ускорителя H100 SXM, а не PCIe — 3958 и 7916 Тфлопс в разреженных (в обычных показатели вдвое меньше) FP16- и FP8-вычислениях на тензорных ядрах соответственно, что в 2,6 раз больше, чем у H100 PCIe. Кроме того, NVL-вариант получил сразу 188 Гбайт HBM3-памяти с суммарной пропускной способностью 7,8 Тбайт/с. NVIDIA утверждает, что форм-фактор H100 NVL позволит задействовать новинку большему числу пользователей, хотя четыре слота и TDP до 800 Вт подойдут далеко не каждой платформе. NVIDIA H100 NVL станет доступна во второй половине текущего года. А вот ещё одну новинку, NVIDIA L4 на базе Ada, в ближайшее время можно будет опробовать в облаке Google Cloud Platform, которое первым получило этот ускоритель. Кроме того, он же будет доступен в рамках платформы NVIDIA Launchpad, да и ключевые OEM-производители тоже взяли его на вооружение. Сама NVIDIA называет L4 поистине универсальным серверным ускорителем начального уровня. Он вчетверо производительнее NVIDIA T4 с точки зрения графики и в 2,7 раз — с точки зрения инференса. Маркетинговые упражнения компании при сравнении L4 с CPU оставим в стороне, но отметим, что новинка получила новые аппаратные ускорители (де-)кодирования видео и возможность обработки 130 AV1-потоков 720p30 для мобильных устройств. С L4 возможны различные сценарии обработки видео, включая замену фона, AR/VR, транскрипцию аудио и т.д. При этом ускорителю не требуется дополнительное питание, а сам он выполнен в виде HHHL-карты. |

|