Материалы по тегу: sapphire rapids

|

27.04.2026 [13:35], Сергей Карасёв

«Гравитон» представил российские серверы на базе Intel Xeon для облаков, виртуализации и ИИ

emerald rapids

gpu

granite rapids

hardware

intel

sapphire rapids

sierra forest

xeon

гравитон

сделано в россии

сервер

Российский разработчик и производитель вычислительной техники «Гравитон» представил шесть серверов на аппаратной платформе Intel, предназначенных для реализации масштабных IT-проектов в сегментах, где наличие техники в реестре Минпромторга РФ не является обязательным требованием. В зависимости от модификации устройства подходят для решения различных задач — от облачных сервисов и виртуализации до нагрузок ИИ и НРС. В частности, дебютировали модели СН2124И5 и СН2127И5 в форм-факторе 4U и 7U соответственно. Они рассчитаны на два процессора Xeon Sapphire Rapids или Xeon Emerald Rapids с TDP до 350 Вт. Поддерживается до 8 Тбайт оперативной памяти DDR5 в виде 32 модулей. У сервера СН2124И5 слоты расширения выполнены по схеме 10 × PCIe 5.0 х16 FHFL + 1 × OCP NIC. Есть 12 фронтальных отсеков для LFF-накопителей NVMe/SATA/SAS и два коннектора M.2 2280/22110 (PCIe 5.0). Возможна установка восьми GPU с энергопотреблением до 350 Вт. В свою очередь, система СН2127И5 имеет аналогичные характеристики, но позволяет использовать до восьми GPU с TDP до 600 Вт. Кроме того, анонсированы серверы СН2122И6 (2U), СН2242И6 (2U), СН2124И6 (4U) и СН2127И6 (7U) с поддержкой двух чипов Xeon 6 (Sierra Forest-SP/Granite Rapids-SP) с показателем TDP до 350 Вт. У первой из этих систем слоты расширения выполнены по схеме 6 × PCIe 5.0 х16 FHFL + 2 × OCP NIC (или 6 × PCIe 5.0 х16 FHFL + 2 × PCIe 5.0 х8 HHHL + 2 × OCP NIC), у трёх других — 10 × PCIe 5.0 х16 FHFL + 1 × OCP NIC. Во всех случаях возможно использование до 8 Тбайт памяти DDR5 (32 модуля).

Источник изображений: «Гравитон» Модель СН2122И6 поддерживает следующие накопители: 12 × LFF NVMe/SATA/SAS во фронтальной части, 2 × SFF SATA/SAS или 4 × SFF NVMe/SATA/SAS, а также 2 × M.2 2280/22110 (PCIe 5.0). Модификации СН2242И6, СН2124И6 и СН2127И6 рассчитаны на накопители в конфигурации 12 × LFF NVMe/SATA/SAS и 2 × M.2 2280/22110 (PCIe 5.0). Две старшие версии поддерживают восемь GPU с TDP до 350 и 600 Вт.  Все серверы располагают контроллером Aspeed AST2600 с выделенным сетевым портом управления 1GbE и воздушной системой охлаждения. Устанавливаются блоки питания мощностью до 3000 Вт с сертификатом 80 Plus Platinum. Заявлена совместимость с Windows и Linux. Гарантия производителя составляет три года.

19.02.2026 [12:26], Сергей Карасёв

«НВБС» представила российские серверы «Необайт» на платформах Intel и AMDКомпания «НВБС», российский системный интегратор и производитель технологических решений, анонсировала собственные серверы семейства «Необайт». Дебютировали модели NeoByte NBR220 и NeoByte NBR680 на аппаратной платформе Intel, а также NeoByte NBR685 с процессорами AMD. По словам компании, новинки «сопоставимы с решениями ведущих компаний на рынке, но при этом в среднем стоят на 10–15 % дешевле за счёт широкого пула поставщиков и оптимизированной логистики». Система NeoByte NBR220 типоразмера 2U может нести на борту два чипа Intel Xeon Sapphire Rapids или Emerald Rapids с показателем TDP до 350 Вт. Доступны 32 слота для модулей оперативной памяти DDR5-4800. В зависимости от конфигурации во фронтальной части возможна установка 12 накопителей LFF/SFF или 24 устройств SFF с интерфейсом SATA/SAS/NVMe. В тыльной зоне корпуса расположены посадочные места ещё для четырёх накопителей LFF/SFF (SATA/SAS/NVMe), тогда как внутри есть два коннектора для SSD формата M.2 (SATA/NVMe). Реализована поддержка до 10 стандартных слотов PCIe и одного слота OCP 3.0. В оснащение входят контроллер AST2600, два сетевых порта 1GbE, выделенный сетевой порт управления 1GbE, четыре порта USB 3.0 (по два спереди и сзади), два интерфейса D-Sub (по одному спереди и сзади) и последовательный порт. Питание обеспечивают два блока с резервированием мощностью 800/1300/1600/2000 Вт. Сервер оптимизирован для ИИ-задач, виртуализации, баз данных и файловых хранилищ. Платформа практически идентична представленным ранее серверам «Аквариус» AQserv T50 D224RS и T50 D212RS. Модель NeoByte NBR680 стандарта 6U имеет аналогичные характеристики подсистем CPU, ОЗУ, хранения данных и интерфейсов ввода/вывода. При этом возможна установка до восьми GPU-ускорителей двойной ширины. Есть пять стандартных слотов PCIe и один слот OCP; передняя панель поддерживает до трёх стандартных слотов PCIe и один слот OCP. Мощность каждого из двух блоков питания — 2700 или 3200 Вт. Машина предназначена для научных исследований и крупных ИИ-проектов. В свою очередь, GPU-сервер NeoByte NBR685 формата 6U рассчитан на два процессора AMD EPYC 9005 Turin или EPYC 9004 Genoa с показателем TDP до 500 Вт. Предусмотрены 24 слота для модулей оперативной памяти DDR5-4800. Прочие характеристики идентичны версии NeoByte NBR680, включая поддержку восьми GPU-ускорителей двойной ширины. Система подходит для анализа больших данных в реальном времени, криптографии и блокчейна. Все новинки могут быть опционально укомплектованы контроллером SAS RAID/HBA. Заявлена совместимость с Windows Server 2022 SLES 12.5 и выше, RHEL7.8 и выше, Ubuntu18.04 и выше, CentOS7.6 и выше, Vmware ESXi 7.0 GA и выше. Гарантия производителя достигает пяти лет. Также «НВБС» говорит, что «не зависит от санкций, что снижает риски ограничения поставок».

20.01.2026 [12:12], Сергей Карасёв

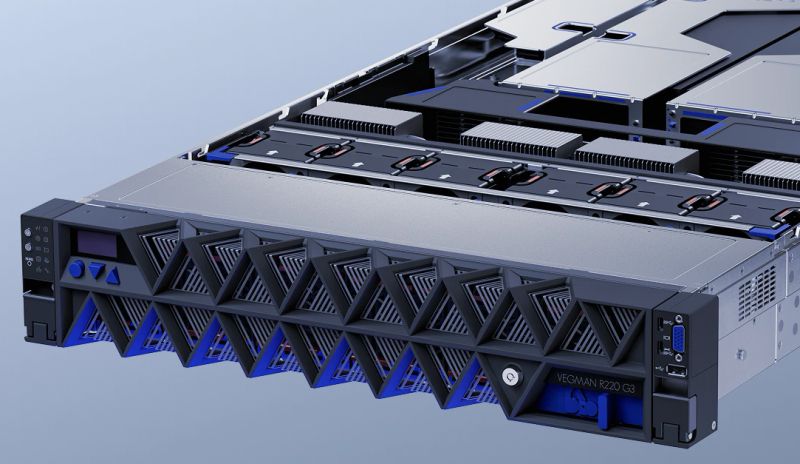

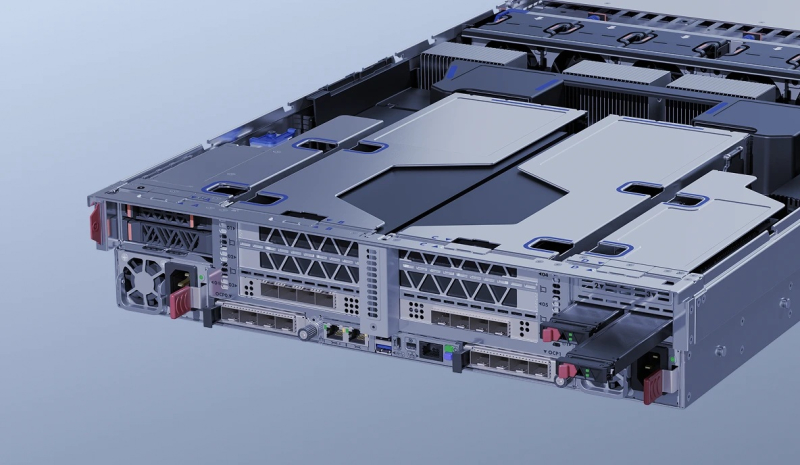

YADRO выпустила отечественные серверы Vegman R220 G3 на базе Intel Xeon Emerald RapidsКомпания YADRO, входящая в «ИКС Холдинг», объявила о доступности универсальных серверов Vegman R220 G3 на аппаратной платформе Intel. Устройства подходят для широкого спектра задач — от хранения и аналитики данных до НРС-приложений и нагрузок ИИ, говорит компания. Новинки выполнены в форм-факторе 2U. Допускается установка двух процессоров Xeon Sapphire Rapids или Xeon Emerald Rapids с показателем TDP до 350 Вт. Возможно использование до 8 Тбайт оперативной памяти DDR5-4400/5600 RDIMM в конфигурации 32 × 256 Гбайт. Во фронтальной части в зависимости от модификации могут быть установлены до 12 накопителей LFF (SAS/SATA/NVMe) или до 24 накопителей SFF (SAS/SATA плюс 16 × NVMe). Сзади предусмотрены посадочные места для четырёх изделий SFF (или 2 × SFF и 2 × M.2/E1.S). Допускается формирование массивов RAID 0/1/10/5/50/6/60. Реализована поддержка CXL 1.1. Есть два сетевых порта 1GbE и выделенный сетевой порт управления 1GbE (все с разъёмами RJ45). Доступны до 11 слотов PCIe 5.0 с учетом OCP 3.0 SFF и гнезда под контроллер RAID/HBA. Спереди находятся два порта USB 3.1 Type-C, по одному разъёму USB 2.0 Type-A и D-Sub, сзади — два порта USB 3.1 Type-A, последовательный интерфейс (разъём USB Type-C) и коннектор Mini DisplayPort (BMC). Питание обеспечивают два блока мощностью до 2700 Вт с сертификатом 80 PLUS Platinum. Применено воздушное охлаждение с шестью вентиляторами диаметром 60 мм с возможностью горячей замены. Диапазон рабочих температур — от +10 до +35 °C при относительной влажности от 20 % до 80 %. Заявлена совместимость с Astra Linux, ALT Linux, RED OS, zVirt и пр. С серверами поставляется ПО управления «YADRO Суприм» и набор инструментов Vegman Satellites. Реализована поддержка доступа через IPMI 2.0, WebUI, CLI, SNMP, Redfish. Устройства Vegman R220 G3 включены в Единый реестр российской радиоэлектронной продукции Минпромторга, что подтверждает соблюдение требований локализации.

22.12.2025 [08:07], Сергей Карасёв

Российские двухсокетные серверы Amur Terra поддерживают чипы Intel Xeon Emerald RapidsРоссийский производитель вычислительной техники Amur представил серверы семейства Terra A02R на аппаратной платформе Intel. В серию вошли модели 12S2S и 24S2S формата 2U и версия 24S12S2S типоразмера 4U. Все новинки внесены в реестр Минромторга РФ, протестированы на совместимость с реестровыми российскими ОС и прикладным ПО, говорит компания. Устройства оснащены материнской платой на наборе логики Intel C741A. Они могут нести на борту два процессора Intel Xeon Sapphire Rapids или Xeon Emerald Rapids. Поддерживается до 8 Тбайт оперативной памяти DDR5-4400/4800/5600 МГц RDIMM/LRDIMM в виде 32 модулей. Базовая модель Terra A02R 12S2S оборудована 12 фронтальными отсеками для накопителей LFF/SFF с интерфейсом SATA/SAS (опционально NVMe). Дополнительно могут быть реализованы два тыльных слота для SFF-устройств SATA. Этот сервер предназначен для работы с большими массивами данных в памяти, построения систем виртуализации, поддержки критически важных бизнес-приложений и пр.

Источник изображений: Amur Модификация Terra A02R 24S2S допускает установку 24 фронтальных SFF-накопителей SATA/SAS/NVMe и двух тыльных SFF-устройств SATA (опционально). Машина подходит для создания файловых серверов, систем виртуализации высокой плотности и VDI, аналитики и работы с СУБД, требующими высоких скоростей чтения, включая PostgreSQL, Tantor, MySQL.  Сервер Terra A02R 24S12S2S рассчитан на 24 фронтальных и 12 тыльных накопителей LFF/SFF с интерфейсом SATA/SAS (плюс два опциональных SFF-устройства SATA сзади). Таким образом, могут формироваться системы хранения высокой ёмкости — на уровне 1 Пбайт.  Все новинки располагают контроллером Aspeed AST2600, двумя блоками питания мощностью 1300/1600 Вт с горячей заменой и резервированием, портами D-Sub (спереди и сзади), USB 3.0 (по два спереди и сзади), 1GbE (RJ45) и последовательным портом. Слоты расширения в стандартной конфигурации выполнены по схеме 1 × PCIe 5.0 x16 FHFL, 2 × PCIe 5.0 x8 FHFL+FHHL, 2 × OCP 3.0. Альтернативная схема — 2 × PCIe 5.0 x16 FHFL+FHHL, 2 × PCIe 5.0 x8 HHHL или 1 × PCIe 5.0 x16 HHHL. Возможна установка двух GPU полной высоты, полной длины и двойной толщины (например, NVIDIA A100, H100). Диапазон рабочих температур — от +5 до +35 °C при относительной влажности от 35 % до 80 % без конденсации.

12.11.2025 [10:28], Владимир Мироненко

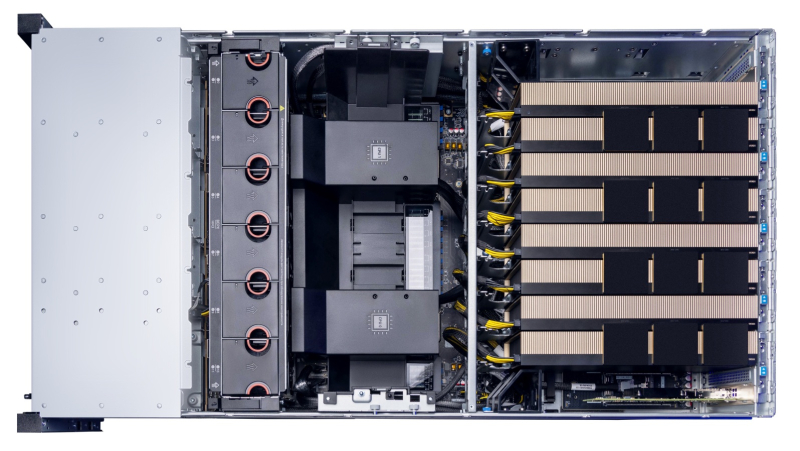

YADRO выводит на рынок высокопроизводительный ИИ-сервер для компаний, внедряющих искусственный интеллектYADRO (входит в «ИКС Холдинг») объявляет о коммерческом запуске ИИ-сервера YADRO G4208P G3 — решения для компаний, которые рассматривают искусственный интеллект как стратегический драйвер роста. В условиях перехода рынка от отдельных пилотных проектов к широкому внедрению прикладных сценариев использования искусственного интеллекта новый сервер призван удовлетворить растущий спрос бизнеса на масштабируемую инфраструктуру с предсказуемой эффективностью. Многолетний опыт YADRO в построении ИИ-систем для российских заказчиков лёг в основу архитектуры нового сервера G4208P G3. Платформа спроектирована под реальные задачи бизнеса: дообучение корпоративных моделей и обучение компактных моделей, высокопроизводительный инференс в промышленной среде, а также задачи, где требуется GPU-ускорители, включая видеоаналитику и обработку изображений. YADRO G4208P G3 поддерживает установку до восьми GPU-ускорителей и конфигурации на основе двух процессоров Intel Xeon Scalable 4-го/5-го поколений с интерфейсами PCIe 5.0 и памятью DDR5-5600. Сочетание производительности и масштабируемости такого уровня выводит сервер в число самых сильных предложений на российском рынке. Сервер прошел серию испытаний и сравнений с публичными бенчмарками, включая MLCommons и прикладные тесты для генеративных моделей (LLM). Результаты подтвердили уровень производительности и эффективности, сопоставимый с решениями ведущих мировых вендоров. Для российских компаний это означает, что инфраструктура на базе YADRO G4208P G3 позволит запускать крупные современные ИИ- модели, включая DeepSeek-R1 685B, и обеспечить их стабильную работу в продуктивной среде с соблюдением целевых SLO/SLA, снижением времени отклика сервисов и контролируемыми затратами на развитие инфраструктуры. Параллельно идёт широкая программа испытаний совместно с технологическими партнёрами — разработчиками отечественных программных решений. Ряд сценариев уже успешно протестирован, подтверждены совместимость и ключевые показатели производительности. ИИ-стеки, валидированные на базе серверов YADRO, формируют инфраструктурную основу для развития отечественных технологий искусственного интеллекта. YADRO сопровождает заказчиков на всем пути внедрения своих продуктов. Команда помогает определить оптимальную конфигурацию под конкретные задачи — от картирования рабочих нагрузок и выбора архитектуры до пилотирования и настройки производительности. Полный цикл сервиса включает консультирование, инсталляцию, сопровождение и поддержку на всём жизненном цикле решения. В результате заказчики получают устойчивую ИИ-инфраструктуру, которая работает надёжно и развивается вместе с бизнесом. «Компании переходят к практической интеграции ИИ в ключевые процессы, и мы уверены, что сейчас самый подходящий момент для выхода сервера YADRO G4208P G3. Платформа создана на основе нашего опыта реальных внедрений и ориентирована на быстрый путь от идеи к промышленной эксплуатации. Мы предлагаем оборудование и экспертную поддержку — от выбора конфигурации и внедрения до последующего обслуживания — чтобы заказчики могли эффективно управлять развитием своих ИИ- инициатив», — резюмирует Павел Егоров, директор по продуктам YADRO. Сервер YADRO G4208P G3 внесён в Единый реестр российской радиоэлектронной продукции Минпромторга, что подтверждает его соответствие требованиям импортозамещения и открывает возможность применения в государственных и корпоративных проектах с требованиями по локализации. Подробнее ознакомиться с конфигурациями, результатами тестов и сценариями применения, а также получить рекомендации экспертов и оставить заявку на пилотное тестирование сервера можно на сайте.

13.10.2025 [13:20], Сергей Карасёв

«Инферит» представил российские 2U-серверы для ИИ на базе Intel Xeon Emerald RapidsРоссийский поставщик IT-решений «Инферит» (ГК Softline) анонсировал серверы на аппаратной платформе Intel. Дебютировали модели UR2X2G4V1-D24, GR2X2G4V1-D24, UR2X2G4V1-D12 и GR2X2G4V1-D12 для решения различных задач. Все новинки выполнены в форм-факторе 2U. Они могут нести на борту два процессора Intel Xeon Sapphire Rapids или Xeon Emerald Rapids с TDP до 350 Вт. Поддерживается до 8 Тбайт оперативной памяти DDR5-4400/4800 в виде 32 модулей. Модель Inferit UR2X2G4V1-D24 предназначена для комплексных вычислений, виртуализации, облачных сервисов и работы с большими данными. Во фронтальной части расположены 24 отсека для SFF-накопителей SAS/SATA/NVME с поддержкой горячей замены. Доступны два слота PCIe 5.0 x16 и четыре слота PCIe 5.0 x8 для карт полной высоты, а также два разъёма OCP 3.0 (PCIe 5.0 x8). Предусмотрены выделенный сетевой порт управления 1GbE (RJ45), последовательный порт, разъёмы USB 3.0 и D-Sub. Установлены два блока питания мощностью 1300 Вт с сертификатом 80 Plus Platinum. Вариант Inferit GR2X2G4V1-D24 имеет аналогичные технические характеристики, но оснащается двумя ИИ-ускорителями на базе GPU суммарной мощностью до 600 Вт. Система ориентирована на развёртывание языковых моделей, обучение ИИ, 3D-визуализацию и 3D-рендеринг, работу с большими данными, комплексные научные вычисления, виртуализацию и облачные сервисы. Задействованы два блока питания на 2000 Вт с сертификатом 80 Plus Platinum. Сервер Inferit UR2X2G4V1-D12, в свою очередь, подходит для комплексных вычислений, виртуализации и облачных сервисов. Он оборудован 12 лицевыми отсеками для LFF/SFF-накопителей SAS/SATA/NVMe с поддержкой горячей замены. Прочие характеристики аналогичны версии Inferit UR2X2G4V1-D24. Наконец, модификация Inferit GR2X2G4V1-D12 схожа с версией GR2X2G4V1-D24, но при этом оснащена 12 посадочными местами для накопителей LFF/SFF. На все серверы опционально предустанавливается фирменная ОС «МСВСфера». Базовая гарантия составляет три года с возможностью продления до пяти лет. «Мы укрепляем свои позиции на рынке ИТ, развивая линейки собственных продуктов для бизнеса и госсектора. Новая серия серверов — это топовое решение в нашей продуктовой линейке для крупного бизнеса, науки и госучреждений. Конструируя их, мы ориентировались не только на производительность — надёжность, масштабируемость и минимум отказов были не меньшими приоритетами», — говорит «Инферит Техника».

26.09.2025 [09:53], Сергей Карасёв

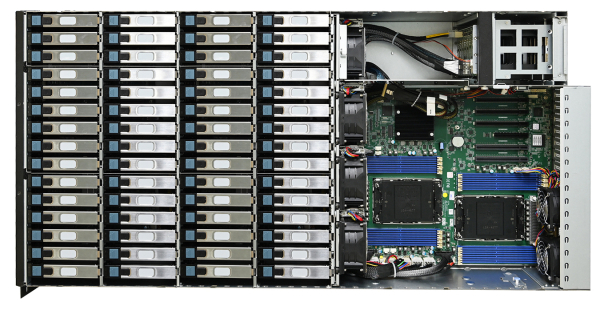

Сервер хранения AIC SB407-VA допускает установку 60 накопителей LFF SATA/SASКомпания AIC представила сервер хранения данных SB407-VA, выполненный в форм-факторе 4U на аппаратной платформе Intel. Новинка допускает установку в общей сложности 70 накопителей разных типов, что позволяет сформировать массив большой ёмкости для таких задач, как аналитика данных, периферийные ИИ-приложения и пр. Сервер может комплектоваться двумя процессорами Xeon Sapphire Rapids или Emerald Rapids. Доступны 16 слотов для модулей DDR5-5600/4800 суммарным объёмом до 4 Тбайт (3DS RDIMM). Предусмотрены четыре слота расширения PCIe x16 и один разъём PCIe x8: во всех случаях могут монтироваться карты формата FHHL. Предусмотрены посадочные места для 60 накопителей LFF с интерфейсом SATA/SAS и возможностью горячей замены. Кроме того, могут быть установлены восемь SFF-устройств в конфигурации 6 × NMVe (PCIe 4.0) и 2 × SATA с поддержкой горячей замены. Плюс к этому есть два коннектора M.2 M Key 2280 для SSD с интерфейсом PCIe 4.0. Модель AIC SB407-VA наделена контроллером Aspeed AST2600. Реализованы два сетевых порта 1GbE на базе Broadcom BCM5720 и выделенный сетевой порт управления 1GbE на основе Realtek RTL8211FS. Во фронтальной части расположен один порт USB3.0 Type-A, в тыльной — три гнезда RJ45 для сетевых кабелей, два разъёма USB 3.1 Gen1 Type-A и коннектор D-Sub. Габариты составляют 434 × 853 × 176 мм. Питание обеспечивают четыре блока мощностью 800 Вт с сертификатом 80 Plus Platinum/Titanium. Задействовано воздушное охлаждение, а диапазон рабочих температур простирается от 0 до +35 °C.

03.09.2025 [17:22], Сергей Карасёв

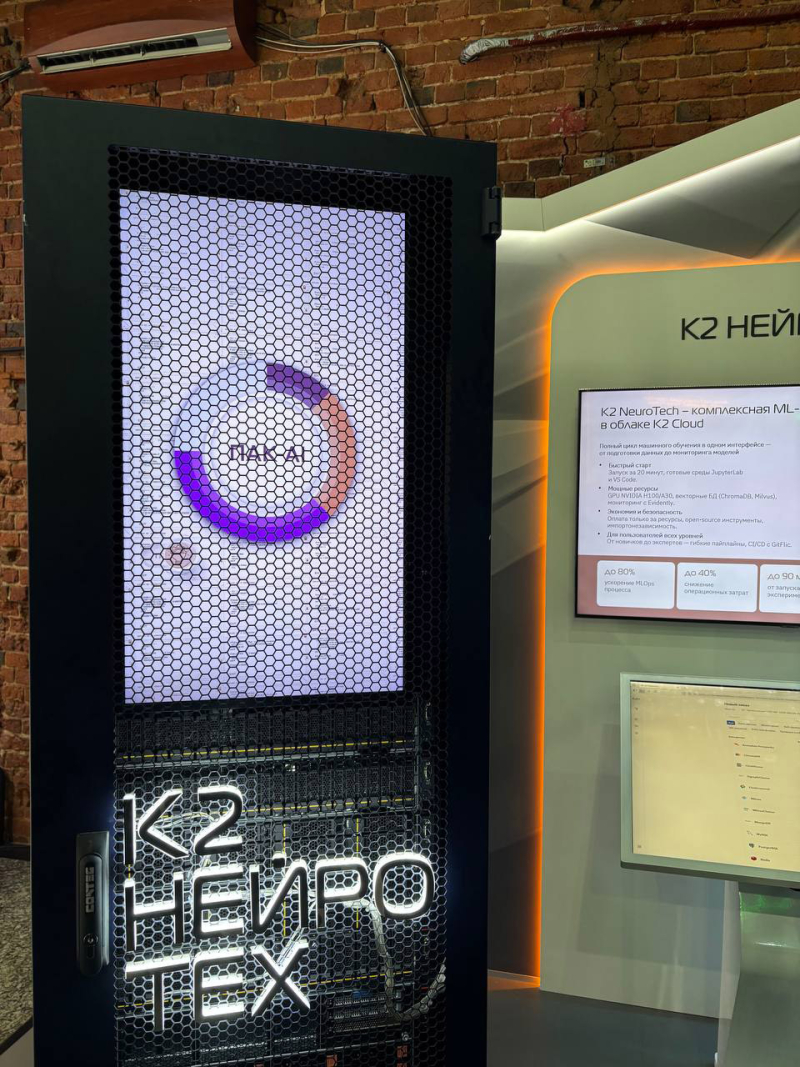

«К2 НейроТех» представил ПАК-AI 2.0 с увеличенной на 30 % производительностью

emerald rapids

gpu

hardware

intel

sapphire rapids

xeon

yadro

ии

к2тех

россия

сделано в россии

сервер

Компания «К2 НейроТех», подразделение компании «К2Тех», анонсировала программно-аппаратный комплекс ПАК-AI 2.0, предназначенный для построения локальной ИИ-инфраструктуры. Утверждается, что по сравнению с оригинальной версией платформы, дебютировавшей в июне нынешнего года, производительность поднялась на 30 %. ПАК объединяют аппаратный слой, платформу управления, преднастроенное ПО и инструменты для работы с ИИ. Решение может быть кастомизировано под конкретные задачи заказчика. Количество серверных стоек масштабируется для обеспечения необходимой производительности. Реализован встроенный маркетплейс приложений, через который в числе прочего доступна платформа Yandex Cloud AI Studio для создания приложений на базе ИИ. Обновленная аппаратная платформа ПАК-AI 2.0 включает шесть серверов YADRO, в том числе серверы для глубокого обучения, инференса и работы с большими данными, а также новый GPU-сервер G4208P G3. Последний специально разработан для обучения нейросетей, обработки больших объемов данных и построения распределённых ИИ-кластеров. Этот сервер несёт на борту два процессора Intel Xeon Sapphire Rapids или Emerald Rapids с TDP до 350 Вт. Поддерживается до 8 Тбайт DDR5. Возможна установка до восьми GPU двойной ширины (PCIe 5.0 x16) с энергопотреблением до 450 Вт каждый. Помимо улучшенной аппаратной части, ПАК-AI 2.0 получил доработанную сборку Kubernetes, которая предоставляет в режиме самообслуживания работу с различными ускорителями (в том числе PCIe, SXM) в формате GPU, vGPU MIG и увеличивает производительность GPU до 30 %. Благодаря этому, как утверждается, повышается эффективность запуска моделей машинного обучения и снижаются эксплуатационные расходы. «К2 НейроТех» заявляет, что ПАК позволяет в короткие сроки развернуть IT-инфраструктуру, которая максимально раскрывает потенциал ИИ, обеспечивает высокий уровень безопасности и соответствие регламентам ИБ, а также прозрачное управление данными. Благодаря наличию LLM-моделей и агентов, предварительно настроенных для выполнения бизнес-задач, ускоряется вывод продуктов на рынок.

08.07.2025 [17:09], Владимир Мироненко

Российский суперкомпьютер «Говорун» получил два узла «РСК Экзастрим ИИ» с NVIDIA H100 и фирменной СЖО

emerald rapids

h100

h200

hpc

intel

nvidia

sapphire rapids

xeon

россия

рск

сделано в россии

сервер

суперкомпьютер

ГК РСК продемонстрировала 2U-узел (912 × 508 × 88 мм) собственной разработки «РСК Экзастрим ИИ» на базе восьми ускорителей NVIDIA H100 с прямым жидкостным охлаждением. Два таких узла были установлены в суперкомпьютере «Говорун» в Дубне. «РСК Экзастрим ИИ» включает:

«РСК Экзастрим ИИ» имеет локальную подсистему хранения «тёплых данных», сетевую подсистему с доступом на основе технологии GPUDirect. Также есть возможность расширения ресурсов путём подключения дополнительных пар ускорителей или системы внешнего хранения данных на базе пула JBOF, подключаемой напрямую. Производительность «РСК Экзастрим ИИ» составляет до 208 Тфлопс (FP64). При установке 21 сервера в шкаф «РСК Экзастрим» пиковая производительность достигает 4,26 Пфлопс (FP64). Сервер отличается высокой энергоэффективностью, сверхвысокой плотностью монтажа и надёжной работой. Он может использоваться для решения ресурсоёмких задач в области машинного обучения и ИИ, создания мощных вычислительных ресурсов облачных провайдеров и в частных облаках и т.д.

Источник изображений: РСК Два узла «РСК Экзастрим ИИ» были установлены в суперкомпьютере «Говорун» в Лаборатории информационных технологий им М.Г. Мещерякова Объединенного института ядерных исследований (ЛИТ ОИЯИ) в Дубне в рамках нового этапа модернизации, проведенной силами специалистов ГК РСК и лаборатории. Как сообщается, новые серверы «РСК Экзастрим ИИ» уникальны и были сконструированы и изготовлены для СК «Говорун» с учётом его архитектурных особенностей. При этом пиковая FP64-производительность GPU-компоненты суперкомпьютера «Говорун» выросла на 36 % и достигла 1,4 Пфлопс, пиковая суммарная FP64-производительность суперкомпьютера теперь составляет 2,2 Пфлопс. Характеристики серверов «РСК Экзастрим ИИ», установленных в ОИЯИ:

В конце 2024 года было проведено расширение СХД суперкомпьютера «Говорун», после чего её ёмкость увеличилась до 10 Пбайт. В СХД вычислительного комплекса ОИЯИ были добавлены два узла хранения данных RSC Tornado AFS ёмкостью 1 Пбайт каждый. Обновленная модификация СХД RSC Tornado AFS включает серверную плату на базе процессоров Intel Xeon Sapphire Rapids, а также коммутатор с интерфейсом PCIe 4.0, что позволило установить по два адаптера интерконнекта с пропускной способностью 200 Гбит/с каждый.  СХД RSC Tornado AFS поддерживает технологию GPUDirect Storage (GDS), которая обеспечивает прямую передачу данных между локальным или удалённым хранилищем и памятью ускорителя. Две СХД, установленные ранее специалистами РСК в суперкомпьютере «Говорун» входят в мировой рейтинг IO500 самых высокопроизводительных системам хранения данных. В суперкомпьютере «Говорун» используются интегрированный программный комплекс «РСК БазИС 4» и модуль «РСК БазИС СХД» (включены в Реестр российского ПО). Микроагентная архитектура «РСК БазИС 4» обеспечивает функционирование объектов системы, позволяя также взаимодействовать с ними. «РСК БазИС» в сочетании с аппаратными платформами РСК позволяет создавать гиперконвергентные решения для HPC и эффективной обработки больших объёмов данных.

29.06.2025 [21:11], Сергей Карасёв

Таёжное облако: ИИ-кластер Northern Data Njoerd вошёл в рейтинг TOP500

h100

hardware

hpc

hpe

intel

northern data

nvidia

sapphire rapids

xeon

великобритания

ии

облако

суперкомпьютер

Немецкая компания Northern Data Group, поставщик решений в области ИИ и НРС, объявила о том, что её система Njoerd вошла в июньский рейтинг мощнейших суперкомпьютеров мира TOP500. Этот вычислительный комплекс, расположенный в Великобритании, построен на платформе HPE Cray XD670. Машина Njoerd попала на 26-е место списка TOP500. Она объединяет 244 узла, каждый из которых содержит восемь ускорителей NVIDIA H100. В общей сложности задействованы примерно 28,5 млн ядер CUDA. Кроме того, в составе системы используются процессоры Intel Xeon Platinum 8462Y+ (32C/64C, 2,8–4,1 ГГц, 300 Вт). Применён интерконнект Infiniband NDR400. FP64-производительность Njoerd достигает 78,2 Пфлопс, а теоретическое пиковое быстродействие составляет 106,28 Пфлопс. При рабочих нагрузках ИИ суперкомпьютер демонстрирует производительность 3,86 Эфлопс в режиме FP8 и 1,93 Эфлопс в режиме FP16. Заявленный показатель MFU (Model FLOPs Utilization) при предварительном обучении современных больших языковых моделей (LLM) находится на уровне 50–60 %. Таким образом, как утверждается, система Njoerd на сегодняшний день представляет собой наиболее эффективный кластер H100 подобного размера, оптимизированный для ресурсоёмких рабочих нагрузок ИИ и HPC. Суперкомпьютер входит в состав Taiga Cloud — одной из крупнейших в Европе облачных платформ, ориентированных на задачи генеративного ИИ. Эта вычислительная инфраструктура использует на 100 % безуглеродную энергию. Показатель PUE варьируется от 1,15 до 1,06. Доступ к ресурсам предоставляется посредством API или через портал самообслуживания. Одним из преимуществ Taiga Cloud компания Northern Data Group называет суверенитет данных.

Источник изображения: Northern Data Group |

|