Материалы по тегу: fpga

|

20.10.2024 [20:39], Владимир Мироненко

Intel разослала предложения по продаже своей доли в AlteraIntel намерена продать по крайней мере миноритарную долю в своем подразделении Altera (ранее PSG), специализирующемся на разработке ПЛИС, чтобы получить несколько миллиардов долларов для укрепления пошатнувшегося финансового положения, сообщил CNBC со ссылкой на информированные источники. Крупнейшим конкурентом Altera, как и крупнейшим производителем FPGA является AMD, которая вышла на этот рынок в 2022 году благодаря приобретению Xilinx за $49 млрд. По словам источников ресурса, на минувшей неделе компания обратилась к ряду частных и стратегических инвесторов с предложением о продаже доли в Altera. Некоторым из них она сообщила о готовности продать контрольный пакет акций. В предлагаемой сделке Intel исходит из рыночной стоимости Altera в $17 млрд, что ненамного больше $16,7 млрд, уплаченных за неё в 2015 году.

Источник изображения: Intel Сообщение CNBC подтверждает сделанное ранее заявление гендиректора Altera Сандры Ривера (Sandra Rivera) о том, что компания продолжает следовать плану, объявленному более года назад. План предусматривает продажу доли в компании и проведение IPO в 2026 году. Ривера заявила об этом после появления сообщений о том, что Intel может продать Altera полностью, возможность чего она исключает.

20.10.2024 [11:09], Сергей Карасёв

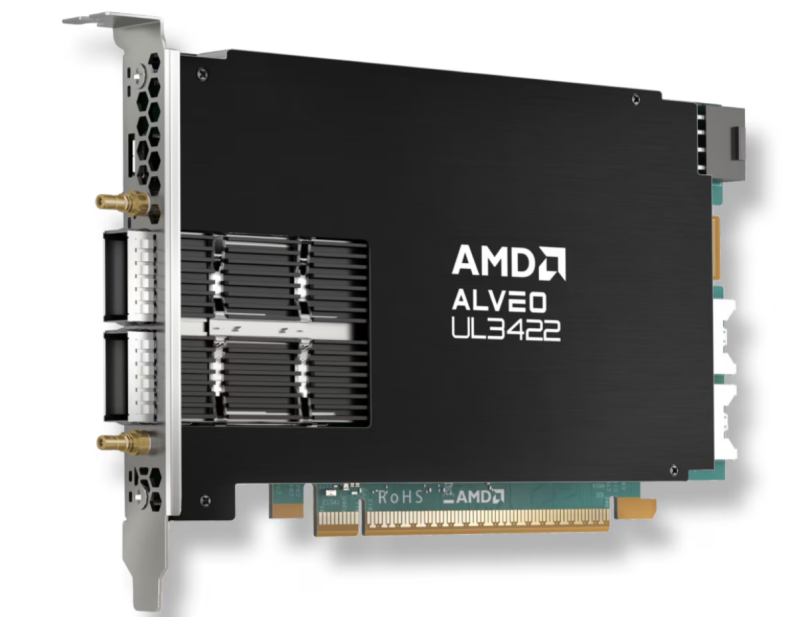

AMD выпустила ускоритель для трейдеров Alveo UL3422 на базе FPGA Virtex UltraScale+ VU2PКомпания AMD анонсировала изделие Alveo UL3422: это, как утверждается, самый быстрый в мире однослотовый ускоритель половинной длины (FHHL) для брокерских и биржевых приложений. Новинка уже поставляется заказчикам из финансового сектора по всему миру. В устройстве применена FPGA Virtex UltraScale+ VU2P. Конфигурация включает 32 трансивера с ультранизкой задержкой, 787 тыс. LUT и 1680 DSP. В состав FPGA входят 256 Мбайт встроенной памяти — 76 Мбайт блочной RAM и 180 Мбайт UltraRAM. Заявленная задержка на уровне трансиверов составляет менее 3 нс. Карта использует интерфейс PCIe 4.0 x8 (коннектор x16). Заявленный показатель TDP равен 120 Вт; используется пассивное охлаждение. В оснащение входят 16 Гбайт памяти DDR4-2400. Предусмотрены два разъёма QSFP-DD (16×10/25G) и два коннектора ARF6. Ускоритель Alveo UL3422 может использоваться в комплексе с платформой разработки Vivado Design Suite. AMD также предоставляет клиентам среду разработки FINN с открытым исходным кодом и поддержкой сообщества, что позволяет интегрировать модели ИИ с низкими задержками в высокопроизводительные торговые системы. FINN использует PyTorch и методы квантования нейронных сетей. Ускоритель поставляется с набором референсных проектов и тестов производительности. Среди ключевых сфер применения новинки названы торговые операции со сверхнизкими задержками и анализ рисков.

24.09.2024 [20:05], Владимир Мироненко

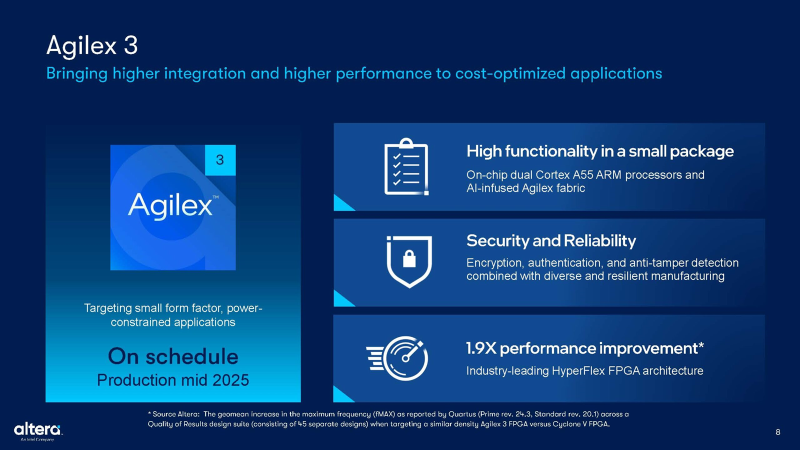

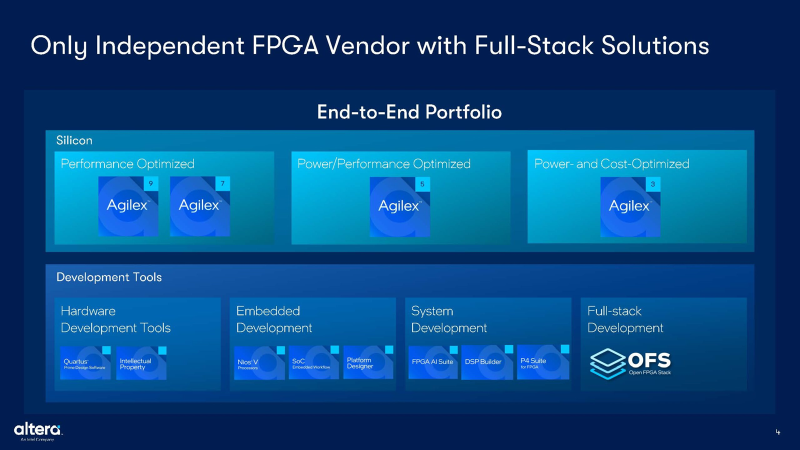

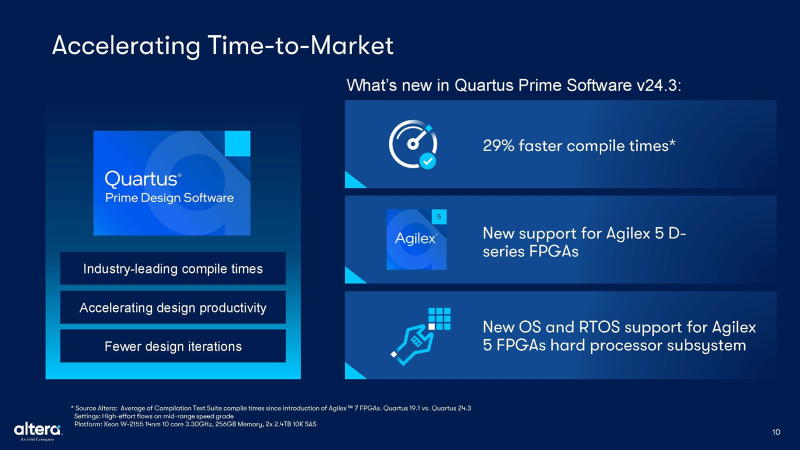

Altera поделилась подробностями об FPGA Agilex 3 и анонсировала предстоящий релиз Quartus Prime ProКомпания Altera, созданная на базе выделенной из Intel группы программируемых решений (PSG), поделилась на ежегодной конференции для разработчиков Altera Innovators Day новыми подробностями о следующем поколении оптимизированных по энергопотреблению и стоимости чипов Agilex 3, а также анонсировала новые комплекты разработки и поддержку ПО для FPGA Agilex 5. Altera сообщила, что новые FPGA Agilex отличается от предыдущего поколения более высоким уровнем интеграции, повышенной безопасностью и более высокой производительностью, объединяя эти качества в компактном корпусе с плотностью от 25 тыс. до 135 тыс. логических элементов. Наряду с ПЛИС, наделённой возможностями ИИ, семейство Agilex 3 содержит пару Arm-ядер Cortex-A55. FPGA серии Agilex 3 ориентированы на системы, в которых энергоэффективность важнее производительности. Intel полагает, что эти чипы найдут применение в таких продуктах, как подключённые устройства, промышленные роботы и автономные транспортные средства. Для интеллектуальных периферийных приложений именно FPGA обеспечивают вычисления в реальном времени для чувствительных ко времени приложений. А для интеллектуальных технологий автоматизации производства Agilex 3 предложат бесшовную интеграцию датчиков, драйверов, актуаторов и алгоритмов машинного обучения. Agilex 3 используют архитектуру HyperFlex и имеют в 1,9 раза более высокую производительность по сравнению с предыдущим поколением, говорит Altera. Рост производительности достигнут за счёт интегрированных высокоскоростных трансиверов (до 12,5 Гбит/с) и поддержки экономичной памяти LPDDR4. Для удовлетворения потребности как оборонных систем, так и коммерческих проектов в области безопасности, в Agilex 3 добавлено шифрование потоков данных, аутентификация и функция обнаружения физического несанкционированного доступа. Компания сообщила, что ПО для Agilex 3 FPGA выйдет в I квартале 2025 года, а поставки комплектов разработчика и самого продукта, как ожидается, начнутся в середине 2025 года. Altera также анонсировала предстоящий выпуск ПО Quartus Prime Pro 24.3 для современных ПЛИС Agilex и расширенную поддержку встраиваемых решений. Речь как об аппаратных блоках, так и, например, о программном RISC-V ядре Nios V. Кроме того, объявлено о поддержке Agilex 5 SoC в Linux, VxWorks и Zephyr. Клиенты смогут использовать Quartus Prime Pro 24.3 для серии Agilex 5 D, которая нацелена на более широкий спектр вариантов использования по сравнению с Agilex 5 E, оптимизированной для обеспечения эффективных вычислений на периферии. При этом для Agilex 5 E-серии доступна бесплатная лицензия ПО Quartus Prime, что снизит барьер для входа при работе с FPGA Altera среднего уровня. Также отмечена выросшая почти на треть скорость компиляции. Наконец, Altera и её партнеры по экосистеме объявили о выпуске 11 новых комплектов разработчика на основе Agilex 5 и SoM. В дальнейшем Altera сосредоточится именно на работе с партнёрами, а сама заниматься созданием плат и решений вряд ли будет.

14.09.2024 [00:42], Владимир Мироненко

Altera не будут продавать — лишь долю в бизнесе, как и планировалосьСандра Ривера (Sandra Rivera), гендиректор компании Altera, созданной на базе выделенной из Intel группы программируемых решений (PSG), опровергла сообщения о планах чипмейкера по продаже Altera с целью получения средств для выхода из кризисного положения. В интервью ресурсу CRN Ривера заявила, что для компании ничего не изменилась, и предприятие по-прежнему следует плану, который был объявлен более года назад. Он предполагает продажу доли в бизнесе, а не всей компании целиком, и проведение IPO в 2026 году. Напомним, что на прошлой неделе агентство Reuters сообщило со ссылкой на неназванные источники, что Intel планирует вынести на рассмотрение совета директоров на заседании в середине сентября потенциальную продажу предприятий, не являющихся ключевыми для её стратегии, в том числе Altera. Altera с начала 2024 года работает независимо от Intel, но процесс разделения бизнеса с материнской компанией всё ещё не завершён, хотя и «фактически опережает график». По словам Риверы, крайний срок завершения разделения структур и функций двух компаний — 1 января 2025 года. В настоящее время ведётся подготовка к продаже доли компании, проводятся встречи с банками, а также выполняется необходимая для этого работа, говорит Ривера. «И команда очень, очень сосредоточена на нашей долгосрочной цели, нашей конечной цели — стать номером один в отрасли. И IPO — это важная и волнующая веха на этом пути», — заявила она. Intel приобрела компанию Altera в 2015 году за $16,7 млрд. В октябре прошлого года Intel объявила о предстоящем выделении с 1 января 2024 года группы программируемых решений (PSG) в отдельную бизнес-структуру, а в феврале 2024 анонсировала возрождение независимого бренда Altera.

20.05.2024 [19:32], Александр Бенедичук

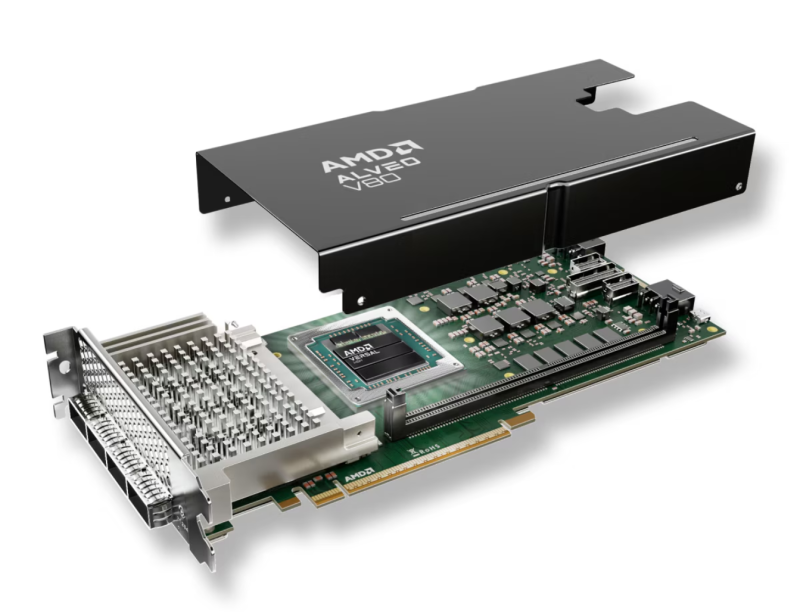

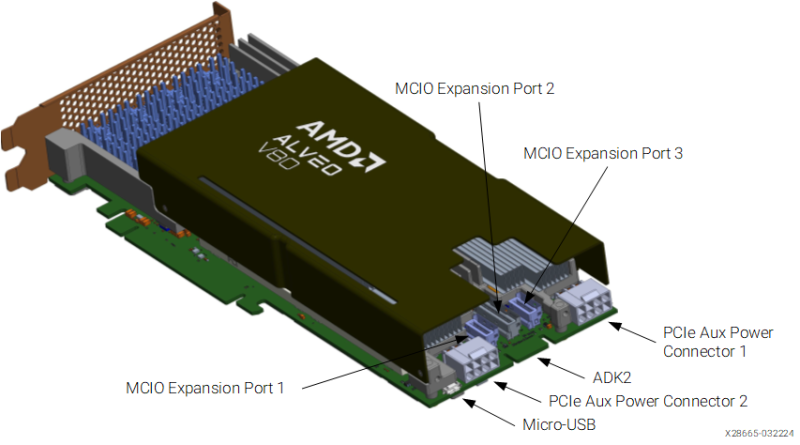

FPGA с HBM2e: AMD без лишнего шума выпустила ускоритель Alveo V80 стоимостью всего $9,5 тыс.AMD начала массовое производство ускорителя Alveo V80 стоимостью $9,5 тыс., передаёт Wccftech. Новинка на базе SoC Versal HBM предназначена для рабочих нагрузок среднего уровня, существенно зависящих от пропускной способности памяти (ПСП), и, как ожидается, получит широкое распространение в области HPC, сетей и СХД. Alveo V80 базируется на гибридной 7-нм SoC Versal XCV80 HBM и включает 32 Гбайт HBM2e-памяти с ПСП 820 Гбайт/с. FPGA предлагает 10 848 DSP, 2,6 млн LUT, 132 Мбит BRAM и 541 Мбит UltraRAM. Также есть два ядра общего назначения Arm Cortex-A72, дополненных 4 или 8 Гбайт DDR4-3200 ECC, и пара ядер Arm Cortex-R5F. На плате есть DIMM-слот для установки 32 Гбайт DDR4-памяти. Ускоритель обладает развитой сетевой подсистемой, которая включает три криптодвижка класса 400G, шесть 100G Ethernet MAC, три 600G Ethernet MAC и один 600G-интерфейс Interlaken для межчипового взаимодействия. Впрочем, на самой карте есть только четыре порта QSFP56, работающих либо в режиме 2 × 100GbE, либо 4 × 10/25/40/50GbE. Сама карта имеет интерфейс PCIe 4.0 x16, который также может быть сконфигурирован как два PCIe 5.0 x8. В задней части есть пара коннекторов MCIO x4 и один MCIO x8. Ускоритель выполнен в виде двухслотовой карты с пассивным охлаждением и имеет TDP до 190 Вт. При этом у него есть сразу два восьмиконтактных гнезда для дополнительного питания. По словам компании, Alveo V80 является своего рода наследницей Alveo U55C и в 2–4 раза лучше её по ряду параметров.

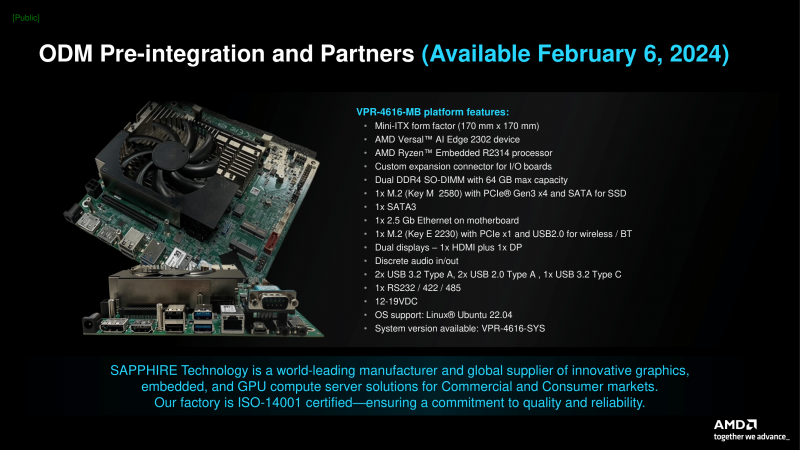

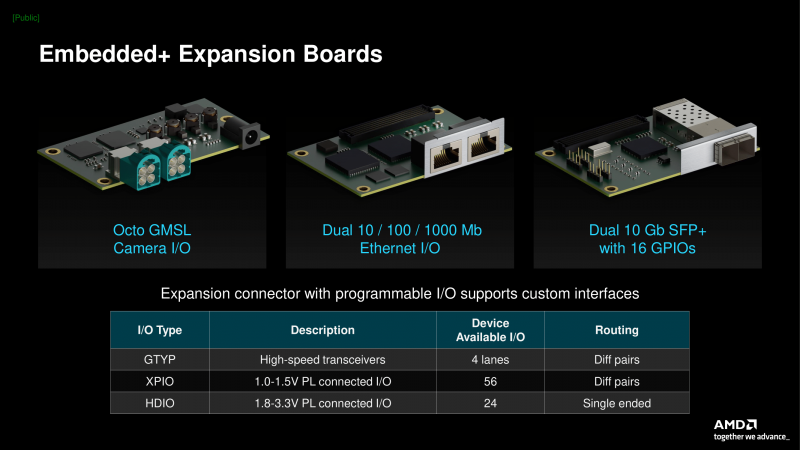

07.02.2024 [20:00], Алексей Степин

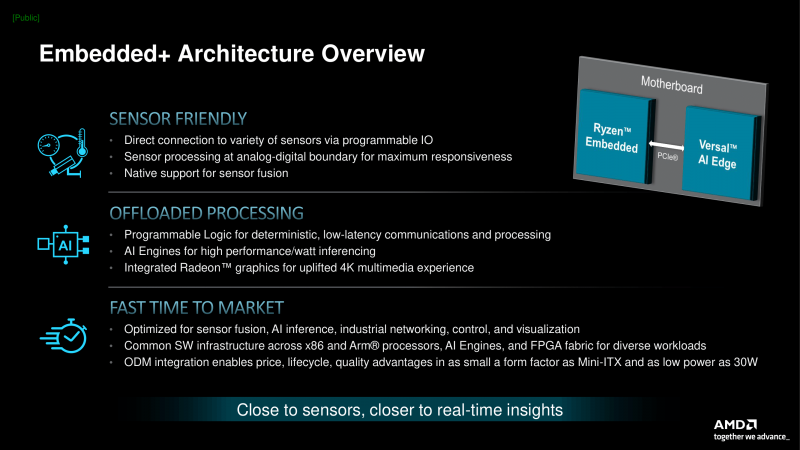

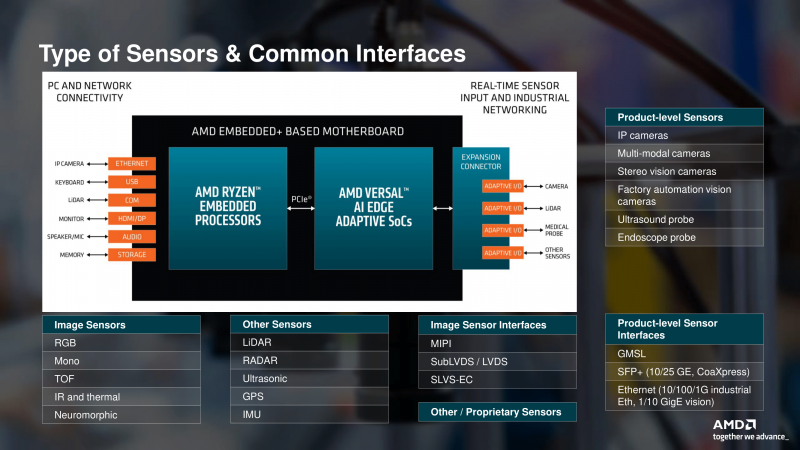

Ryzen + Versal: AMD представила платформу Embedded+Как правило, основное внимание AMD привлекает своими процессорами с архитектурой x86, будь то Ryzen или EPYC. Тем не менее, другие направления, такие как встраиваемые платформы или решения для периферийных вычислений, для компании также играют важную роль. Вчера AMD анонсировала новую платформу Embedded+, главной особенностью которой является сочетание хорошо знакомой и отлично себя зарекомендовавшей архитектуры Zen+ с наработками бывшей Xilinx в лице SoC Versal AI Edge. В данном случае речь идёт об использовании соответствующих чипов в рамках одной системной платы, представляющей собой практически законченное изделие, предназначенное для использования в сценариях, требующих низкого энергопотребления при достаточно серьёзных вычислительных возможностях, особенно в традиционных для ИИ форматах. Сфера применения такого решения крайне широка и включает в себя любые задачи, требующие обработки массивов данных, поступающих в реальном времени с различных сенсорных систем и датчиков. Это могут быть как медицинские устройства, так и решения «умной промышленности» или автономный транспорт. Во всех упомянутых случаях требуется низкая латентность, и платформа AMD Embedded+ соответствует подобного рода требованиям. Также она является поистине универсальной, поскольку несёт в своём составе как x86-ядра процессора Ryzen Embedded, так и ядра Arm в составе чипа Versal, а для уникальных задач можно использовать программируемую FPGA-логику. Новую платформу характеризует широкий спектр поддерживаемых интерфейсов ввода-вывода, начиная со стандартных Ethernet, USB и HDMI/Display Port, заканчивая интерфейсами различных сенсоров, такими, как MIPI и LVDS, а также GMSL. Речь идёт не только о сенсорах машинного зрения, но и о различных радарах, лидарах, ультразвуковых датчиках, приёмниках GPS и тому подобных устройствах. Одновременно с анонсом самой платформы AMD представила готовое решение на её основе — плату Sapphire VPR-4616-MB. Решение имеет форм-фактор mini-ITX и несёт на борту Ryzen Embedded R2314 и Versal AI Edge 2302. Первый имеет конфигурацию с четырьмя x86-ядрами и шестью блоками Radeon Vega. В составе второго имеется по паре ядер Arm Cortex-A72 и Cortex-R5F, последние предназначены для работы в режиме реального времени. Программируемая часть содержит 329 тысяч логических ячеек и свыше 150 тысяч LUT. Чип способен развивать до 23 Топс на операциях в формате INT8 за счёт 34 собственных движков ИИ, ещё 5 Топс может выдать программируемая логика. 464 движка DSP делают данное решение хорошо подходящим для реализации машинного зрения, в том числе в системах автопилота. Плата имеет специальный разъём расширения, к нему подключаются различные модули с интерфейсами машинного зрения, Ethernet и GPIO. Объём оперативной памяти, которым можно укомплектовать решение, достигает 64 Гбайт, доступна установка накопителя M.2 и SATA, имеется отдельный слот M.2 2230 для реализации беспроводной связи.

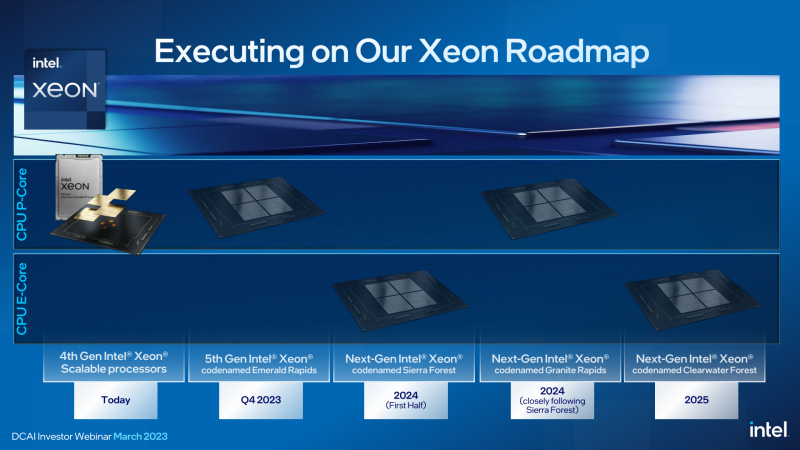

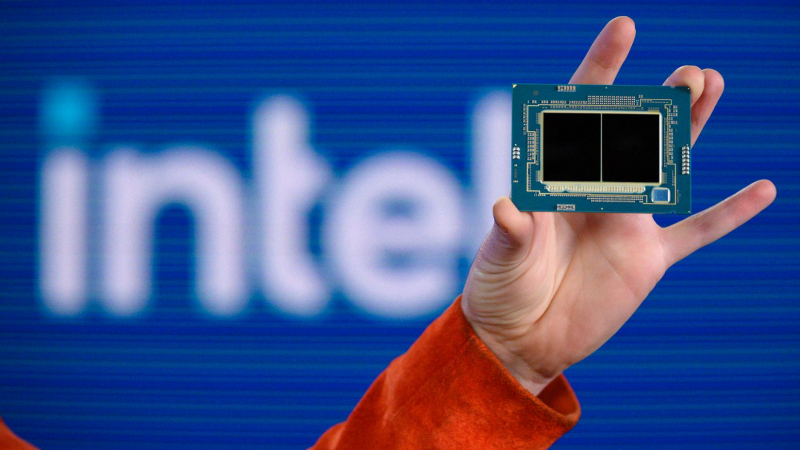

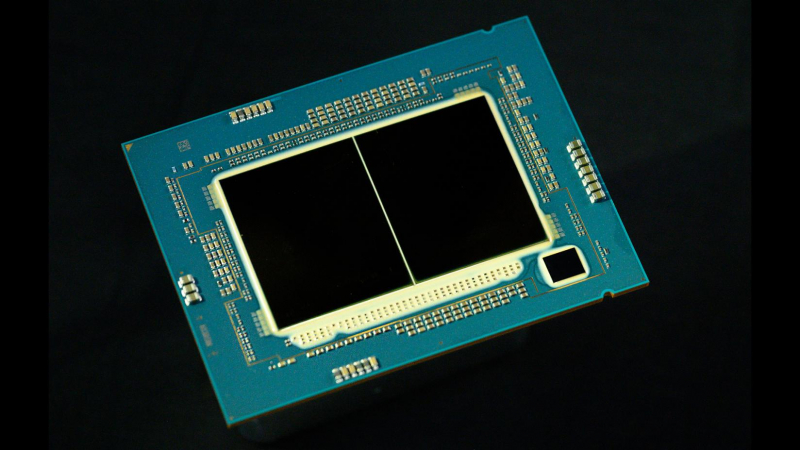

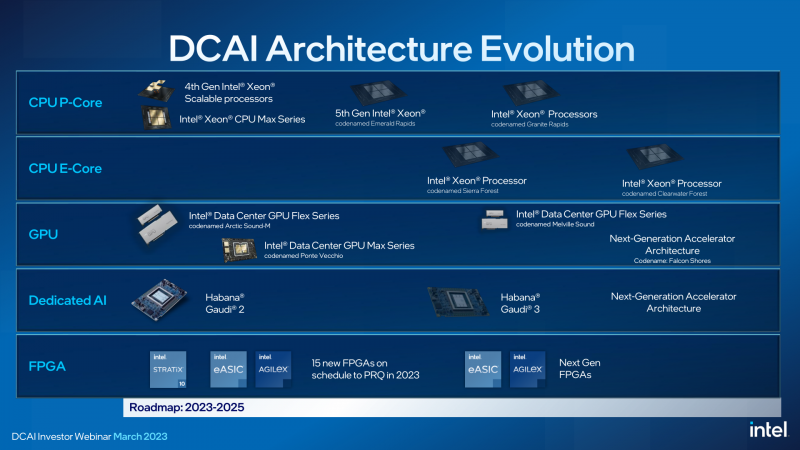

30.03.2023 [19:45], Владимир Мироненко

В 2023 году Intel выпустит Xeon Emerald Rapids и подготовит полтора десятка FPGA, а чипы Sierra Forest и Granite Rapids появятся уже в 2024 годуВ ходе мероприятия для инвесторов Intel подтвердила свои планы по противодействию процессорам AMD EPYC Bergamo, в которых будет использоваться архитектура с высокой плотностью ядер Zen4c, а также всё нарастающему давлению Arm. Intel придерживается планов по созданию собственных архитектур с производительными и энергоэффективными ядрами для чипов Xeon. Intel объявила, что рассчитывает выпустить следующее, пятое по счёту поколение процессоров Xeon Scalable под кодовым названием Emerald Rapids (EMR), преемников Sapphire Rapids (SPR), в IV квартале 2023 года. Компания также продемонстрировала чип Emeralds Rapids, состоящий из двух чиплетов (тайлов в терминологии Intel). Sapphire Rapids, напомним, имеется четыре тайла меньших размеров. Сообщается, что образцы Emerald Rapids уже доступны избранным заказчикам. Не вдаваясь особо в технические подробности, компания рассказала, что Emerald Rapids будет работать в том же диапазоне TDP, что и Sapphire Rapids, что повысит общую производительность платформы в пересчёте на Вт. Учитывая то, что Emerald Rapids будет использовать ту же платформу LGA 4677, что и Sapphire, заказчики смогут заменить Sapphire на Emerald в существующих решениях. Такой подход позволит легко модернизировать уже внедрённые системы, а в случае производителей оборудования — ускорить вывод Emerald Rapids на рынок. Emerald Rapids будет построен на том же техпроцессе Intel 7. Это означает, что прирост производительности должен быть обеспечен за счёт архитектурных улучшений. Intel сообщила о «повышенной плотности ядер», поэтому можно предположить, что у Emerald Rapids будет больше ядер в сравнении с Sapphire Rapids. Вслед за Emerald Rapids компания планирует начать в 2024 году поставки чипов следующего поколения Granite Rapids (GNR) на базе производительных P-ядер. Сообщается, что вычислительные тайлы Granite Rapids будут выпускаться с использованием техпроцесса Intel 3. Intel также впервые сообщила, что Granite Rapids будут поддерживать MCR DIMM (DDR5-8800+) и обеспечат ПСП в пределах 1,5 Тбайт/с (12 каналов памяти). Ещё одной особенностью станет полный переход на чиплетную компоновоку с независимым IO-тайлом. Первые образцы Granite Rapids уже тестируются некоторыми заказчиками. В первой половине 2024 года должен выйти и процессор Sierra Forest (SRF), первый Intel Xeon с энергоэффективными E-ядрами (следующее за Gracemont поколение) общим числом до 144 единиц. Сообщается, что Sierra Forest и Granite Rapids будут использовать одну и ту же платформу Birch Stream. Следует отметить, что чипы Sierra Forest появятся несколько раньше, чем Granite Rapids, и тоже будут использовать техпроцесс Intel 3, а также IO-тайлы. Отмечается, что Sierra Forest даже в текущем виде оказались на удивление стабильно работающими. Более того, их уже тестирует как минимум один заказчик Intel. На смену Sierra Forest придут в 2025 году чипы Clearwater Forest (CWF), которые станут первыми в семействе Intel Xeon, основанными на техпроцессе Intel 18A. По словам Intel, её заказчики не хотят серверные процессоры смешанной архитектуры, то есть требуют чипы либо только с P-ядрами, либо только с E-ядрами. Sierra Forest сейчас является, пожалуй, наиболее важным продуктом для Intel и для демонстрации производственных возможностей, и для сохранения заказчиков среди гиперскейлеров. Что касается ускорителей, то компания в этом году планирует подготовить сразу 15 различных FPGA в сериях Agilex и Stratix, а также eASIC. Intel, как уже говорилось ранее, не забрасывает работу над специализированными ускорителями Habana, но грядущие Gaudi3 от нынешних Gaudi2 будут отличаться переходом с 7-нм на 5-нм техпроцесс. Отменённых Rialto Bridge в планах более нет, да и Falcon Shores тоже не упоминаются. При этом Intel считает, что к 2027 году в области ИИ-чипов соотношение между CPU и GPU будет на уровне 60/40.

28.07.2021 [15:27], Алексей Степин

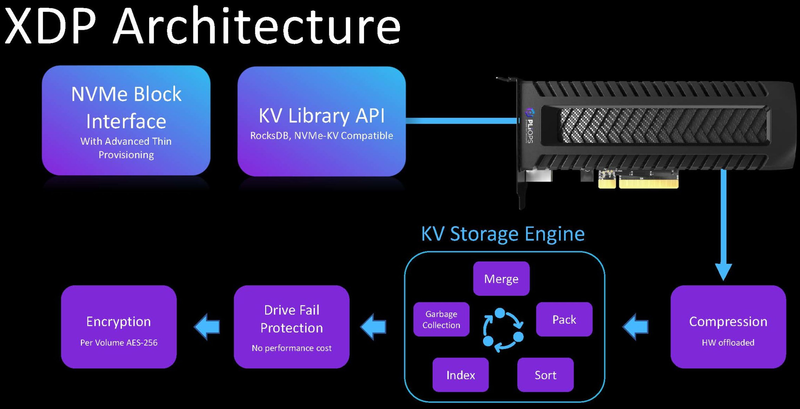

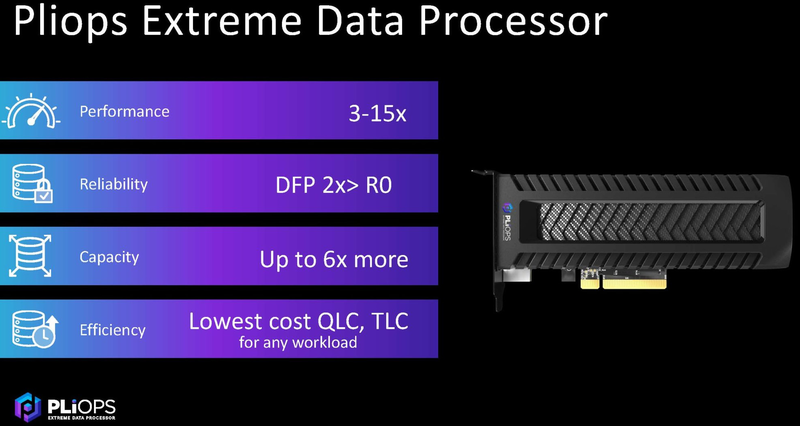

Pliops анонсировала высокопроизводительный DPU XDP ExtremeКонцепция сопроцессора данных (DPU) продолжает набирать популярность — анонсы новых решений в этой области следуют один за другим. Компания Pliops, ранее представившая ускоритель для СУБД, представила свой новый продукт — XDP Extreme, который имеет более широкую сферу применения и предназначен для разгрузки процессоров современных систем хранения данных, целиком построенных на энергонезависимой памяти. Внешне новинка выглядит как обычная плата расширения с разъёмом PCIe x8, в основе лежит мощная ПЛИС производства Xilinx. В будущем компания планирует заменить её на более экономичный ASIC-вариант. У XDP Extreme нет сетевых портов, вместо этого разработчики сконцентрировали свои усилия на ускорении общих для СХД задач и повышении эффективности использования пула флеш-памяти.  XDP использует так называемый KV Storage Engine — движок, работающий с Key-Value данными. За счёт фирменного API обеспечена совместимость со всеми приложениями, которые используют KV-подход. Уровнем ниже всё так же находится NVMe, как протокол, наиболее отвечающий устройствам на базе флеш-памяти. KV Storage Engine берёт на себя всю обработку ключей БД, включая их сортировку, индексацию и сборку мусора, а значит, этим не придётся заниматься центральным процессорам системы. Также ускоритель обеспечивает разгрузку ЦП при сжатии, отвечает за защиту от сбоев SSD и выполняет шифрование томов с использованием AES-256.  Востребованность XDP высока: KV-движки сегодня используются в подавляющем большинстве баз данных, также они применяются в комплексах машинной аналитики на базе Elastic или Hadoop и в распределённых файловых системах. Эффективность XDP Extreme, если верить данным Pliops, внушает уважение: даже на операциях чтения можно добиться двухкратного прироста линейной производительности, а выигрыш при записи может составлять и три-четыре раза. Более того, флеш-массив под управлением XDP оказывается быстрее, нежели классический RAID0. А снижение коэффициента усиления записи (write amplification) позволяет использовать недорогую, но априори менее надёжную память QLC. Впрочем, с Optane новый DPU тоже прекрасно работает.  Фактически, компания говорит о производительности, сопоставимой с решениями на базе DRAM, но с куда более низкой стоимостью владения. Экономия достигается и за счёт более эффективного использования SSD: в частности, при равном уровне надёжности с классическим массивом RAID 10, система на базе Pliops XDP позволяет обойтись меньшим количеством серверов и накопителей, что, естественно, отразится и на стоимости. Поставки новых ускорителей Pliops XDP Extreme уже развёрнуты.

24.11.2020 [18:54], Игорь Осколков

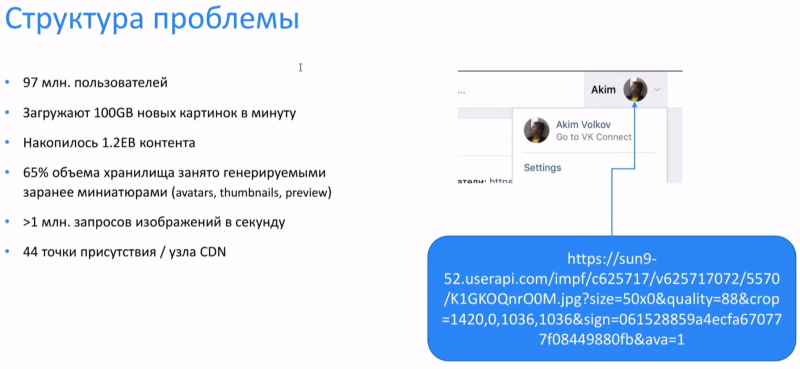

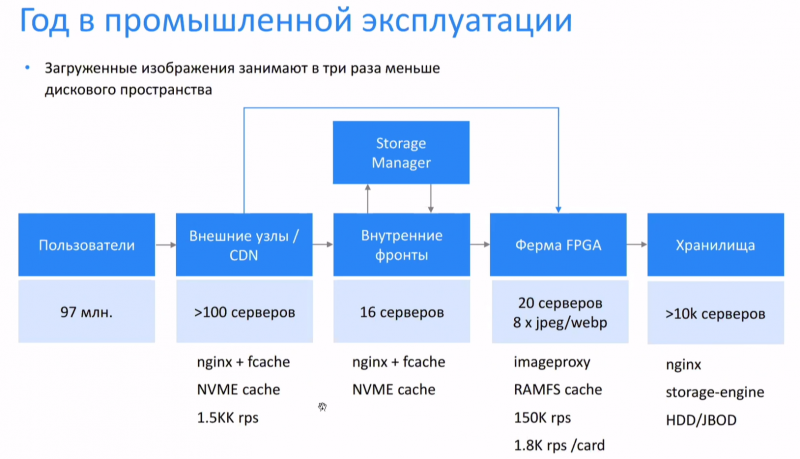

«ВКонтакте» использует FPGA Intel Arria для обработки изображений на летуГод назад на Intel Experience Day 2019 «ВКонтакте» поделилась результатами первых экспериментов по использованию FPGA-ускорителей для обработки изображений на лету. За прошедшее время компания внедрила ПЛИС в свою инфраструктуру, ускорив работу и сэкономив место в хранилище, где уже находится 1,2 Эбайта различного контента. У «ВКонтакте» почти 100 млн активных пользователей, которые ежеминутно загружают порядка 100 Гбайт изображений. Для каждого из них после загрузки генерируется более десятка копий различных формата и размера, которые используются в разных частях социальной сети. Основная проблема в том, что на таких масштабах все эти дополнительные изображения отъедают очень много места — до двух третей от общего объёма. Оптимальнее было бы генерировать их на лету, однако это очень существенная вычислительная нагрузка. Тестовые машины с Intel Xeon E5-2620 v4, которые на тот момент составляли значительную часть серверного парка, могли обработать до 200-220 изображений в секунду, чего явно было недостаточно. Поэтому и было принято решение попробовать для решения этой задачи FPGA, в данном случае это Arria 10. Теперь изображения с нужными характеристиками можно сформировать, указав параметры в URL. Если оно уже не закешировано на одной из конечных точек для отдачи контента, то запрос уходит «вниз» и из хранилища (а это более 10 тыс. серверов) извлекается оригинал и отправляется на FPGA-ферму, которая состоит всего из 20 серверов с ПЛИС, которых достаточно для удовлетворения всех запросов. На FPGA изображения конвертируются и отправляются «наверх», где кешируются и отдаются клиенту. Основными форматами, с которыми работает FPGA-ферма, являются JPEG и WebP, но компания рассматривает и другие, более современные. Кроме того, VK планирует изучить возможности FPGA для декодирования медиафайлов, сжатия данных (zstd) со стороны хранилища, а также опробовать в деле более современные модели ПЛИС.

16.10.2020 [23:17], Юрий Поздеев

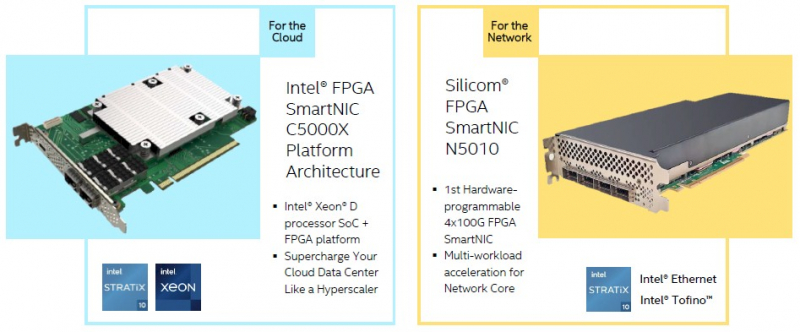

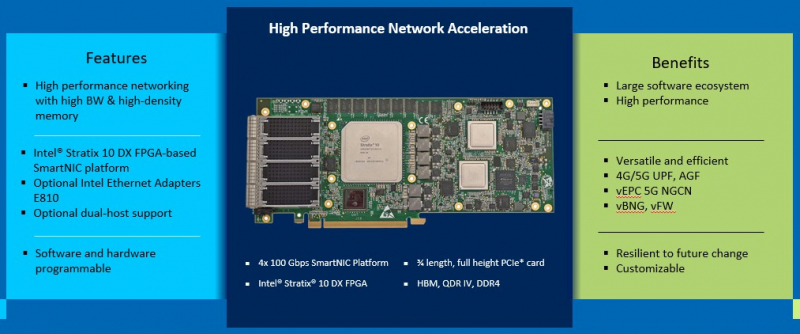

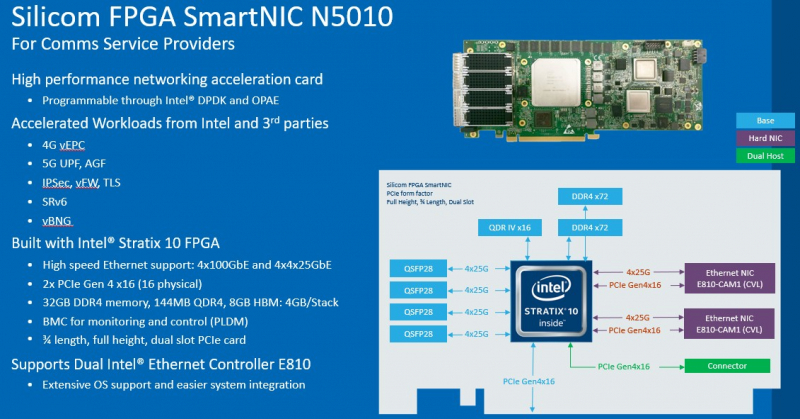

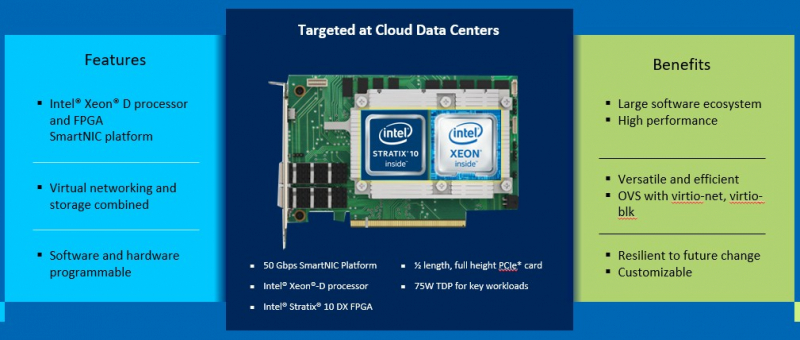

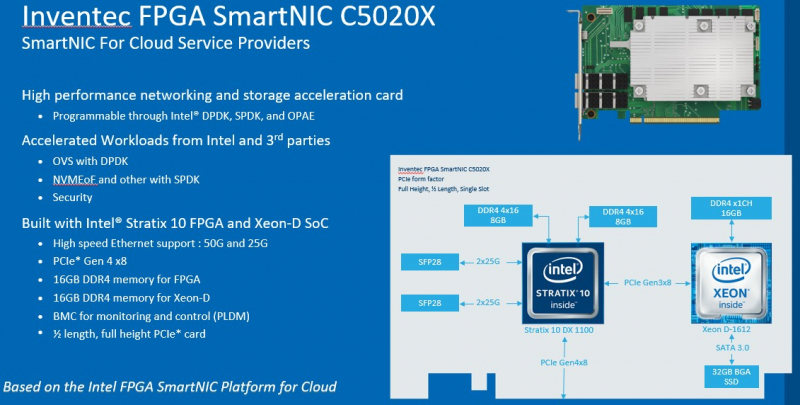

DPU в стиле Intel: сетевые адаптеры с Xeon D, FPGA, HBM и SSDМир сетевых карт становится умнее. Это следующий шаг в дезагрегации ресурсов центров обработки данных. Наличие расширенных возможностей сетевых карт позволяет разгрузить центральный процессор, при этом специализированные сетевые адаптеры обеспечивают более совершенные функции и безопасность. В этой новости мы познакомим вас сразу с двумя адаптерами: Silicom SmartNIC N5010 и Inventec SmartNIC C5020X. Silicom FPGA SmartNIC N5010 предназначена для систем крупных коммуникационных провайдеров. Операторы все чаще стремятся заменить проприетарные форм-факторы от поставщиков телекоммуникационного оборудования на более стандартные варианты. В рамках этого мы видим, что производители ПЛИС не прочи освоить и эту нишу.  В Silicom FPGA SmartNIC N5010 используется Intel Stratix 10 DX с 8 Гбайт памяти HBM. Поскольку пропускная способность памяти становится все большим аспектом производительности системы, HBM будет продолжать распространяться за пределы графических процессоров и FPGA. В SmartNIC и DPU память HBM может использоваться для размещения индексных таблиц поиска и других функций для интенсивных сетевых нагрузок. Помимо HBM SmartNIC N5010 имеет еще 32 Гбайт памяти DDR4 ECC. SmartNIC N5010 потребляет до 225 Вт, что предполагает несколько вариантов исполнения карты, в том числе и с активным охлаждением.  Самая интересная особенность новой карты — 4 сетевых порта по 100 Гбит/с. На плате SmartNIC N5010 установлены две базовые сетевые карты Intel E810 (Columbiaville). На приведенной схеме можно заметить, что используется интерфейс PCIe Gen4 x16, причем их тут сразу два. Для работы четырех 100GbE-портов уже недостаточно одного интерфейса PCIe 4.0 x16. Второй порт PCIe 4.0 x16 может быть подключен через дополнительный кабель к линиям второго процессора, чтобы избежать межпроцессорного взаимодействия для передачи данных.  Вторая новинка, Inventec FPGA SmartNIC C5020X, совмещает на одной плате процессор Intel Xeon D и FPGA Intel Stratix 10. Этот адаптер предназначен для разгрузки центрального процессора в серверах крупных облачных провайдеров. На плате установлен процессор Intel Xeon D-1612 с 32-Гбайт SSD и 16 Гбайт DDR4, подключение к ПЛИС Intel Stratix 10 DX 1100 осуществляется через PCIe 3.0 x8. Нужно отметить, что FPGA Stratix имеет свои собственные 16 Гбайт памяти DDR4, а также обеспечивает сетевые подключения 25/50 Гбит/с и оснащен интерфейсом PCIe 4.0 x8, через который адаптер подключается к хосту.  У Inventec уже есть решение на базе Arm (Inventec X250), которое использует ПЛИС Arria 10 GX660 вместе с сетевым адаптером Broadcom Stingray BCM8804, которое имеет аналогичный форм-фактор и TPD не более 75 Вт. Однако для некоторых организаций наличие единой x86 платформы, включая SmartNIC, упрощает развертывание, поэтому вариант C5020X для таких компаний более предпочтителен. Решение получилось очень интересным, однако вряд ли его можно назвать адаптером для массового рынка, как Intel Columbiaville. На примере этого адаптера Intel показала, что может объединить элементы своего портфеля для создания комплексных решений. Inventec FPGA SmartNIC C5020X является хорошей альтернативой предложению на базе Broadcom, что позволит крупным облачным провайдерам диверсифицировать свои платформы. Несмотря на то, что обе новинки классифицируются как «умные» сетевые адаптеры SmartNIC, вторая, пожалуй, уже ближе к DPU, если сравнивать её с адаптерами NVIDIA DPU, в которых сетевая часть дополнена Arm-процессором и GPU-ускорителем. В данном случае есть и x86-ядра общего назначения, и ускоритель, хотя и на базе ПЛИС. Впрочем, устоявшегося определения DPU и списка критериев соответствия этому классу процессоров пока нет. |

|