Материалы по тегу: fpga

|

02.10.2025 [15:28], Руслан Авдеев

Дата-центр радиотелескопа Square Kilometre Array (SKA) «засадили» сразу в две клетки Фарадея для защиты сверхчувствительных антенн от радиопомехРаботы в дата-центре, предназначенным для обслуживания радиообсерватории Square Kilometre Array (SKA) на западе Австралии, практически завершены. В числе прочего установлены две клетки Фарадея, блокирующие радиоволны — это делается, чтобы ЦОД не повлияли на работу сверхчувствительных антенн гигантского радиотелескопа, сообщает The Register. SKA представляет собой международный проект, предусматривающий строительство 131 072 антенн. Это крупнейший радиоинтерферометр в мире, потенциально позволяющий совершенно по-новому взглянуть на Вселенную. Работы начались в 2022 году. По имеющимся данным, уже установлено 12 100 антенн, работы по прокладке силовых кабелей и оптоволокна тоже в основном завершены. Работы над дата-центром в Мерчисоне (Murchison, штат Виктория), отдалённой части SKA, тоже завершены. Мерчисон выбран потому, что там почти нет людей и, следовательно, современной техники, что позволяет соблюдать режим радиомолчания. В дата-центре размещены около 100 стоек с серверами на базе FPGA, которые отвечают за фильтрацию терабайт данных, ежедневно собираемых SKA. Ценная информация будет отправляться по 10-Тбайт/с ВОЛС суперкомпьютеру в городе Перт (Perth).

Источник изображения: SKA Observatory Несмотря на то, что в Мерчисоне в целом мало электронных устройств, компьютеры генерируют немало радиопомех. Хотя в большинстве случаев в ЦОД и офисах это не проблема, в случае с SKA дело обстоит совсем иначе, поскольку тот настроен на поиск даже самых слабых сигналов. Именно поэтому ЦОД поместили сразу в две «клетки Фарадея». Экранированы даже входы в здание, а внутренняя дверь не откроется, пока не закрыта внешняя. Строительство на объекте SKA, вероятно, продолжится до 2029 года. В 2026 году учёным предложат представить собственные предложения по использованию радиотелескопа, некоторые выберут для испытаний SKA в 2027 году — к тому времени SKA уже будет самым большим «физическим низкочастотным радиотелескопом на планете». Руководство SKA уверено, что даже тесты 2027 года уже дадут результаты, достойные включения в научные труды. Одно из препятствий — поиск дополнительных средств. У SKA пока есть лишь 80 % средств для завершения проекта.

01.10.2025 [11:01], Сергей Карасёв

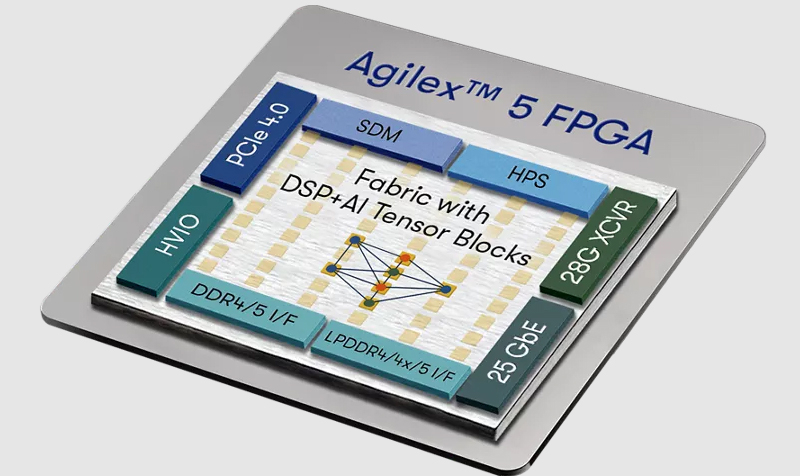

Altera улучшила характеристики FPGA семейства Agilex 5 и приступила к их массовому производствуКомпания Altera, контролирующая доля в которой недавно перешла частной инвестиционной компании Silver Lake, объявила о начале массового производства FPGA Agilex всех ключевых семейств, включая Agilex 5 и Agilex 3. При этом характеристики некоторых изделий были улучшены. Напомним, решения Agilex 3, дебютировавшие в марте нынешнего года, объединяют ПЛИС с возможностями ИИ и два ядра Arm Cortex-A55 с тактовой частотой 800 МГц. Поддерживается работа с памятью LPDDR4-2133. В свою очередь, решения Agilex 5 содержат ПЛИС с ИИ-архитектурой, а также по два ядра Arm Cortex-A76 и Cortex-A55 с частотой до 1,8 и 1,5 ГГц соответственно. Допускается использование памяти DDR4/5 и LPDDR4/5.

Источник изображения: Altera Altera сообщила об апгрейде изделий Agilex 5 D-Series среднего уровня. В частности, плотность логики в таких устройствах повышена в 2,5 раза — до 1,6 млн элементов. Благодаря этому достигается более высокая производительность при решении ИИ-задач на периферии, обработке видео в форматах 4K/8K, при построении сетей связи 5G/6G и др. Кроме того, внесены изменения в спецификацию памяти Agilex 5 D-Series: если раньше была реализована поддержка DDR5-4000 и LPDDR5-4267, то теперь заявлена совместимость с DDR5-5600 и LPDDR5-5500. Таким образом, прирост быстродействия памяти превышает 25 % по сравнению с оригинальными версиями. Помимо этого, Altera анонсировала выход программного обеспечения для разработчиков Quartus Prime версии 25.3, которое предоставляет доступ к новым инструментам проектирования, ускоряющим создание ПЛИС и вывод продукции на рынок. Новая редакция Quartus Prime в числе прочего позволяет использовать интеграционный инструментарий Visual Designer Studio на основе удобного интерфейса с функцией перетаскивания блоков.

29.08.2025 [23:15], Владимир Мироненко

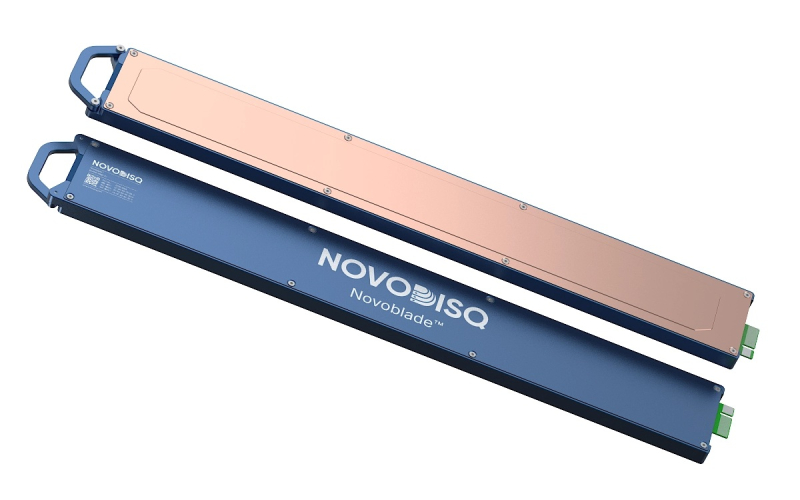

11,5 Пбайт в 2U: Novodisq представил блейд-сервер для ИИ и больших данныхСтартап Novodisq представил блейд-сервер формата 2U ёмкостью 11,5 Пбайт с функцией ускорения ИИ и др. задач. Гиперконвергентная кластерная система разработан для замены или дополнения традиционных решений NAS, SAN и публичных облачных сервисов. Новинка поддерживает платформы Ceph, MinIO и Nextcloud (также планируется поддержка DAOS), предлагая доступ по NFS, iSCSI, NVMe-oF и S3. Сервер содержит до 20 модулей Novoblade с фронтальной загрузкой. В каждом из них имеется до четырёх встроенных E2 SSD Novoblade объёмом 144 Тбайт каждый, на базе TLC NAND с шиной PCIe 4.0 x4. Накопители поддерживают NVMe v2.1 и ZNS, обеспечивая последовательную производительность чтения/записи до 1000 Мбайт/с, а на случайных операциях — до 70/30 тыс. IOPS. Надёжность накопителей составляет до 24 PBW. Энергопотребление: от 5 до 10 Вт. Система Novoblade предназначена для «тёплого» и «холодного» хранения данных. Модули Novoblade объединяют вычислительные возможности, ускорители и хранилища. Основной модулей являются гибридные SoC AMD Versal AI Edge Gen 2 (для ИИ-нагрузок) или Versal Prime Gen 2 (для традиционных вычислений) c FPGA, 96 Гбайт DDR5, 32 Гбайт eMMC, модулем TPM2 и двумя интерфейсам 10/25GbE с RoCE v2 RDMA и TSN. Энергопотребление не превышает 60 Вт. Есть функции шифрования накопителей, декодирования видео, ускорения ИИ-обработки, оркестрации контейнеров и т.д. Платформа специально разработана для задач с большими объёмами данных, таких как геномика, геопространственная визуализация, видеоархивация и периферийные ИИ-вычисления. Сервер может работать под управлением стандартных дистрибутивов Linux (RHEL и Ubuntu LTS) с поддержкой Docker, Podman, QEMU/KVM, Portainer и OpenShift. 2U-шасси глубиной 1000 мм рассчитано на установку до двадцати модулей Novodisq и оснащено двумя (1+1) БП мощностью 2600 Вт каждый (48 В DC). Возможно горизонтальное масштабирование с использованием каналов 100–400GbE. В базовой конфигурации шасси включает четыре 200GbE-модуля с возможностью горячей замены, каждый из которых имеет SFP28-корзины, а также управляемый L2-коммутатор. Предусмотрен набор средств управления, включая BMC с веб-интерфейсом, CLI и поддержкой API Ansible, SNMP и Redfish. Novoblade поддерживает локальное и удалённое управление, может интегрироваться в существующий стек или предоставляться с помощью инструментов «инфраструктура как код» (Infrastructure-as-Code). По словам разработчика, система Novoblade обеспечивает плотность размещения примерно в 10 раз выше, чем у сервера на основе жестких дисков, и снижает энергопотребление на 90–95 % без необходимости в механическом охлаждении. Novodisq утверждает, что общая стоимость владения системой «обычно на 70–90 % ниже, чем у традиционных облачных или корпоративных решений в течение 5–10 лет». «Это обусловлено несколькими факторами: уменьшенным пространством в стойке, низким энергопотреблением, отсутствием платы за передачу данных, минимальным охлаждением, длительным сроком службы и значительным упрощением управления. В отличие от облака, ваши расходы в основном фиксированы, а значит, предсказуемы, и, в отличие от традиционных систем, Novodisq не требует дорогостоящих лицензий, внешних контроллеров или постоянных циклов обновления. Вы получаете высокую производительность, долгосрочную надёжность и более высокую экономичность с первого дня», — приводит Blocks & Files сообщение компании. Для сравнения, узлы Dell PowerScale F710 и F910 на базе 144-Тбайт Solidigm SSD ёмкостью 122 Тбайт, 24 отсеками в 2U-шасси и коэффициентом сжатия данных 2:1 обеспечивают почти 6 Пбайт эффективной емкости, что почти вдвое меньше, чем у сервера Novoblade.

12.03.2025 [14:57], Сергей Карасёв

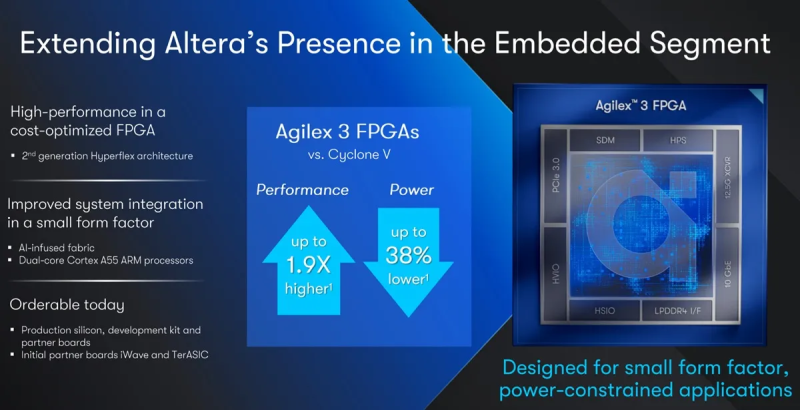

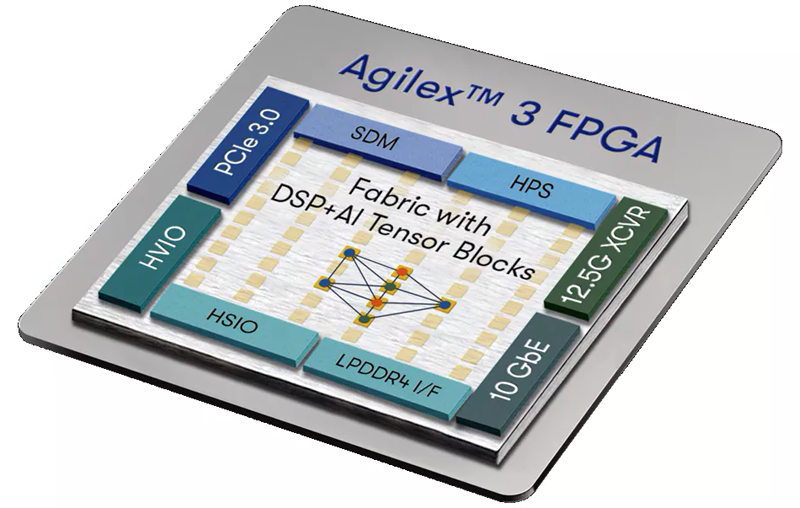

Altera представила малые FPGA семейства Agilex 3 для энергоэффективных системКомпания Altera, сформированная на базе выделенной из Intel группы программируемых решений (PSG), анонсировала FPGA семейства Agilex 3 для маломощных и экономичных систем. Среди сфер применения изделий названы автоматизация производственных процессов, медицинская визуализация, видеонаблюдение, мониторинг транспортных систем, периферийные ИИ-вычисления и пр. О подготовке Agilex 3 сообщалось в сентябре прошлого года. Задействована архитектура HyperFlex второго поколения. В состав решений входят ПЛИС с возможностями ИИ и два ядра Arm Cortex-A55 с тактовой частотой 800 МГц. По заявлениям Altera, чипы Agilex 3 обеспечивают 1,9-кратный рост производительности по сравнению Cyclone V при снижении энергопотребления до 38 %. Для трансиверов Agilex 3 заявлена скорость передачи данных до 12,5 Гбит/с. Говорится о поддержке интерфейсов PCIe 3.0 x4 и 10GbE. Усовершенствованный цифровой сигнальный процессор с блоком AI Tensor Block обеспечивает пиковую ИИ-производительность 2,8 TOPS на операциях INT8. Реализованы различные средства обеспечения безопасности, включая защищённую загрузку, шифрование AES и управление конфигурацией FPGA.  В семейство Agilex 3 вошли модели A3C025, A3C050, A3C065, A3C100 и A3C135, насчитывающие от 25 075 до 135 110 логических элементов. Поддерживается работа с памятью LPDDR4-2133. Изделия могут быть выполнены в корпусе с размерами 12 × 12, 16 × 16 или 18 × 18 мм. В качестве примеров использования Agilex 3 компания Altera приводит роботизированные системы, где FPGA обеспечивают управление в реальном времени для многоосевых манипуляторов. В составе промышленных камер чипы улучшают обнаружение дефектов. Приём предварительных заказов на изделия уже начался.

12.03.2025 [12:12], Сергей Карасёв

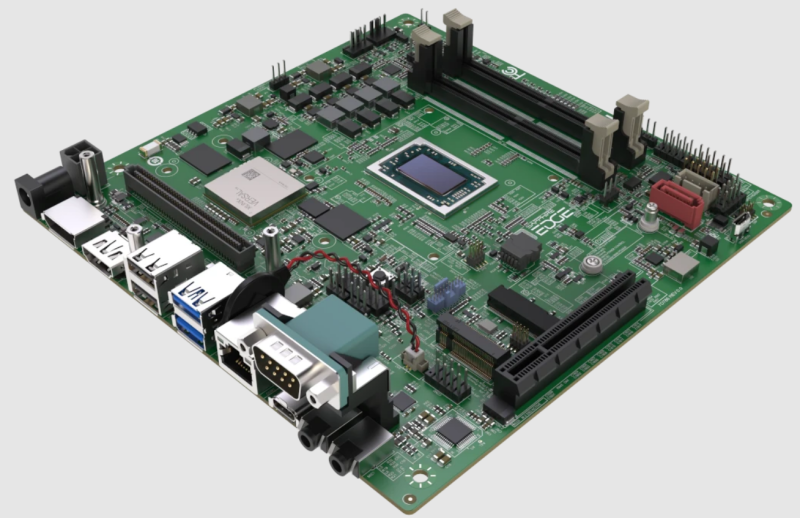

Mini-ITX-плата Sapphire Edge+ VPR-5050 содержит чип AMD Ryzen V2748 и FPGA VersalКомпания Sapphire анонсировала материнскую плату Edge+ VPR-5050 на платформе AMD Embedded+, выполненную в форм-факторе Mini-ITX с размерами 170 × 170 мм. Новинка предназначена для таких задач, как ИИ-приложения, промышленная автоматизация, обработка данных от различных датчиков в режиме реального времени и пр. Плата содержит процессор AMD Ryzen Embedded V2748 с восемью ядрами (2,9/4,15 ГГц) и графическим ускорителем Radeon RX Vega 7 с частотой 1,6 ГГц. Кроме того, задействована FPGA AMD Versal AI Edge VE2302 с двумя ядрами Arm Cortex-A72 (до 1,6 ГГц), двумя ядрами Arm Cortex-R5F, ИИ-движком с производительностью до 23 TOPS, памятью LPDDR4 (2 × 4 Гбайт или 2 × 8 Гбайт) и опциональным чипом eMMC на 64 Гбайт. Материнская плата располагает двумя слотами SO-DIMM с поддержкой до 64 Гбайт памяти DDR4-3200. Есть коннектор M.2 для SSD (PCIe 3.0 x4 или SATA-3) и порт SATA-3 для дополнительного накопителя (SSD или HDD). В разъём M.2 Key-E 2230 (PCIe 3.0 x1 и USB 2.0) может быть установлен комбинированный модуль Wi-Fi/Bluetooth. Доступен слот расширения PCIe x8. Набор интерфейсов включает выходы DP и HDMI, по два порта USB 3.2 Gen2 Type-A и USB 2.0 Type-A, один порт USB 3.2 Gen2 Type-C, гнездо RJ-45 для сетевого кабеля (контроллер 2.5GbE), последовательный порт и 3,5-мм аудиогнёзда. Диапазон рабочих температур простирается от 0 до +60 °C. Говорится о совместимости с RHEL/CentOS 7.9, RHEL 8.2–8.6 и Ubuntu 22.04. Для новинки доступны различные индустриальные модули расширения, в частности, с двумя портами 10/25GbE или 1GbE. Материнская плата может быть оборудована активным кулером с вентилятором.

27.12.2024 [13:44], Сергей Карасёв

Стартап Ubitium создал универсальный чип на базе RISC-V с функциями CPU, GPU, DSP и FPGAСтартап Ubitium, основанный в 2024 году, анонсировал проект по созданию чипа с универсальной архитектурой, которая полностью независима от рабочих нагрузок. Речь идёт об объединении в одном изделии решений разного типа: CPU, GPU, DSP и FPGA. Отмечается, что на протяжении более 50 лет полупроводниковая промышленность занималась созданием самостоятельных центральных, графических и других процессоров, предназначенных для решения конкретных вычислительных задач. Ubitium предлагает пересмотреть данный подход, создав универсальный чип на открытой архитектуре RISC-V, который сможет одинаково хорошо справляться с нагрузками разного типа. Стартап отмечает, что основным препятствием для внедрения новых процессоров являются проприетарные ISA, которые требуют использования специализированных программных инструментов. Кроме того, трудности может создавать отсутствие зрелой программной экосистемы, предоставляющей необходимые фреймворки и приложения. Чипы Ubitium, как утверждается, будут на 100 % совместимы с RISC-V, что упростит и ускорит разработку и внедрение конечных продуктов. В отличие от традиционных процессоров со специализированными ядрами, предназначенными для определённых задач, блоки универсального чипа Ubitium могут динамически «переназначаться» для обработки широкого спектра вычислительных нагрузок, включая простую логику управления, общие вычисления, ИИ и рендеринг графики. Ещё одним преимуществом предлагаемой концепции стартап называет масштабируемость. Ubitium планирует выпускать изделия разного уровня, которые при этом будут иметь идентичную архитектуру и использовать одни и те же программные инструменты. Компания рассчитывает, что её чипы смогут применяться в самых разных сферах — от встраиваемых устройств, бытовой электроники и домашней техники до систем промышленной автоматизации, роботов и космического оборудования. По сравнению с традиционными процессорами, использование решений Ubitium, как утверждается, обеспечит повышение гибкости, снижение стоимости и ускорение разработки. Компания заявляет, что универсальный чип может обеспечить в 10–100 раз большую производительность в расчёте на доллар по сравнению с современными специализированными решениями. В команду Ubitium входят выходцы из Intel, NVIDIA и Texas Instruments. Головной офис компании находится в Дюссельдорфе (Германия). Генеральным директором является Хён Шин Чо (Hyun Shin Cho) из Университета Пердью (Purdue University). Пост технического директора занимает Мартин Форбах (Martin Vorbach), на имя которого зарегистрированы более 200 патентов. Стартап Ubitium уже привлёк $3,7 млн начального финансирования. На данный момент компания создала экспериментальную эмуляцию, которая подтверждает, что универсальный процессор работоспособен. Первые коммерческие решения планируется выпустить к 2026 году.

27.12.2024 [12:40], Сергей Карасёв

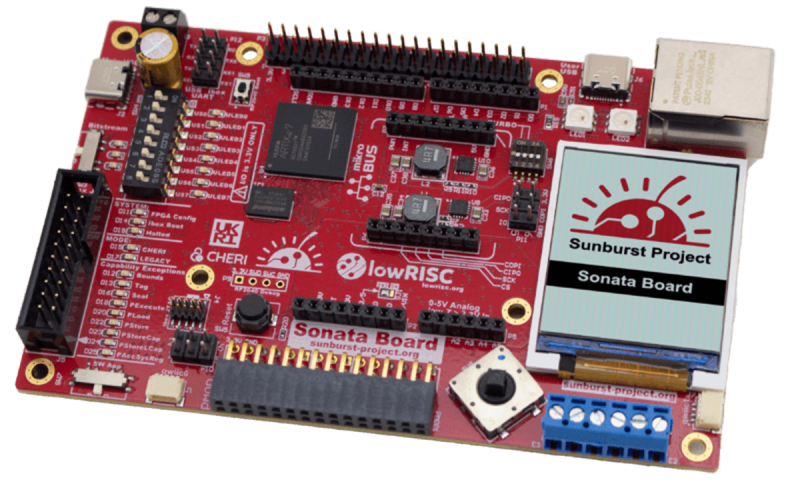

Плата lowRISC Sonata v1.0 с системой защиты памяти CHERIoT объединяет FPGA AMD Artix-7 и микроконтроллер Raspberry Pi RP2040Участники проекта lowRISC по созданию 64-бит чипов RISC-V, как сообщает ресурс CNX Software, анонсировали аппаратную платформу Sonata v1.0 для разработчиков встраиваемых систем и всевозможных устройств Интернета вещей (IoT). Новинка поддерживает технологию CHERIoT (Capability Hardware Extension to RISC-V for IoT). Напомним, летом уходящего года lowRISC, а также Capabilities Limited, Codasip, FreeBSD Foundation, SCI Semiconducto и Кембриджский университет создали альянс CHERI для продвижения средств надёжной защиты памяти от атак. Специальные механизмы исключают ряд потенциальных уязвимостей, таких как переполнение буфера или некорректная работа с указателями. Отмечалось, что первыми новую технологию могут получить процессоры RISC-V. В основе платформы Sonata v1.0 лежит FPGA AMD Xilinx Artix-7 (XC7A35T-1CSG324C). Изделие содержит Soft-процессорное ядро AMD MicroBlaze с архитектурой RISC и 400 Кбайт распределённой памяти RAM. Ещё одной составляющей платы является микроконтроллер Raspberry Pi RP2040 (два ядра Cortex-M0+ с частотой 133 МГц), который отвечает за IO-функции. Есть 64 Мбит памяти HyperRAM (Winbond W956D8MBYA5I), 256 Мбит памяти SPI-флеш (Winbond W25Q256JVEIQ) для FPGA AMD Artix-7 или Raspberry Pi RP2040, ещё 64 Мбит SPI-флеш (Winbond W25Q64JVZEIQ) для RP2040 и 256 Мбит памяти SPI-флеш (Winbond W25Q256JVEIQ) для FPGA. В арсенале Sonata v1.0 — встроенный цветной ЖК-дисплей с диагональю 1,8″, сетевой порт 10/100MbE, два разъёма USB Type-C (для программирования и подачи питания) и слот microSD. Реализованы последовательные интерфейсы RS-232 и RS-485, 40-контактный разъём Raspberry Pi, две 10-контактные колодки Ibex JTAG, две 4-контактные колодки Ibex UART и пр. Размеры составляют 125 × 80 мм. Разработчики могут получить доступ к подробной документации и дополнительным ресурсам на сайтах lowRISC и GitHub, чтобы в полной мере использовать возможности платформы Sonata v1.0. Цена новинки — примерно $413.

21.12.2024 [14:00], Сергей Карасёв

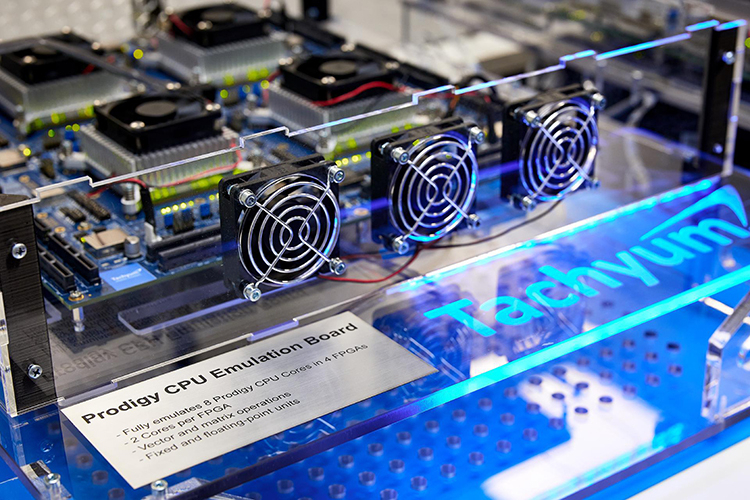

Для невыпущенного суперчипа Tachyum Prodigy выпустили 1600-страничное руководство по оптимизации производительностиСловацкая компания Tachyum, разрабатывающая процессоры Prodigy с уникальной архитектурой, объявила о выпуске руководства по оптимизации производительности этих чипов. Точнее, для FPGA-эмулятора Prodigy, поскольку самих чипов всё ещё нет. Огромный документ на 1600 страниц содержит подробную информацию о том, как в полной мере воспользоваться потенциалом новинки. Первая информация о разработке Prodigy появилась в 2019–2020 гг. Эти суперпроцессоры, как утверждается, объединяют возможности CPU, GPU и TPU. Они предназначены для решения различных ресурсоёмких задач, связанных в том числе с ИИ и машинным обучением. Сроки выпуска Prodigy несколько раз пересматривались: сначала выход чипов был перенесён с 2021-го на 2022 год, затем — на 2023 год, а впоследствии — на 2024-й. В соответствии с текущими планами Tachyum намерена начать отгрузку образов чипов в 2025 году.

Источник изображения: Tachyum Подготовленное руководство для изделий Prodigy, как заявляет компания, содержит рекомендации по созданию высокопроизводительного ПО для этой платформы. Документ описывает конкретные методы оптимизации, включая управление ограничениями диспетчеризации, улучшение процедур работы памяти и пр. Кроме того, описаны способы обработки операций кеширования и доступа к специальным регистрам для тонкой настройки с целью достижения максимальной производительности. В руководстве рассматриваются особенности чипов. Архитектура набора инструкций Prodigy (ISA) представляет собой смесь RISC и CISC, но не включает какие-либо сложные и/или длинные и неэффективные инструкции переменной длины. Все инструкции имеют ширину 32 или 64 бит, а некоторые из них содержат функции доступа к памяти для дальнейшего повышения производительности. Изделия Prodigy объединяют до 192 ядер с тактовой частотой до 5 ГГц и выше. Реализованы 16 каналов памяти DDR5-7200 с возможностью использования до 32 Тбайт ОЗУ в расчёте на процессорный разъём. Поддерживаются 96 линий PCIe 5.0. Планируемая технология производства — 5 нм. В конце 2023 года Tachyum получила заказ на поставку чипов Prodigy для создания суперкомпьютера с ИИ-производительностью до 8 Зфлопс.

12.12.2024 [17:36], Сергей Карасёв

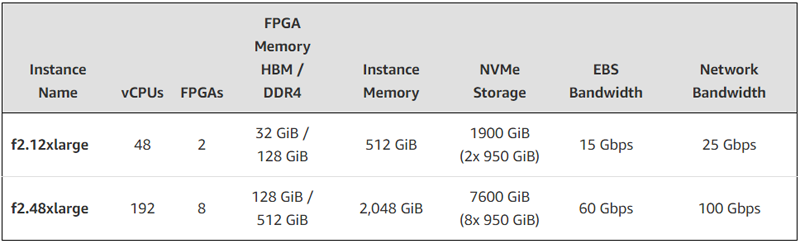

FPGA + EPYC: AWS представила AMD-инстансы EC2 F2 с процессорами Milan и ПЛИС Virtex UltraScale+Облачная платформа AWS анонсировала инстансы второго поколения с FPGA на борту. Экземпляры EC2 F2 ориентированы на решение задач в области геномики, обработки мультимедийных материалов, больших данных, спутниковой связи, компьютерных сетей, моделирования кремниевых чипов и видеотрансляций в реальном времени. В новых инстансах применяются FPGA AMD Virtex UltraScale+ HBM VU47P. Эти изделия содержат 2,852 млн логических ячеек и 9024 DSP. Заявленная ИИ-производительность достигает 28 TOPS при вычислениях INT8. Кроме того, в состав EC2 F2 входят процессоры AMD EPYC поколения Milan. Новые инстансы доступны в вариантах f2.12xlarge и f2.48xlarge — с 48 и 192 vCPU и 2 и 8 FPGA соответственно. Каждая ПЛИС оперирует 16 ГиБ памяти HBM и 64 ГиБ памяти DDR4. Таким образом, в случае f2.12xlarge используется в сумме 32 ГиБ HBM и 128 ГиБ DDR4, а в случае f2.48xlarge — 128 ГиБ и 512 ГиБ соответственно.

Источник изображения: AWS Конфигурация f2.12xlarge включает 512 ГиБ системной памяти и два накопителям NVMe SSD суммарной вместимостью 1900 ГиБ. Пропускная способность сетевого подключения составляет 25 Гбит/с, пропускная способность EBS-томов — 15 Гбит/с. У экземпляра f2.48xlarge объём памяти составляет 2048 ГиБ, общая вместимость NVMe SSD — 7600 ГиБ. Пропускная способность сетевого подключения и EBS-томов достигает 100 Гбит/с и 60 Гбит/с соответственно. Для этого экземпляра предусмотрена поддержка AWS Cloud Digital Interface (CDI) для надёжной передачи несжатого видео (задержка между инстансами заявлена на уровне 8 мс).

25.11.2024 [16:17], Владимир Мироненко

В Lattice Semiconductor обсуждают возможность покупки у Intel всего FPGA-подразделения AlteraLattice Semiconductor из Хиллсборо (штат Орегон) проявила интерес к покупке Altera (ранее PSG), подразделения Intel, специализирующегося на разработке ПЛИС. Это не вполне согласуется с планами производителя чипов продать лишь миноритарный пакет акций подразделения для улучшения своего финансового положения. Именно такое предложение Intel разослала потенциальным покупателям. Тем не менее, по данным источников Bloomberg, в Lattice Semiconductor обсуждают с консультантами возможность подачи предложения о полной покупке Altera и сейчас ищут потенциального частного инвестора для финансирования сделки. Как сообщают источники, компании, специализирующиеся на поглощениях, включая Francisco Partners, Bain Capital и Silver Lake Management, также рассматривают варианты инвестирования в Altera. Кроме того, возможность покупки доли в Altera может привлечь интерес и других полупроводниковых компаний. Предложения о покупке Altera должны быть поданы в четверг на этой неделе, сообщили источники агентства. По мнению аналитиков Bloomberg, приобретение Altera станет для Lattice сложной задачей, учитывая её относительно небольшие размеры. Рыночная стоимость Lattice составляет $7,48 млрд, что менее половины суммы, которую Intel заплатила за Altera в 2015 году — около $17 млрд.

Источник изображения: Intel По словам источников, предложения о покупке доли в Altera, чьи многоцелевые чипы преимущественно используются в телекоммуникационных сетях, должны быть тщательно структурированы. Частные инвестиционные компании рассматривают возможность инвестирования порядка $3 млрд, которые могут быть представлены в форме сложных интегрированных инструментов. Это может привести к оценке Altera ниже той стоимости, за которую её приобрела Intel, отмечают источники. Intel в прошлом месяце вновь заявила о намерении продать долю в Altera, не отказываясь от планов дальнейшего проведения IPO. Это является частью более широкой стратегии чипмейкера по реорганизации своего бизнеса. На этой неделе состоится заседание совета директоров Intel, повестка которого включает обсуждение будущего Altera, сообщили источники, повторив, что Intel предпочла бы продать миноритарную долю в Altera, а не все подразделение. Генеральный директор Intel Пэт Гелсингер (Pat Gelsinger) заявил, что компания намерена решить вопрос с Altera в начале следующего года. Источники подчеркнули, что потенциальные покупатели Altera продолжают обсуждения, и гарантий того, что сделка состоится, пока нет. |

|