Материалы по тегу: интерконнект

|

30.03.2024 [14:03], Сергей Карасёв

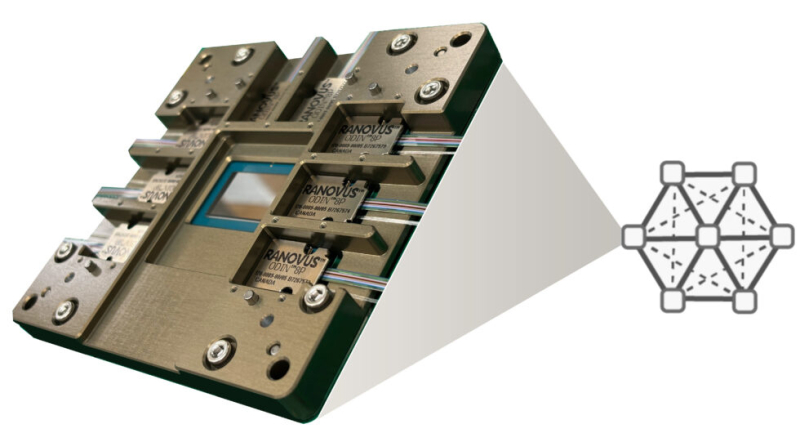

MediaTek и Ranovus создадут оптический интерконнект с пропускной способностью 6,4 Тбит/с для ЦОД-платформКомпании MediaTek и Ranovus объявили о заключении соглашения о сотрудничестве в области разработки оптического интерконнекта для дата-центров, ориентированных на задачи ИИ и машинного обучения. Речь идёт о создании решения Co-Packaged Optics (CPO) с пропускной способностью 6,4 Тбит/с для ASIC MediaTek следующего поколения. Технология CPO предусматривает интеграцию оптических компонентов и традиционных электронных интегральных схем в одном изделии. Сообщается, что Ranovus создала модуль Odin CPO 3.0 — первую в отрасли монолитную электронно-фотонную интегральную схему для мультитерабитного оптического интерконнекта. Это решение представляет собой специализированный чип, содержащий трансимпедансные усилители (TIA) класса 100 Гбит/с, драйверы, модуляторы на основе кремниевой фотоники и фотодетекторы. Возможно использование интегрированного лазера или внешнего лазерного источника. Утверждается, что использование Odin CPO 3.0 позволяет снизить энергопотребление (4 пДж/бит), занимаемую площадь и стоимость системы на 50 % по сравнению с существующими решениями. Предполагается, что использование Odin CPO 3.0 позволит MediaTek создавать наиболее передовые ASIC-решения для дата-центров с высокими ИИ-нагрузками и интенсивным обменом информацией. «Совместная работа с MediaTek над созданием этой CPO-платформы открывает новую эру оптического интерконнекта высокой плотности в экосистемах ИИ и Ethernet», — говорит Ходжат Салеми (Hojjat Salemi), директор по развитию бизнеса Ranovus.

29.03.2024 [13:39], Сергей Карасёв

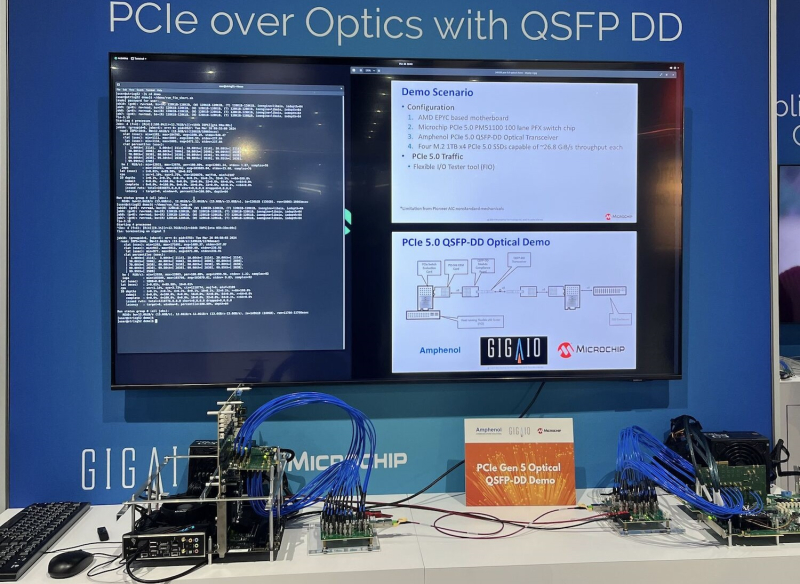

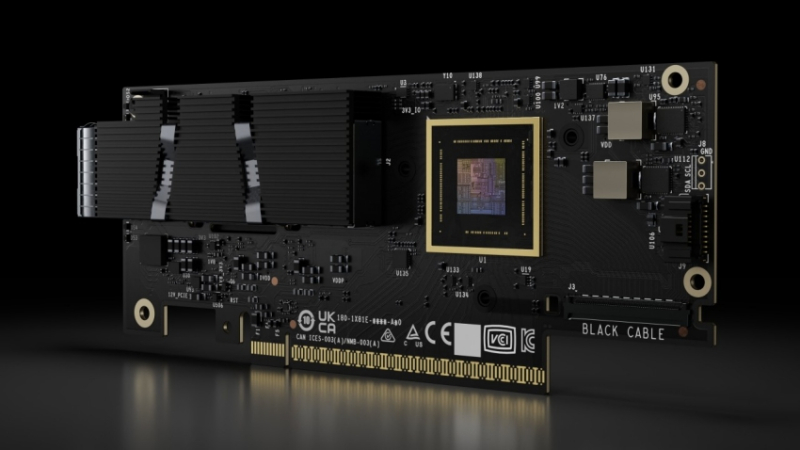

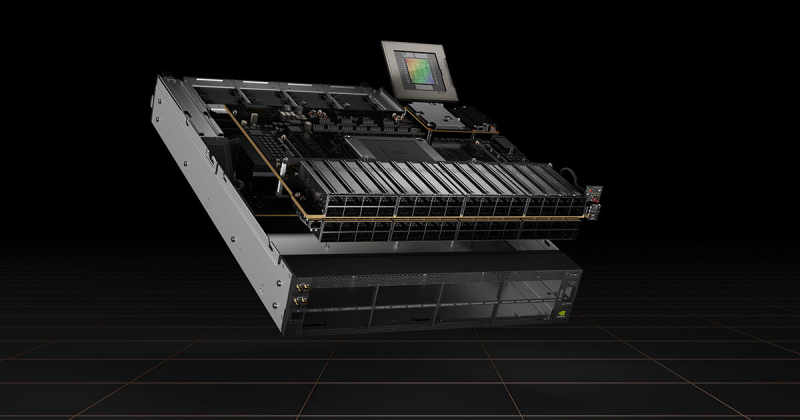

GigaIO представила оптические кабели PCIe 5.0 для развёртывания масштабных ИИ-кластеровКомпания GigaIO, разрабатывающая систему распределённого интерконнекта на базе PCI Express под названием FabreX, представила первые в отрасли оптические кабели QSFP-DD с поддержкой PCIe 5.0. Отмечается, что оптические кабели обеспечивают ряд преимуществ перед традиционными медными соединениями. Это, в частности, повышенная пропускная способность. Кроме того, длина оптических линий может превышать 3 м, что является ограничением для медных кабелей. Представленные кабели используют конфигурацию PCIe 5.0 x8 с возможностью агрегации 16 линий. Благодаря этим изделиям упрощается развёртывание высокопроизводительных систем GigaIO SuperNODE, которые позволяют связать воедино до 32 ускорителей посредством упомянутой платформы FabreX. Отмечается, что оптические кабели способны обеспечить передачу данных с высокой скоростью на десятки метров. Таким образом, несколько систем SuperNODE или SuperDuperNODE могут быть объединены в единый кластер для решения наиболее ресурсоёмких задач ИИ. Медные соединения обычно ограничивают размер кластеров двумя–тремя стойками. В случае оптических кабелей предоставляется гораздо большая гибкость в плане конфигурации оборудования. В результате системы SuperNODE могут быть развёрнуты даже в тех дата-центрах, в которых существуют жёсткие ограничения по мощности и охлаждению в расчёте на стойку. Оптические кабели QSFP-DD с поддержкой PCIe 5.0 станут доступны предстоящим летом.

28.03.2024 [20:42], Сергей Карасёв

Оптика для HBM: стартап Celestial AI получил ещё $175 млн инвестиций, в том числе от AMD и SamsungКомпания Celestial AI, занимающаяся созданием технологий оптического интерконнекта, сообщила о проведении раунда финансирования Series C, в ходе которого привлечено $175 млн. Деньги будут использованы для ускорения разработки и вывода передовых продуктов на коммерческий рынок. Летом прошлого года Celestial AI объявила о разработке технологии Photonic Fabric. Она ориентирована на ИИ-платформы и системы НРС. Благодаря оптическому интерконнекту нового типа ИИ-чипы могут быть соединены с большим пулом высокопроизводительной памяти HBM3, а в перспективе — и HBM4. Таким образом, решается проблема ограниченного объёма памяти HBM в составе ИИ-ускорителей. По заявлениям Celestial AI, технология Photonic Fabric обеспечивает повышение пропускной способности и объёма доступной памяти более чем в 25 раз при одновременном снижении задержек и энергопотребления примерно в 10 раз по сравнению с существующими оптическими альтернативами и традиционными медными соединениями. Таким образом, можно масштабировать нагрузки ИИ.

Источник изображения: Celestial AI В июне 2023 года Celestial AI провела раунд финансирования Series B на сумму в $100 млн. Тогда средства предоставили IAG Capital Partners, Koch Disruptive Technologies (KDT), Temasek Xora Innovation, Samsung Catalyst, Smart Global Holdings (SGH), Porsche Automobil Holding SE, The Engine Fund, imec.xpand, M Ventures и Tyche Partners. Инвестиционная программа Series C проведена под предводительством Фонда инновационных технологий США (USIT) миллиардера Томаса Талла (Thomas Tull), основателя Legendary Entertainment. В программе также приняли участие AMD Ventures, KDT, Temasek, Xora Innovation, IAG Capital Partners, Samsung Catalyst, SGH, Porsche Automobil Holding SE, Engine Ventures, M-Ventures и Tyche Partners.

28.03.2024 [14:44], Сергей Карасёв

Стартап Eliyan, разработчик интерконнекта NuLink, получил на развитие ещё $60 млнМолодая компания Eliyan из Санта-Клары (Калифорния, США) сообщила о проведении раунда финансирования Series B, в рамках которого на развитие привлечено $60 млн. Средства поступили в дополнение к $40 млн, которые стартап получил в 2022 году в ходе инвестиционной программы Series А. Eliyan является разработчиком интерконнекта NuLink, предназначенного для соединения чиплетов. Данная технология рассматривается в качестве альтернативы упаковочным решениям TSMC CoWoS и Intel EMIB. При этом NuLink совместима с единым стандартом UCIe.

Источник изображения: Eliyan По заявлениям Eliyan, технология NuLink способна обеспечить производительность, в четыре раза превышающую показатели конкурирующих решений. При этом показатель TCO может быть снижен вдвое. Внедрение NuLink может помочь в развитии аппаратных ИИ-платформ нового поколения. Помимо объединения чиплетов, эта система также позволяет связывать процессоры с модулями памяти. Eliyan отмечает, что в NuLink реализована функция одновременной двунаправленной передачи сигналов, что позволяет каждому соединению отправлять и получать данные одновременно. Это удваивает пропускную способность на линию по сравнению с традиционными решениями, которые обычно могут в каждый момент времени либо передавать, либо принимать информацию. Раунд финансирования Series B возглавили Samsung Catalyst Fund и Tiger Global Management. Кроме того, средства предоставили существующие инвесторы, в том числе Intel Capital, а также SK hynix, Cleveland Avenue, Mesh Ventures и др. Деньги пойдут на дальнейшее развитие и внедрение технологии. Говорится, что недавно NuLink была реализована на базе 3-нм техпроцесса TSMC, обеспечив лучшую в отрасли производительность — до 64 Гбит/с на канал. В целом, система NuLink достигла коммерческой готовности.

27.03.2024 [23:40], Сергей Карасёв

Coherent представила оптические коммутаторы для дата-центров, ориентированных на задачи ИИCoherent анонсировала специализированные оптические коммутаторы для ИИ-кластеров высокой плотности. В основу устройств Optical Circuit Switch (OCS) положена фирменная платформа кросс-коммутации Lightwave Cross-Connect (DLX). В изделиях, в отличие от традиционных коммутаторов, не применяются приемопередатчики для преобразования фотонов в электроны и обратно. Вместо этого все операции осуществляются в оптическом тракте: импульсы поступают в один порт и выходят из другого (конечно, с небольшим ослаблением). Coherent выделяет несколько ключевых преимуществ своей технологии. Прежде всего значительно возрастает производительность, что важно при решении ресурсоёмких задач, связанных с приложениями ИИ. Кроме того, благодаря отказу от преобразования среды сокращаются энерозатраты. Наконец, отпадает необходимость в обновлении собственно коммутаторов при установке в ЦОД оборудования следующего поколения. Это значительно повышает окупаемость капитальных затрат.

Источник изображения: Coherent Представленное решение насчитывает 300 входных и 300 выходных оптических портов. Коммутаторы OCS помогают решить проблемы масштабируемости и надёжности дата-центров, ориентированных на приложения ИИ. Аналитики Dell'Oro Group отмечают, что для ИИ-задач требуется более высокий уровень отказоустойчивости, нежели для традиционных приложений. Крайне важно, чтобы коммутаторы, используемые в составе ИИ-платформ, не провоцировали никаких перебоев во время обучения или эксплуатации больших языковых моделей. Устройства Coherent, как сообщается, обеспечивают необходимый уровень надёжности. Массовые поставки новых коммутаторов планируется организовать в 2025 году. При этом Google уже использует в своих дата-центрах оптические коммутаторы (OCS) собственной разработки на базе MEMS-переключателей для формирования ИИ-кластеров, а Meta✴ совместно с MIT разработала систему TopoOpt, представляющую собой оптическую патч-панель с манипулятором, который позволяет менять топологию сети.

22.03.2024 [21:10], Сергей Карасёв

Консорциум Ultra Ethernet пополнился 45 участниками, но NVIDIA среди них так и нетКонсорциум Ultra Ethernet объявил о том, что в его состав вошли 45 новых участников. Таким образом, на сегодняшний день общее количество членов этой организации достигает 55. К участию в Ultra Ethernet приглашаются и другие заинтересованные компании и институты. Напомним, консорциум был создан в июле 2023 года. Его задача заключается в разработке основанной на Ethernet открытой высокопроизводительной архитектуры с полным коммуникационным стеком, отвечающей задачам современных рабочих нагрузок ИИ и НРС. Изначально в состав Ultra Ethernet входили AMD, Arista, Broadcom, Cisco, Eviden (Atos), HPE, Intel, Meta✴ и Microsoft. Позднее к консорциуму присоединилась компания Cornelis Networks, поставщик HPC-интерконнекта на базе Omni-Path. С ноября 2023-го организация начала принимать новых участников в массовом порядке. С тех пор инициативу поддержали Nokia, Lenovo, Baidu, Dell, Huawei, IBM, Supermicro, Tencent и многие другие компании. Примечательно, что в списке участников так и нет AWS, Google и NVIDIA. Последняя по-прежнему считает InfinBand лучшим интерконнектом для HPC/ИИ-кластеров и является фактически единственным поставщиком данной технологии. Более того, даже Ethernet-решения NVIDIA подвергаются критике со стороны конкурентов. Для тех, кто заинтересован в работах в рамках проекта, Ultra Ethernet предлагает различные варианты участия через восемь технических групп. В их число, в частности, входят физический, транспортный и программный уровни, хранение, управление, отладка и пр. В настоящее время ведётся активная работа над спецификацией Ultra Ethernet версии 1.0: представить её планируется в III квартале текущего года. Ожидается, что совместная работа десятков IT-компаний в перспективе позволит создать революционные коммуникационные платформы.

22.03.2024 [09:09], Алексей Степин

NVIDIA представила 800G-платформы Quantum-X800 и Spectrum-X800 для InfiniBand- и Ethernet-фабрик нового поколенияДополнением к только что представленным ИИ-ускорителям NVIDIA Blackwell станут новые сетевые 800G-платформы Quantum-X800 и Spectrum-X800, а также сетевые адаптеры ConnectX-8. Именно они позволят вывести масштабирование ИИ-кластеров на новый уровень и позволят «прокормить» гигантские массивы ускорителей в дата-центрах гиперскейлеров. Платформа NVIDIA Quantum-X800 ориентирована на наиболее производительные ИИ- и HPC-кластеры. Она использует новое поколение технологии InfiniBand, всё ещё обладающей рядом преимуществ в сравнении с Ethernet, и включает в себя обновлённые SHARP-движки. Технология SHARPv4 реализует «вычисления в сети» (In-Network Computing), что позволяет не только существенно разгрузить вычислительные узлы и серверы, но и обеспечить более высокую пропускную способность интерконнекта вкупе с более серьёзными возможностями его масштабирования. Основой платформы Quantum-X800 стал 4U-коммутатор Q3400-RA, впервые в индустрии, как говорит компания, использующий 200G-блоки SerDes для каждой линии InfiniBand. Коммутатор располагает 144 портами 800G в 72 OSFP-модулях и выделенным портом для Unified Fabric Manager. Новинка имеет стандартное 19″ исполнение с воздушным охлаждением, но есть и вариант Q3400-LD с жидкостным охлаждением, предназначенный для 21″ OCP-стоек. В двухуровневом варианте fat tree коммутаторы позволят объединить 10 368 NIC. Основным адаптером для новой платформы InfiniBand является ConnectX-8 SuperNIC с интерфейсом PCIe 6.0. Он является частью SHARPv4 и предлагается в однопортовом (OSFP224) и двухпортовом (QSFP112) вариантах и в нескольких форм-факторах, включая OCP 3.0. На платах также имеется разъём SocketDirect на 16 линий PCIe. Также компания представила компоненты NVIDIA LinkX: оптические трансиверы 2xDR4/2xFR4 и активные медные кабели (LACC). Не забыла NVIDIA и про Ethernet: здесь вывести производительность сети на новый уровень должна платформа Spectrum-X800. Её основой служит новейший коммутатор SN5600 — это, по словам NVIDIA, первый в мире Ethernet-коммутатор класса 800GbE, специально разработанный для применения гиперскейлерами в крупных облачных ИИ-комплексах. Применяемая архитектура позволяет гарантировать каждому клиенту оптимальный и постоянный уровень производительности, а потоковая телеметрия позволит находить и ликвидировать возможные «бутылочные горлышки» в сети буквально на лету. Общая пропускная способность SN5600 составляет 51,2 Тбит/с. Коммутатор располагает 64 портами 800GbE в формате OSFP. В нём используется ASIC пятого поколения на базе архитектуры Spectrum-4. В качестве основного адаптера предлагается SuperNIC на базе DPU BlueField-3 с двумя 400GbE-портами. Spectrum-X800 сопровождает полноценный спектр инфраструктурных компонентов, включая кабели DAC и LACC. С оптическими трансиверами длина соединения 800GbE может достигать двух километров. Начиная со следующего года, решения на базе новых сетевых платформ NVIDIA будут доступны от широкого круга поставщиков оборудования, включая Aivres, DDN, Dell Technologies, Eviden, Hitachi Vantara, HPE, Lenovo, Supermicro и VAST Data.

14.03.2024 [23:45], Алексей Степин

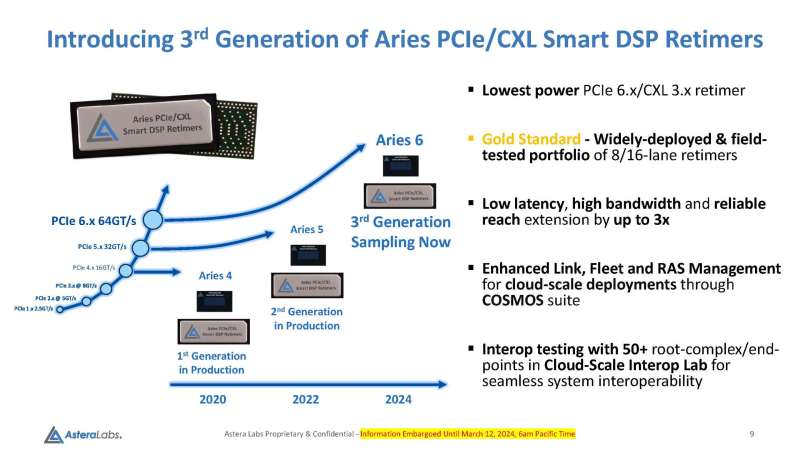

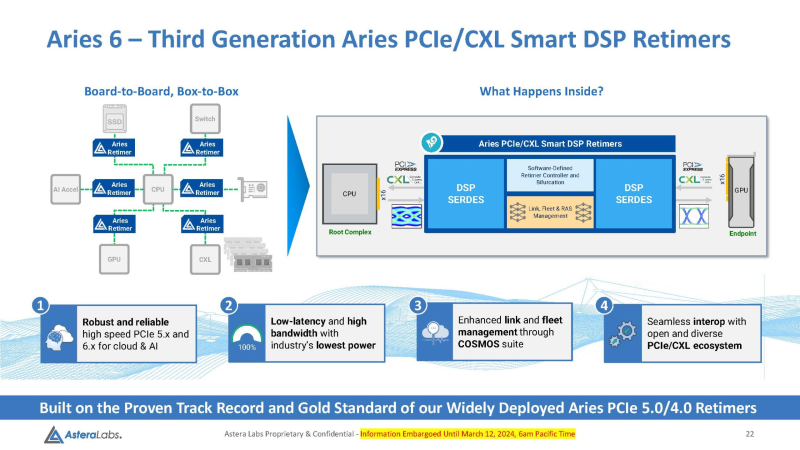

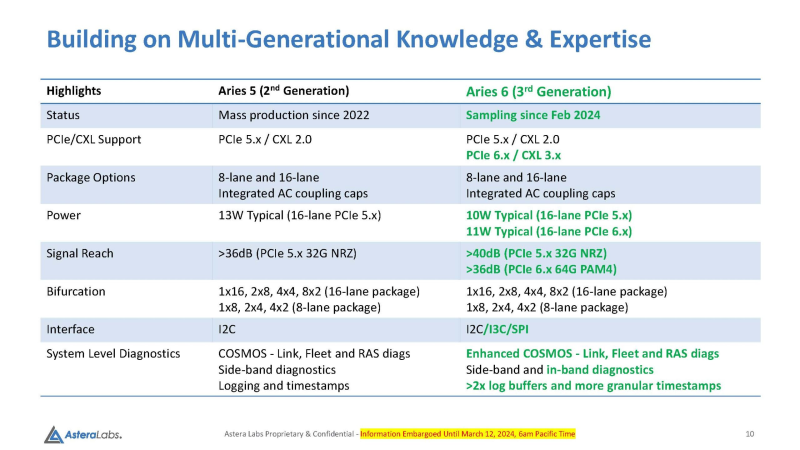

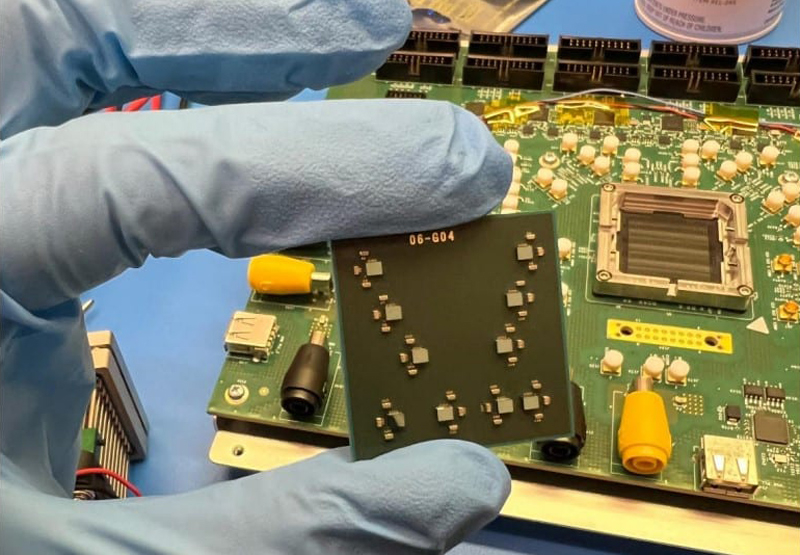

Войны ретаймеров: Astera Labs анонсировала чипы Aries 6 для PCIe 6.0Практически сразу после анонса чипов Broadcom Vantage 5 и 6 Astera представила свой вариант ретаймеров для инфраструктуры PCIe следующего поколения — серию чипов Aries 6, передаёт ServeTheHome. Высокий интерес к ретаймерам вызван теми возможностями, что открывает PCI Express 6.0 как в плане скоростей, так и в плане функциональности (CXL). А переход на новое поколение шины необходим для дальнейшего развития набирающего популярность генеративного ИИ. По мере роста скоростей PCI Express обострялась и проблема длины проводников на печатной плате, при которой сигнал достаточно устойчив и вписывается в окно требуемых характеристик. Если при переходе от PCIe 3.0 к 4.0 удалось обойтись сравнительно малой кровью, то для PCIe 5.0 уже потребовались более сложная схемотехника и более продвинутые ретаймеры. PCIe 6.0 же накладывает ещё более жёсткие требования к целостности сигнала. Платформы GPU-кластеров и СХД компактнее не становятся, так что требуемая длина проводников на печатных платах растёт, а вместе с ней растёт и важность ретаймеров, поскольку без них согласовать высокоскоростной сигнал PCIe 6.0 становится невозможно. Таким системам требуется сразу несколько подобных чипов, причём стоимость каждого из них достигает $20, так что суммарная стоимость этих компонентов на уровне целого ЦОД весьма внушительна. Новые чипы Aries 6 относятся к третьему поколению «умных» DSP-ретаймеров. Они представлены в вариантах с 8 и 16 линиями PCIe 6.0 и позволяют в три раза увеличить длину соответствующего соединения на плате, говорит Astera Labs. При этом новинки поддерживают CXL 3.x и предоставляют расширенные средства диагностики и управления COSMOS. Энергопотребление в режиме PCIe 6.0 при этом заявлено меньше, чем у Broadcom Vantage 6 — 11 Вт против 13 Вт у конкурента. Aries 6 уже протестированы на совместимость с полсотней разнообразных PCIe-соединений, включая root-комплексы и конечные устройства. И если Broadcom пока только говорит о ретаймерах для PCIe 6.0, а появление первого «кремния» Vantage 6 запланировано лишь на следующий год, то Astera Labs начала поставки образцов Aries 6 ещё в феврале. Похоже, Broadcom будет нелегко развернуться на этом рынке.

02.08.2023 [18:00], Сергей Карасёв

Светлое будущее: у PCIe появится версия с оптическими соединениями — создана рабочая группа для разработки технологииКонсорциум PCI-SIG объявил о формировании рабочей группы PCI-SIG Optical Workgroup, которая займётся реализацией интерфейса PCI Express (PCIe) по оптическим соединениям. Это, как ожидается, станет важным этапом развития соответствующей экосистемы. Внедрение оптических соединений для PCIe по сравнению с существующими решениями обеспечит более высокую пропускную способность, пониженное энергопотребление, увеличенную дальность действия и меньшие задержки.

Источник изображения: pixabay.com Новая технология, как ожидается, будет востребована в облачных дата-центрах, системах НРС и на площадках гиперскейлеров. Речь идёт о создании системы, поддерживающей широкий спектр оптических технологий. Консорциум PCI-SIG призывает всех своих участников присоединиться к Optical Workgroup, поделиться опытом и помочь определить конкретные цели рабочей группы и требования к аппаратным компонентам. Новая рабочая группа сосредоточит усилия над тем, чтобы сделать архитектуру PCIe более подходящей для оптических сетей. Между тем, как отмечается, продолжаются работы над спецификацией PCIe 7.0, которая предусматривает увеличение производительности до 128 ГТ/с по одной линии.

20.07.2023 [23:30], Игорь Осколков

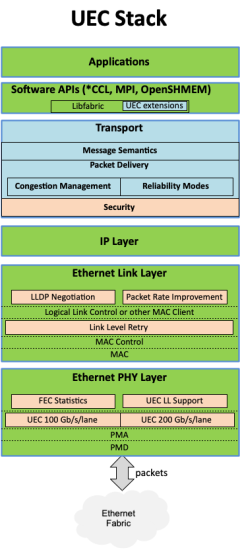

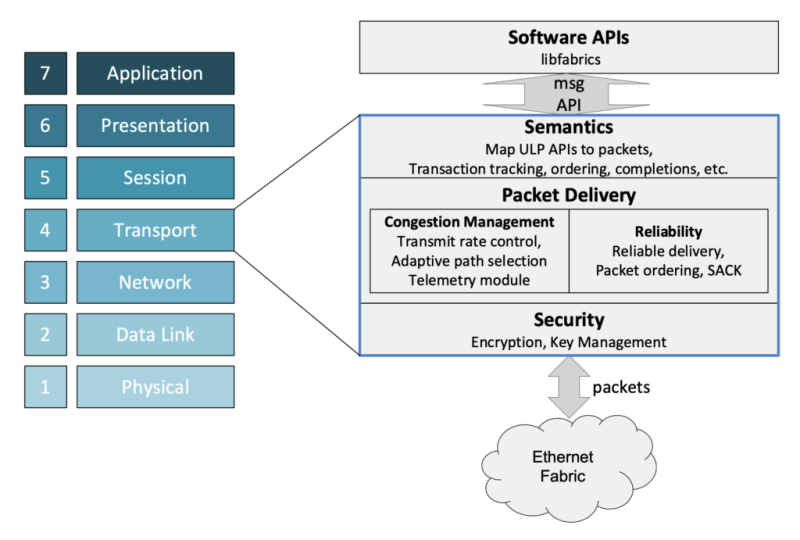

AMD, Broadcom, Cisco, Intel и другие вендоры создадут интерконнект Ultra Ethernet для HPC и ИИAMD, Arista, Broadcom, Cisco, Eviden (Atos), HPE, Intel, Meta✴ и Microsoft в рамках Linux Foundation сформировали новый консорциум Ultra Ethernet Consortium, который намерен создать на базе Ethernet новый масштабируемый и эффективный с точки зрения стоимости коммуникационный стек, ориентированный на высокопроизводительные вычисления (HPC) и ИИ. Иными словами, речь идёт о создании спецификаций интерконнекта нового поколения на базе Ethernet для современных кластеров, облаков и иных платформ. UEC сформировал четыре рабочих группы, ответственных за физический, канальный и транспортный уровни, а также за уровень ПО. Целью же является создание современного сетевого стека, который учитывает потребности HPC- и ИИ-нагрузок, включая новые методы борьбы с заторами в сети, высокий уровень утилизации канала (в том числе 800G/1.6T), многопутевую и гарантированную доставку, сквозную телеметрию, консистентность и низкий уровень задержек, автоматизацию, безопасность и защищённость, масштабируемость, стабильность, надёжность, снижение TCO и так далее. Фактически отдельные вендоры уже наделили рядом перечисленных свойств свои продукты, однако унификация и объединение усилий, как считается, должны пойти на пользу всем. Всем, кроме, по-видимому, NVIDIA, которой в списке основателей UEC нет (как и Marvell, к слову). NVIDIA после поглощения Mellanox фактически стала монополистом на рынке InfiniBand, который она активно продвигает, не забывая, впрочем, и о своём проприетарном интерконнекте NVLink, который в последней своей версии выбрался за пределы узла. Справедливости ради — про Ethernet компании тоже не забывает. В обзоре UEC аккуратно критикуется и InfiniBand, и его адаптация в виде RoCE. Авторы указывают на правильность и успешность идеи RDMA, но жалуются на не слишком высокую практичность и удобство современных реализаций. И именно поэтому они первым делом предлагают внедрить новый транспортный протокол Ultra Ethernet Transport (UET), который и позволит реализовать интерконнект будущего, а заодно ещё раз доказать эффективность и гибкость технологии Ethernet, которой в этом году исполнилось 50 лет. Впрочем, это только один из кирпичиков UEC. Примечательно, что первые продукты на базе новых спецификаций обещали показать уже в 2024 году. |

|