Материалы по тегу: epyc

|

13.08.2024 [11:19], Сергей Карасёв

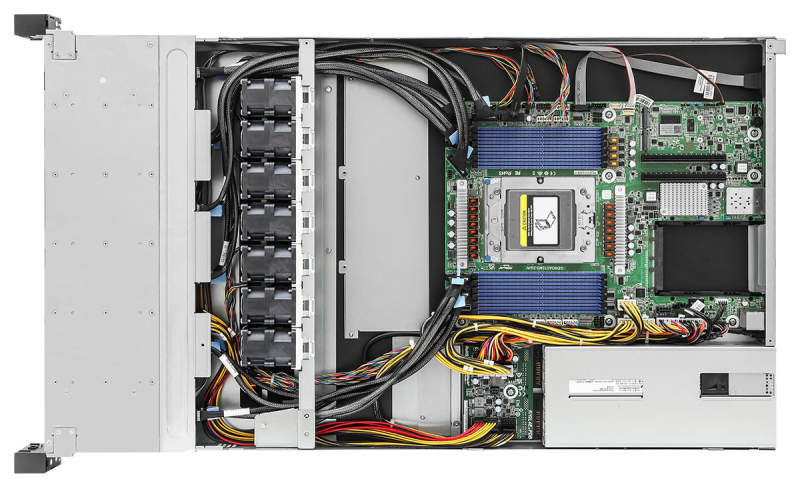

MSI представила сервер S2301 с поддержкой CXL на базе AMD EPYC TurinКомпания MSI в ходе выставки Future of Memory and Storage 2024 (FMS) анонсировала сервер S2301, предназначенный для работы с резидентными базами данных, НРС-приложениями, платформами для автоматизации проектирования электроники (EDA) и пр. Сервер поддерживает стандарт CXL 2.0 на основе интерфейса PCIe. Технология обеспечивает высокоскоростную передачу данных с малой задержкой между хост-процессором и такими устройствами, как серверные ускорители, буферы памяти и интеллектуальные IO-блоки. На основе CXL 2.0 функционирует высокопроизводительный механизм доступа к памяти, который позволяет модулям расширения напрямую взаимодействовать с иерархией памяти CPU. При этом дополнительные блоки памяти работают так, как если бы они были частью собственной памяти системы. Подключив к серверу модули расширения CXL, можно с высокой эффективностью масштабировать ресурсы для обработки сложных задач. Сервер MSI S2301 поддерживает установку двух процессоров AMD EPYC поколения Turin. Доступны 24 слота для модулей ОЗУ. Возможно применение CXL-модулей в форм-факторе E3.S 2T (PCIe 5.0 x8). Такие решения, в частности, в августе 2023 года представила компания Micron Technology. Устройства имеют вместимость 128 и 256 Гбайт. Кроме того, память DRAM с поддержкой CXL 2.0 предлагает Samsung. Во фронтальной части нового сервера располагаются отсеки для SFF-модулей. Говорится об использовании софта Memory Machine X разработки MemVerge, который оптимизирует затраты и помогает улучшить производительность ИИ-приложений и других ресурсоёмких рабочих нагрузок путём интеллектуального управления памятью.

25.07.2024 [10:12], Владимир Мироненко

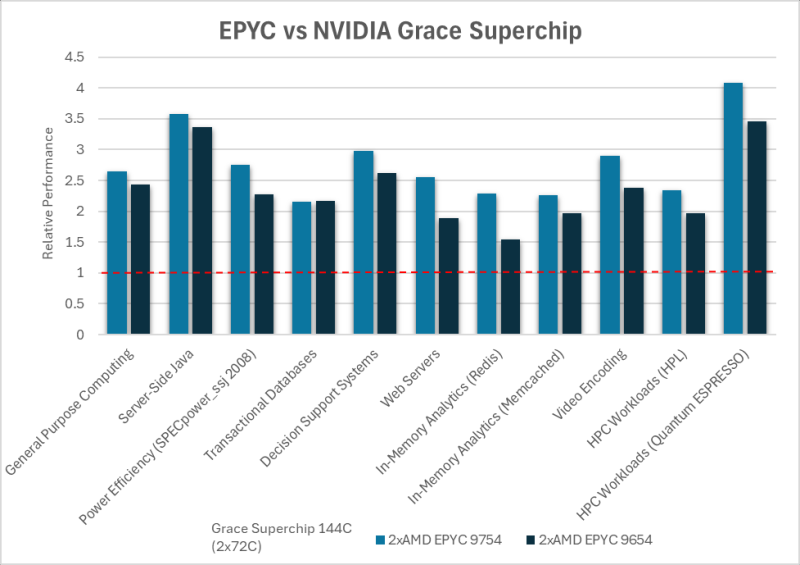

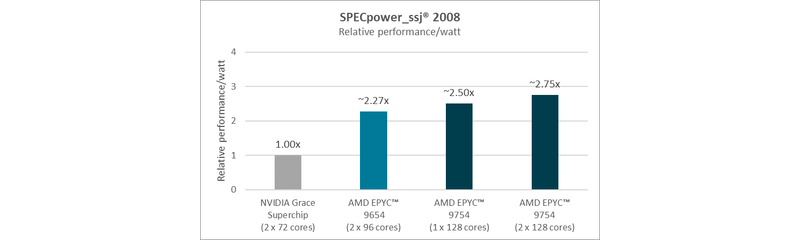

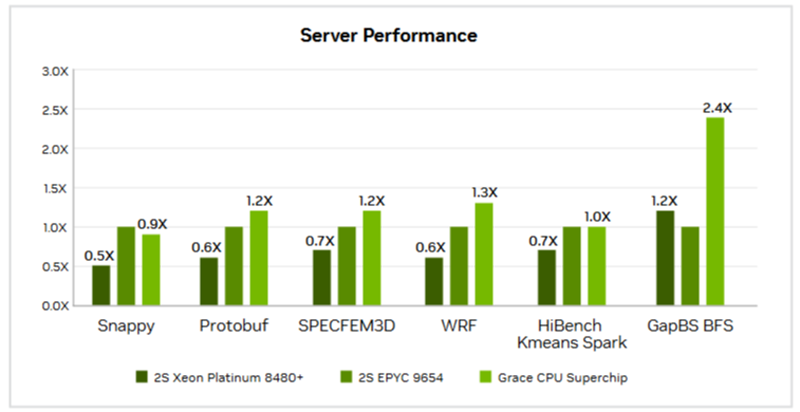

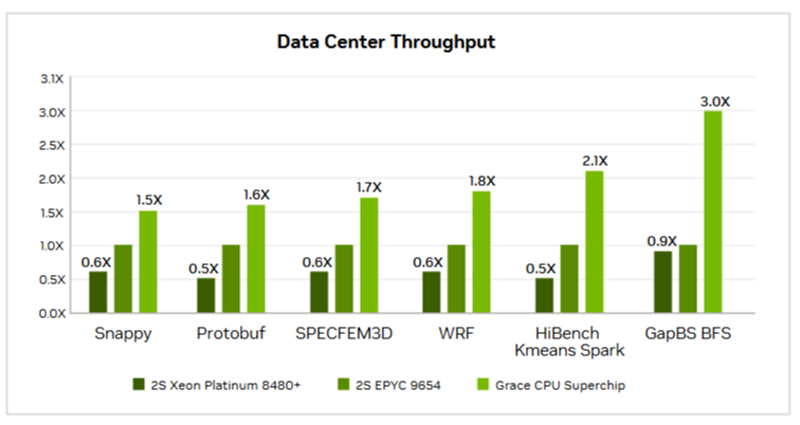

AMD показала превосходство чипов EPYC над Arm-процессорами NVIDIA Grace в серии бенчмарков, но не всё так простоAMD провела серию тестов, чтобы доказать преимущество своих нынешних процессоров AMD EPYC над Arm-процессорами NVIDIA Grace Superchip. Как отметила AMD, в связи с растущей востребованностью ЦОД некоторые компании начали предлагать альтернативные варианты процессоров, «часто обещающие преимущества по сравнению с обычными решениями x86». «Обычно их представляют с большой помпой и заявлениями о значительных преимуществах в производительности и энергоэффективности по сравнению с x86. Слишком часто эти утверждения довольно сложно воплотить в реальные сценарии конкурентной рабочей нагрузки — с использованием устаревших, недостаточно оптимизированных альтернатив или плохо документированных предположений», — отметила AMD. С помощью серии стандартных отраслевых тестов AMD, по её словам, продемонстрировала преимущество EPYC над решениями на базе Arm. «Благодаря проверенной архитектуре x86-64, впервые разработанной AMD, вы можете получить всё это без дорогостоящего портирования или изменений в архитектуре», — подчеркнула компания. Иными словами, тесты AMD могут быть просто попыткой развеять опасения, что архитектура x86 «выдыхается» и что Arm берёт верх. AMD сравнила производительность AMD EPYC и NVIDIA Grace CPU в десяти ключевых рабочих нагрузках, охватывающих вычисления общего назначения, Java, транзакционные базы данных, системы поддержки принятия решений, веб-серверы, аналитику, кодирование видео и нагрузки HPC. Согласно представленному выше графику, 128-ядерный процессор EPYC 9754 (Bergamo) и 96-ядерный EPYC 9654 (Genoa) более чем вдвое превзошли NVIDIA Grace CPU Superchip по производительности при обработке вышеуказанных нагрузок. Напомним, что Grace CPU Superchip содержит два 72-ядерных кристалла Grace, использующих ядра Arm Neoverse V2, соединённых шиной NVLink C2C с пропускной способность 900 Гбайт/с, и работает как единый 144-ядерный процессор. В свою очередь, ресурс The Register отметил, что речь идёт о версии с 480 Гбайт памяти LPDDR5x, а не с 960 Гбайт.  В тесте SPECpower-ssj2008, по данным AMD, одно- и двухсокетные системы на базе AMD EPYC 9754 превосходят систему NVIDIA Grace CPU Superchip по производительности на Вт примерно в 2,50 раза и 2,75 раза соответственно, а двухсокетная система AMD EPYC 9654 — примерно в 2,27 раза. Помимо производительности и эффективности, ещё одним важным фактором для операторов ЦОД является совместимость, сообщила AMD. По оценкам, во всем мире существуют триллионы строк программного кода, большая часть которого написана для архитектуры x86. EPYC основаны на архитектуре x86-64, впервые разработанной AMD, и эта архитектура является наиболее широко используемой и поддерживаемой в индустрии ЦОД, заявила компания, добавив, что изменения в архитектуре сложны, дороги и чреваты риском. AMD также отметила, что экосистема AMD EPYC включает более 250 различных конструкций серверов и поддерживает около 900 уникальных облачных инстансов. Также процессоры AMD EPYC установили более 300 мировых рекордов производительности и эффективности в широком спектре тестов. В то же время лишь немногие Arm-решения доказали свою эффективность. В свою очередь, ресурс The Register отметил, что ситуация не так проста, как AMD пытается всех убедить. В феврале сайт The Next Platform сообщил, что исследователи из университетов Стоуни-Брук и Буффало сравнили данные о производительности суперчипа NVIDIA Grace CPU Superchip и нескольких процессоров x86, предоставленные несколькими НИИ и разработчиком облачных решений.

Источник изображений: NVIDIA Большинство этих тестов были ориентированы на HPC, включая Linpack, HPCG, OpenFOAM и Gromacs. И хотя производительность системы Grace сильно различалась в разных тестах, в худшем случае она находилась где-то между Intel Skylake-SP и Ice Lake-SP, превосходя AMD Milan и находясь в пределах досягаемости от показателей Xeon Max. Данные результаты отражают тот факт, что самые мощные процессоры AMD EPYC Genoa и Bergamo могут превзойти первый процессор NVIDIA для ЦОД — при правильно выбранном тесте.  В техническом описании Grace CPU Superchip компания NVIDIA сообщает, что этот чип обеспечивает от 0,9- до 2,4-кратного увеличения производительности по сравнению с двумя 96-ядерными EPYC 9654 и предлагает до трёх раз большую пропускную способность в различных облачных и HPC-сервисах. NVIDIA отмечает, что Superchip предназначен для «обработки массивов для получения интеллектуальных данных с максимальной энергоэффективностью», говоря об ИИ, анализе данных, нагрузках облачных гиперскейлеров и приложениях HPC.

24.07.2024 [10:58], Сергей Карасёв

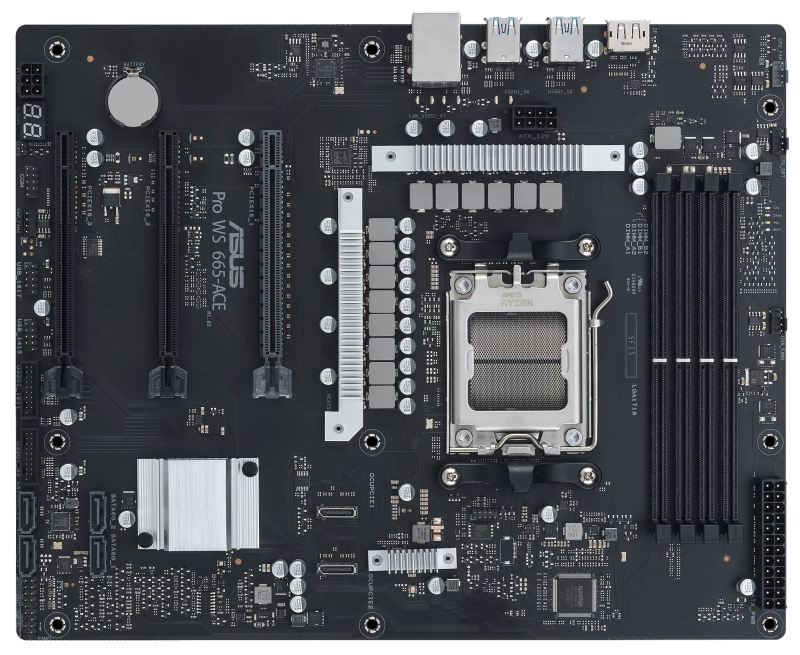

ASUS представила плату Pro WS 665-ACE для рабочих станций с ИИ на базе AMD EPYC 4004Компания ASUS анонсировала материнскую плату Pro WS 665-ACE, предназначенную для построения рабочих станций, рассчитанных на работу с приложениями ИИ. Новинка, выполненная в форм-факторе АТХ, допускает установку одного процессора AMD EPYC 4004 в исполнении AM5. Плата располагает четырьмя разъёмами для модулей оперативной памяти DDR5. Реализована фирменная технология OptiMem II: оптимизированная разводка слотов способствует снижению перекрёстных наводок и улучшает целостность сигнала, что обеспечивает стабильную работу даже при использовании памяти с высокой частотой. Для подключения накопителей доступны четыре порта SATA-3. Предусмотрены два разъёма OCuLink (PCIe 4.0 x4), а также три слота PCIe 4.0 x16. Применён сетевой контроллер Intel I225-LM с поддержкой 2.5GbE. Плата поставляется с программным обеспечением ASUS Control Center Express, которое предназначено для эффективного централизованного управления компьютерной инфраструктурой на базе корпоративных и коммерческих продуктов через удобный пользовательский интерфейс. У модели Pro WS 665-ACE процессорный разъём развёрнут на 90°. Отмечается, что новинку можно применять в серверах начального уровня для дата-центров и облачных платформ. Компания ASUS также представила ряд других продуктов с поддержкой чипов AMD EPYC 4004. В их число вошли сервер Pro ER100A B6 формата 1U, рабочая станция ExpertCenter Pro ET500A B6 с поддержкой памяти DDR5-5200 и двумя коннекторами для накопителей M.2, компактная материнская плата Pro WS 600M-CL.

19.07.2024 [10:10], Сергей Карасёв

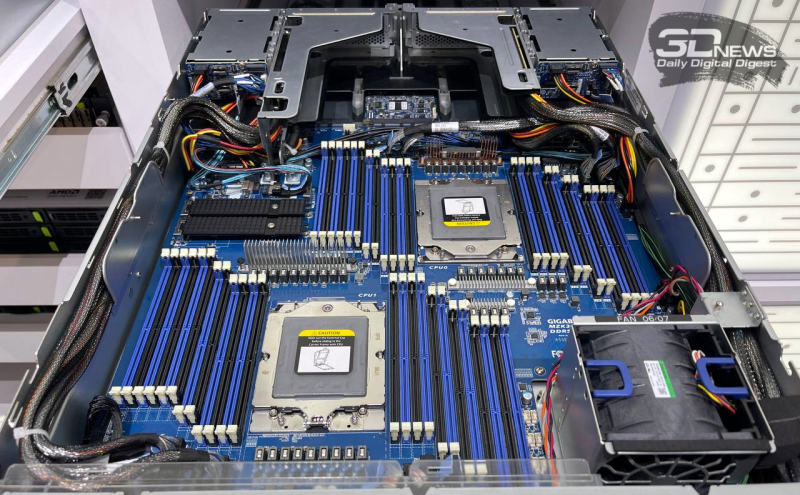

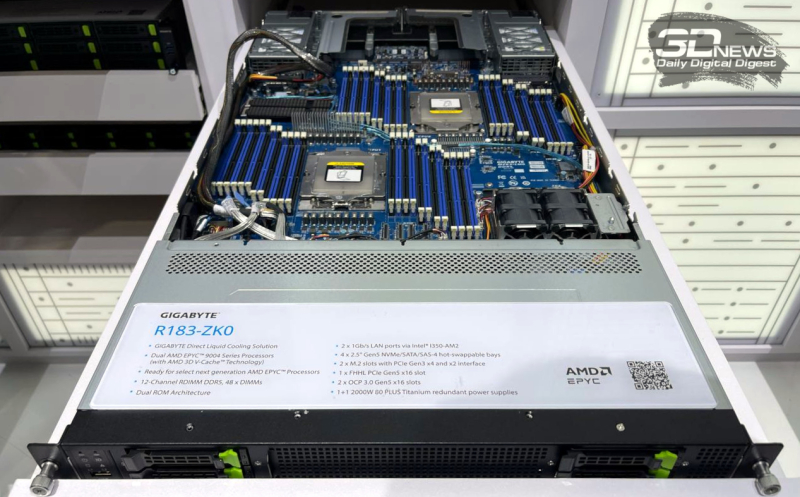

48 слотов DIMM в стандартном корпусе: EPYC-серверы Gigabyte R283-ZK0 и R183-ZK0 предлагают высокоплотное размещение DDR5Компания Gigabyte, по сообщению ресурса Tom's Hardware со ссылкой на ServeTheHome, готовит к выпуску двухпроцессорный сервер R283-ZK0 типоразмера 2U на аппаратной платформе AMD EPYC Genoa. Особенность данной модели заключается в наличии 48 слотов (24 на процессор) для модулей оперативной памяти DDR5, размещённых в уникальной конфигурации. Сервер допускает установку двух чипов в исполнении SP5: в частности, говорится о возможности использования изделий со 128 ядрами (256 потоков) с показателем TDP до 300 Вт. Из-за ограниченного пространства внутри корпуса сформировать систему с 12 каналами DDR5 на процессорный сокет, располагая слоты ОЗУ рядом друг с другом, оказалось невозможно. Поэтому соответствующие разъёмы на материнской плате Gigabyte MZK3-LM0 выполнены лесенкой: с одной стороны каждого процессора они имеют трёхступенчатую конфигурацию 6-2-4, с другой — четырёхступенчатую вида 4-2-2-4. Таким образом, удалось расположить 48 слотов DDR5 в стандартном форм-факторе 2U. Сервер R283-ZK0 оснащён восемью фронтальными отсеками для SFF-накопителей NVMe, четырьмя посадочными местами для SFF-устройств в тыльной части и двумя внутренними коннекторами М.2. Есть четыре слота FHHL для карт расширения с интерфейсом PCIe 5.0 x16, два слота OCP 3.0 и два порта 1GbE. За питание отвечают два блока мощностью 2700 Вт с сертификатом 80 Plus Titanium. Прочие характеристики сервера и сроки его поступления в продажу пока не раскрываются. Нужно отметить, что Gigabyte также готовит схожую модель R183-ZK0 в форм-факторе 1U, которая отличается от 2U-версии наличием всего четырёх слотов SFF NVMe, одного слота FHHL и БП мощностью 2000 Вт.

27.06.2024 [12:58], Сергей Карасёв

В Японии запущен суперкомпьютер TSUBAME4.0 с ускорителями NVIDIA H100 для ИИ-задачГлобальный научно-информационный вычислительный центр (GSIC) Токийского технологического института (Tokyo Tech) в Японии объявил о вводе в эксплуатацию вычислительного комплекса TSUBAME4.0, созданного компанией HPE. Новый суперкомпьютер будет применяться в том числе для задач ИИ. В основу машины легли 240 узлов HPE Cray XD665. Каждый из них несёт на борту два процессора AMD EPYC Genoa и четыре ускорителя NVIDIA H100 SXM5 (94 Гбайт HBM2e). Объём оперативной памяти DDR5-4800 составляет 768 Гбайт. Задействован интерконнект Infiniband NDR200. Вместимость локального накопителя NVMe SSD — 1,92 Тбайт. В состав НРС-комплекса входит подсистема хранения данных HPE Cray ClusterStor E1000. Сегмент на основе HDD имеет ёмкость 44,2 Пбайт — это в 2,8 раза больше по сравнению с суперкомпьютером предыдущего поколения TSUBAME 3.0. Кроме того, имеется SSD-раздел ёмкостью 327 Тбайт. Пиковая производительность TSUBAME4.0 достигает 66,8 Пфлопс (FP64), что в 5,5 больше по отношению к системе третьего поколения. Быстродействие на операциях половинной точности (FP16) поднялось в 20 раз по сравнению с TSUBAME3.0 — до 952 Пфлопс.

Источник изображения: Tokyo Tech На сегодняшний день TSUBAME4.0 является вторым по производительности суперкомпьютером в Японии после Fugaku. Эта система в нынешнем рейтинге TOP500 занимает четвёртое место с показателем 442 Пфлопс. Лидером в мировом масштабе является американский комплекс Frontier — 1,21 Эфлопс.

17.06.2024 [08:53], Руслан Авдеев

Cerebras и Dell предложат заказчикам современные ИИ-платформыРазработчик ИИ-суперчипов Cerebras Systems анонсировал сотрудничество с Dell. Вместе компании займутся созданием передовых вычислительных инфраструктур для генеративного ИИ. В рамках сотрудничества будут создаваться масштабируемые решения для ИИ-суперкомпьютеров Cerebras с платформами Dell на базе процессоров AMD EPYC Genoa. По словам участников проекта, новые технологические решения дадут возможность обучать модели, на порядки более крупные, чем те, что есть на данный момент. В частности, будут задействованы системы Dell PowerEdge R6615 на базе AMD EPYC 9354P, которые предоставят потоковый доступ к 82 Тбайт памяти — для обучения моделей практически любого размера. Совместные платформы Cerebras и Dell будут включать ИИ-системы и суперкомпьютеры. Также будет предложена тренировка ИИ-моделей и иные сервисы поддержки машинного обучения. Как утверждают в самой Cerebras, сотрудничество с Dell станет поворотной точкой, открывающие каналы глобальной дистрибуции. Компании предоставят ИИ-оборудование, ПО и экспертизу, что позволит заказчикам упростить и ускорить внедрении современных ИИ-технологий, попутно снизив TCO. В марте Cerebras представила новейшие суперчипы Cerebras WSE-3, а в мае появилась новость, что совместно с Core42 из ОАЭ компания создаст суперкомпьютер Condor Galaxy 3 (CG-3) со 172,8 млн ИИ-ядер.

15.06.2024 [00:25], Алексей Степин

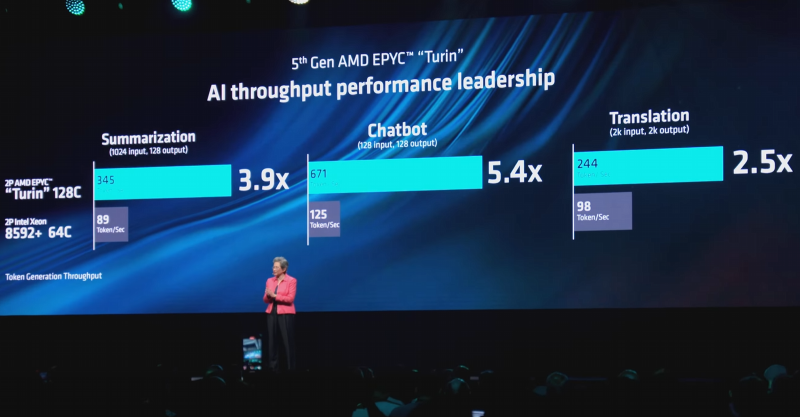

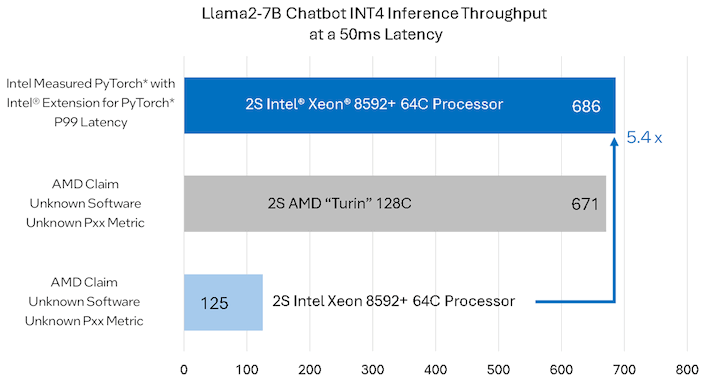

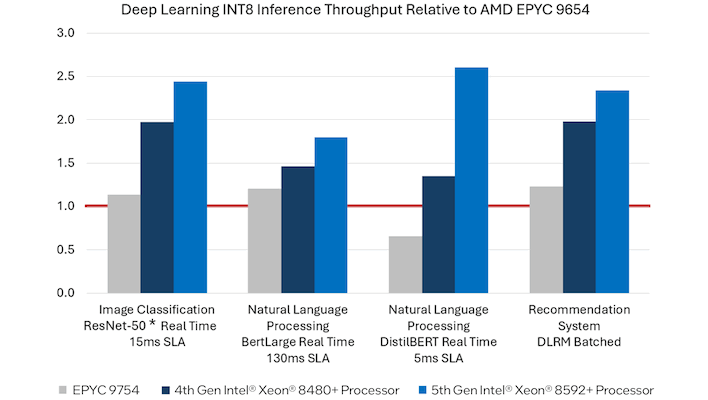

Intel поймала AMD на подтасовке результатов в ИИ-тестах EPYC против XeonНа Computex 2024 AMD анонсировала новое поколение серверных процессоров EPYC Turin на базе архитектуры Zen 5. При этом компания продемонстрировала слайды, из которых следует, что новые решения серьёзно опережают процессоры Intel Xeon. Так, 128-ядерный Turin сравнивается с 64-ядерным Xeon Platinum 8592+ (Emerald Rapids). AMD говорит о 2,5–5,4-кратном превосходстве, однако Intel опровергает полученные результаты и достаточно подробно разбирает вопрос тестирования в своём блоге. Конечно, превосходство AMD в чисто количественных показателях очевидно, но в сложных вычислительных задачах, к которым относятся HPC- и ИИ-сценарии, не меньшую, а то и большую роль может играть оптимизация ПО. Intel отмечает, что AMD не привела в своём анонсе конкретных сведений о версиях и настройках ПО, и, вероятнее всего, отказалась от различных расширений. Но, например, Intel Extension for PyTorch (IPEX) позволяет добиться более чем пятикратного прироста производительности по сравнению с «чистой» версией PyTorch. Для системы с двумя Xeon Platinum 8592+ применение IPEX позволяет поднять производительность инференса в режиме INT4 с чат-ботом на базе Llama2-7B со 127 до 686 запросов в секунду при заданной задержке не более 50 мс. Для своей 256-ядерной платформы на базе Turin AMD говорит про 671 запрос — как видно, с оптимизацией результаты получаются вполне сопоставимыми. И потенциал для дальнейшего роста у Xeon есть: Intel сообщает, что при отключении функции Sub-NUMA Clustering результат может достигать 740 запросов. К сожалению, для других тестов компания диаграмм не опубликовала, хотя и там оптимизация позволяет добиться увеличения производительности в 1,2–2,3 раза. Этого уже не хватает, чтобы бороться с платформой Turin, которая, помимо превосходства в числе ядер, использует и более мощную 12-канальную подсистему памяти.

Источник: Intel Следует отметить, что Intel не сказала последнего слова: Xeon Platinum 8592+ уже не нов, а в ближайшем будущем AMD Turin придётся столкнуться с Xeon 6 с большим числом ядер. Пока эти чипы доступны лишь в исполнении с энергоэффективными ядрами, но уже в III квартале появятся и 128-ядерные Granite Rapids с производительными P-ядрами и 12-канальной памятью.

Источник: Intel Тем не менее, тема затронута достаточно фундаментальная: свои плюсы имеет как чисто количественный подход, которого придерживается AMD, так и подход Intel, позволяющий добиться высоких результатов при тщательной оптимизации под более комплексную архитектуру. Нельзя сказать, что результаты AMD являются мошенничеством, хотя случай и не первый — согласно тестам компании, ускоритель Instinct MI300X серьёзно опередил NVIDIA H100, но при этом AMD точно так же «забыла» про оптимизированный фреймворк TensorRT-LLM. Правда, в тот раз «честь мундира» отстоять удалось и с оптимизациями NVIDIA.

06.06.2024 [13:37], Сергей Карасёв

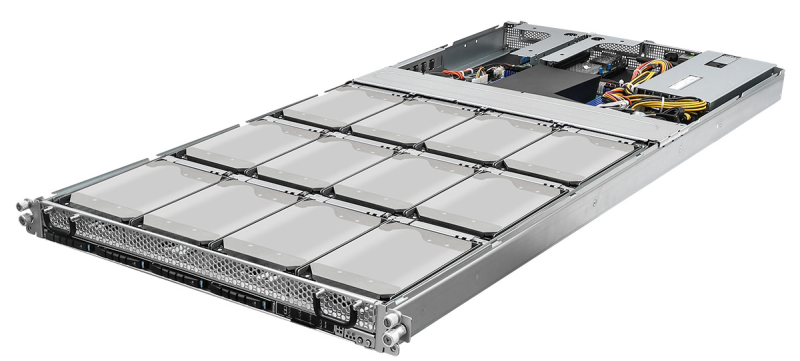

QCT анонсировала серверы QuantaGrid на базе AMD EPYC 9004 для ИИ и НРСКомпания Quanta Cloud Technology (QCT) представила серверы семейства QuantaGrid на аппаратной платформе AMD EPYC 9004 (Genoa). Новинки предназначены для облачных приложений, задач ИИ и НРС. В частности, дебютировали модели QuantaGrid S44NL-1U и QuantaGrid D44N-1U типоразмера 1U. Они рассчитаны на установку соответственно одного и двух процессоров EPYC 9004 с показателем TDP до 400 Вт. Доступны 24 слота для модулей оперативной памяти DDR5-4800. В зависимости от варианта исполнения возможно использование 12 накопителей SFF NVMe/SATA/SAS SSD или 12/16 устройств E1.S NVMe SSD. Опционально могут монтироваться два модуля M.2 2230/2280 с интерфейсом PCIe 3.0.

Источник изображений: QCT Слоты расширения могут быть выполнены по схеме 3 × PCIe 5.0 x16 HHHL и 2 × PCIe 5.0 x16 OCP 3.0 SFF, 2 × PCIe 5.0 x16 HHHL и 2 × PCIe 5.0 x16 OCP 3.0 SFF или 2 × PCIe 5.0 x16 FHHL и 2 × PCIe 5.0 x16 OCP 3.0 SFF. Доступен выделенный сетевой порт управления 1GbE. В оснащение входит контроллер AST2600. Допускается развёртывание системы жидкостного охлаждения. Питание обеспечивают два блока с сертификатом 80 PLUS Titanium мощностью до 1600 Вт у младшей версии и до 2000 Вт у старшей.  Кроме того, представлен мощный сервер QuantaGrid D74A-7U формата 7U. Он рассчитан на два процессора EPYC 9004 с TDP до 400 Вт. Во фронтальной части находятся 18 отсеков для SFF-накопителей NVMe. В максимальной конфигурации могут быть задействованы восемь ускорителей в составе платы NVIDIA HGX H100. Реализованы два слота PCIe 5.0 x16 OCP 3.0 SFF и десять слотов PCIe 5.0 x16 OCP 3.0 TSFF. В оснащение включён выделенный сетевой порт управления 1GbE.

05.06.2024 [11:41], Сергей Карасёв

ASRock Rack представила свой первый GPU-сервер на базе AMD Instinct MI300XКомпания ASRock Rack анонсировала систему 6U8M-GENOA2 — свой первый GPU-сервер, оснащённый ускорителями AMD Instinct MI300X. Кроме того, дебютировали новые решения на платформе AMD EPYC 9004 (Genoa) — модели 1U12E-GENOA/EVAC и 1U12L4E-GENOA/2Q. Характеристики 6U8M-GENOA2 полностью пока не раскрываются. Известно, что новинка выполнена в форм-факторе 6U с применением процессоров EPYC 9004. Допускается установка до восьми ускорителей Instinct MI300X, соединённых между собой посредством Infinity Fabric. Общий объём высокопроизводительной памяти HBM3 может достигать 1,5 Тбайт. Сервер ориентирован на приложения генеративного ИИ, задачи НРС и пр. В свою очередь, 1U12E-GENOA/EVAC — это сервер в форм-факторе 1U, предназначенный для построения СХД типа All-Flash. Он допускает установку одного чипа AMD EPYC в исполнении SP5 с показателем TDP до 360 Вт. Доступны 12 слотов для модулей DDR5-4800. Поддерживается использование до 12 накопителей SFF NVMe (PCIe 5.0 x4), а также двух SSD типоразмера М.2 22110/2280/2260 с интерфейсом PCIe 5.0 x4 или SATA-3. Есть два разъёма для карт расширения FHHL PCIe 5.0 x16 и один слот OCP NIC 3.0 (PCIe 5.0 x16). Питание обеспечивают два блока мощностью 1600 Вт с сертификатом 80 PLUS Platinum. Модель 1U12L4E-GENOA/2Q также представляет собой сервер хранения типоразмера 1U. Он может быть оснащён одним чипом AMD EPYC 9004 с TDP до 300 Вт и 12 модулями DDR5-4800. Есть 12 посадочных мест для LFF-накопителей с интерфейсом SATA-3 и четыре посадочных места для SFF-изделий NVMe (PCIe 4.0 x4). Кроме того, предусмотрены два коннектора для SSD стандарта М.2 22110/2280/2260 с интерфейсом PCIe 5.0 x4 или SATA-3. Задействованы два блока питания на 1000 Вт. Есть по одному слоту для карт FHHL PCIe 5.0 x16, HHHL PCIe 5.0 x16 и OCP NIC 3.0 (PCIe 5.0 x16).

03.06.2024 [23:30], Алексей Степин

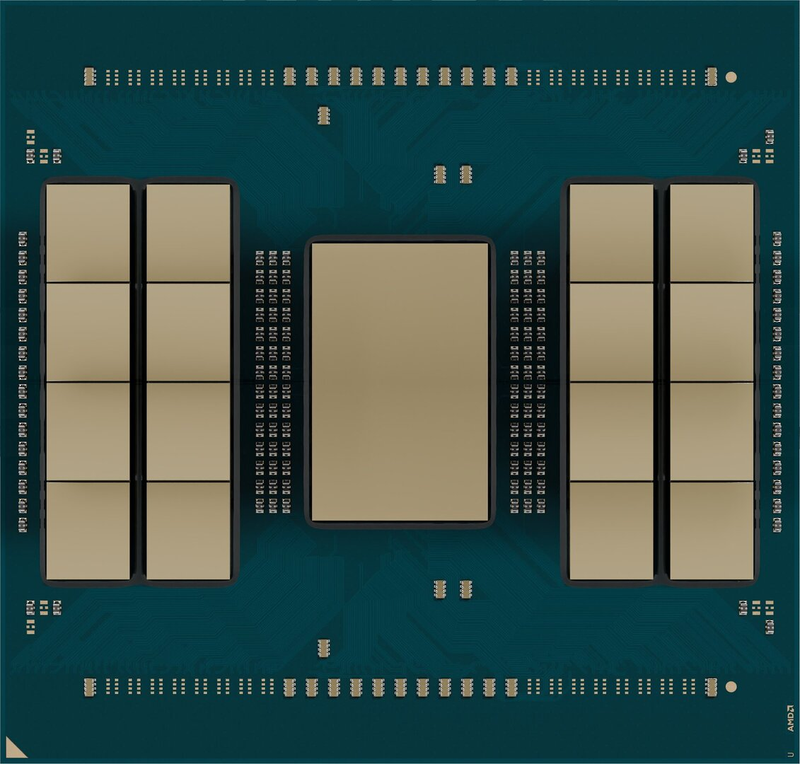

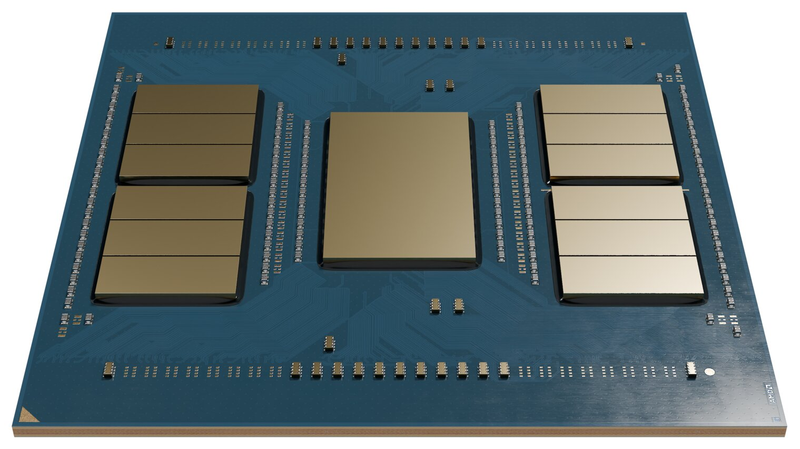

Поплотнее и попроще: AMD EPYC Turin получат до 128 ядер Zen 5 и до 192 ядер Zen 5cAMD продолжает прочно удерживать первенство по плотности упаковки ядер среди процессоров с архитектурой x86. Сегодня компания показала чипы EPYC Turin, которые увидят свет в двух вариантах — обычном, идущим на смену Genoa, и высокоплотном (Dense), который должен будет заменить Bergamo и конкурировать с Intel Xeon 6 (Sierra Forest) на рынке решений для гиперскейлеров и провайдеров облачных услуг. В основу обоих серий лягут архитектуры Zen 5 и Zen 5c соответственно. В текущем поколении EPYC Genoa предлагают 96 ядер Zen 4, а Bergamo — 128 ядер Zen 4c. В поколении Turin количество подрастёт до 128 ядер, а Turin Dense достигнет отметки 192 ядра (384 потока). Компоновка этих процессоров будет различаться.

Источник здесь и далее: ComputerBase.de Классические Turin получат компоновку из 17 чиплетов. Центральное место, как и прежде, займёт чиплет ввода-вывода (IOD), он по-прежнему будет выпускаться с использованием 6-нм техпроцесса. Не изменится даже процессорный разъём, это по-прежнему будет SP5, причём обещана совместимость с уже доступными платформами для Genoa. Чиплеты CCD, расположенные в четыре ряда справа и слева от IOD, переведены на использование техпроцесса N4P, а общее количество 8-ядерных CCD составляет 16, что в пределе и даёт заявленные 128 ядер. По имеющимся сведениям, общий объём кеша достигнет 512 Мбайт.

Turin Dense получит новые высокоплотные 16-ядерные чиплеты Процессоры Turin Dense будут состоять из 13 чиплетов, из них 12 получат по 16 ядер. Достигнуто это как оптимизацией архитектуры, так и применением 3-нм техпроцесса. Относительно компоновки Genoa CCD развёрнуты на 90°, что обеспечивает практически одинаковую длину интерконнекта до IOD. Возможно, это позволит немного сократить латентность. Объём кеша здесь меньше — до 384 Мбайт. Поскольку в обоих вариантах используется если не старый, то как минимум совместимый IOD, то речь по-прежнему идёт о 12-канальной подсистеме памяти DDR5 и 128 линиях шины PCI Express. Возможно, немного подрастёт частота работы модулей DIMM. |

|