Материалы по тегу: risc-v

|

05.03.2025 [23:05], Татьяна Золотова

Российский альянс разработчиков RISC-V запросил у государства поддержкуАльянс российских разработчиков микроэлектроники RISC-V направил премьер-министру Михаилу Мишустину и в Минпромторг письмо с предложением внести технологии на базе открытой процессорной архитектуры RISC-V в приоритетное направление развития нацпроектов и госпрограмм. Об этом сообщает «Коммерсантъ». В России альянс по развитию архитектуры RISC-V был создан осенью 2022 года. В письме перечислены практически все доступные формы господдержки. Помимо включения в нацпроекты альянс просит предоставить субсидии на НИОКР для проектов с архитектурой RISC-V и возмещать затраты на патенты для продукции на базе этой архитектуры. Также альянс хочет, чтобы государство стимулировало производство и экспорт продукции RISC-V, субсидировало затраты на ее внедрение, предусмотрело приоритетную закупку оборудования на базе RISC-V с использованием механизма «второй лишний» в госзакупках (когда при наличии хотя бы одного российского производителя или из ЕАЭС автоматически отклоняются заявки иностранных поставщиков).

Источник изображения: Brian Kostiuk/unsplash.com RISC-V хоть и открытая архитектура, но лицензию предоставляет международный консорциум RISC-V, основанный в США, а значит, он обязана выполнять санкционные требования в отношении России, сообщил «Коммерсанту» эксперт среди разработчиков процессоров, сославшись на ситуацию 2022 года, когда Великобритания ограничила доступ к спецификациям архитектуры Arm, которую использовали последние процессоры «Байкал». Однако головная некоммерческая организация RISC-V International ещё в 2019 году «сменила прописку» на швейцарскую как раз из-за опасений возможных ограничений со стороны Вашингтона. В октябре 2023 года американские власти уже заявляли, что рассматривают возможность ограничить недружественным компаниям участие в международных сообществах RISC-V. Помимо юридических рисков участники рынка микроэлектроники называют монополизацию и снижение технологического суверенитета. Так, в МЦСТ (разрабатывает процессоры «Эльбрус» на собственной архитектуре) считают, что запрошенные альянсом преференции должны применяться ко всем отечественным процессорам при условии, что микропроцессоры и их ядра разрабатываются в России.

01.03.2025 [14:17], Сергей Карасёв

Alibaba выпустила серверный процессор XuanTie C930 с архитектурой RISC-VНаучно-исследовательский институт Damo Academy, подразделение Alibaba Group Holding, по сообщению газеты South China Morning Post, выпустил свой первый процессор для серверов — изделие XuanTie C930, построенное на открытой архитектуре RISC-V. О подготовке названного чипа впервые стало известно в марте прошлого года. Тогда говорилось, что CPU будет использоваться в системах, предназначенных в том числе для работы с ИИ-приложениями. Характеристики XuanTie C930 полностью не раскрываются. Отмечается, что это суперскалярный процессор, который содержит 15-ступенчатый конвейер и поддерживает внеочередное исполнение команд. Заявлена поддержка унифицированного профиля RVA23. В рамках RVA23 предусмотрены такие функции, как векторные операции, обработка данных с плавающей запятой и атомарные инструкции, которые необходимы в том числе при решении ИИ-задач. Отгрузки XuanTie C930 заказчикам начнутся в текущем месяце.

Источник изображения: pconline.com.cn Ранее Damo Academy анонсировала несколько чипов XuanTie с архитектурой RISC-V для различных задач, включая C910 в 2019 году и C920 в 2024-м. В перспективе планируется выпуск процессоров XuanTie C908X, R908A и XL200, которые будут ориентированы соответственно на ИИ-системы, автомобильные приложения и коммуникационное оборудование. Нужно отметить, что Китай активно развивает собственную полупроводниковую промышленность, а одним из приоритетов является направление RISC-V. В 2023 году ведущие китайские RISC-V-разработчики сформировали патентный альянс — China RISC-V Industry Alliance. Разработкой RISC-V-изделий занимаются многие компании и организации из КНР, включая Китайскую академию наук. Создание собственных CPU имеет для страны большое значение в свете усиливающихся санкций со стороны США.

08.02.2025 [16:14], Сергей Карасёв

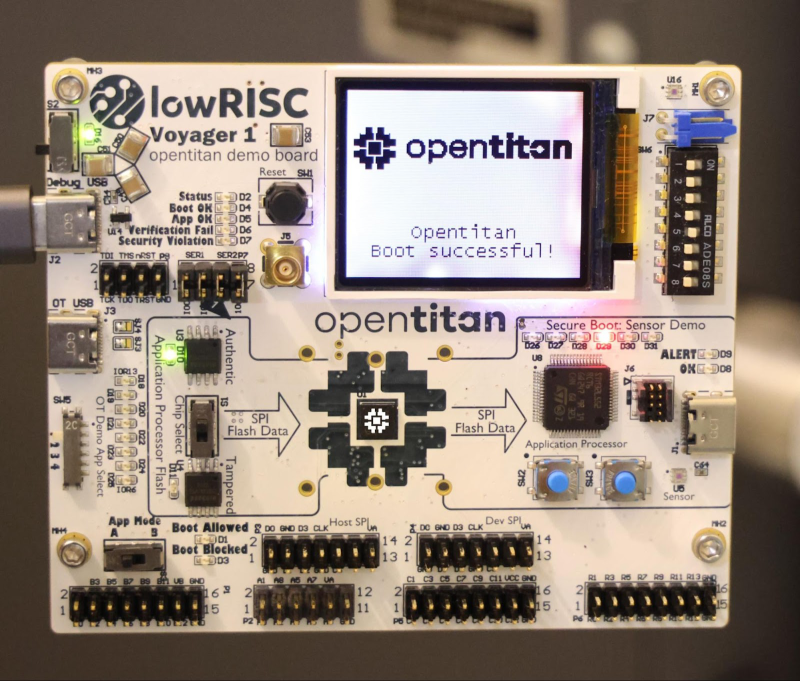

Начато производство первых чипов безопасности на открытой платформе OpenTitanКорпорация Google объявила о начале производства первого чипа, построенного на аппаратной платформе с открытым исходным кодом OpenTitan. Целью инициативы является создание открытой, доступной и надёжной аппаратной реализации Root of Trust (RoT). Проект OpenTitan был начат с нуля в 2018 году. Помимо Google, в нём участвуют Nuvoton, Швейцарская высшая техническая школа Цюриха (ETH Zurich), G+D Mobile Security, lowRISC, Rivos, Seagate, Western Digital, Winbond, zeroRISC и др. Первый чип на базе OpenTitan, пока не получивший определённого названия, изготавливается компанией Nuvoton. Изделие использует архитектуру RISC-V. Отмечается, что в ближайшее время чип станет доступен в составе демонстрационной платы Voyager 1 от lowRISC, а позднее в текущем году появится в хромбуках и решениях для дата-центров. Целью проекта OpenTitan является обеспечение безопасной загрузки критически важных компонентов системы с использованием авторизованного и открытого кода. Чипы OpenTitan могут применяться в самом разном оборудовании — от серверных материнских плат, сетевых карт и маршрутизаторов до потребительских устройств и IoT-продуктов. Google и другие участники инициативы предоставляют исходный код, а также руководства по интеграции и эталонную прошивку. Ожидается, что в перспективе OpenTitan создаст основу, позволяющую повысить уровень доверия к ИТ-платформам и снизить издержки при разработке специализированных чипов для обеспечения безопасности. В настоящее время Nuvoton поставляет образцы изделий OpenTitan для тестирования и оценки, а массовое производство намечено на весну нынешнего года.

04.02.2025 [11:54], Сергей Карасёв

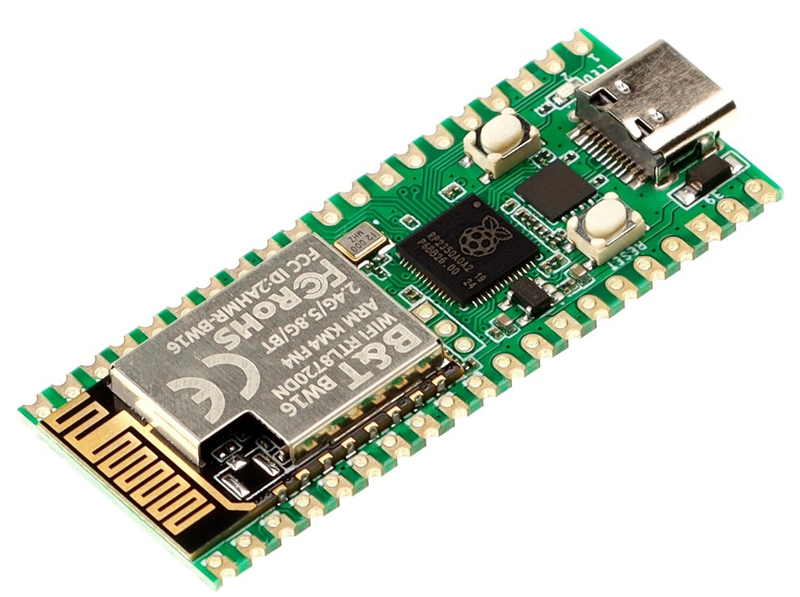

Крошечная плата RP2350-USB-A за $7 оснащена контроллером Raspberry Pi RP2350В продажу, по сообщению ресурса CNX Software, поступила микроплата Waveshare RP2350-USB-A, в основу которой положен микроконтроллер Raspberry Pi. При подключении к хосту изделие может применяться для эмуляции мыши, клавиатуры или другого USB-устройства. Новинка оснащена чипом Raspberry Pi RP2350A (QFN-60; 7 × 7 мм; 30 × GPIO), который объединяет по два ядра Arm Cortex-M33 (с поддержкой Trustzone) и RISC-V Hazard3 с тактовой частотой 150 МГц (в обоих случаях). Но использовать эти кластеры сообща нельзя: одна из двух пар ядер выбирается при инициализации платы. Объём памяти SRAM составляет 520 Кбайт, SPI Flash — 2 Мбайт (для хранения прошивки). Предусмотрены два 9-контактных массива GPIO с поддержкой 2 × UART, 2 × I2C, 2 × SPI, 4 × ADC, 15 × GPIO и пр. Для подачи питания (5 В) и программирования служит порт USB 1.1 Type-C. Имеются кнопки сброса и перезагрузки, а также светодиодный RGB-индикатор. Размеры микроплаты составляют 33 × 17,5 мм. Изделие также получило разъём USB Type-A с программным вводом-выводом (PIO). Это позволяет использовать плату как в качестве USB-устройства, так и в роли хоста. Waveshare предлагает демонстрационные программы на C/C++ и Arduino. Модель RP2350-USB-A доступна для заказа по ориентировочной цене $7. Отметим, что ранее дебютировала мини-плата Pico W5, также выполненная на контроллере Raspberry Pi RP2350. Это решение оборудовано адаптерами Wi-Fi 4 802.11n (частотные диапазоны 2,4 и 5 ГГц) и Bluetooth 5.0 (LE) на основе модуля BW16 (контроллер Realtek RTL8720DN).

20.01.2025 [07:53], Владимир Мироненко

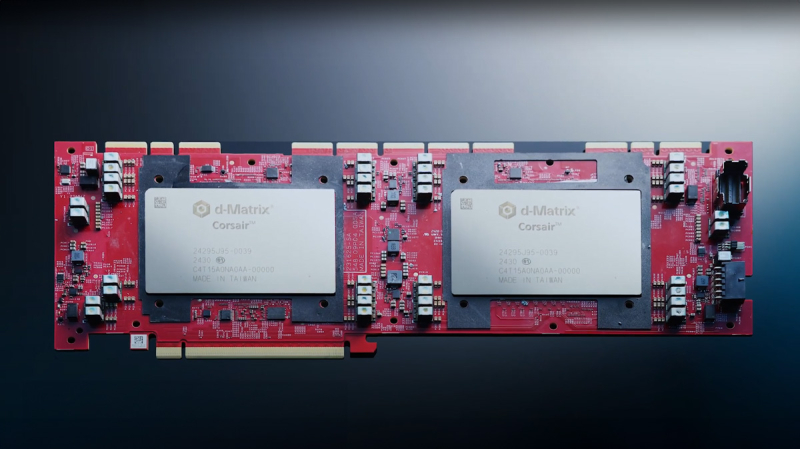

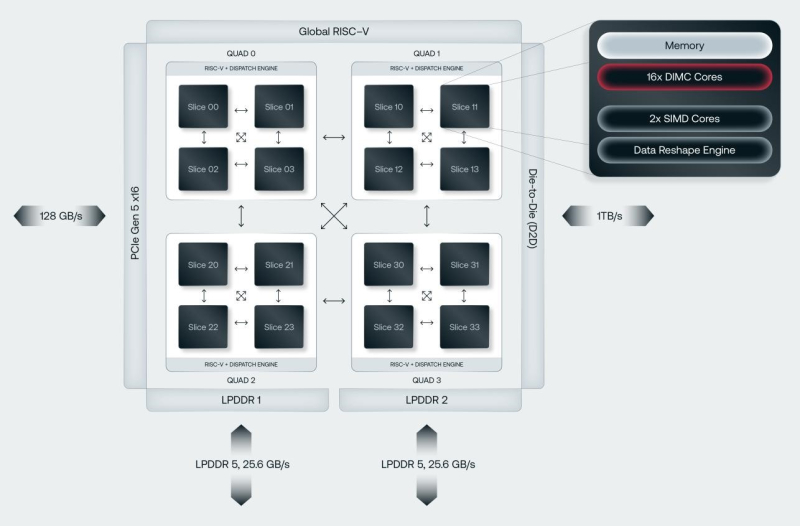

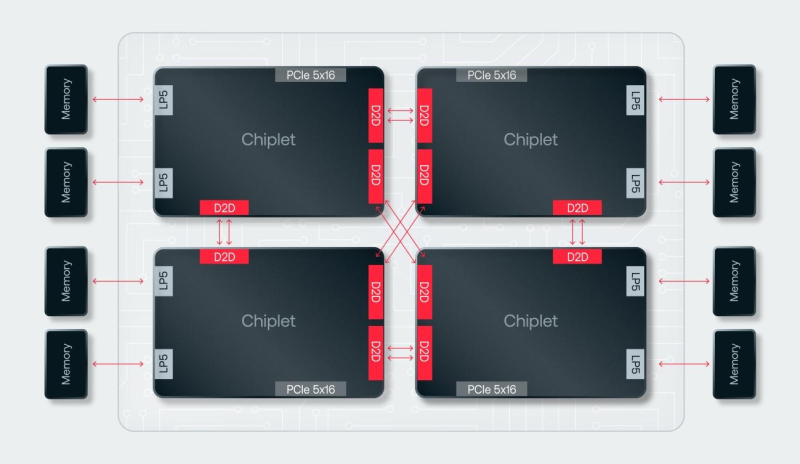

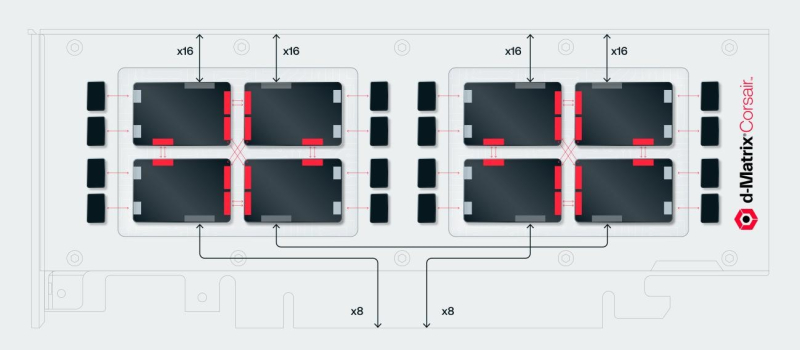

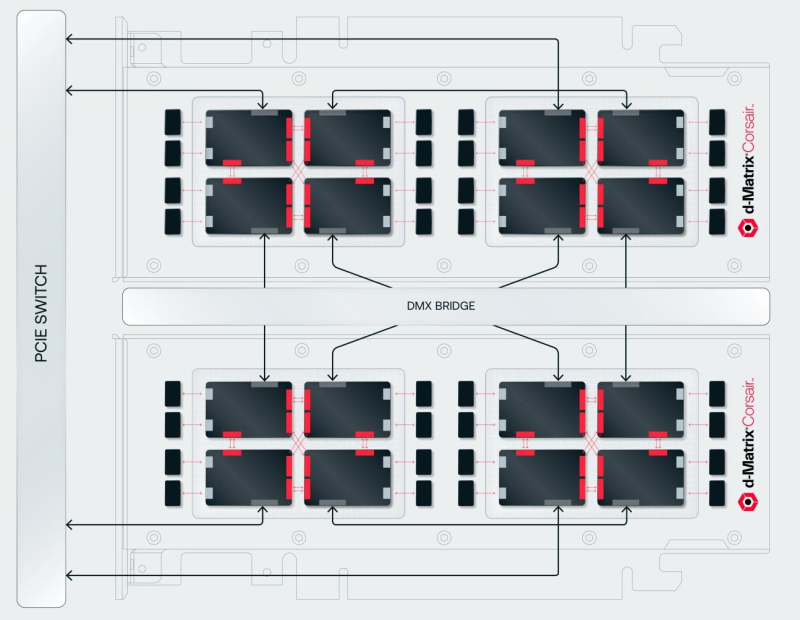

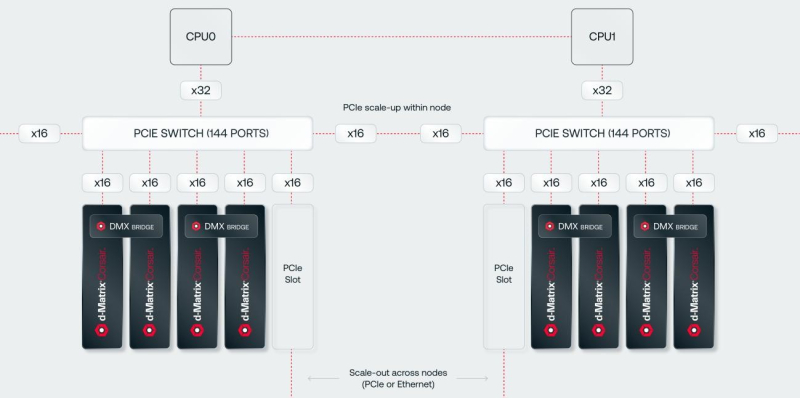

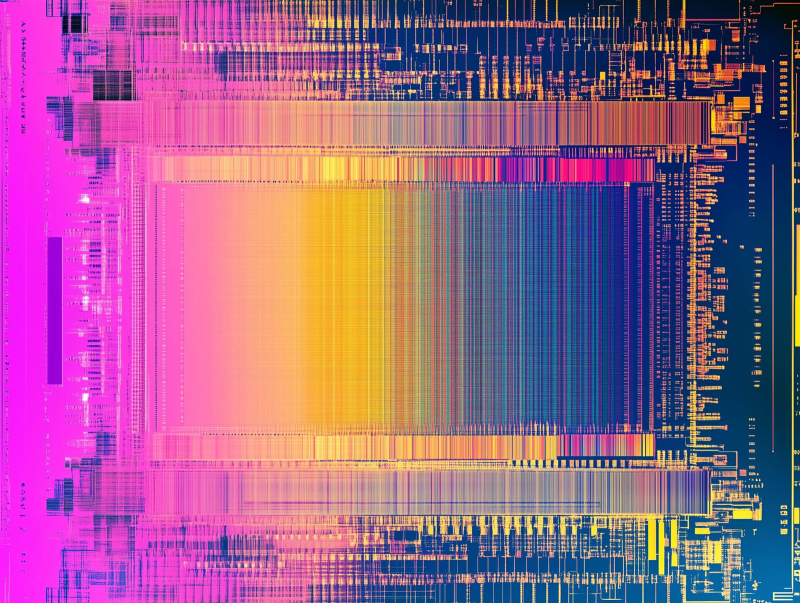

SRAM, да и только: d-Matrix готовит ИИ-ускоритель CorsairСтартап d-Matrix создал ИИ-ускоритель Corsair, оптимизированный для быстрого пакетного инференса больших языковых моделей (LLM). Архитектура ускорителя основана на модифицированных ячейках SRAM для вычислений в памяти (DIMC), работающих на скорости порядка 150 Тбайт/с. Новинка, по словам компании, отличается производительностью и энергоэффективностью, пишет EE Times. Массовое производство Corsair начнётся во II квартале. Среди инвесторов d-Matrix — Microsoft, Nautilus Venture Partners, Entrada Ventures и SK hynix. d-Matrix фокусируется на пакетном инференсе с низкой задержкой. В случае Llama3-8B сервер d-Matrix (16 четырёхчиплетных ускорителей в составе восьми карт) может производить 60 тыс. токенов/с с задержкой 1 мс/токен. Для Llama3-70B стойка d-Matrix (128 чипов) может производить 30 тыс. токенов в секунду с задержкой 2 мс/токен. Клиенты d-Matrix могут рассчитывать на достижение этих показателей для размеров пакетов порядка 48–64 (в зависимости от длины контекста), сообщила EE Times руководитель отдела продуктов d-Matrix Шри Ганесан (Sree Ganesan). Производительность оптимизирована для исполнения моделей в расчёте до 100 млрд параметров на одну стойку. По словам Ганесан, это реалистичный сценарий использования LLM. В таких сценариях решение d-Matrix обеспечивает 10-кратное преимущество в интерактивности (время до получения токена) по сравнению с решениями на базе традиционных ускорителей, таких как NVIDIA H100. Corsair ориентирован на модели размером менее 70 млрд параметров, подходящих для генерации кода, интерактивной генерации видео или агентского ИИ, которые требуют высокой интерактивности в сочетании с пропускной способностью, энергоэффективностью и низкой стоимостью. Ранние версии архитектуры d-Matrix использовали MAC-блоки на базе SRAM-ячеек, дополненных большим количеством транзисторов для операций умножения. Сложение же выполнялось в аналоговом виде с использованием разрядных линий, измерения тока и аналого-цифрового преобразования. В 2020 году компания выпустила чиплетную платформу Nighthawk на основе этой архитектуры. «[Nighthawk] продемонстрировал, что мы можем значительно повысить точность по сравнению с традиционными аналоговыми решениями, но мы всё ещё отстаем на пару процентных пунктов от традиционных решений типа GPU», — сказал EE Times генеральный директор d-Matrix Сид Шет (Sid Sheth). Однако потенциальным клиентам не понравилось, что при таком подходе возможно снижение точности, так что в Corsair компания вынужденно сделала выбор в пользу полностью цифрового сумматора. ASIC d-Matrix включает четыре чиплета, каждый из которых содержит по четыре вычислительных блока, объединённых посредством DMX Link по схеме каждый-с-каждым, и по одному планировщику и RISC-V ядру. Внутри каждого вычислительного блока есть 16 DIMC-ядер, состоящих из наборов SRAM-ячеек (64×64), а также два SIMD-ядра и движок преобразования данных. Суммарно доступен 1 Гбайт SRAM с пропускной способностью 150 Тбайт/с. ASIC объединён со 128 Гбайт LPDDR5 (до 400 Гбайт/с) посредством органической подложки (без дорогостоящего кремниевого интерпозера). Хотя текущее поколение ASIC включает только четыре чиплета именно из-за ограничений подложки, в будущем их количество увеличится. Внешние интерфейсы ASIC представлены стандартным PCIe 5.0 x16 (128 Гбайт/с) и фирменным интерконнектом DMX Link (1 Тбайт/с) для объединения чиплетов. FHFL-карта Corsair включает два ASIC d-Matrix (т.е. всего восемь чиплетов) и имеет TDP на уровне 600 Вт. Ускоритель работает с форматами данных OCP MX (Microscaling Formats) и обеспечивает до 2400 Тфлопс в MXINT8-вычислениях или 9600 Тфолпс в случае MXINT4. Две карты Corsair можно объединить посредством 512-Гбайт/с мостика DMX Bridge. Их, по словам компании, достаточно для задействования тензорного параллелизма. Дальнейшее масштабирование возможно посредством PCIe-коммутации. Именно поэтому d-Matrix работает с GigaIO и Liqid. В одно шасси можно поместить восемь карт Corsair, а в стойку, которая будет потреблять порядка 6–7 кВт — 64 карты. d-Matrix уже разрабатывает ASIC следующего поколения Raptor, который должен выйти в 2026 году. Raptor будет ориентирован на «думающие» модели и получит ещё больше памяти за счёт размещения DRAM непосредственно поверх вычислительных чиплетов. SRAM-чиплеты Raptor также перейдут с 6-нм техпроцесса TSMC, который используется при изготовлении Corsair, к 4 нм без существенных изменений микроархитектуры. По словам компании, она потратила два года на работу с TSMC, чтобы создать 3D-упаковку для нового поколения ASIC. Как отмечает EETimes, команда разработчиков ПО d-Matrix в два раза больше команды разработчиков оборудования (120 против 60). Стратегия компании в области ПО заключается в максимальном использовании open source экосистемы, включая PyTorch, OpenAI Triton, MLIR, OpenBMC и т.д. Вместе они образуют программный стек Aviator, который отвечает за конвертацию моделей в числовые форматы d-Matrix, применяет к ним фирменные методы разрежения, компилирует их, распределяет нагрузку по картам и серверам, а также управляет исполнением моделей, включая обслуживание большого количества запросов.

27.12.2024 [13:44], Сергей Карасёв

Стартап Ubitium создал универсальный чип на базе RISC-V с функциями CPU, GPU, DSP и FPGAСтартап Ubitium, основанный в 2024 году, анонсировал проект по созданию чипа с универсальной архитектурой, которая полностью независима от рабочих нагрузок. Речь идёт об объединении в одном изделии решений разного типа: CPU, GPU, DSP и FPGA. Отмечается, что на протяжении более 50 лет полупроводниковая промышленность занималась созданием самостоятельных центральных, графических и других процессоров, предназначенных для решения конкретных вычислительных задач. Ubitium предлагает пересмотреть данный подход, создав универсальный чип на открытой архитектуре RISC-V, который сможет одинаково хорошо справляться с нагрузками разного типа. Стартап отмечает, что основным препятствием для внедрения новых процессоров являются проприетарные ISA, которые требуют использования специализированных программных инструментов. Кроме того, трудности может создавать отсутствие зрелой программной экосистемы, предоставляющей необходимые фреймворки и приложения. Чипы Ubitium, как утверждается, будут на 100 % совместимы с RISC-V, что упростит и ускорит разработку и внедрение конечных продуктов. В отличие от традиционных процессоров со специализированными ядрами, предназначенными для определённых задач, блоки универсального чипа Ubitium могут динамически «переназначаться» для обработки широкого спектра вычислительных нагрузок, включая простую логику управления, общие вычисления, ИИ и рендеринг графики. Ещё одним преимуществом предлагаемой концепции стартап называет масштабируемость. Ubitium планирует выпускать изделия разного уровня, которые при этом будут иметь идентичную архитектуру и использовать одни и те же программные инструменты. Компания рассчитывает, что её чипы смогут применяться в самых разных сферах — от встраиваемых устройств, бытовой электроники и домашней техники до систем промышленной автоматизации, роботов и космического оборудования. По сравнению с традиционными процессорами, использование решений Ubitium, как утверждается, обеспечит повышение гибкости, снижение стоимости и ускорение разработки. Компания заявляет, что универсальный чип может обеспечить в 10–100 раз большую производительность в расчёте на доллар по сравнению с современными специализированными решениями. В команду Ubitium входят выходцы из Intel, NVIDIA и Texas Instruments. Головной офис компании находится в Дюссельдорфе (Германия). Генеральным директором является Хён Шин Чо (Hyun Shin Cho) из Университета Пердью (Purdue University). Пост технического директора занимает Мартин Форбах (Martin Vorbach), на имя которого зарегистрированы более 200 патентов. Стартап Ubitium уже привлёк $3,7 млн начального финансирования. На данный момент компания создала экспериментальную эмуляцию, которая подтверждает, что универсальный процессор работоспособен. Первые коммерческие решения планируется выпустить к 2026 году.

27.12.2024 [12:40], Сергей Карасёв

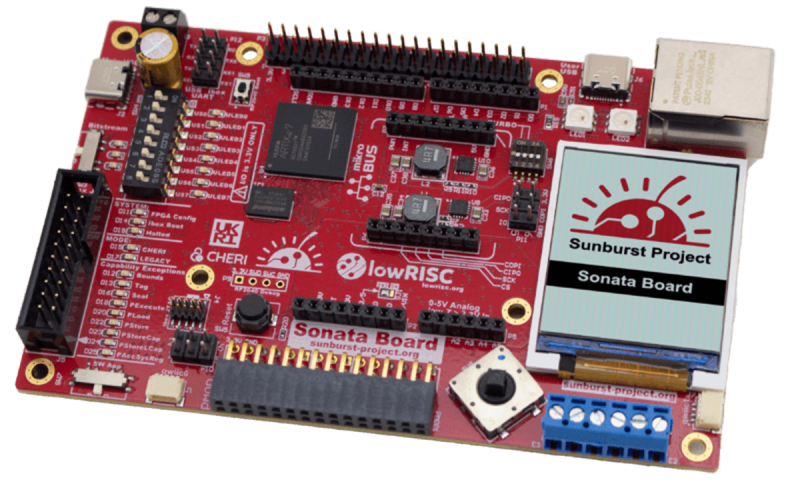

Плата lowRISC Sonata v1.0 с системой защиты памяти CHERIoT объединяет FPGA AMD Artix-7 и микроконтроллер Raspberry Pi RP2040Участники проекта lowRISC по созданию 64-бит чипов RISC-V, как сообщает ресурс CNX Software, анонсировали аппаратную платформу Sonata v1.0 для разработчиков встраиваемых систем и всевозможных устройств Интернета вещей (IoT). Новинка поддерживает технологию CHERIoT (Capability Hardware Extension to RISC-V for IoT). Напомним, летом уходящего года lowRISC, а также Capabilities Limited, Codasip, FreeBSD Foundation, SCI Semiconducto и Кембриджский университет создали альянс CHERI для продвижения средств надёжной защиты памяти от атак. Специальные механизмы исключают ряд потенциальных уязвимостей, таких как переполнение буфера или некорректная работа с указателями. Отмечалось, что первыми новую технологию могут получить процессоры RISC-V. В основе платформы Sonata v1.0 лежит FPGA AMD Xilinx Artix-7 (XC7A35T-1CSG324C). Изделие содержит Soft-процессорное ядро AMD MicroBlaze с архитектурой RISC и 400 Кбайт распределённой памяти RAM. Ещё одной составляющей платы является микроконтроллер Raspberry Pi RP2040 (два ядра Cortex-M0+ с частотой 133 МГц), который отвечает за IO-функции. Есть 64 Мбит памяти HyperRAM (Winbond W956D8MBYA5I), 256 Мбит памяти SPI-флеш (Winbond W25Q256JVEIQ) для FPGA AMD Artix-7 или Raspberry Pi RP2040, ещё 64 Мбит SPI-флеш (Winbond W25Q64JVZEIQ) для RP2040 и 256 Мбит памяти SPI-флеш (Winbond W25Q256JVEIQ) для FPGA. В арсенале Sonata v1.0 — встроенный цветной ЖК-дисплей с диагональю 1,8″, сетевой порт 10/100MbE, два разъёма USB Type-C (для программирования и подачи питания) и слот microSD. Реализованы последовательные интерфейсы RS-232 и RS-485, 40-контактный разъём Raspberry Pi, две 10-контактные колодки Ibex JTAG, две 4-контактные колодки Ibex UART и пр. Размеры составляют 125 × 80 мм. Разработчики могут получить доступ к подробной документации и дополнительным ресурсам на сайтах lowRISC и GitHub, чтобы в полной мере использовать возможности платформы Sonata v1.0. Цена новинки — примерно $413.

26.12.2024 [11:35], Сергей Карасёв

Индийский RISC-V-стартап Mindgrove привлек на развитие $8 млнИндийский стартап Mindgrove Technologies, занимающийся разработкой SoC для различных сфер применения, провёл раунд финансирования Series A, в ходе которого на развитие привлечено $8 млн. Деньги будут направлены на ускорение вывода продуктов на коммерческий рынок. Фирма Mindgrove основана в 2021 году. Штаб-квартира располагается в исследовательском парке Мадрасского технологического института (IITM) в Ченнаи. Компания не имеет собственных производственных мощностей: она занимается проектированием изделий под брендом Mindgrove Silicon.

Источник изображения: Mindgrove Mindgrove фокусируется на чипах для вычислений общего назначения. Речь идёт о решениях для таких отраслей, как автомобилестроение, робототехника, носимые гаджеты и интеллектуальные устройства. В частности, в мае 2024 года Mindgrove анонсировала чип Secure IoT — первую в Индии высокопроизводительную коммерческую SoC, для которой предусмотрена 28-нм технология производства. Изделие предназначено для смарт-часов, умных счётчиков и замков, принтеров, POS-терминалов и пр. Чип, как ожидается, выйдет на рынок к середине 2025 года. Кроме того, Mindgrove проектирует процессор на открытой архитектуре RISC-V, ориентированный на камеры видеонаблюдения, видеорегистраторы, автомобильные системы помощи водителю (ADAS) и смарт-телевизоры. В начале 2023 года Mindgrove Technologies получила $2,325 млн начального финансирования от Peak XV Partners (ранее Sequoia Capital India & SEA), Speciale Invest и Whiteboard Capital. Новый инвестиционный раунд на $8 млн возглавили Rocketship.vc и Speciale Invest при участии Mela Ventures, Peak XV Partners, Nishchay Goel, Whiteboard Capital и Anshul Goel. Полученные средства будут направлены на расширение штата, улучшение инженерных возможностей и коммерциализацию продуктов.

24.12.2024 [15:41], Сергей Карасёв

Sipeed выпустила NanoKVM-PCIe — плату расширения IP-KVM с OLED-дисплеем и Wi-Fi 6Компания Sipeed анонсировала решение NanoKVM-PCIe — плату расширения с интерфейсом PCIe для организации удалённого управления IP-KVM (Keyboard, Video, Mouse). Изделие может применяться в настольных рабочих станциях, а также в стоечных серверах. Новинка представляет собой альтернативу крошечному модулю NanoKVM, вышедшему летом нынешнего года. В основу NanoKVM-PCIe положен чип Sophgo SG2002, который объединяет два ядра C906 с архитектурой RISC-V (1000 и 700 МГц), одно ядро Arm Cortex-A53, а также контроллер 8051 с частотой от 25–300 МГц. Есть нейропроцессорный блок с производительностью до 1 TOPS (INT8) и 256 Мбайт памяти DDR3. Карта располагает слотом microSD, интерфейсом HDMI с поддержкой видео 1080p60, сетевым портом 10/100MbE RJ45 с опциональной поддержкой PoE, а также двумя разъёмами USB Type-C. Дополнительно в оснащение может быть включён адаптер Wi-Fi 6 с коннектором для антенны. Особенность NanoKVM-PCIe заключается в наличии небольшого информационного OLED-дисплея с диагональю 0,49″ и разрешением 64 × 32 точки: этот экран расположен на монтажной планке. Плата имеет низкопрофильное исполнение с габаритами 66 × 57 × 18 мм. Питание (0,2 A / 5 В) может подаваться через слот PCIe, порт USB Type-C или посредством PoE. Применяется прошивка с поддержкой управления UEFI/BIOS, эмулированными USB-мышью/клавиатурой и USB-накопителем, IPMI, WoL, Tailscale, WebSSH и пр. компания Sipeed принимает предварительные заказы на новинку по цене от $42 до $58 в зависимости от выбранных опций.

17.12.2024 [11:50], Сергей Карасёв

Вышла крошечная плата Pico W5 с контроллером Raspberry Pi RP2350, Wi-Fi 4 и Bluetooth 5.0По сообщению ресурса CNX Software, в продажу поступила микроплата Pico W5, построенная на контроллере Raspberry Pi RP2350. Изделие может стать альтернативой устройству Raspberry Pi Pico 2 W, которое дебютировало менее месяца назад. Чип RP2350 содержит по два ядра Arm Cortex-M33 и RISC-V Hazard3 с тактовой частотой 150 МГц. Однако использовать их одновременно нельзя: нужная пара ядер выбирается при инициализации платы. Объём встроенной памяти SRAM составляет 520 Кбайт. Реализована функция Secure Boot (только при использовании блока Arm). Новинка несёт на борту 8 Мбайт памяти QSPI Flash. В оснащение входят адаптеры Wi-Fi 4 802.11n (частотные диапазоны 2,4 и 5 ГГц) и Bluetooth 5.0 (LE) на основе модуля BW16 (контроллер Realtek RTL8720DN). Предусмотрен порт USB Type-C 1.1.

Источник изображения: CNX Software Крошечная плата Pico W5 располагает 26 контактами GPIO с поддержкой 2 × UART, 2 × SPI, 2 × I2C, 24 × PWM, 4 × ADC. Габариты составляют 51 × 21 мм, масса — 3 г. Питание (5 В) подаётся через коннектор USB Type-C. Диапазон рабочих температур простирается от -10 до +60 °C. Модель Pico W5 поддерживает разработку на базе Arduino и MicroPython. Приобрести новинку можно по ориентировочной цене $7. Столько же стоит оригинальная версия Raspberry Pi Pico 2 W, но это изделие поддерживает Wi-Fi 802.11n только в диапазоне 2,4 ГГц. |

|