Материалы по тегу: risc-v

|

25.07.2025 [12:08], Сергей Карасёв

«Байкал Электроникс» начала выпуск микроконтроллеров BE-U1000 на базе RISC-VРоссийская компания «Байкал Электроникс» организовала производство отечественных микроконтроллеров BE-U1000: внимание на это обратил ресурс CNews. Изделия могут применяться в объектах управления, инженерной инфраструктуры, промышленной автоматизации, устройствах IoT, АСУ ТП, в автомобилестроении и пр. Новинка выполнена на открытой архитектуре RISC-V. Задействованы два ядра CloudBEAR BR-350 с максимальной частотой 200 МГц и производительностью 3,42 CoreMark/МГц, а также одно ядро CloudBEAR BM-310 с частотой до 100 МГц и быстродействием 3,6 CoreMark/МГц. В оснащение входят три 12-разрядных АЦП (8 мультиплексируемых каналов с поддержкой дифференциальных входов; частота дискретизации — 1 МSps).

Источник изображения: gisp.gov.ru Микроконтроллер располагает 32 Кбайт памяти SRAM и 256 Кбайт встроенной флеш-памяти. Максимальный объём непосредственно адресуемой внешней флеш-памяти составляет 16 Мбайт (в XIP-режиме). Присутствуют четыре таймера с четырьмя каналами ШИМ (три комплементарных и одиночный PWMA), два одноканальных таймера общего назначения (PWMG), два таймера TIM, два сторожевых таймера WDT, встроенный датчик температуры, два DMA-контроллера, внутренний генератор с частотой от 12 до 32 МГц, 48 линий GPIO. В число реализованных интерфейсов входят USB 2.0 OTG+PHY (HS), 2 × CAN FD, 8 × UART (2 × UART с поддержкой RS-485), 4 × SPI (по два ведущих и ведомых), 2 × QSPI; 4 × I2C, 2 × I2S. Изделие выполнено в корпусе QFN-88 с размерами 10 × 10 мм. Подсистема питания поддерживает входное напряжение 3,3 В (1,7 В и 1,2 В опционально) и опорное напряжение 1,0 В. Максимальный потребляемый ток домена питания VDDIO составляет 250 мА, домена V1P2 — 250 мА. Ведётся работа по включению микроконтроллера в реестр Минпромторга. Новинка производится в соответствии с ГОСТ 18725-83: микросхемы интегральные, общие технические условия. Код по ОКПД 2 — 26.11.3: схемы интегральные электронные. Код по ТН ВЭД — 8542 31: схемы электронные интегральные — процессоры и контроллеры, объединенные или не объединенные с запоминающими устройствами, преобразователями, логическими схемами, усилителями, синхронизаторами или другими схемами.

21.07.2025 [14:05], Сергей Карасёв

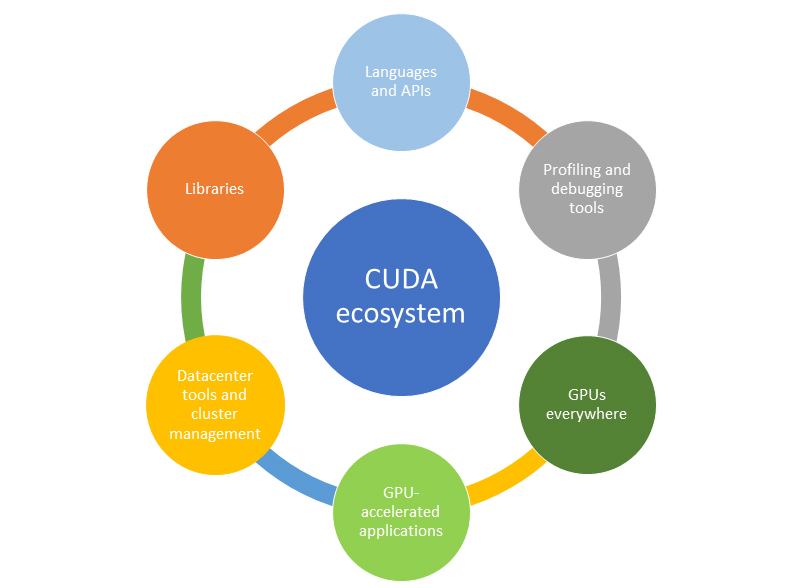

NVIDIA CUDA обзавелась поддержкой RISC-VКомпания NVIDIA в ходе саммита RISC-V 2025 в Китае объявила о том, что ее платформа параллельных вычислений CUDA обзавелась поддержкой открытой архитектуры RISC-V. Это событие отражает растущий интерес к чипам RISC-V в сегменте дата-центров. Представленное решение предполагает использование типичной конфигурации: графический ускоритель обрабатывает параллельные рабочие нагрузки, тогда как CPU на основе RISC-V отвечает за функционирование системных драйверов, логики приложений и операционной системы. Такая модель позволяет CPU полностью координировать GPU-вычисления в среде CUDA.

Источник изображения: RISC-V International (X/@risc_v) Кроме того, в дополнение к CPU с архитектурой RISC-V и ускорителю NVIDIA может быть задействован специализированный сопроцессор для обработки данных (DPU). Таким образом, могут формироваться гетерогенные вычислительные среды, в которых процессор RISC-V играет ключевую роль в управлении рабочими нагрузками. Предполагается, что чипы RISC-V будут использоваться на периферийных устройствах с поддержкой CUDA, включая решения с модулями NVIDIA Jetson. Поддержка RISC-V расширяет возможности CUDA в системах, где предпочтение отдаётся открытым наборам команд или где требуются специально оптимизированные чипы. По сути, NVIDIA создаёт мост между проприетарным стеком CUDA и открытой архитектурой RISC-V, которая активно развивается по всему миру, в том числе в Китае.

Источник изображения: NVIDIA Ранее ряд китайских компаний, включая T-Head (принадлежит гиганту Alibaba Group Holding), Shanghai Shiqing Technology, Juquan Optoelectronics, Xinsiyuan Microelectronics и StarFive, сформировали патентный альянс в сфере RISC-V. Разработкой RISC-V-процессоров занимается научно-исследовательский институт Damo Academy (подразделение Alibaba Group Holding), Китайская академия наук, а также ряд других участников местного рынка. Не имея возможности поставлять флагманские ИИ-ускорители в Китай из-за американских санкций, NVIDIA вынуждена искать другие способы развития экосистемы CUDA в КНР.

19.07.2025 [13:46], Сергей Карасёв

Rockchip анонсировала ИИ-ускоритель RK182X с архитектурой RISC-VКомпания Rockchip, по сообщению ресурса CNX Software, представила в Китае ИИ-ускоритель RK182X, предназначенный для работы с большими языковыми моделями (LLM) и визуально-языковыми моделями (VLM) на периферии. Новинка ориентирована на совместное использование с другими SoC Rockchip. Изделие получило многоядерную архитектуру RISC-V (точное количество ядер пока не раскрывается). В зависимости от модификации задействованы 2,5 или 5 Гбайт памяти DRAM со «сверхвысокой пропускной способностью» (ПСП тоже не раскрывается). Реализована поддержка интерфейсов PCIe 2.0, USB 3.0 и Ethernet. По заявлениям Rockchip, ИИ-ускоритель RK182X способен обрабатывать LLM/VLM, насчитывающие до 7 млрд параметров. В частности, таким моделям требуется примерно 3,5 Гбайт памяти при использовании режимов INT4/FP4. Говорится о совместимости с фреймворками PyTorch, ONNX и TensorFlow, а также форматом HuggingFace GGUF (GPT-Generated Unified Format). ИИ-ускоритель спроектирован для применения в связке с такими процессорами Rockchip, как RK3576/RK3588 и другими, вероятно, включая решения RK3668 и RK3688, которые были также представлены вчера. Эти чипы содержат собственный интегрированный NPU-модуль с производительностью 6 TOPS или более для обработки ИИ-нагрузок. Однако благодаря применению отдельного ускорителя ИИ-быстродействие на определённых задачах может быть повышено в 8–10 раз. Rockchip, в частности, обнародовала скоростные показатели RK182X для таких популярных моделей, как DeepSeek-R1-Distill-Qwen-7B, Qwen2.5-1.5B и Qwen2.5-3B.

06.07.2025 [00:44], Владимир Мироненко

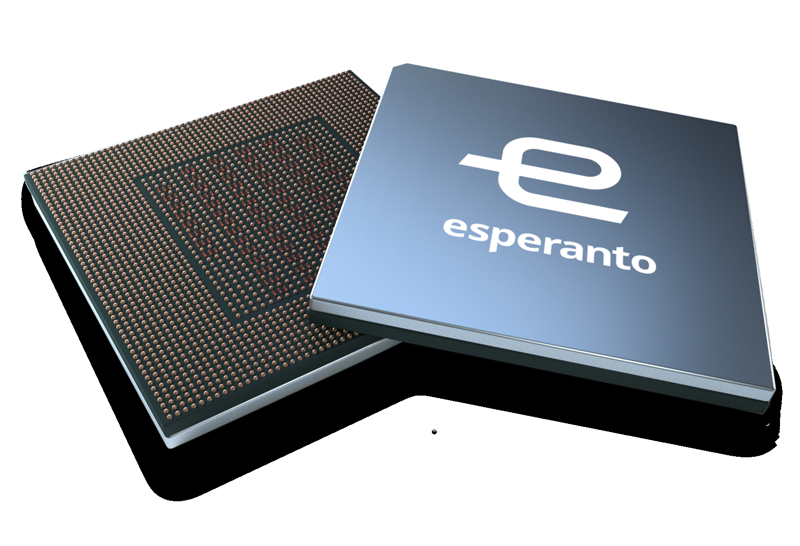

Esperanto, создатель уникального тысячеядерного RISC-V-ускорителя, закрывается — всех инженеров переманили крупные компанииСтартап Esperanto, специализирующийся на разработке серверных ускорителей на базе архитектуры RISC-V, сворачивает свою деятельность, сообщил ресурс EE Times. В настоящее время компания, которую уже покинуло большинство сотрудников, ищет покупателя на свои технологии или заинтересованных в лицензировании её разработок. Компания известна созданием тысячеядерного ИИ-ускорителя ET-SoC-1. Генеральный директор Esperanto Арт Свифт (Art Swift) сообщил EE Times о закрытии дочерних предприятий в Европе — у неё была значительная инженерная команда в Испании и ещё одна небольшая в Сербии. В штаб-квартире Esperanto в Маунтин-Вью (Калифорния) численность персонала сократилась на 90 %. Свифт и еще несколько инженеров остались, чтобы продать или лицензировать разработки компании и содействовать любой потенциальной передаче технологий. По словам Свифта, компания подверглась атаке со стороны богатых конкурентов, которые предлагали зарплату «в два, три, даже в четыре раза выше», чем могла предложить небольшая Esperanto. «Они фактически уничтожили наши команды — очень жаль, но мы не смогли конкурировать с ними», — говорит Свифт, отмечая, что уже несколько компаний проявило интерес к приобретению технологии или её лицензированию на неисключительной основе. Он добавил, что у Esperanto был крупный клиент, которому есть что предложить, что добавляет оптимизма. Ранее компания, судя по всему, пыталась предложить свои чипы Meta✴.

Источник изображения: Esperanto Technologies Интерес рынка к RISC-V для чипов ЦОД остаётся высоким, особенно в Европе, где инвестирует в новую экосистему чипов на основе RISC-V. Вместе с тем именно ключевое преимущество разработок Esperanto — энергоэффективность — оказалось труднореализуемым, говорит гендиректор: «При неограниченном бюджете на электроэнергию энергоэффективность на самом деле не имеет значения». Esperanto готовила к выпуску чиплет второго поколения, который должен был поступить в производство на мощностях Samsung по 4-нм техроцессу в 2026 году. Чиплет предложил бы до 16 Тфлопс в FP64-вычислениях или до 256 Тфлопс в FP8-расчётах при потреблении 15–60 Вт. В один чип можно объединить до восьми чиплетов. Третье поколение технологии удвоило бы вычислительную мощность чиплетов. «Компании действительно были заинтересованы в получении этой технологии, так что посмотрим», — говорит Свифт. В прошлом году Esperanto договорилась с корпорацией NEC о сотрудничестве в области НРС с целью создания программных и аппаратных решений следующего поколения с архитектурой RISC-V. Также сообщалось о разработке чипа ET-SoC-2 для НРС и ИИ-задач. На пике развития штат Esperanto составлял 140 человек. По словам Свифта, 95 % бывших сотрудников стартапа уже нашли новую работу. В аналогичной ситуации оказалась Codasip, объявившая о готовности продать свои активы, поскольку обострение конкуренции на рынке RISC-V и отсутствие достаточного запаса средств ограничивают возможности небольших компаний, которые зачастую не могут конкурировать с IT-гигантами. ИИ-стартап Untether AI тоже провалил тест на выживание, объявив о закрытии бизнеса после того, как AMD переманила ряд его ведущих специалистов.

04.07.2025 [19:50], Владимир Мироненко

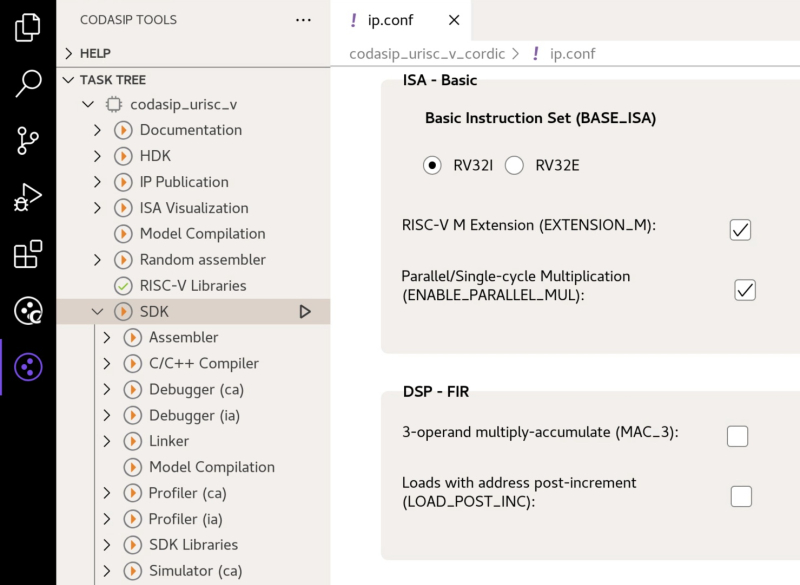

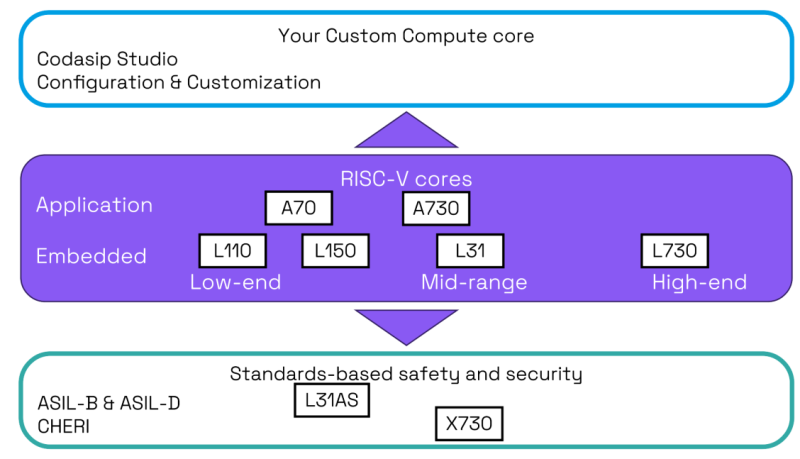

Разработчик RISC-V-чипов Codasip готов продаться — целиком или по частямРазработчик чипов с архитектурой RISC-V и инструментов проектирования из Мюнхена Codasip объявил о готовности продать свои активы, сославшись на проявление к ним интереса со стороны компаний во время недавнего раунда финансирования. Компания сообщила, что процесс приёма заявок на покупку, начавшийся 1 июля, продлится три месяца, что, по мнению ресурса The Register, может указывать на уже поступившие предложения. Ландшафт открытой архитектуры RISC-V превращается из экосистемы сотрудничества в высококонкурентную коммерческую среду, отметил ресурс EE Times. На фоне этого один из основных поставщиков EDA-инструментов Synopsys запустил полный набор основных IP-блоков RISC-V. Попутно крупные игроки рынка полупроводников, такие как Bosch, Infineon, NXP, Qualcomm и Nordic Semiconductor, сформировали консорциум Quintauris для разработки собственных процессорных решений для автомобильного сектора. В связи с этим Codasip попала в сложное положение, оказавшись между гигантами, предлагающими интегрированные решения, и крупными вертикальными игроками, разрабатывающими собственные продукты на базе RISC-V, что потенциально может сократить её целевой рынок. Codasip сообщила, что у неё есть несколько бизнес-подразделений, нацеленных на четыре ключевых направления продуктов, с «отделимыми» R&D-командами, намекая таким образом, что можно купить отдельные группы, а не компанию целиком.

Источник изображений: Codasip Как пишет The Register, у Codasip предполагаемая годовая выручка составляет $88,7 млн, что делает её одним из крупнейших разработчиков микросхем в экосистеме RISC-V. У Ventana Micro Systems предполагаемая выручка составляет $37,4 млн за год, а SiFive ожидала получить около $60 млн в прошлом году. Хотя RISC-V вызывает определённый интерес, предлагая открытый набор инструкций, лёгких путей для построения успешного бизнеса здесь не обещают — SiFive ранее уволила 20 % штата, Intel отказалась от программы Pathfinder for RISC-V, а Imagination Technologies отказалась от RISC-V, сосредоточившись на продуктах GPU и ИИ. У Codasip есть портфолио решений для прикладных и встраиваемых процессоров и портфолио процессоров с архитектурой безопасности CHERI с аппаратной защитой памяти, а также сопутствующее ПО. Отдельно разрабатываются высокопроизводительные прикладные процессоры в рамках проекта Евросоюза Digital Autonomy with RISC-V in Europe (DARE). Наконец, у компании есть и собственные EDA-инструменты для разработки и кастомизации чипов. Немалую часть средств компании приносят гранты от различных органов ЕС, многочисленных общеевропейских и национальных проектов, включая DARE, TRISTAN и NEUROKIT2E — более €119 млн ($140 млн). Однако большая часть этих денег пока не получена компанией. На следующих этапах грантовой поддержки компания может получить ещё €210 млн ($248 млн). Codasip также утверждает, что является частью новых консорциумов и проектов, которые могут принести ей финансирование в размере €51 млн ($60) или больше. По словам компании, эти средства могут быть переданы покупателю на разумных условиях. «В первую очередь, быть разработчиком CPU — это дорогостоящий бизнес, поэтому долгосрочное финансирование имеет важное значение — если рыночное признание низкое, доходы не появятся немедленно», — отметил Эндрю Басс (Andrew Buss), старший директор по исследованиям IDC в регионе EMEA. По оценкам EE Times, потенциальные приобретатели Codasip делятся на три категории. Первая включает гигантов в сфере EDA и интеллектуальной собственности (IP), таких как Synopsys, для которой приобретение Codasip означает возможность консолидации рынка благодаря получению уникального набора инструментов Codasip Studio, расширению портфеля интеллектуальной собственности и устранению значительного конкурента. Вторая категория состоит из вертикальных интеграторов, в основном американских технологических титанов, таких как Intel, Qualcomm и Broadcom. Intel уже предлагала в 2021 году более $2 млрд за SiFive, но сделка не состоялась. Приобретение Codasip даст Intel зрелый портфель интеллектуальной собственности для клиентов Intel Foundry Services (IFS), а также надёжную, отличающуюся от x86 архитектуру для собственных продуктов. Для Qualcomm, судящейся с Arm, сделка означала бы снижение зависимости от архитектуры Arm. Сертифицированные IP-блоки для автомобильных решений Codasip идеально соответствует роли Qualcomm в качестве соучредителя в Quintauris, пишет EE Times. Broadcom может быть интересен набор Codasip Custom Compute, который она могла бы использовать для внутренних ядер контроллеров в SoC. Хотя вероятность заявки от Broadcom довольно низкая. И, наконец, третья категория — организации ЕС, которые могли бы купить Codasip для потенциального европейского консорциума. Европейский союз сделал технологический суверенитет центральной политической целью, что очевидно на примере таких инициатив, как «Европейский закон о чипах» (European Chips Act). Для Евросоюза покупка является стратегической: не допустить приобретения неевропейской организацией критически важного европейского технологического актива, в значительной степени субсидируемого за счет средств ЕС. Покупатель из страны, не входящей в ЕС, должен будет предоставить твёрдые, юридически обязывающие обязательства по поддержанию и развитию европейских центров НИОКР Codasip, обеспечению постоянного участия в стратегических проектах ЕС и в целом соответствию технологической повестке ЕС, подчеркнул EE Times.

18.06.2025 [11:54], Сергей Карасёв

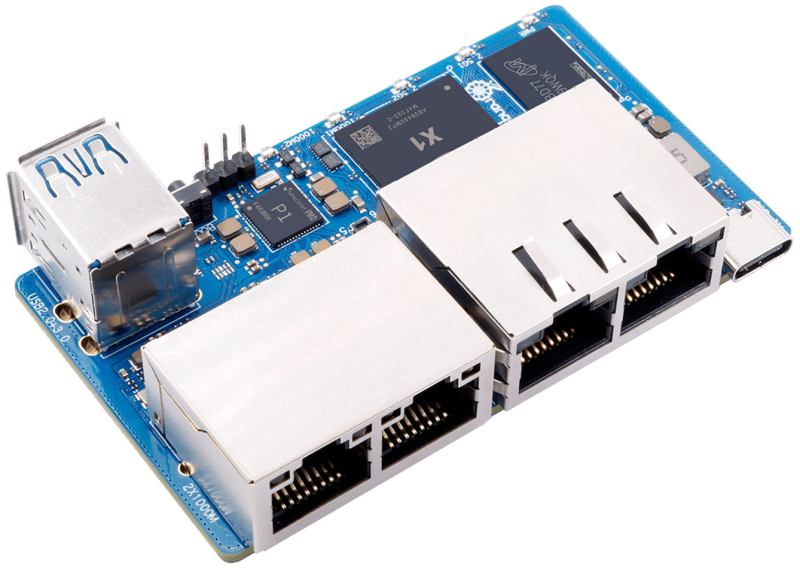

Мини-плата для мини-маршрутизатора: представлена Orange Pi R2S с чипом RISC-VВ семействе одноплатных компьютеров Orange Pi, по сообщению ресурса CNX Software, появилась модель R2S, которую можно использовать для построения различных сетевых устройств, в частности, маршрутизаторов. Новинка уже доступна для заказа по цене от $30. В основу изделия положен процессор Ky X1 с восемью 64-битными ядрами RISC-V (RV64GCVB), функционирующими на частоте до 1,6 ГГц. В состав чипа входят графический ускоритель Imagination IMG BXE-2-32 (819 МГц) с поддержкой OpenGL ES3.2, Vulkan 1.3 и OpenCL 3.0, а также VPU-блок с возможностью декодирования видео H.265, H.264, VP8, VP9, MPEG4, MPEG2 в форматах до 4K@60 Гц и кодирования H.265, H.264, VP8, VP9 в форматах до 4K @ 30 Гц. Процессор также располагает ИИ-ускорителем с производительностью до 2 TOPS (INT8). В зависимости от модификации плата несёт на борту 2, 4 или 8 Гбайт памяти LPDDR4X. Предусмотрены флеш-модуль eMMC вместимостью 8 Гбайт и слот для карты microSD. За сетевые подключения отвечают два порта 2.5GbE на основе контроллеров RealTek RTL8125BG и два порта 1GbE на базе YT8531C-CA: во всех случаях для подключения кабелей служат разъёмы RJ45. Кроме того, имеются по одному порту USB 3.0 и USB 2.0. Питание 5 В / 3 A подаётся через порт USB Type-C. Изделие имеет размеры 79,2 × 46 мм и весит 60 г. Отмечается, что для новинки будут доступны образы OpenWrt 24.10 и Ubuntu 24.04 (ядро Linux 6.6.xx). Стоимость Orange Pi R2S с 2 Гбайт ОЗУ составляет $30, с 4 Гбайт — $40. Цена варианта с 8 Гбайт памяти пока не указывается, но, по всей видимости, она окажется на уровне $50.

01.05.2025 [00:15], Владимир Мироненко

«Байкал электроникс» поставила в Россию 85 тыс. процессоров Baikal

arm

baikal-l

baikal-m

baikal-s

cpu

hardware

risc-v

байкал электроникс

импортозамещение

микроконтроллер

россия

санкции

сделано в россии

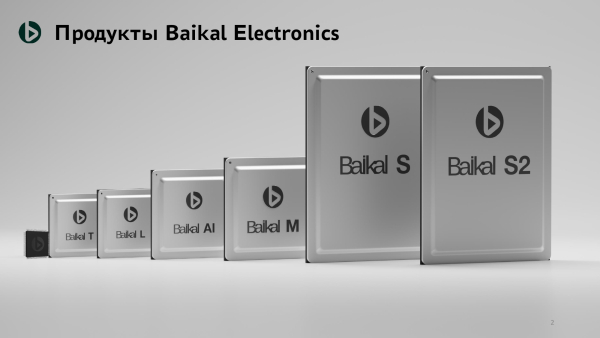

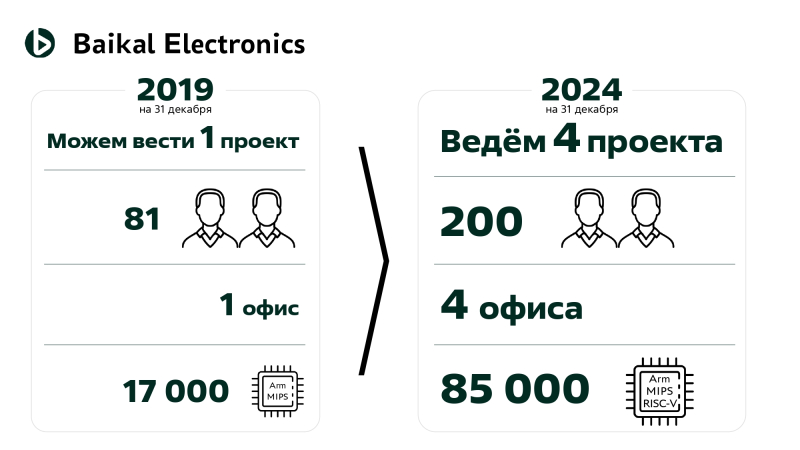

Компания «Байкал электроникс» за время работы ввезла в Россию 85 тыс. процессоров собственной разработки, включая модели Baikal-T, Baikal-M и Baikal-S. Из этого объёма компания поставила на российский рынок в 2019 году 17 тысяч процессоров. Об этом рассказал гендиректор «Байкал электроникс» Андрей Евдокимов на конференции «Планирование карьеры в электронной области», прошедшей в МИЭТ в апреле 2025 года. По словам Евдокимова, поставки должны были быть гораздо больше, но из-за санкций производство чипов было прекращено. Так, на Тайване была арестована партия из 150 тыс. процессоров Baikal-M. Кроме того, «Байкал электроникс» пришлось отменить из-за санкций заказ на изготовление 15 тыс. штук чипа Baikal-S, благо компания не успела его оплатить. В связи с отказом TSMC обслуживать российских заказчиков, выпуск Baikal-S был полностью отменён летом 2022-го года. Кроме того, санкциям подверглись и разработчики open source ПО. Вместе с тем «Байкал электроникс» продолжает работать и расширять свою деятельность. Если в 2019 году в ней работал 81 сотрудник и был один офис, то сейчас у компании четыре офиса и штат сотрудников составляет 205 человек. В настоящее время компания занимается четырьмя проектами. Евдокимов сообщил, что компания в апреле начала серийное производство собственного микроконтроллера Baikal-MCU, о разработке которого сообщалось два года назад, и вскоре будет направлен в серийное производство чип Baikal-L для ноутбуков и планшетов. Также в настоящее время в разработке компании находится следующее поколение серверных чипов Baikal-S2. Ранее компания также рассчитывала разработать Arm-процессоры Baikal-M2 и Baikal-M Lite, RISC-V чипы Baikal-NX, а также ИИ-ускорители Baikal AI SoC-C (для ЦОД) и AI SoC-E (для периферии). ИИ-ускорители, как ожидается, будут анонсированы в следующем году. По-видимому, в результате санкций компания пересмотрела развитие ряда проектов.

28.04.2025 [12:54], Сергей Карасёв

Одноплатный компьютер Muse Pi Pro оснащён чипом RISC-V, адаптерами Wi-Fi 6 и Bluetooth 5.2Китайская компания SpacemiT, по сообщению ресурса CNX Software, выпустила одноплатный компьютер Muse Pi Pro — более компактную модификацию изделия Muse Pi, которое дебютировало в июне 2024 года. Новинка уже доступна для заказа по ориентировочной цене от $122. Как и оригинальная версия, модель Muse Pi Pro несёт на борту процессор SpacemiT M1 с восемью ядрами X60 с архитектурой RISC-V, работающими на частоте до 1,8 ГГц. В состав чипа входят графический ускоритель Imagination IMG BXE-2-32 с поддержкой OpenGL ES3.2, Vulkan 1.2 и OpenCL 3.0, а также VPU-блок с возможностью кодирования/декодирования материалов H.265/H.264 1080p60. Кроме того, имеется нейропроцессорный узел (NPU) с ИИ-производительностью до 2 TOPS (INT8).

Источник изображения: CNX Software Одноплатный компьютер может комплектоваться 8 или 16 Гбайт оперативной памяти LPDDR4X-2400, а также флеш-чипом eMMC 5.1 вместимостью 64 или 128 Гбайт. Есть слот microSD (UHS-II), коннектор M.2 M-Key 2230 для NVMe SSD и коннектор miniPCIe (PCIe 2.1 x1) для сотового модема 4G/5G. В оснащение входят адаптеры Wi-Fi 6 и Bluetooth 5.2, сетевой контроллер 1GbE. Устройство располагает разъёмом HDMI 1.4 (1080p60), четырьмя портами USB 3.0 Type-A и одним портом USB 2.0 Type-C OTG, гнездом RJ45 для сетевого кабеля, интерфейсами MIPI CSI на четыре и две линии, 40-контактной колодкой GPIO и 3,5-мм аудиогнездом. Габариты составляют 85 × 56 мм. Диапазон рабочих температур простирается от -20 до +70 °C у обычной версии и от -40 до +85 °C у индустриального варианта. Питание (5/9/12 В, до 3 A) подаётся через разъём USB Type-C. Говорится о совместимости с Bianbu Desktop, Ubuntu, OpenKylin, Deepin, Fedora и др.

23.04.2025 [11:20], Сергей Карасёв

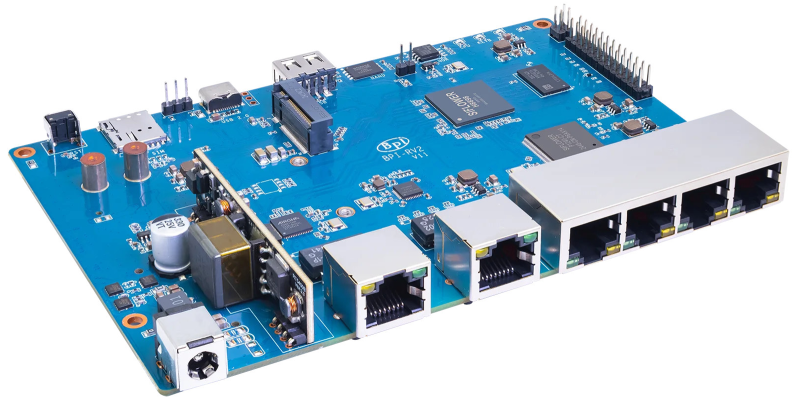

Плата Banana Pi BPI-RV2 для компактных маршрутизаторов оснащена чипом RISC-VВ ассортименте Banana Pi, по сообщению ресурса CNX-Software, появилась плата BPI-RV2, предназначенная для построения компактных маршрутизаторов. Изделие доступно для заказа по ориентировочной цене от $35. Основой новинки служит процессор Siflower SF21H8898 с четырьмя 64-битядрами с архитектурой RISC-V, работающими на тактовой частоте до 1,25 ГГц. Объём оперативной памяти DDR3 составляет 512 Мбайт. Предусмотрено 128 Мбайт памяти SPI NAND Flash (для U-Boot и Linux), а также 16 Мбайт памяти SPI NOR Flash (U-Boot и Linux) с защитой от записи по умолчанию. Плата располагает коннектором M2 Key-B (PCIe 2.0 x1 + USB 2.0) для NVMe SSD или модема 5G (плюс разъём для карты Nano SIM), а также слотом mini PCIe (PCIe 2.0 x1) для адаптера Wi-Fi или сетевой карты. Есть 26-контактная колодка GPIO, разъём USB 2.0 Type-A и порт USB Type-C. Изделие оборудовано шестью сетевыми портами RJ45, из которых пять поддерживают стандарт 1GbE, а один — 2.5GbE. Опционально может быть реализована поддержка 802.3at/af PoE (через порт 2.5GbE). Новинка имеет размеры 148 × 100,5 мм. Питание (12 В / 2 A) подаётся через коннектор 5.5/2.1 мм. Плата Banana Pi BPI-RV2 использует форк OpenWrt (Linux 5.10). Базовая версия изделия предлагается за $34,5, а доплатив ещё $4, можно приобрести вариант с PoE. На текущий момент для платы нет специализированного корпуса, позволяющего получить полноценный маршрутизатор. Но по габаритам решение идентично модели Banana Pi BPI-R3, для которой предлагается недорогой металлический корпус.

21.04.2025 [08:46], Сергей Карасёв

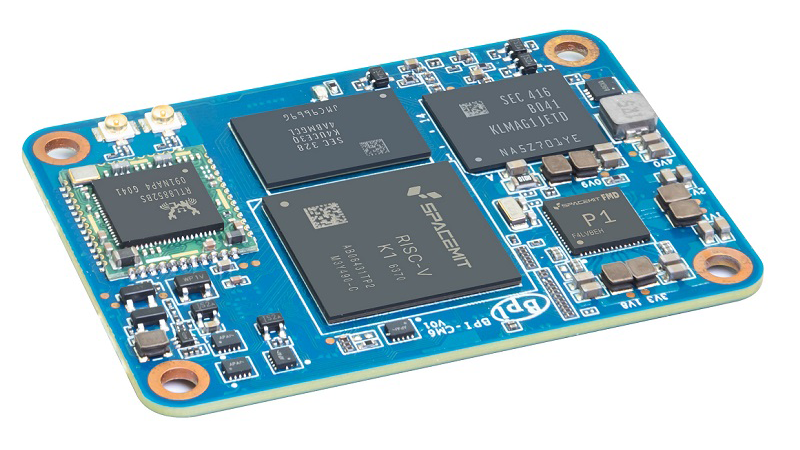

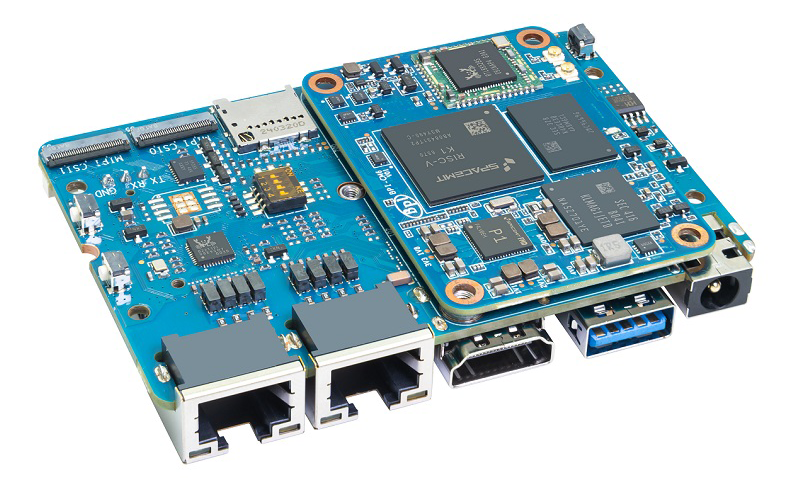

Представлен модуль Banana Pi BPI-CM6 — аналог Raspberry Pi CM4 на базе RISC-VВ ассортименте Banana Pi появился вычислительный модуль BPI-CM6 — это альтернатива Raspberry Pi CM4, выполненная на процессоре с открытой архитектурой RISC-V вместо Arm. Новинка подходит для создания систем промышленного контроля и автоматизации, NAS-устройств, робототехники, периферийных решений и пр. По форме, габаритам и расположению коннекторов новинка идентична Raspberry Pi CM4. Задействован чип SpacemiT K1, который объединяет восемь 64-битных ядер RISC-V, графический блок Imagination BXE-2-32 с поддержкой OpenCL 3.0, OpenGL ES3.2 и Vulkan 1.3, а также нейропроцессорный узел (NPU) с производительностью до 2 TOPS для ускорения ИИ-операций.

Источник изображений: Banana Pi Модуль Banana Pi BPI-CM6 располагает 8 Гбайт оперативной памяти LPDDR4 (максимум 16 Гбайт) и чипом eMMC вместимостью 16 Гбайт (максимум 128 Гбайт). Реализована поддержка Bluetooth и Wi-Fi, PCIe 2.1 (5 линий), USB 3.0 и USB 2.0 (×2), HDMI 1.4, MIPI DSI и MIPI CSI (×3). Размеры составляют 40 × 55 мм. Диапазон рабочих температур простирается от -40 до +85 °C. Говорится о совместимости с Ubuntu Linux.  Для новинки доступна сопутствующая интерфейсная плата, которая содержит по одному разъёму HDMI, USB 3.0 Type-A, USB 2.0 Type-A и USB Type-C OTG, два сетевых порта 1GbE RJ45 и слот для карты microSD. Кроме того, есть два коннектора M.2 M-Key (PCIe х2) для подключения SSD, 26-контактная колодка GPIO, два интерфейса MIPI CSI (4 линии) и один интерфейс MIPI DSI (4 линии). Питание (12 В) подаётся через DC-коннектор. Габариты — 56 × 85 мм. |

|