Материалы по тегу: cadence

|

08.05.2025 [19:22], Сергей Карасёв

Cadence представила суперкомпьютер Millennium M2000 на базе NVIDIA BlackwellКомпания Cadence анонсировала суперкомпьютер Millennium M2000, спроектированный для выполнения сложного моделирования с использованием ИИ. Новая НРС-система предназначена для ускорения проектирования микрочипов, разработки лекарственных препаратов следующего поколения и пр. Суперкомпьютер построен на платформе NVIDIA HGX B200. Кроме того, задействованы карты NVIDIA RTX Pro 6000 Blackwell Server Edition, оснащённые 96 Гбайт памяти GDDR7. Применены библиотеки NVIDIA CUDA-X и специализированное ПО для решения ресурсоёмких задач. Утверждается, что Millennium M2000 обеспечивает до 80 раз более высокую производительность по сравнению с системами на базе CPU в области автоматизации проектирования электроники (EDA), создания и анализа систем (SDA) и разработки медикаментов. При этом глубоко оптимизированный программно-аппаратный стек помогает существенно сократить общее энергопотребление. В качестве примера приводится моделирование подсистемы питания на уровне полупроводниковых чипов. В случае вычислительных комплексов на основе сотен традиционных CPU на выполнение такой задачи может потребоваться около двух недель. Суперкомпьютер Millennium M2000 позволит получить результат менее чем за один день. Генеральный директор NVIDIA Дженсен Хуанг (Jensen Huang) сообщил, что компания планирует приобрести десять суперкомпьютерных систем Millennium на базе GB200 NVL72 для ускорения проектирования собственных продуктов. Сторонние заказчики смогут получить доступ к Millennium M2000 через облако или купить устройство для установки в собственном дата-центре. Базовая конфигурация включает около 32 ускорителей и стоит $2 млн, но это не финальная цена.

04.08.2022 [15:54], Владимир Мироненко

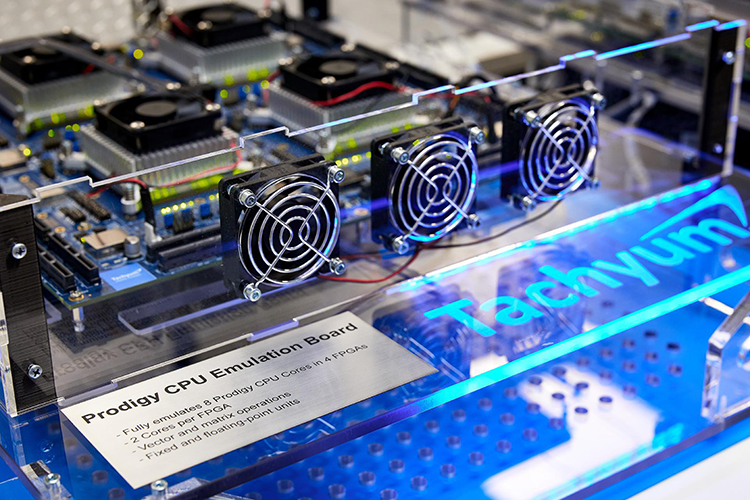

Разработчик серверных чипов Prodigy с невероятными характеристиками обвинил в своих бедах CadenceКак сообщает The Register, cтартап Tachyum подал в суд на Cadence Design Systems, обвинив компанию в саботаже при выполнении контракта на поставку IP-блоков для будущих 5-нм серверных процессоров Prodigy. По словам Tachyum, старшие 128-ядерные CPU Prodigy с частотой 5,7 ГГц будут втрое быстрее AMD EPYC 7763 и NVIDIA H100. В иске утверждается, что заключённая в 2019 году сделка на предоставление решений Cadence для процессоров Prodigy, была сорвана, поскольку Cadence не смогла предоставить необходимые технологии для вывода продукта на рынок. Заказанные Tachyum блоки не относятся к разряду новшеств, и инженеры Cadence уверяли Tachyum, что стандартные компоненты могли быть без труда интегрированы в процессор. Однако график поставок был нарушен, и дошло даже до того, что Cadence посоветовала Tachyum не использовать её компоненты или вообще приобрести аналоги у других поставщиков.

Источник изображения: Tachyum Стартап добавил в иске, что Cadence усугубила ущерб, прекратив доступ Tachyum к ПО eDAcard, тем самым вынудив понести расходы на лицензирование другого ПО и переобучение своих инженеров. Срыв сроков и прочие препятствия привели к задержке выхода Prodigy примерно на два года. Tachyum потребовал возместить упущенную выгоду в размере $206 млн и ещё $27 млн дополнительных затрат на поиск альтернативных решений в сжатые сроки.

Источник изображения: Tachyum Tachyum также указала, что из-за срыва сроков она потеряла возможность получения заказов на поставку чипов для испанского суперкомпьютера MareNostrum 5 стоимостью €151,41 млн. В итоге Барселонский суперкомпьютерный центр (BSC), с которым был подписан меморандум о взаимопонимании, предпочёл компанию Atos. Последняя выбрала ускорители NVIDIA и процессоры Intel, поскольку ни одна европейская компания не могла бы поставить чипы, отвечающие ключевым критериям отбора. В иске Tachyum отмечает, что тогдашний генеральный директор Cadence Лип-Бу Тан (Lip-Bu Tan) входил в совет директоров двух конкурентов Tachyum — SambaNova и Nuvia (поглощена Qualcomm) — и активно участвовал в фондах Walden International и Walden Catalyst, которые инвестировали в другие «кремниевые» стартапы. Ещё один член совета директоров Cadence, Янг Сон (Young Sohn), также является директором одного из этих инвестфондов. По мнению Tachyum, налицо явный конфликт интересов. |

|