Материалы по тегу: интерфейсы

|

06.10.2025 [09:19], Сергей Карасёв

Corning и GlobalFoundries создадут оптические коннекторы для кремниевой фотоникиАмериканский контрактный производитель полупроводниковых изделий GlobalFoundries и компания Corning, специализирующаяся на производстве стёкол, керамики и т.п., объявили о сотрудничестве. Совместными усилиями партнёры разработают разъёмные волоконно-оптические коннекторы для кремниевой фотоники. Речь идёт о решении GlassBridge для платформы GF Fotonix. Коннектор на основе стеклянного волновода совместим с V-образными канавками GF Fotonix. Система предназначена для удовлетворения растущих потребностей ИИ ЦОД в высокой пропускной способности каналов связи. Разрабатываются также другие механизмы соединения, включая вертикальное разъёмное решение типа Fibre-to-PIC (Photonic Integrated Circuit). Сотрудничество предусматривает использование передовых разработок Corning в области материалов, оптического волокна и средств связи. Это, в частности, стёкла специального состава, стеклянные подложки и методы лазерной обработки. Кроме того, будут применяться оптоволоконные массивы (Fibre Array Unit — FAU) с волокнами со сверхточным выравниванием сердцевины, благодаря которому минимизируются потери. В перспективе разъёмы нового типа помогут повысить удобство развёртывания и эксплуатации высокоскоростного интерконнекта на основе кремниевой фотоники в дата-центрах, ориентированных на ресурсоёмкие приложения ИИ и НРС. Не так давно GlobalFoundries объявила о том, что её платформа кремниевой фотоники выделена в отдельное продуктовое семейство. При этом компания увеличила объём инвестиции в соответствующей сфере в два раза.

11.08.2025 [10:46], Сергей Карасёв

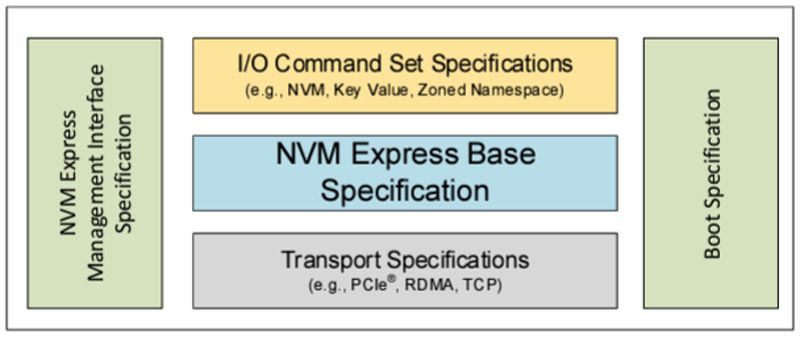

SSD под контролем: консорциум NVM Express обновил спецификации, добавив быстрое восстановление после сбоевКонсорциум NVM Express обнародовал ряд новых спецификаций, призванных ускорить и упростить разработку изделий с архитектурой NVMe. Реализованы функции, которые помогают в решении эксплуатационных задач, предоставляя администраторам улучшенную прозрачность и контроль над хранилищами для критически важных бизнес-приложений и нагрузок в дата-центрах. В частности, обновлены базовая спецификация NVMe 2.3, спецификация набора команд (NVM Command Set 1.2, ZNS Command Set 1.4, Key Value Command Set 1.3, Subsystem Local Memory Command Set 1.2, Computational Programs Command Set 1.2), транспортная спецификация (NVMe over PCIe Transport 1.3, NVMe over RDMA Transport 1.2, NVMe over TCP Transport 1.2), а также спецификации NVM Express Management Interface (NVMe-MI) 2.1 и NVMe Boot 1.3.

Источник изображения: NVM Express Одной из новых функций является восстановление после сбоев Rapid Path Failure Recovery. Этот инструмент обеспечивает связь с подсистемой NVM через альтернативные каналы, что позволяет быстро восстанавливать подключение в случае потери связи с контроллером, избегая повреждения данных и дублирования невыполненных команд. Кроме того, появилась возможность ограничения мощности (Power Limit Config): эта функция обеспечивает полный контроль над максимальной мощностью устройств NVMe, что особенно важно для старых платформ с ограниченным потенциалом в плане питания. В свою очередь, режим Self-reported Drive Power позволяет хосту измерять и контролировать мощность устройства NVMe, а также энергопотребление в течение всего срока его службы. Это помогает в решении вопросов, связанных с обслуживанием хранилищ и устойчивым развитием. Инструмент Sanitize Per Namespace обеспечивает криптографическую очистку отдельных пространств имен, не затрагивая всю подсистему NVM. Кроме того, упомянут механизм индивидуальной настройки устройств Configurable Device Personality.

12.12.2024 [22:54], Владимир Мироненко

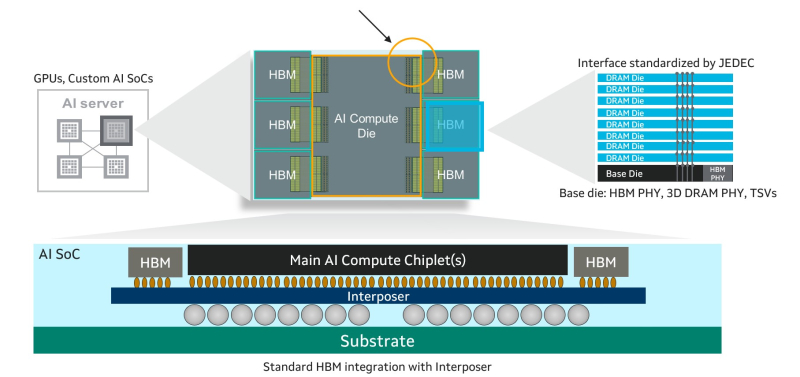

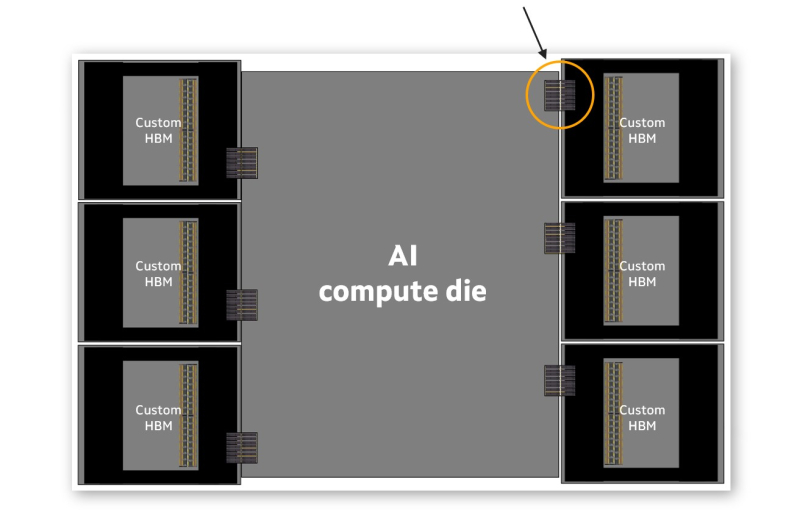

Всё дальше от народа: Marvell предложила гиперскейлерам кастомизацию HBM для ИИ-ускорителейMarvell Technology анонсировала новый подход к интеграции HBM (CHBM) в специализированные XPU, который предоставляет адаптированные интерфейсы для оптимизации производительности, мощности, размера кристалла и стоимости для конкретных конструкций ИИ-ускорителей. Как указано в пресс-релизе, этот подход учитывает вычислительный «кремний», стеки HBM и упаковку. Marvell сотрудничает с облачными клиентами и ведущими производителями HBM, такими, как Micron, Samsung и SK hynix. CHBM повышает возможности XPU, ускоряя ввода-вывод между внутренними кристаллами самого ускорителя и базовыми кристаллами HBM. Это приводит к повышению производительности и снижению энергопотребления интерфейса памяти до 70 % по сравнению со стандартными интерфейсами HBM. Оптимизированные интерфейсы также уменьшают требуемую площадь кремния в каждом кристалле, позволяя интегрировать логику для поддержки HBM в базовый кристалл и сэкономить до 25 % площади. Высвободившееся пространство может быть использовано для размещения дополнительных вычислительных или функциональных блоков и поддержки до 33 % большего количества стеков HBM. Всё это повышает производительность и энергоэффективность XPU, одновременно снижая совокупную стоимость владения для операторов облачных инфраструктур. Правда, это же означает и несоответствие стандартами JEDEC. Как отметил ресурс ServeTheHome, HBM4 требует более 2000 контактов, т.е. вдвое больше, чем HBM3. Для кастомного решения нет необходимости в таком количестве контактов, что также высвобождает место для размещения других компонентов. «Ведущие операторы ЦОД масштабируются с помощью индивидуальной инфраструктуры. Улучшение XPU путем адаптации HBM к конкретной производительности, мощности и общей стоимости владения — это последний шаг в новой парадигме разработки и поставки ускорителей ИИ», — сказал Уилл Чу (Will Chu), старший вице-президент Marvell и генеральный менеджер группы Custom, Compute and Storage. В свою очередь, Гарри Юн (Harry Yoon), корпоративный исполнительный вице-президент Samsung Electronics, отметил, что оптимизация HBM для конкретных XPU и программных сред значительно повысит производительность облачной инфраструктуры операторов и её энергоэффективность. Согласно данным ServeTheHome, в этом году гиперскейлеры увеличили капзатраты примерно на $100 млрд. Следующее поколение ИИ-кластеров будет в десять и более раз превосходить по мощности систему xAI Colossus на базе 100 тыс. NVIDIA H100. Отказ от стандартов JEDEC и появление возможности настройки памяти с учётом потребностей гиперскейлеров является монументальным шагом для отрасли. Также этого говорит о нацеленности архитектуры Marvell XPU на гиперскейлеров, поскольку в таком «тюнинге» памяти небольшие заказчики не нуждаются.

19.01.2024 [22:20], Сергей Карасёв

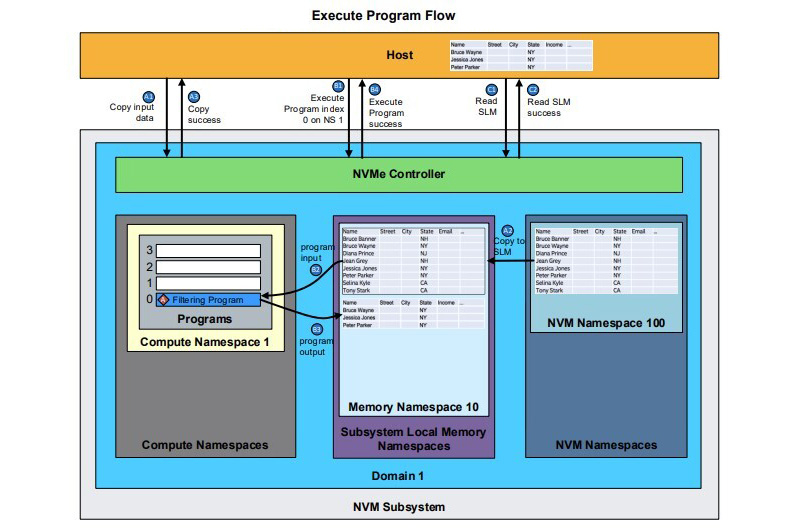

Консорциум NVM Express добавил в стандарт поддержку вычислительных хранилищКонсорциум NVM Express обновил спецификации, добавив возможность работы с вычислительными хранилищами NVMe Computational Storage Feature. Речь идёт о возможности использования устройств хранения, которые могут самостоятельно обрабатывать хранящуюся на них информацию по команде извне. Это позволит снизить совокупную стоимость владения IT-системами и повысить их общую производительность. Спецификация включает два новых набора команд: Computational Programs и Subsystem Local Memory Command Sets. Первый отвечает за исполнение программ на устройстве хранения, в том числе их загрузку, поиск уже загруженных программ и их запуск. Набор обеспечивает модульный подход к программам, управляемым хостом. Второй предоставляет доступ к памяти в подсистеме NVM и позволяет работать с данными, обрабатываемыми программами на устройстве хранения.

Источник изображения: NVM Express Вычислительное хранилище сокращает необходимость в перемещении данных между накопителями и процессором/ускорителем. Определённые операции могут производиться непосредственно на устройстве хранения, что повышает время отклика приложений, критичных к задержке. Это могут быть базы данных, модели ИИ и системы доставки контента. В целом, функция NVMe Computational Storage Feature обеспечивает стандартизированную, не зависящую от поставщика оборудования архитектуру для хранения и обработки данных на накопителях NVMe. Решение ориентировано прежде всего на операторов дата-центров и гиперскейлеров.

01.08.2022 [23:00], Игорь Осколков

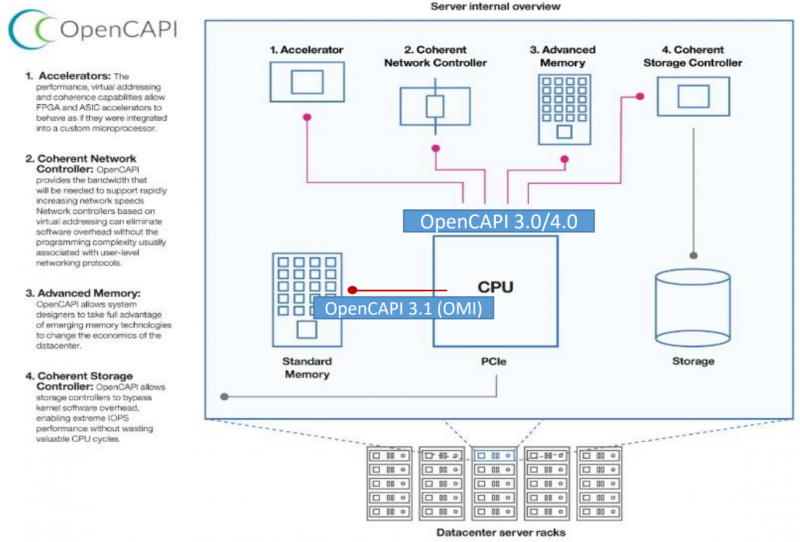

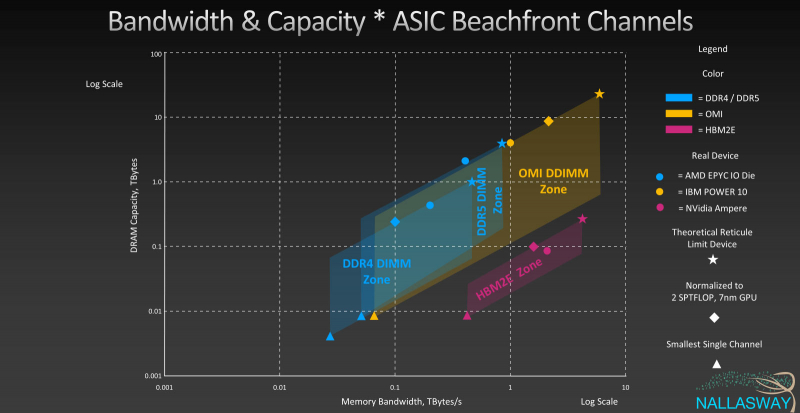

Великое объединение: спецификации и наработки OpenCAPI и OMI планируется передать консорциуму CXLКонсорциумы OpenCAPI Consortium (OCC) и Compute Express Link (CXL) подписали соглашение, которое подразумевает передачу в пользу CXL всех наработок и спецификаций OpenCAPI и OMI. Если будет получено одобрения всех участвующих сторон, то это будет ещё один шаг в сторону унификации ключевых системных интерфейсов и возможности реализации новых архитектурных решений. Во всяком случае, на бумаге. Консорциумы OpenCAPI (Open Coherent Accelerator Processor Interface) был сформирован в 2016 году с целью создание единого, универсального, скоростного и согласованного интерфейса для связи CPU с ускорителями, сетевыми адаптерами, памятью, контроллерами и устройствами хранения и т.д. Причём в независимости от типа и архитектуры самого CPU. На тот момент новый интерфейс был определённо лучше распространённого тогда PCIe 3.0. С течением времени дела у OpenCAPI шли ни шатко ни валко, однако фактически его использование было ограничено только POWER-платформами от IBM. Тем не менее, в недрах OpenCAPI родился ещё один очень интересный стандарт — Open Memory Interface (OMI). OMI, если коротко, предлагает некоторую дезагрегацию путём добавления буферной прослойки между CPU и RAM. С одной стороны у OMI есть унифицированный последовательный интерфейс для подключения к CPU, с другой — интерфейсы для подключения какой угодно памяти, на выбор конкретного производителя. OMI позволяет поднять пропускную способность памяти, не раздувая число контактов и физические размеры и самого CPU, и модулей. Однако и в данном случае массовая поддержка OMI по факту есть только в процессорах IBM POWER10. Концептуально CXL в части работы с памятью повторяет идею OMI, только в данном случае в качестве физического интерфейса используется распространённый PCIe. Существенная разница c OMI в том, что начальная поддержка CXL будет в грядущих процессорах AMD и Intel. А Samsung и SK Hynix уже готовят соответствующие DDR5-модули. Да и в целом поддержка CXL в индустрии намного шире. Так что консорциуму CXL, по-видимому, осталось поглотить только ещё один конкурирующий стандарт в лице CCIX, как это уже произошло с Gen-Z. Комментируя соглашение, президент консорциума CXL отметил, что сейчас наиболее удачное время для объединения усилий, которое принесёт пользу всей IT-индустрии. Участники OpenCAPI имеют богатый опыт, который поможет улучшить грядущие спецификации CXL и избежать ошибок.

03.04.2020 [13:37], Геннадий Детинич

Консорциумы CXL и Gen-Z объединяют усилия: протоколы станут совместимыми, а возможности расширятсяКонсорциумы CXL и Gen-Z сообщили, что их руководящие органы подписали договор о взаимопонимании. Пописанный меморандум раскрывает планы сотрудничества между двумя организациями, обещая совместимые протоколы и расширенные возможности каждого из представленных интерфейсов. Первые версии спецификаций Gen-Z и CXL (Compute Express Link) вышли, соответственно, в феврале 2018 года и в марте 2019 года. Каждый из этих интерфейсов призван обойти ограничения по пропускной способности, накладываемые на многоядерные и многоузловые конфигурации процессоров и ускорителей.  Как один, так и другой интерфейс отвечают за согласованность кешей множества подключённых решений и обеспечивают минимальные задержки при доступе к вычислительным ресурсам и хранилищам данных на основе ОЗУ или долговременных накопителей. В то же время интерфейс CXL специализируется на согласованной работе внутри шасси, а интерфейс Gen-Z позволяет согласовывать работу на уровне блоков, стоек и массивов. В целом, участники консорциума Gen-Z поддержали идею Compute Express Link и признали её как дополняющую для развития интерфейса Gen-Z. В течение прошлого года в консорциум CXL, за организацией которого стоит компания Intel, вошли много компаний, включая AMD и ARM. Дело оставалось за малым ― объединить усилия и добиться совместимости протоколов и архитектур.  Сегодня такой день настал. Консорциумы CXL и Gen-Z договорились организовать совместные смешанные рабочие группы для разработки «мостов» между протоколами обеих спецификаций и сделать всё необходимое, чтобы расширить возможности каждого из стандартов за счёт возможностей другого. |

|