Материалы по тегу: ram

|

05.05.2024 [13:59], Сергей Карасёв

SK hynix продала всю память HBM, запланированную к выпуску в 2024–2025 гг.Компания SK hynix, по сообщению The Register, получила заказы на весь объём памяти HBM, запланированный к выпуску в 2024 году, и на основную часть этих чипов, которые будут произведены в 2025-м. Спрос на изделия HBM быстро растёт на фоне стремительного развития ИИ-рынка. SK hynix объявила на пресс-конференции в своей штаб-квартире в Ичхоне (Южная Корея) о намерении расширить производство микросхем HBM. Генеральный директор компании Квак Но-чжун (Kwak Noh-jung) заявил, что выпуск изделий данного типа удастся значительно нарастить после завершения строительства новых предприятий в Южной Корее и США.

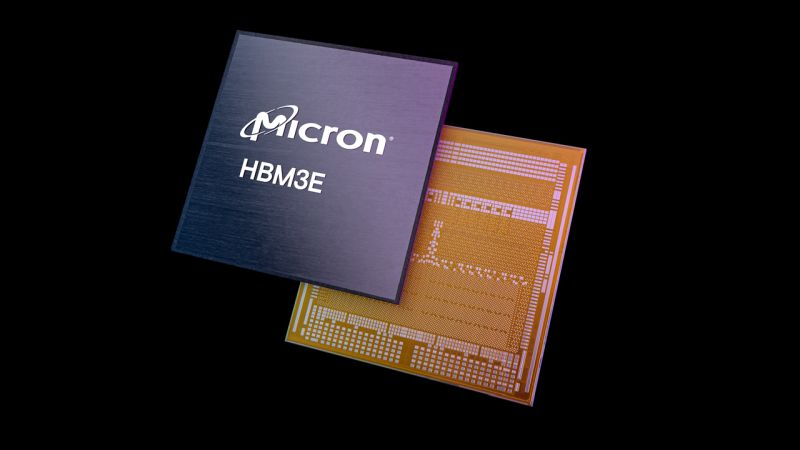

Источник изображения: SK hynix SK hynix является основным поставщиком памяти HBM для ускорителей NVIDIA, с поставками которых наблюдаются сложности из-за высокого спроса со стороны облачных провайдеров и операторов дата-центров, ориентированных на ИИ-нагрузки. Квак Но-чжун прогнозирует, что в среднесрочной и долгосрочной перспективе среднегодовой прирост потребности в чипах HBM будет составлять около 60 %. Это связано с увеличением объёмов генерируемых данных и повышением сложности ИИ-моделей. До конца мая SK hynix планирует предоставить клиентам образцы памяти HBM пятого поколения — 12-слойные изделия HBM3E. Массовый выпуск такой продукции компания наметила на III квартал 2024 года. Недавно SK hynix заявила, что планирует инвестировать более $14,5 млрд в новый корейский завод M15X по производству чипов памяти. Первоначально планировалось, что это предприятие будет выпускать изделия NAND, но затем было решено переориентировать его мощности под выпуск DRAM. В марте сообщалось, что компания Micron Technology, приступившая в феврале к массовому производству памяти HBM3E, уже получила контракты на весь объём поставок этих изделий до конца 2024 года, а также на большую часть поставок в 2025 году.

02.05.2024 [15:33], Алексей Разин

Micron начала поставки RDIMM-модулей DDR5 объёмом 128 Гбайт на базе 32-Гбит чиповПредставив чипы памяти типа DDR5 ёмкостью 32 Гбит ещё прошлой осенью, компания Micron Technology только сейчас сертифицировала модули RDIMM объёмом 128 Гбайт на основе этих чипов на совместимость с оборудованием ключевых игроков серверного рынка. Клиенты Micron смогут получить такие модули памяти в июне. Также компания объявила о поставках восьмиярусных стеков памяти HBM3E. Американский производитель памяти подчёркивает, что и 128-Гбайт модули DDR5-5600 RDIMM, и HBM3E-память Hi-8 наилучшим образом проявят себя в серверной инфраструктуре, ориентированной на обслуживание ИИ-систем. Кого именно из производителей ускорителей вычислений Micron снабжает памятью типа HBM3E, не уточняется, но конкурирующие Samsung и SK hynix уже готовы поставлять клиентам 12-ярусные чипы HBM3E. Впрочем, ещё в феврале Micron сообщил о готовности начать во II квартале поставки чипов HBM3E объёмом 24 Гбайт для ускорителей NVIDIA H200.

Источник изображения: Micron Technology Серверные модули DDR5 объёмом 128 Гбайт со скоростью 5600 МТ/с на основе монолитных 32-Гбит чипов памяти, по данным Micron, позволяют на 45 % поднять плотность хранения данных в пересчёте на один контакт, на 22 % поднять энергетическую эффективность, и на 16 % снизить задержки при передаче информации по сравнению с немонолитными чипами DDR5. Micron отметила, что в этом году начнёт поставки модулей со скоростью 4800, 5600 и 6400 MT/с, а в будущем намерена предложить решения со скоростью до 8000 MT/с. AMD и Intel подтвердили совместимость новых модулей Micron со своими современными серверными платформами. Со следующего месяца Micron начнёт продавать новую память через своих торговых партнёров.

16.03.2024 [23:19], Сергей Карасёв

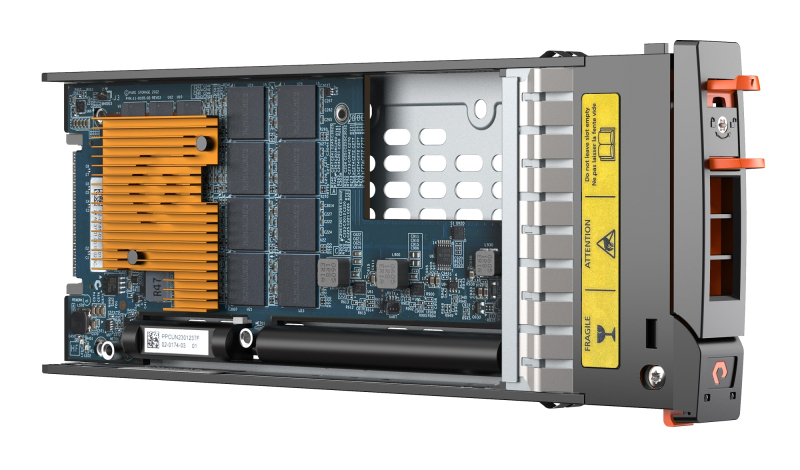

Pure Storage: рост ёмкости SSD будет ограничен возможностями DRAMКомпания Pure Storage, специализирующаяся на All-Flash СХД, считает, что дальнейшее увеличение вместимости SSD будет сопряжено с рядом трудностей, продиктованных необходимостью применения DRAM. Об этом, как сообщает ресурс Blocks & Files, рассказал Шон Роузмарин (Shawn Rosemarin), вице-президент Pure по исследованиям и разработкам. По его словам, коммерческим SSD требуется примерно 1 Гбайт DRAM на каждый 1 Тбайт флеш-памяти. Наличие DRAM необходимо для подсистемы Flash Translation Layer (FTL). По словам Роузмарина, для накопителя ёмкостью 30 Тбайт требуется 30 Гбайт DRAM, для 75 Тбайт — 75 Гбайт и т. д. Таким образом, для SSD вместимостью, например, 128 Тбайт нужно 128 Гбайт DRAM, а это уже сопоставимо с объёмом ОЗУ в сервере. Роузмарин отмечает, что увеличение вместимости корпоративных SSD свыше 30 Тбайт будет проблематично. Во-первых, DRAM заметно дороже NAND, что приведёт к значительному росту стоимости SSD. Во-вторых, из-за увеличения объёма DRAM возрастает энергопотребление, что не только поднимет стоимость владения, но и ухудшит надёжность накопителя. В результате по мере роста вместимости SSD заказчики могут столкнуться с серьёзным увеличением затрат. Роузмарин заявляет, что единственный способ обойти указанные проблемы — найти более экономичную и менее энергозатратную альтернативу DRAM. Необходимые функции, по его словам, могут быть перенесены непосредственно на ПО СХД. Именно такой подход Pure реализует со своими проприетарными накопителями DFM (Direct Flash Module), последняя модификация которых имеет ёмкость 75 Тбайт. В этих устройствах отсутствует зависимость от DRAM на уровне накопителей. Компания намерена выпустить DFM ёмкостью 150 Тбайт в 2025 году, а на 300 Тбайт — ориентировочно в 2026-м. В дальнейшие планы входит создание изделий вместимостью 600 Тбайт и 1,2 Пбайт. Аналогичного подхода придерживается и IBM в своих накопителях FlashCore Modules (FCM).

14.08.2023 [17:37], Алексей Степин

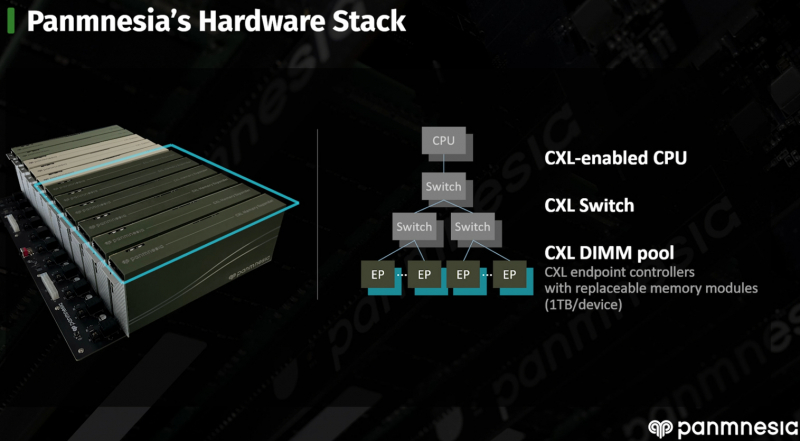

CXL-пул Panmnesia втрое быстрее RDMA-систем и может предложить 6 Тбайт RAMНа конференции Flash Memory Summit южнокорейская компания Panmnesia продемонстрировала свою версию CXL-пула DRAM объёмом 6 Тбайт на базе программно-аппаратного стека собственной разработки. Новинка продемонстрировала более чем троекратное превосходство над системой, построенной на базе технологии RDMA, в нагрузках, связанной с работой рекомендательной ИИ-системы Meta✴. Panmnesia разработана в сотрудничестве с Корейским инститом передовых технологий (KAIST). О более раннем варианте разработок KAIST в этой области мы рассказывали в 2022 году. Коммерческий вариант комплекса поддерживает CXL 3.0 и состоит из CXL-процессора, коммутатора и модулей расширения памяти. Все модули выполнены в форм-факторе, чрезвычайно напоминающем FHFL-карты. Модули устанавливаются в универсальное шасси, при этом их можно произвольно комбинировать. Демо-платформа содержала два процессорных модуля, три модуля коммутации и шесть 1-Тбайт модулей памяти. Модули памяти построены на базе обыкновенных DIMM-планок и поддерживают их замену и расширение. Реализован не только режима CXL.mem, но и CXL.cache и CXL.io. При этом компания предлагает не только готовые IP-решения, но и их кастомизацию под конкретного заказчика, что поможет оптимизировать цикл создания продукта и снизить общую стоимость разработки и валидации. Фирменное ПО базируется на Linux и содержит необходимые драйверы, а также специализированную виртуальную машину, с помощью которой пространство памяти представляется в виде безпроцессорного NUMA-узла. Поверх этих компонентов функционирует пользовательская часть, отвечающая за эффективное размещение и предвыборку (prefetching) данных. По ряду параметров Panmnesia можно назвать лидером в области CXL-решений. В частности, по объёму DRAM она уже обгоняет совместное решение Samsung, MemVerge, H3 и XConn, а использование DIMM-модулей только придаёт ей гибкости. Развитая программная часть, как утверждается, упрощает и удешевляет интеграцию в существующую инфраструктуру ЦОД. Спектр применения, как и у всех систем CXL-пулинга, крайне широкий и включает в себя не только ИИ-сценарии, но и любые задачи, требующие большого объёма оперативной памяти.

04.11.2019 [21:00], Алексей Степин

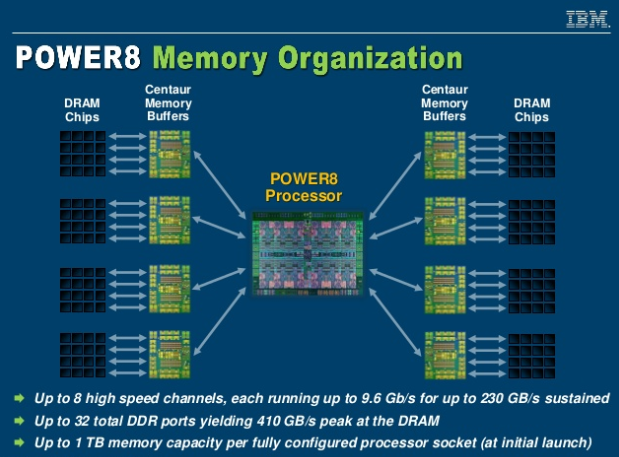

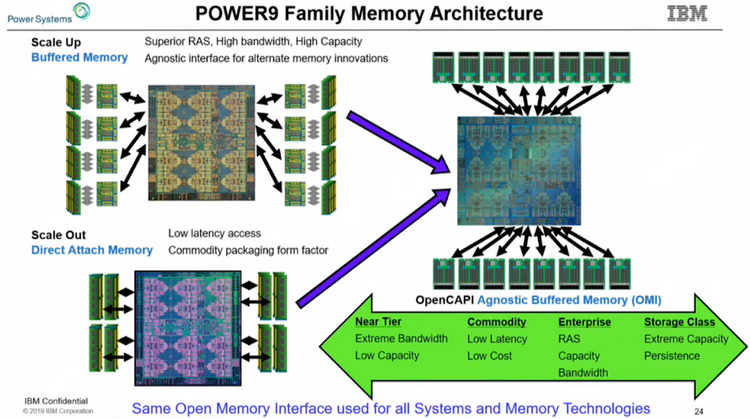

IBM продвигает открытый стандарт оперативной DDIMM-памяти OMI для серверовПрактически у всех современных процессоров контроллер памяти давно и прочно является частью самого ЦП, будь то монолитный кристалл или чиплетная сборка. Но не всегда подобная монолитность является плюсом — к примеру, она усложняет задачу увеличения количества каналов доступа к памяти. Таких каналов уже 8 и существуют проекты процессоров с 10 каналами памяти. Но это усложняет как сами ЦП, так и системные платы, ведь только на подсистему памяти, без учёта интерфейса PCI Express, может уйти 300 и более контактов, которые ещё требуется корректно развести и подключить.

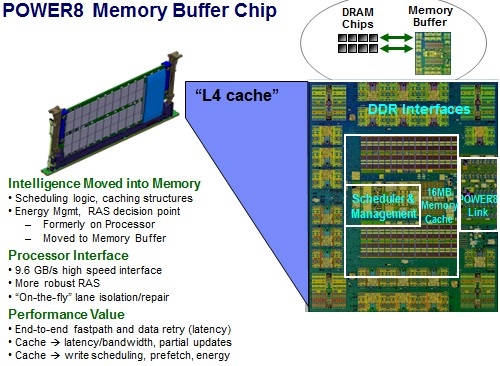

Организация подсистемы памяти у POWER8 У IBM есть ответ, и заключается он в переносе части функций контроллера памяти на сторону модулей DIMM. Сам интерфейс между ЦП и модулями памяти становится последовательным и предельно унифицированным. Похожая схема использовалась в стандарте FB-DIMM, аналогичную компоновку применила и сама IBM в процессорах POWER8 и POWER9 в варианте Scale-Up.

Роль и возможности буфера Centaur у POWER8 Контроллер памяти у этих процессоров упрощён, в нём отсутствует контроллер физического уровня (PHY). Его задачи возложены на чип-буфер Centaur, который посредством одноимённого последовательного интерфейса и связывается с процессором на скорости 28,8 Гбайт/с. Контроллеров интерфейса Centaur в процессорах IBM целых восемь, что дает ПСП в районе 230 Гбайт/с. За счёт выноса ряда функций в чипы-буфера удалось сократить площадь кристалла, и без того немалую (свыше 700 мм2), но за это пришлось заплатить увеличением задержек в среднем на 10 нс. Частично это сглажено за счёт наличия в составе Centaur кеша L4.

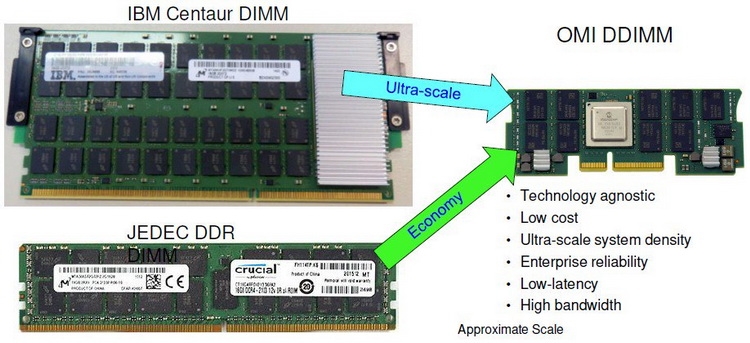

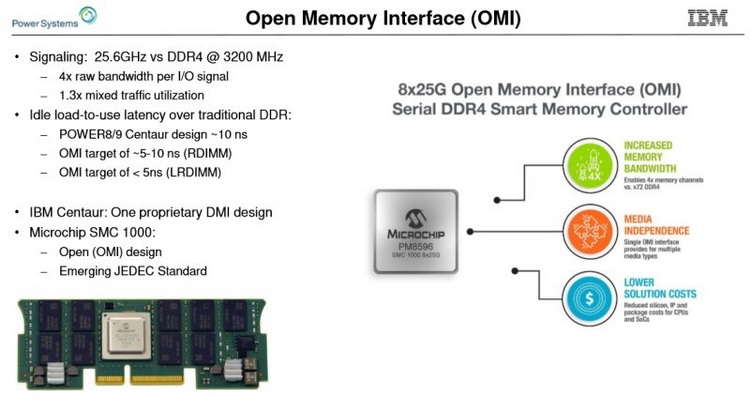

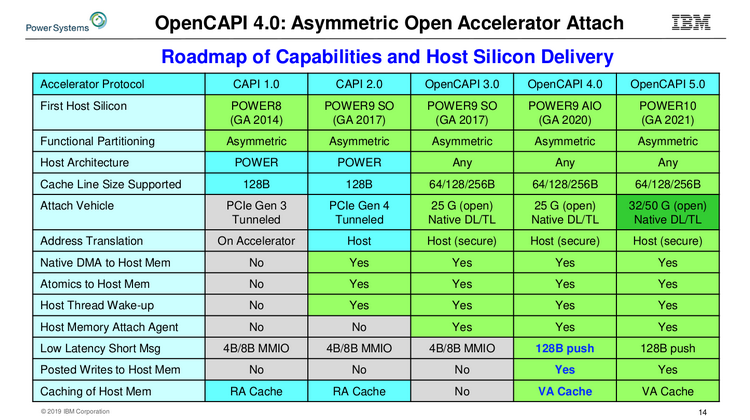

Сравнительные размеры модулей Centaur, RDIMM и OMI DDIMM Стандарт не является открытым, но IBM предлагает ему на смену полностью открытый вариант под названием Open Memory Interface (OMI). В его основу положена семантика и протоколы, описанные в стандарте OpenCAPI 3.1, а физический уровень представлен шиной BlueLink (25 Гбит/с на линию), которая уже используется для реализации NVLink и OpenCAPI. Реализация OMI проще Centaur, что позволяет сделать чип-буфер более компактным и выделяющим меньше тепла. Но все преимущества сохраняются: так, число контактов процессора, отвечающих за интерфейс памяти, можно снизить с примерно 300 до 75, поскольку посылаются только простые команды загрузки и сохранения данных. Вся реализация физического интерфейса осуществляется силами чипа-компаньона OMI, и в нём же может находиться дополнительный кеш.

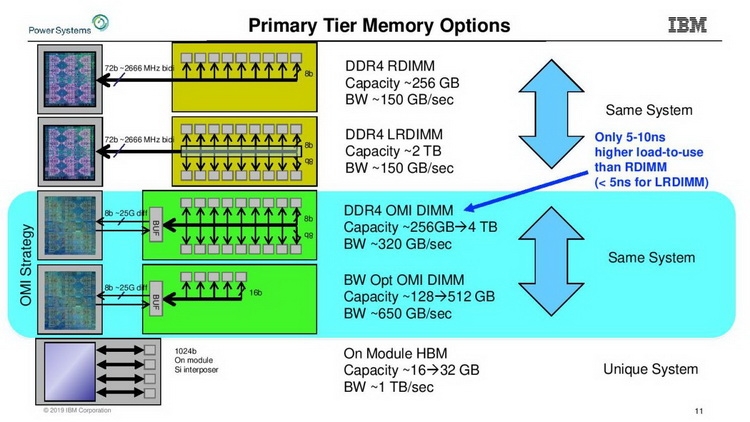

Модули OMI DDIMM станут стандартом JEDEC Помимо экономии контактов есть и ещё одна выгода: можно реализовать любой тип памяти, будь то DDR, GDDR и даже NVDIMM — вся PHY-часть придётся на различные варианты чипов OMI, но со стороны стандартного разъёма любой модуль OMI будет выглядеть одинаково. Сейчас взят прицел на реализацию модулей с памятью DDR5. При использовании существующих чипов DDR4 система с интерфейсом OMI может достичь совокупной ПСП порядка 650 Гбайт/с. Дополнительные задержки составят 5 ‒ 10 нс для RDIMM и лишь 4 нс для LRDIMM. Из всех соперников технологии на такое способны только сборки HBM, которые в силу своей природы имеют ограниченную ёмкость, дороги в реализации и не могут быть вынесены с общей с ЦП подложки.

Новый стандарт упростит процессоры и позволит увеличить ёмкость подсистемы памяти Чипы-буферы OMI можно разместить как на модуле памяти, так и на системной плате. Разумеется, для стандартизации выбран первый вариант. В нём предусмотрено 84 контакта на модуль, сами же модули получили название Dual-Inline Memory Module (DDIMM). ✴-media" data-instgrm-captioned="" data-instgrm-permalink="https://www.instagram.com/p/B5I5Dmpj0rw/?utm_source=ig_embed&utm_campaign=loading" data-instgrm-version="12"> DDIMM вышли существенно компактнее своих традиционных собратьев: ширина модуля сократилась со 133 до 85 мм. Реализация буфера OMI ↔ DDR4 уже существует в кремнии: компания Microsemi продемонстрировала чип SMC 1000 (PM8596), поддерживающего 8 линий OMI со скоростью 25 Гбит/с каждая. Допустима также работа в режиме 4 × 1 с вдвое меньшей общей пропускной способностью.

DDIMM: меньше ширина, проще разъём Со стороны чипов памяти SMC 1000 имеет стандартный 72-битный интерфейс с ECC и поддержкой различных комбинаций DRAM и NAND-устройств. Тактовая частота DRAM — до 3,2 ГГц, высота модуля зависит от количества и типов устанавливаемых чипов. В случае одиночной высоты модули могут иметь ёмкость до 128 Гбайт, двойная высота позволит создать DDIMM объёмом свыше 256 Гбайт. Сам чип SMC 1000 невелик, всего 17 × 17 мм, а невысокое тепловыделение гарантирует отсутствие проблем с перегревом, свойственных FB-DIMM.

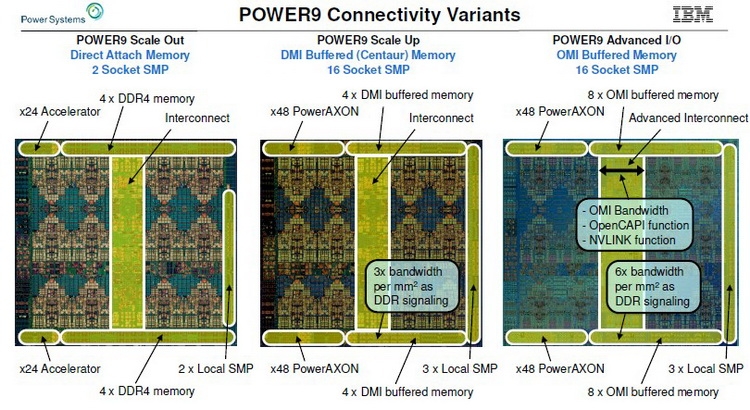

Процессоры IBM POWER9 AIO дополнили существующую серию Первыми процессорами с поддержкой OMI стали новые POWER9 версии Advanced I/O (AIO), дополнившие семейства Scale Up (SC) и Scale Out (SO). В них реализовано 16 каналов OMI по 8 линий каждый (до 650 Гбайт/с суммарно), а также новые версии интерфейсов NVLink (возможно, 3.0) и OpenCAPI 4.0. Количество линий PCI Express 4.0 по-прежнему составляет 48. Шина IBM BlueLink была переименована в PowerAXON. За счёт её использования в системах на базе процессоров POWER возможна реализация 16-сокетных систем без применения дополнительной логики. Максимальное количество ядер у POWER9 AIO равно 24, с учётом SMT4 это даёт 96 исполняемых потоков. Имеется также кеш L3 типа eDRAM объёмом 120 Мбайт. Техпроцесс остался прежним, это 14-нм FinFET.

Архитектура подсистем памяти у семейства IBM POWER9 Поставки POWER9 AIO начнутся в этом году, цены неизвестны, но с учётом 8 миллиардов транзисторов и кристалла площадью 728 мм2 они не могут быть низкими. Однако без OMI эти процессоры были бы ещё более дорогими. В комплект поставки входит и чип-буфер OMI, правда, не самая быстрая версия с пропускной способностью на уровне 410 Гбайт/с. Задел для модернизации есть, и для расширения ПСП достаточно будет заменить модули DDIMM на более быстрые варианты.

Сравнительная таблица существующих и будущих версий OpenCAPI Следующее поколение процессоров IBM, POWER10, появится только в 2021 году. К этому времени ожидается принятие стандарта OMI на рынке высокопроизводительных многопроцессорных систем. Попутно IBM готовит новые версии OpenCAPI, не привязанные к архитектуре POWER, а значит, путь к OMI будет открыт и другим вендорам. |

|