Материалы по тегу: panmnesia

|

14.04.2026 [12:44], Владимир Мироненко

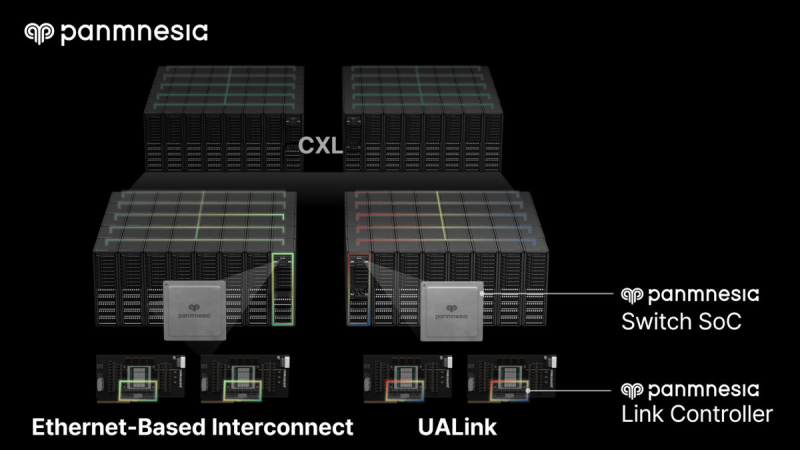

Panmnesia привлёк $10 млн на разработку интерконнекта следующего поколения для ИИ ЦОДЮжнокорейский стартап Panmnesia, специализирующийся на разработке интерконнекта для ИИ-инфраструктур, сообщил о получении финансирования в размере около $10 млн на разработку интерконнекта следующего поколения для ИИ ЦОД. Проект включает разработку контроллеров и коммутаторов на основе открытых стандартов, таких как UALink и протоколов интерконнекта на основе Ethernet. Уже имея обширный портфель продуктов CXL, Panmnesia теперь расширяет свою деятельность в области интерконнекта, ориентированного на ускорители. Компания отметила, что по мере распространения крупномасштабных ИИ-моделей в различных отраслях, ИИ ЦОД всё чаще полагаются на ИИ-ускорители разных вендоров. В этом контексте технологии интерконнекта, обеспечивающие высокоскоростную передачу данных между ускорителями, стали критически важным фактором, определяющим общую производительность ИИ-системы. Также Panmnesia планирует оптимизировать топологию разработанных устройств для ускорения обмена данными между ними и провести валидацию на уровне стойки. Ожидается, что чип-коммутатор с поддержкой интерконнекта, ориентированного на ускорители, такого как UALink, станет доступен во II половине 2027 года. Портфолио продуктов CXL компании включает комплексные решения, в том числе контроллеры и IP-блоки PCIe/CXL, аппаратные SoC, такие, как коммутаторы PCIe/CXL, и специализированные кремниевые решения. В прошлом году Panmnesia представила архитектуру CXL-over-XLink, которая интегрирует специализированные каналы связи для ускорителей (известные как XLink), включая UALink, с CXL для обеспечения расширенной связи в крупных ИИ ЦОД.

19.01.2026 [09:03], Сергей Карасёв

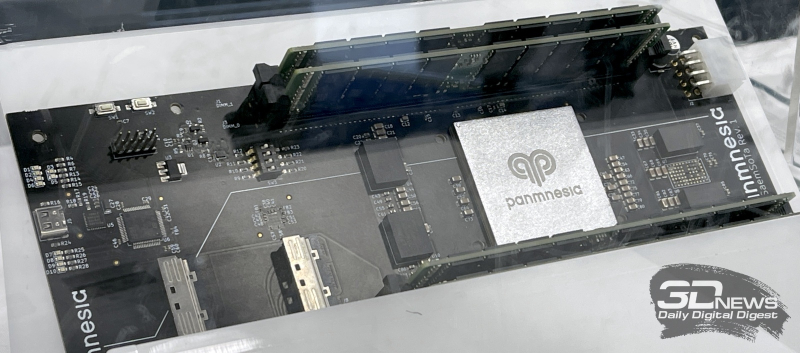

Panmnesia представила чип-коммутатор Panswitch с поддержкой PCIe 6.4 и CXL 3.2Южнокорейский стартап Panmnesia анонсировал чип-коммутатор Panswitch (модель H1SW06245ACFAA), предназначенный для использования в составе масштабных HPC-платформ и дата-центров, ориентированных на задачи ИИ. Кроме того, представлена сопутствующая плата для разработчиков PanRDK. Как утверждается, Panswitch — это первое в мире изделие в своём классе, полностью поддерживающее ключевые функции, описанные в спецификации CXL 3.2, включая Port-based Routing (PBR). Это позволяет соединять тысячи устройств в единой вычислительной среде посредством CXL. Отмечается, что Panswitch даёт возможность формировать сети с различными топологиями — от простых древовидных структур до ячеистых (mesh) конфигураций, систем Dragonfly и пр. Это позволяет оптимизировать пути передачи данных в зависимости от конкретных рабочих нагрузок. В состав Panswitch входит проприетарный CXL-контроллер Panmnesia со сверхнизкой задержкой. Говорится о поддержке интерфейса PCIe 6.4. В целом, как подчёркивает разработчик, Panswitch обеспечивает повышенную производительность и эффективность при крупномасштабных развёртываниях ИИ. В свою очередь, плата PanRDK предназначена для тестирования чипа-коммутатора в реальных условиях. Это решение оснащено FPGA, благодаря чему может быть настроено для работы в качестве различных устройств, в том числе CXL CPU, CXL GPU и пула памяти CXL. Предусмотрены слоты MCIO и CEM, что позволяет сформировать полноценную систему с поддержкой CXL. Плата совместима не только с изделиями Panmnesia, но и с широким спектром решений сторонних производителей, соответствующих стандарту CXL. Поставки чипов Panswitch и пилотных систем уже начались.

16.01.2025 [08:04], Алексей Степин

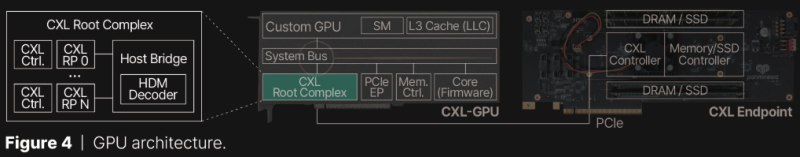

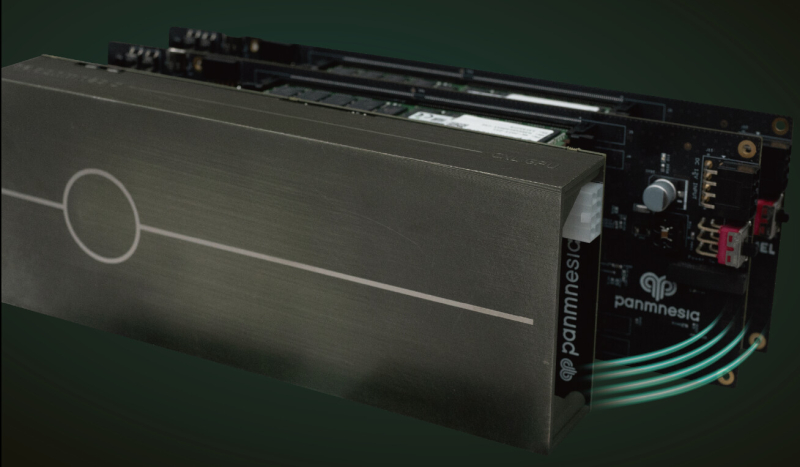

Терабайтные GPU: Panmnesia продемонстрировала CXL-память для ИИ-ускорителейКомпания Panmnesia работает в области проектирования CXL-пулов DRAM довольно давно: в 2023 году она демонстрировала систему, оставляющую позади все решения на базе RDMA и обеспечивающую доступ к 6 Тбайт оперативной памяти. Но большие объёмы памяти сегодня, в эпоху всё более усложняющихся ИИ-моделей, нужны не только и не столько процессорам, сколько ускорителям, априори лишённым возможности апгрейда набортной RAM. На выставке CES 2025 компания продемонстрировала решение данной проблемы. По мнению разработчиков Panmnesia, производительность при обучении масштабных ИИ-моделей упирается именно в объёмы набортной памяти ускорителей: вместо десятков гигабайт требуются уже терабайты, а установка дополнительных ускорителей может обходиться слишком дорого при том, что вычислительные мощности окажутся избыточными. Продемонстрированная на выставке CXL-система построена на базе новейшего контроллера Panmnesia с поддержкой CXL 3.1. В двунаправленном режиме латентность доступа составила менее 100 нс и находится примерно на уровне 80 нс. Ключ к успеху здесь кроется в фирменной реализации CXL 3.1, включая программную часть, благодаря которой GPU могут обращаться к общему пулу памяти, используя те же инструкции типа load/store, что при доступе к набортной HBM или GDDR. Однако технология требует наличия на борту GPU фирменного контроллера CXL Root Complex, одной из важнейших частей которого является декодер HDM, отвечающий за управление адресным пространством памяти (host physical address, HPA), так что уже выпущенные ускорители напрямую работать с системой Panmnesia не смогут. Тем не менее, технология выглядит многообещающей. Она уже привлекла внимание со стороны компаний, занимающихся ИИ, как потенциально позволяющая снизить стоимость инфраструктуры ЦОД.

03.07.2024 [23:49], Сергей Карасёв

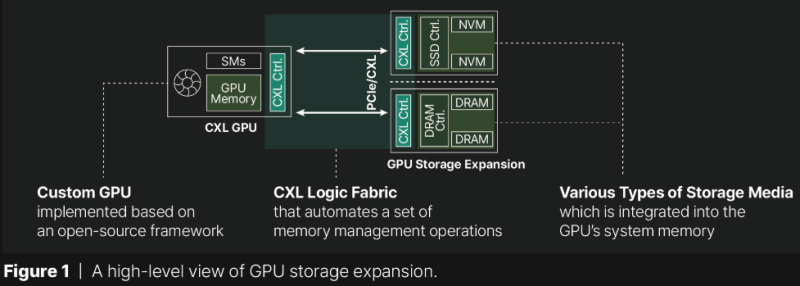

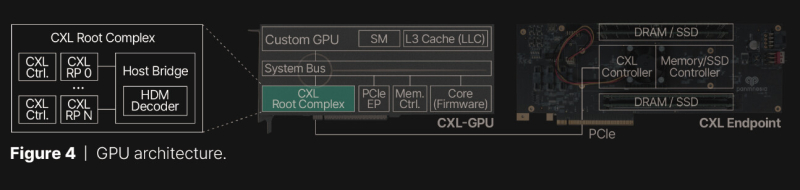

Panmnesia расширит память GPU с помощью DRAM или даже SSDЮжнокорейский стартап Panmnesia сообщил о разработке специализированного CXL-решения, которое позволяет расширять встроенную память ускорителей на базе GPU путём подключения внешних блоков DRAM или даже SSD. Отмечается, что современным приложениям ИИ и НРС требуется значительный объём быстрой памяти, но возможности ускорителей в этом плане ограничены. Сложность расширения памяти актуальных ускорителей заключается в том, что в таких изделиях отсутствуют логическая структура CXL и компоненты, поддерживающие DRAM и/или SSD. Кроме того, подсистемы кеша и памяти GPU не распознают никаких расширений. В лучшем случае предлагается механизм унифицированной виртуальной памяти (UVM) для совместного доступа к содержимому памяти и CPU, и GPU. Однако этот механизм довольно медленный. Panmnesia обошла существующие ограничения путём создания собственного root-комплекса, совместимого со стандартом CXL 3.1 и предоставляющего несколько root-портов. Он и обеспечивает поддержку внешней памяти через PCIe. При этом задействован особый декодер HDM (Host-managed Device Memory), отвечающий за работу с адресными пространствами. Это сложное решение в каком-то смысле «обманывает» подсистему памяти ускорителя, заставляя ее рассматривать внешнюю PCIe-память как доступную напрямую. Прототип, основанный на кастомизированном GPU, в ходе тестов продемонстрировало задержки менее 100 нс при передаче данных в обоих направлениях. При этом решение Panmnesia предоставляет более гранулярный доступ к памяти в сравнении с UVM. Быстродействие CXL-системы Panmnesia оказалось в 3,22 раза выше в пересчёте на IPC по сравнению с UVM.

14.08.2023 [17:37], Алексей Степин

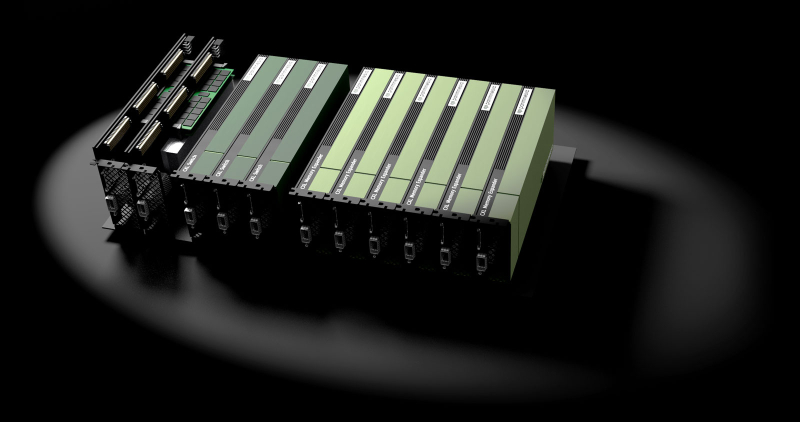

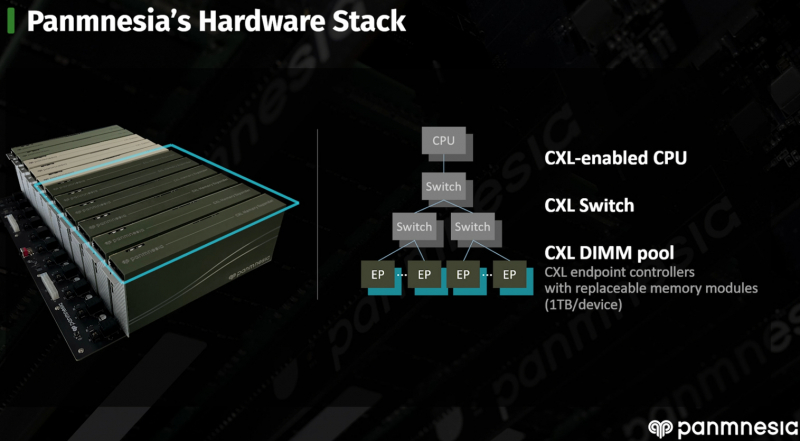

CXL-пул Panmnesia втрое быстрее RDMA-систем и может предложить 6 Тбайт RAMНа конференции Flash Memory Summit южнокорейская компания Panmnesia продемонстрировала свою версию CXL-пула DRAM объёмом 6 Тбайт на базе программно-аппаратного стека собственной разработки. Новинка продемонстрировала более чем троекратное превосходство над системой, построенной на базе технологии RDMA, в нагрузках, связанной с работой рекомендательной ИИ-системы Meta✴. Panmnesia разработана в сотрудничестве с Корейским инститом передовых технологий (KAIST). О более раннем варианте разработок KAIST в этой области мы рассказывали в 2022 году. Коммерческий вариант комплекса поддерживает CXL 3.0 и состоит из CXL-процессора, коммутатора и модулей расширения памяти. Все модули выполнены в форм-факторе, чрезвычайно напоминающем FHFL-карты. Модули устанавливаются в универсальное шасси, при этом их можно произвольно комбинировать. Демо-платформа содержала два процессорных модуля, три модуля коммутации и шесть 1-Тбайт модулей памяти. Модули памяти построены на базе обыкновенных DIMM-планок и поддерживают их замену и расширение. Реализован не только режима CXL.mem, но и CXL.cache и CXL.io. При этом компания предлагает не только готовые IP-решения, но и их кастомизацию под конкретного заказчика, что поможет оптимизировать цикл создания продукта и снизить общую стоимость разработки и валидации. Фирменное ПО базируется на Linux и содержит необходимые драйверы, а также специализированную виртуальную машину, с помощью которой пространство памяти представляется в виде безпроцессорного NUMA-узла. Поверх этих компонентов функционирует пользовательская часть, отвечающая за эффективное размещение и предвыборку (prefetching) данных. По ряду параметров Panmnesia можно назвать лидером в области CXL-решений. В частности, по объёму DRAM она уже обгоняет совместное решение Samsung, MemVerge, H3 и XConn, а использование DIMM-модулей только придаёт ей гибкости. Развитая программная часть, как утверждается, упрощает и удешевляет интеграцию в существующую инфраструктуру ЦОД. Спектр применения, как и у всех систем CXL-пулинга, крайне широкий и включает в себя не только ИИ-сценарии, но и любые задачи, требующие большого объёма оперативной памяти. |

|