Материалы по тегу: cpu

|

12.08.2024 [09:53], Владимир Мироненко

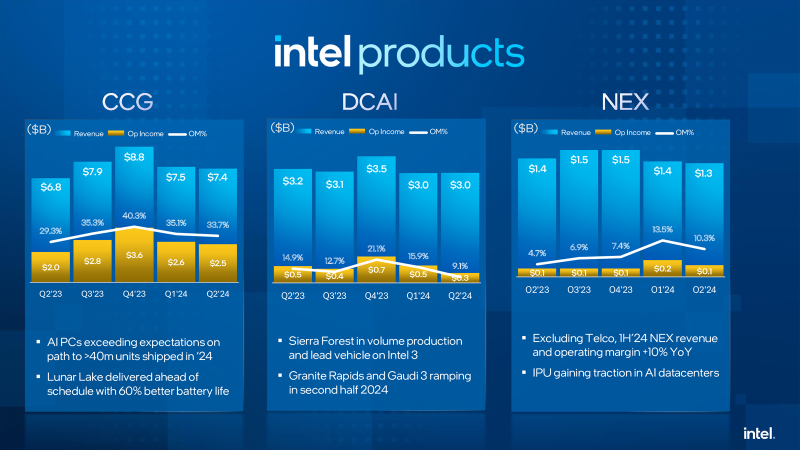

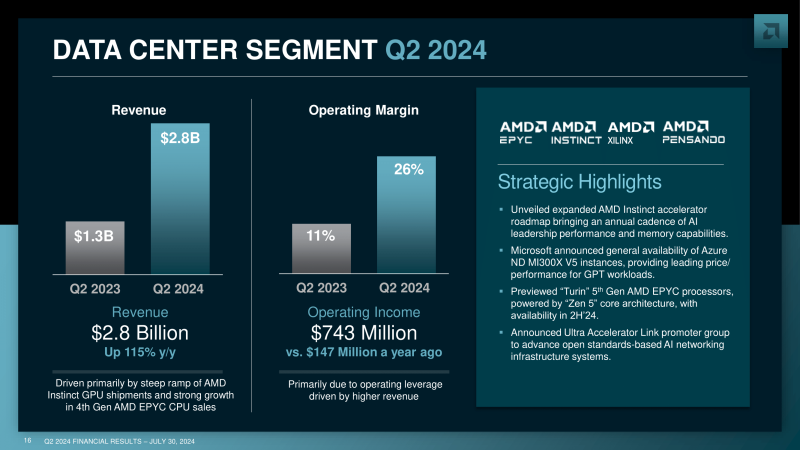

Mercury Research: Intel под натиском AMD теряет долю на рынке CPUIntel постепенно теряет лидирующие позиции на рынке серверных, настольных и мобильных процессоров, хотя по-прежнему удерживает его львиную долю, пишет The Register со ссылкой на исследование Mercury Research, сделанное по итогам II квартала 2024 года. Согласно данным Mercury Research, Intel потеряла год к году несколько п.п. доли рынка в каждой из трёх основных категорий CPU — серверных, настольных и мобильных — в то время как доля AMD выросла. Самых больших успехов AMD добилась в сегменте серверных процессоров, где увеличила долю рынка на 5,6 % до 24,1 % поставок, что также превышает показатель предыдущего квартала. В сегменте мобильных устройств доля поставок AMD выросла на 3,8 % до 20,3 % по сравнению с аналогичным периодом прошлого года, что также немного больше показателей I квартала. Вместе с тем суммарные поставки процессоров во II квартале снизились по сравнению с I кварталом, что, как отметили аналитики, ниже обычных сезонных колебаний. Mercury Research объясняет сокращение рынка гораздо более низкими поставками в сегментах Интернета вещей (IoT) и систем на кристалле (SoC) — рынках встраиваемых решений — из-за более слабого спроса на эти чипы, особенно на SoC AMD для игровых консолей. Также сократились поставки мобильных процессоров начального уровня, в основном используемых в Chromebook. Если учитывать этот нюанс, то Intel фактически увеличила общую долю рынка — на 7 % по сравнению с прошлым годом, что в Mercury Research объясняют сокращением выпуска AMD SoC. Хотя AMD увеличила общую долю клиентских и серверных решений, этого оказалось недостаточно для компенсации резкого сокращения поставок SoC, заявил президент Mercury Research Дин Маккаррон (Dean McCarron). Intel завершила II квартал 2024 года с убытками в размере $1,61 млрд, хотя годом ранее у неё была в аналогичном квартале чистая прибыль в размере $1,48 млрд. В связи с этим компания объявила план по сокращению расходов, включающий увольнение более 16 000 сотрудников — не менее 15 % персонала — и сокращение капитальных вложений более чем на 20 % до $25–27 млрд. Ранее Intel была вынуждена признать наличие проблем у некоторыми из своих процессоров Raptor Lake 13-го и 14-го поколений, и выпускает исправление микрокода для их устранения, которое включено в обновления BIOS. Руководитель Intel Пэт Гелсингер (Pat Gelsinger), объяснил слабые показатели II квартала ограничениями США на экспорт поставок чипов в Китай, но, как отметил The Register, на этом также отразился тот факт, что у компании нет популярных ИИ-ускорителей, тогда как на фоне бума ИИ в поставках для ЦОД преобладают именно такие чипы. В свете этого тренда Mercury Research отметила, что и AMD, и Intel показали скромное увеличение поставок серверных CPU во II квартале, что примечательно, поскольку «рынок обычных серверных процессоров значительно замедлился из-за переключения спроса ЦОД на ИИ-ускорители». Mercury Research сообщила, что рост у Intel наблюдался в основном в сегменте сетевых и периферийных процессоров, а не традиционных процессоров для ЦОД, где доходы Intel, по её данным, были стабильными. Что касается процессоров Arm, то по данным Mercury Research, доля рынка ПК с этой архитектурой снизилась до 10 % с 11 % в I квартале, несмотря на широко разрекламированный запуск серии Windows-компьютеров Copilot+ PC на базе чипов Qualcomm в мае этого года. По словам Mercury Research, падение было вызвано значительным снижением спроса на процессоры для Chromebook и снижением поставок Arm-компьютеров Apple Mac. Поставки систем класса Copilot+ PC были слишком малы, чтобы компенсировать это падение.

10.08.2024 [11:49], Владимир Мироненко

Уязвимость Sinkclose в процессорах AMD позволяет вывести из строя компьютер без возможности восстановленияЭнрике Ниссим (Enrique Nissim) и Кшиштоф Окупски (Krzysztof Okupski), исследователи из компании IOActive, занимающейся вопросами безопасности обнаружили уязвимость в чипах AMD, выпускаемых с 2006 года или, возможно, даже раньше, которая позволяет вредоносному ПО проникать настолько глубоко в систему, что во многих случая её проще выбросить, чем пытаться восстановить, пишет ресурс Wired. Получившая идентификатор CVE-2023-31315 с высоким уровнем опасности (CVSS 7,5) уязвимость была названа исследователями Sinkclose. Уязвимость позволяет злоумышленникам с привилегиями уровня ядра ОС (Ring 0) получать привилегии Ring -2 и устанавливать вредоносное ПО, которое очень сложно обнаружить. Благодаря Sinkclose злоумышленники могут изменять настройки одного из самых привилегированных режимов процессора AMD — SMM, предназначенного для обработки общесистемных функций, таких как управление питанием и контроль оборудования, даже если включена блокировка SMM. Эта уязвимость может использоваться для отключения функций безопасности и внедрения на устройство постоянного, практически необнаруживаемого вредоносного ПО. Ring -2 изолирован и невидим для ОС и гипервизора, поэтому любые вредоносные изменения, внесённые на этом уровне, не могут быть обнаружены или исправлены инструментами безопасности, работающими в ОС. Вредоносное ПО, известное как буткит, которое обходит антивирусные инструменты и потенциально невидимо для операционной системы, предоставляет хакеру полный доступ для вмешательства в работу компьютера и наблюдения за её активностью. По словам Окупски, единственный способ обнаружить и удалить вредоносное ПО, установленное с помощью SinkClose — это физическое подключение с помощью программатора SPI Flash и сканирование памяти на наличие вредоносного ПО. Полные сведения об уязвимости будут представлены исследователями на конференции DefCon в докладе «AMD Sinkclose: Universal Ring -2 Privilege Escalation». Исследователи говорят, что предупредили AMD об уязвимости в октябре прошлого года, и не сообщали о баге почти 10 месяцев, чтобы дать AMD больше времени для устранения проблемы. Комментируя сообщение исследователей, компания AMD указала в заявлении для Wired на сложность использования уязвимости в реальных сценариях, поскольку злоумышленникам требуется доступ на уровне ядра. В ответ исследователи заявили, что подобные уязвимости выявляются в Windows и Linux практически каждый месяц. Они отметили, что опытные хакеры, спонсируемые государством, которые могут воспользоваться Sinkclose, вероятно, уже обладают методами использования подобных уязвимостей. Как ожидают исследователи, для компьютеров с Windows патчи против Sinkclose будут интегрированы в обновления, которыми производители компьютеров поделятся с Microsoft. Исправления для серверов, встраиваемых систем и Linux-машин могут быть более пошаговыми и ручными; для Linux это будет частично зависеть от дистрибутива. AMD указала в заявлении, что уже приняла меры по смягчению последствий для своих процессоров EPYC и AMD Ryzen для настольных и мобильных систем, а дополнительные исправления для встроенных процессоров появятся позже. Согласно AMD, уязвимость имеется в следующих чипах:

UPD 11.08.2024: патчи не получат Ryzen 1000, 2000 и 3000, а также Threadripper 1000 и 2000. Не упомянуты и Ryzen 9000 с Ryzen AI 300, но в этих процессорах уязвимость наверняка устранена ещё до их выхода на рынок. UPD 21.08.2024: Ryzen 3000 всё-таки получит патчи против Sinkclose.

03.08.2024 [12:33], Сергей Карасёв

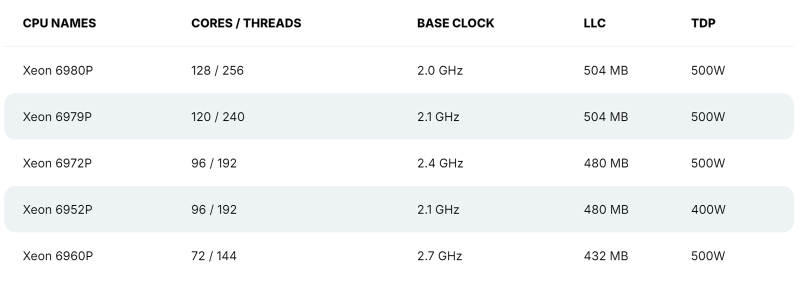

128 P-ядер, 504 Мбайт кеша и TDP 500 Вт: утекли характеристики Intel Xeon Granite RapidsВ распоряжении сетевых источников, по сообщению ресурса VideoCardz, оказалась информация о характеристиках части процессоров Intel Xeon 6 семейства Granite Rapids, в основу которых лягут производительные ядра P-core. Речь идёт о чипах Xeon 6900P, которые, как ожидается, появятся на рынке в текущем квартале. Формальная презентация Xeon 6 Granite Rapids состоялась в начале июня текущего года — вместе с изделиями Xeon 6 Sierra Forest, построенными на энергоэффективных ядрах E-core. Для платформы Xeon 6 предусмотрено использование разъёмов LGA-4710 и LGA-7529: в первом случае заявлена поддержка чипов с TDP до 350 Вт и 8-канальной памяти, во втором — 500 Вт и 12-канальной памяти. При этом в обоих вариантах возможно построение двухсокетных серверов. Как стало известно, в семейство Xeon 6 Granite Rapids войдут модели с 32, 44, 56, 72, 96, 120 и 128 ядрами Redwood Cove. Они получат поддержку SMT и до 504 Мбайт L3-кеша. Величина TDP составит до 500 Вт. В частности, говорится о подготовке процессоров Xeon Platinum 6980P, 6979P, 6972P, 6952P и 6960P. Их базовая тактовая частота варьируется от 2,0 до 2,7 ГГц (см. характеристики). Для чипов Xeon 6 Granite Rapids заявлена поддержка памяти DDR5-6400 и MCR-8800, до 96 линий PCIe Gen 5.0/CXL 2.0 и до 6 линий UPI 2.0.

01.08.2024 [23:55], Алексей Степин

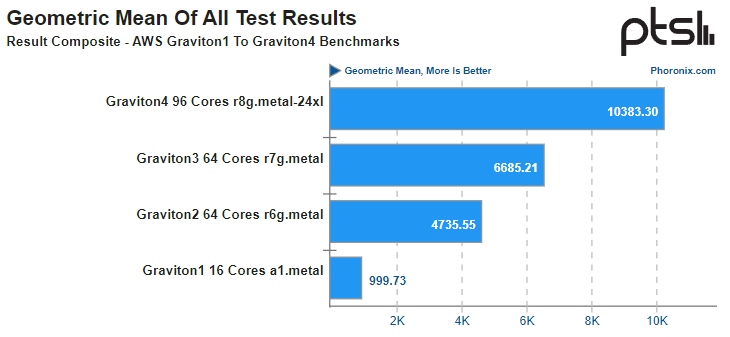

Arm-процессоры AWS Graviton4 успешно конкурируют с актуальными Intel Xeon, а иногда обгоняют даже AMD EPYCВсего за пять лет Amazon успела разработать и внедрить четыре поколения серверных Arm-процессоров Graviton. 4-нм Graviton4 получили 96 ядер и 12 каналов памяти DDR5-5600, а также поддержку PCIe 5.0. Всё это дало AWS основание утверждать, что Graviton4 производительнее предшественника на 30 %, а пропускная способность памяти у него выше на 75 %. Насколько это соответствует истине, выяснил ресурс Phoronix, который заодно сравнил новинки с другими современными процессорами. В тестировании Phoronix приняли участие следующие модели Graviton:

Источник: AWS Платформа Graviton в последней итерации выглядит вполне достойно. Она использует современный набор инструкций Arm, а по количеству ядер и каналов памяти сопоставима с новейшими решениями Intel и AMD. Производительность по мере смены поколений у Graviton растёт практически линейно, за исключением перехода от первого поколения ко второму, что легко объясняется возросшим сразу вчетверо количеством ядер. Что касается Graviton4, то новые процессоры в среднем быстрее Graviton3 примерно в 1,55 раза, а первенца серии они превосходят в 10,4 раза. В некоторых случаях выигрыш выходит далеко за рамки теоретических 1,5x, поскольку у Graviton4 более совершенная архитектура, новее набор инструкций, вдвое больший объем кеша на ядро и существенно более производительная подсистема памяти. Такое поведение, к примеру, характерно для тестов srsRAN, задач криптографии и особенно работы с базами данных.

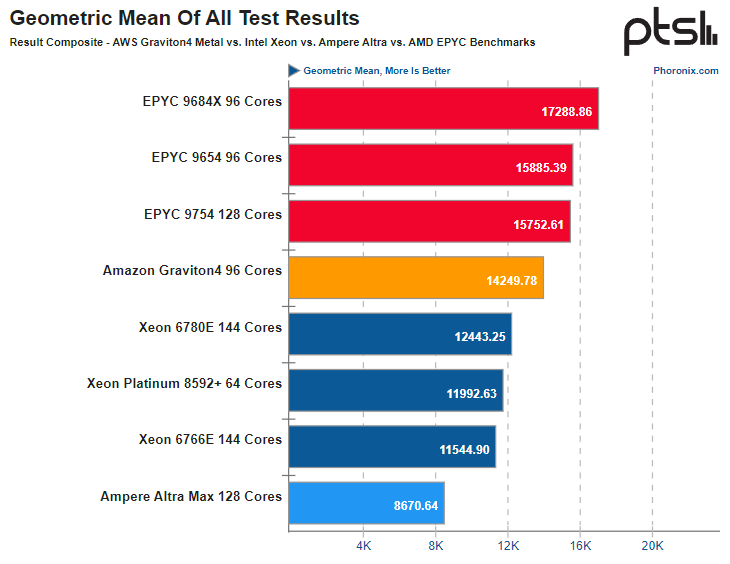

Источник здесь и далее: Phoronix В другом исследовании Phoronix процессорам Graviton4 довелось столкнуться с серьёзными соперниками из мира x86, включая 128-ядерный AMD EPYC 9754 (Bergamo) и 144-ядерные Intel Xeon 67xx (Sierra Forest), а также с ближайшим конкурентом по Arm-платформе, 128-ядерным процессором Ampere Altra Max. К сожалению, метрик энергопотребления в текущей версии инстанса r8g.metal-24xl получить не удалось, но и без этого результаты получены весьма интересные. С первых тестов очевидно, что Altra Max уже не соперник современным решениям, несмотря на сопоставимое количество ядер — сказывается не самая новая архитектура. А вот Graviton4 чувствует себя неплохо и в тестах на компиляцию может опережать даже AMD EPYC 9754. Хороша новинка и в базах данных, она лишь немного уступает процессорам Genoa и зачастую опережает 144-ядерное решение Intel c E-ядрами. И даже в HPC-нагрузках, для которых характерно активное использование FP-вычислений у Graviton4 всё хорошо! Неплохо себя детище AWS чувствует и в сценариях (де-)компрессии данных и кодировании видео.  В итоговом зачёте AWS Graviton4 уверенно занимает место в середине таблицы, опережая оба Xeon — и 64-ядерный Platinum 8592+ (Emerald Rapids), и 144-ядерный Xeon 6780E, но до уровня AMD EPYC 9754 всё же несколько недотягивая. Это вполне даёт основание считать, что платформа AWS Graviton достигла зрелости. Она вполне конкурентоспособна даже на фоне x86-монстров. Более того, на сегодня Graviton4 можно считать самым продвинутым серверным процессором с архитектурой AArch64. Впрочем, вскоре предстоят сражения с Granite Rapids, Turin и AmpereOne (а на подходе ещё и Aurora с HBM).

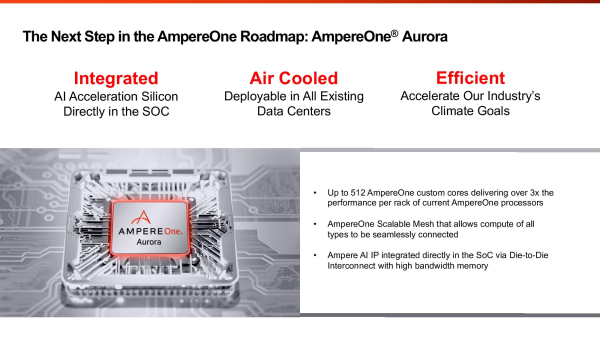

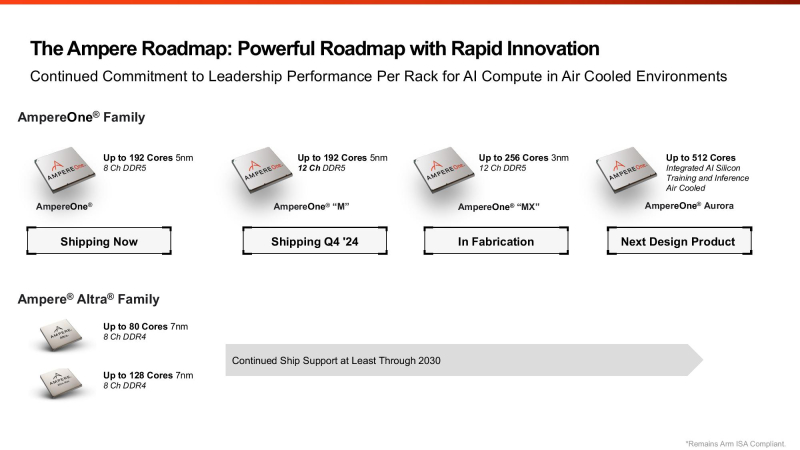

01.08.2024 [00:53], Игорь Осколков

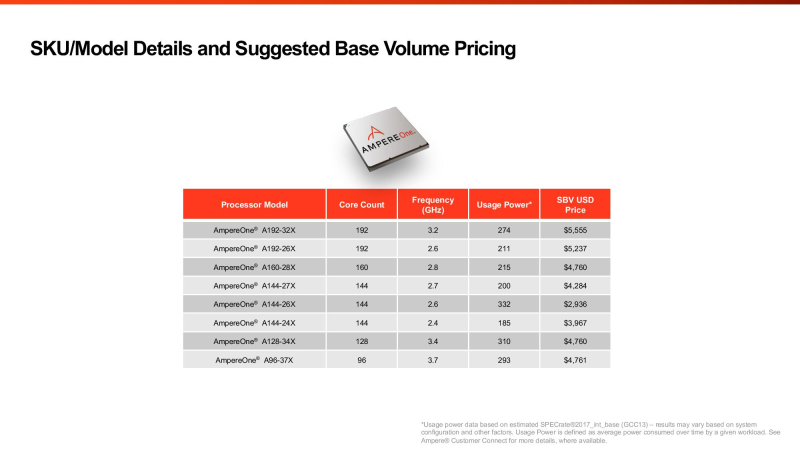

Ampere анонсировала 512-ядерные Arm-процессоры AmpereOne Aurora с HBM-памятью и встроенным ИИ-ускорителемAmpere Computing анонсировала процессоры AmpereOne Aurora, которые получат до 512 однопоточных Arm-ядер собственной разработки, набортную HBM-память и фирменные IP-блоки для обучения и инференса ИИ-моделей. Речь, судя по всему, идёт о чиплетной компоновке, поскольку компания говорит не только о фирменном меш-интерконнекте для вычислительных блоков, но и об объединении разных кристаллов в рамках SoC. Предполагается, что Aurora появятся где-то на рубеже 2025–2026 гг. Что интересно, для Aurora обещана возможность использования воздушного охлаждения. Для гиперскейлеров, на которых Ampere по-прежнему ориентируется, это важный пункт. Впрочем, больше никаких подробностей о новинках компания не сообщила, отметив лишь, что встроенный ускоритель сгодится для RAG и векторных баз данных. Ну и сообщив, что по количеству ядер и производительности её ещё не выпущенный чип обгоняет все остальные чипы: 144-ядерные Intel Xeon 6 (Sierra Forest), которые вскоре станут 288-ядерными (при этом все варианты без Hyper-Threading), и 128-ядерные AMD EPYC Bergamo (256 потоков), которым на смену придут 192-ядерные EPYC Turin Dense (384 потока). До Aurora компания выпустит ещё две серии процессоров AmpereOne: M в конце 2024 года и MX в 2025 году. 5-нм AmpereOne M получат до 192 ядер и 12-канальный контроллер памяти DDR5. 3-нм AmpereOne MX получат такой же контроллер и до 256 ядер. Заодно компания опубликовала прайс-лист актуальных CPU. В нём нет изначально заявлявшихся 136- и 172-ядерных моделей. Кроме того, остальные процессоры несколько подорожали в сравнении с прошлым поколением Altra Max, но по цене всё ещё привлекательнее решений AMD и Intel — $5555 за 192 ядра. Следует учесть, что в таблице приведён не привычный показатель TDP, а усреднённое энергопотребление чипа, из-за чего сравнивать процессоры Ampere с другими чипами затруднительно. Насколько Aurora станет популярным у гиперскейлеров и других заказчиков, покажет время. У Ampere есть якорный заказчик в лице Oracle, но другие IT-гиганты уже сами разрабатывают собственные Arm-процессоры. AWS в Graviton4 довела количество ядер до 96, Microsoft анонсировала 128-ядерный Cobalt 100, Alibaba массово внедряет 128-ядерные Yitian 710, а Google готовит Axion. Fujitsu к 2027 году подготовит 144-ядерные MONAKA, которые тоже получат поддержку ИИ-нагрузок, но упор в них сделан не на HBM, а на SRAM. Собственно говоря, HBM есть только у HPC-процессоров: Fujitsu A64FX, SiPearl Rhea1 и C-DAC AUM. Даже NVIDIA Grace, которые в основном ассистируют ускорителям, обходятся LPDDR5x.

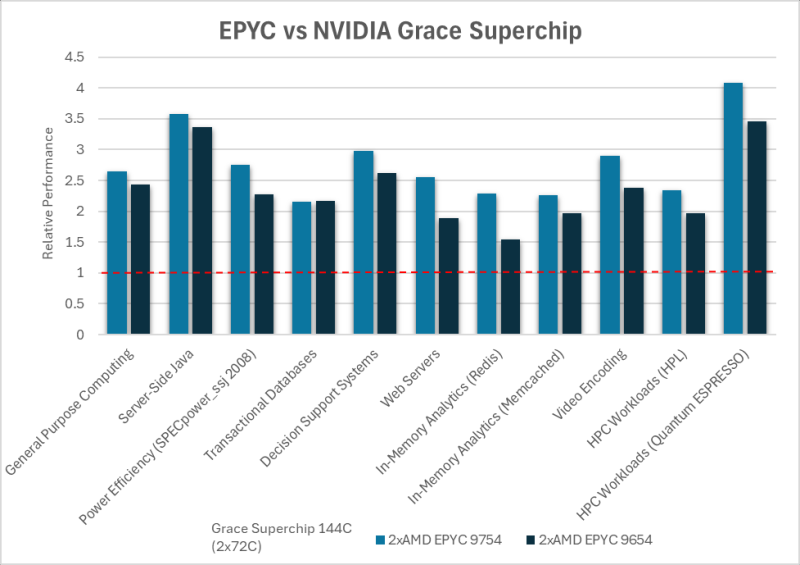

25.07.2024 [10:12], Владимир Мироненко

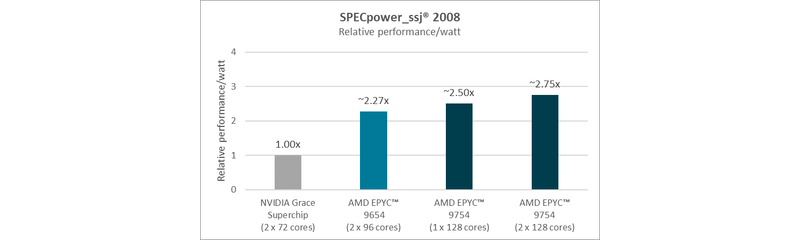

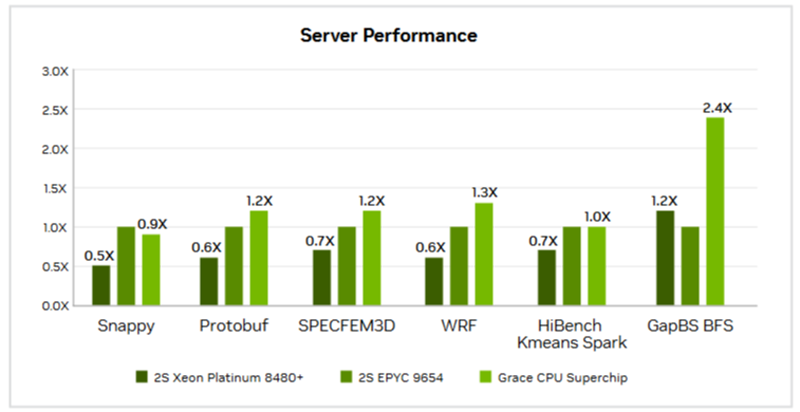

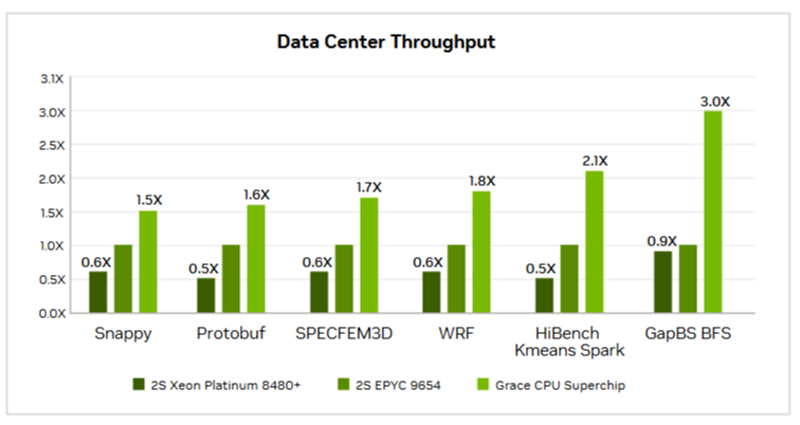

AMD показала превосходство чипов EPYC над Arm-процессорами NVIDIA Grace в серии бенчмарков, но не всё так простоAMD провела серию тестов, чтобы доказать преимущество своих нынешних процессоров AMD EPYC над Arm-процессорами NVIDIA Grace Superchip. Как отметила AMD, в связи с растущей востребованностью ЦОД некоторые компании начали предлагать альтернативные варианты процессоров, «часто обещающие преимущества по сравнению с обычными решениями x86». «Обычно их представляют с большой помпой и заявлениями о значительных преимуществах в производительности и энергоэффективности по сравнению с x86. Слишком часто эти утверждения довольно сложно воплотить в реальные сценарии конкурентной рабочей нагрузки — с использованием устаревших, недостаточно оптимизированных альтернатив или плохо документированных предположений», — отметила AMD. С помощью серии стандартных отраслевых тестов AMD, по её словам, продемонстрировала преимущество EPYC над решениями на базе Arm. «Благодаря проверенной архитектуре x86-64, впервые разработанной AMD, вы можете получить всё это без дорогостоящего портирования или изменений в архитектуре», — подчеркнула компания. Иными словами, тесты AMD могут быть просто попыткой развеять опасения, что архитектура x86 «выдыхается» и что Arm берёт верх. AMD сравнила производительность AMD EPYC и NVIDIA Grace CPU в десяти ключевых рабочих нагрузках, охватывающих вычисления общего назначения, Java, транзакционные базы данных, системы поддержки принятия решений, веб-серверы, аналитику, кодирование видео и нагрузки HPC. Согласно представленному выше графику, 128-ядерный процессор EPYC 9754 (Bergamo) и 96-ядерный EPYC 9654 (Genoa) более чем вдвое превзошли NVIDIA Grace CPU Superchip по производительности при обработке вышеуказанных нагрузок. Напомним, что Grace CPU Superchip содержит два 72-ядерных кристалла Grace, использующих ядра Arm Neoverse V2, соединённых шиной NVLink C2C с пропускной способность 900 Гбайт/с, и работает как единый 144-ядерный процессор. В свою очередь, ресурс The Register отметил, что речь идёт о версии с 480 Гбайт памяти LPDDR5x, а не с 960 Гбайт.  В тесте SPECpower-ssj2008, по данным AMD, одно- и двухсокетные системы на базе AMD EPYC 9754 превосходят систему NVIDIA Grace CPU Superchip по производительности на Вт примерно в 2,50 раза и 2,75 раза соответственно, а двухсокетная система AMD EPYC 9654 — примерно в 2,27 раза. Помимо производительности и эффективности, ещё одним важным фактором для операторов ЦОД является совместимость, сообщила AMD. По оценкам, во всем мире существуют триллионы строк программного кода, большая часть которого написана для архитектуры x86. EPYC основаны на архитектуре x86-64, впервые разработанной AMD, и эта архитектура является наиболее широко используемой и поддерживаемой в индустрии ЦОД, заявила компания, добавив, что изменения в архитектуре сложны, дороги и чреваты риском. AMD также отметила, что экосистема AMD EPYC включает более 250 различных конструкций серверов и поддерживает около 900 уникальных облачных инстансов. Также процессоры AMD EPYC установили более 300 мировых рекордов производительности и эффективности в широком спектре тестов. В то же время лишь немногие Arm-решения доказали свою эффективность. В свою очередь, ресурс The Register отметил, что ситуация не так проста, как AMD пытается всех убедить. В феврале сайт The Next Platform сообщил, что исследователи из университетов Стоуни-Брук и Буффало сравнили данные о производительности суперчипа NVIDIA Grace CPU Superchip и нескольких процессоров x86, предоставленные несколькими НИИ и разработчиком облачных решений.

Источник изображений: NVIDIA Большинство этих тестов были ориентированы на HPC, включая Linpack, HPCG, OpenFOAM и Gromacs. И хотя производительность системы Grace сильно различалась в разных тестах, в худшем случае она находилась где-то между Intel Skylake-SP и Ice Lake-SP, превосходя AMD Milan и находясь в пределах досягаемости от показателей Xeon Max. Данные результаты отражают тот факт, что самые мощные процессоры AMD EPYC Genoa и Bergamo могут превзойти первый процессор NVIDIA для ЦОД — при правильно выбранном тесте.  В техническом описании Grace CPU Superchip компания NVIDIA сообщает, что этот чип обеспечивает от 0,9- до 2,4-кратного увеличения производительности по сравнению с двумя 96-ядерными EPYC 9654 и предлагает до трёх раз большую пропускную способность в различных облачных и HPC-сервисах. NVIDIA отмечает, что Superchip предназначен для «обработки массивов для получения интеллектуальных данных с максимальной энергоэффективностью», говоря об ИИ, анализе данных, нагрузках облачных гиперскейлеров и приложениях HPC.

22.07.2024 [09:12], Сергей Карасёв

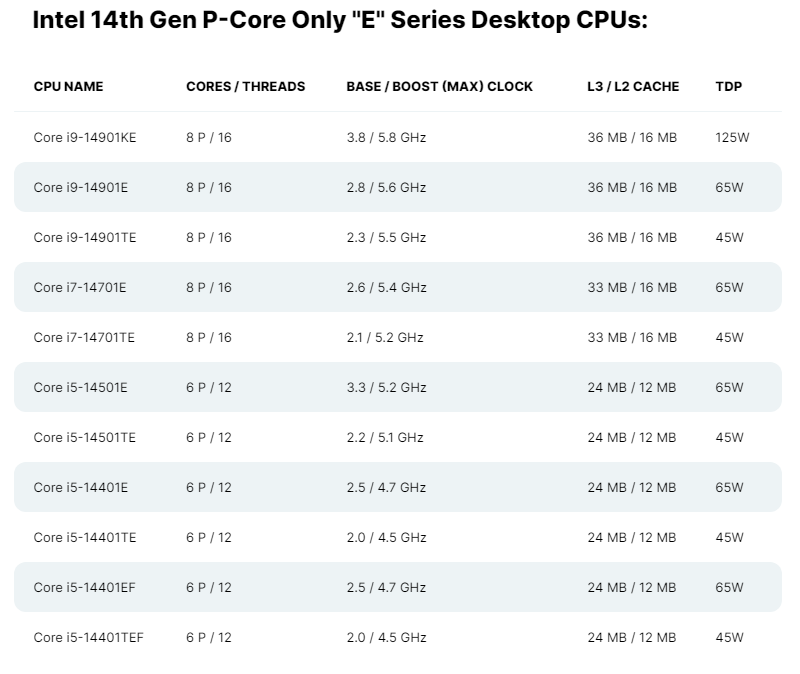

Intel представила чипы Raptor Lake Refresh с отключёнными E-ядрами для встраиваемых устройствКомпания Intel, по сообщению ресурса Wccftech, анонсировала процессоры Raptor Lake Refresh (Core 14-го поколения) для встраиваемых устройств. У этих чипов деактивирован кластер энергоэффективных Е-ядер (Gracemont) — они оперируют только производительными Р-ядрами (Raptor Cove). В общей сложности перечислены 11 моделей: Core i9-14901KE, Core i9-14901E, Core i9-14901TE, Core i7-14701E, Core i7-14701TE, Core i5-14501E, Core i5-14501TE, Core i5-14401E, Core i5-14401TE, Core i5-14401EF и Core i5-14401TEF. Они имеют исполнение LGA1700, а показатель TDP варьируется от 45 до 125 Вт. На вершине семейства располагается изделие Core i9-14901KE с восемью ядрами (16 потоков), базовая частота которого составляет 3,8 ГГц с возможностью динамического повышения до 5,8 ГГц. Объём кеша третьего уровня равен 36 Мбайт. Индекс «К» в обозначении указывает на возможность разгона. Возможно, данная особенность заинтересует DIY-энтузиастов.

Источник изображения: Wccftech В зависимости от модификации новые процессоры насчитывают шесть или восемь Р-ядер, при этом все чипы поддерживают технологию многопоточности. Возможна работа с двухканальной оперативной памятью DDR4/DDR5. Изделия с индексом «F» не имеют встроенного графического контроллера, тогда как модели «Т» обладают повышенной энергоэффективностью. Среди прочего упомянута поддержка PCIe 5.0 x16, PCIe 4.0 x4 (NVMe) и DMI 4.0 x8.

17.07.2024 [13:16], Сергей Карасёв

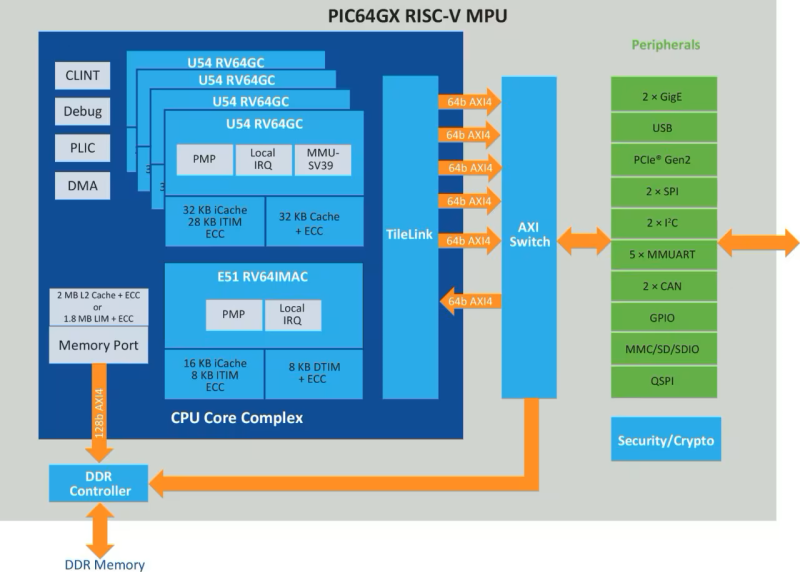

Microchip представила свои первые 64-бит чипы PIC64GX на архитектуре RISC-VКомпания Microchip Technology анонсировала изделия PIC64GX — своё первое семейство 64-бит чипов, выполненных на открытой архитектуре RISC-V. Среди ключевых сфер применения названы устройства для промышленного, автомобильного, коммуникационного, аэрокосмического и оборонного сегментов, а также для Интернета вещей. Первым представителем нового семейства стал чип PIC64GX1000. Он содержит четыре 64-битных ядра SiFive U54 (RV64GC) без внеочередного исполнения инструкций, но с блоком управления памятью (MMU). Тактовая частота достигает 625 МГц. Кроме того, присутствует вспомогательное ядро SiFive E51 RISC-V (RV64IMAC) с той же частотой, отвечающее за функции мониторинга. Чип может работать как в режиме SMP, так и AMP. Заявленный уровень производительности составляет порядка 5 тыс. DMIPS. Реализована подсистема кеша L1 с функциями коррекции ошибок Single-Error Correct, Double-Error Detect (SECDED). Объём кеша L2 с поддержкой SECDED составляет 2 Мбайт (SRAM). Все кеши можно переконфигурировать под свои нужды. Также есть 128 Кбайт энергонезависимой памяти для загрузчика и 56 Кбайт защищённой памяти для хранения пользовательских данных и ключей. Имеется встроенный 36-бит контроллер памяти (LP)DDR4-1333 (SECDED) с поддержкой до 32 Гбит на DDR-интерфейс. Реализована поддержка интерфейсов MMC 5.1, SD, SDIO, HDMI 1.4, MIPI CSI-2 (две линии), 2 × 1GbE, USB 2.0 OTG, PCIe 2.2 x4 (версия FCV) или x1 (модификация FCS), 2 × SPI, 5 × UART, 2 × I2C, 32 × GPIO, 2 × CAN. Средства обеспечения безопасности включают AES/SHA (256 бит), TRNG, HMAC, RSA, ECDSA. Доступны варианты упаковки FCSG325 (11 × 11 × 0,5 мм) c 200 контактами и FCVG484 (19 × 19 × 0,8 мм) с 244 контактами. Будут предлагаться коммерческая и индустриальная модификации: в первом случае диапазон рабочих температур простирается от 0 до +100 °C, во втором — от -40 до +100 °C.

12.07.2024 [09:09], Алексей Степин

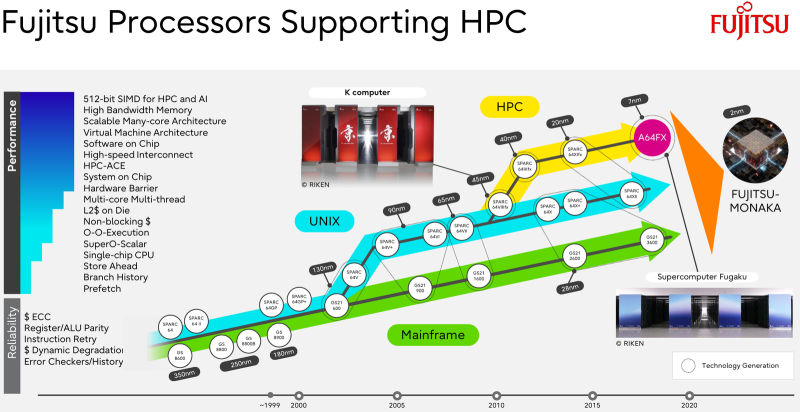

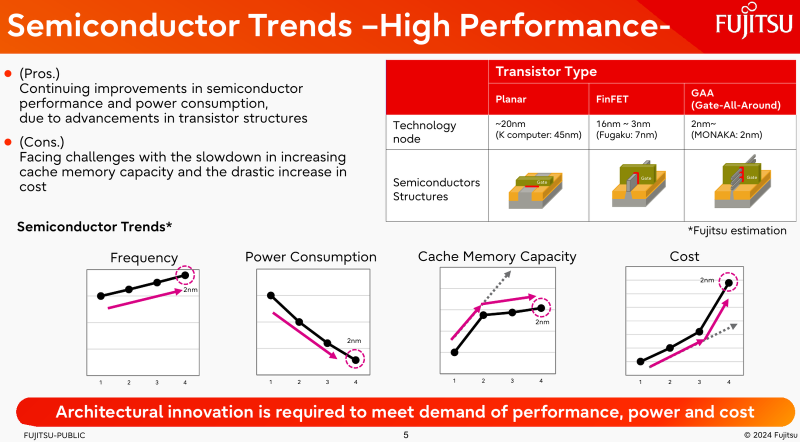

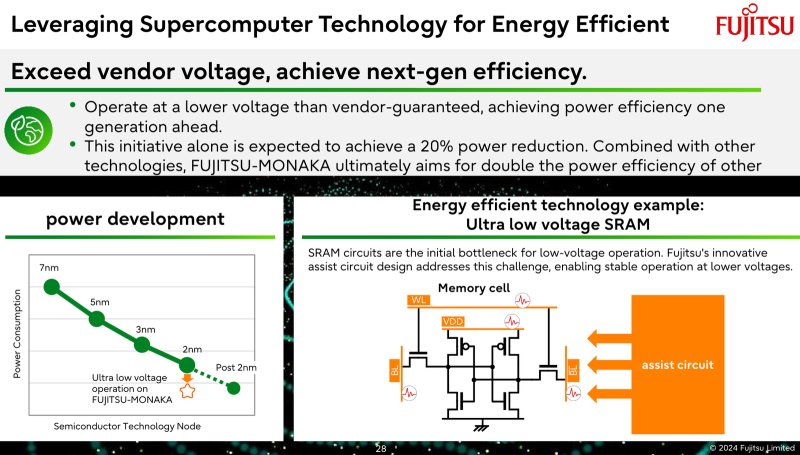

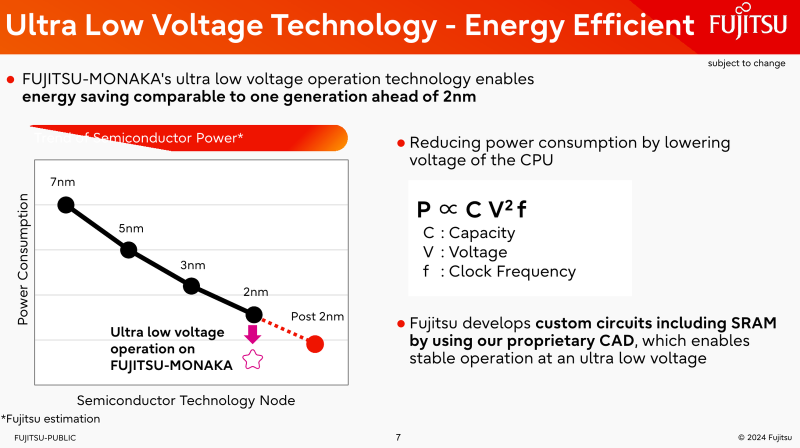

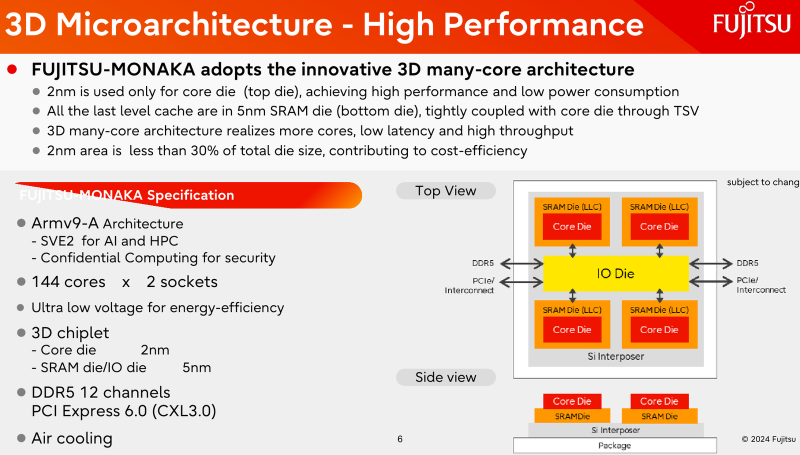

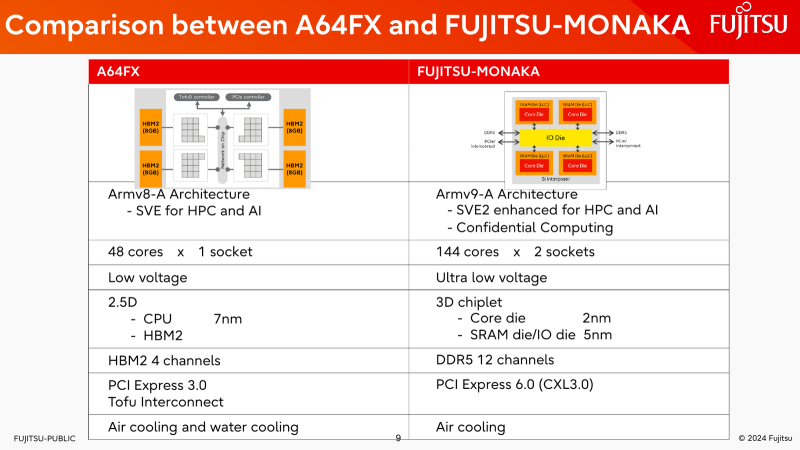

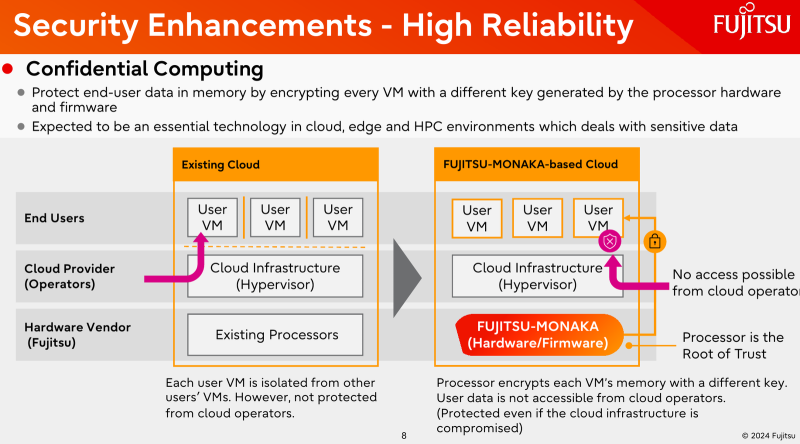

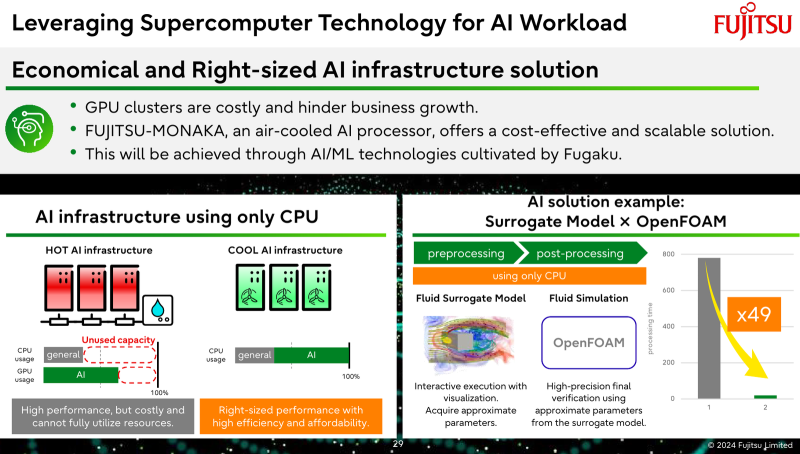

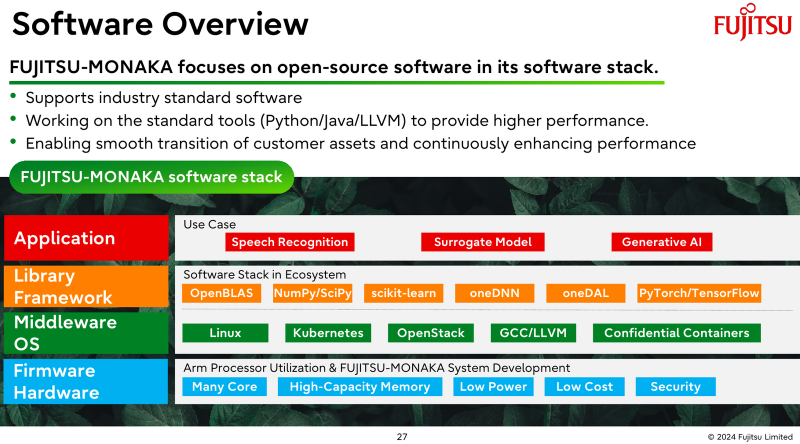

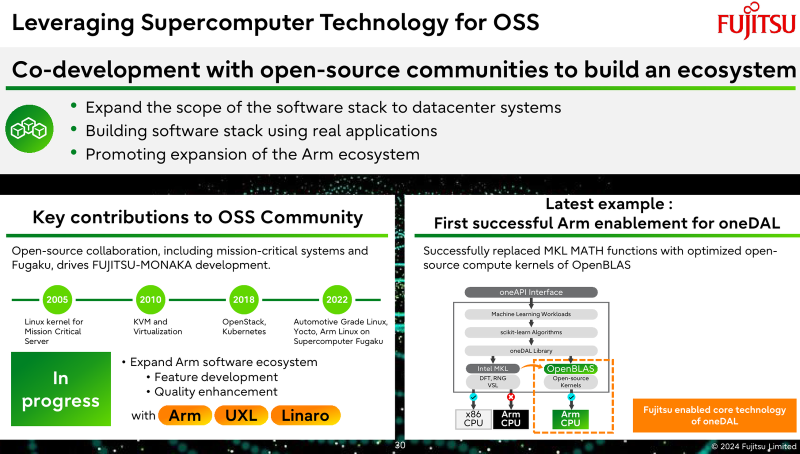

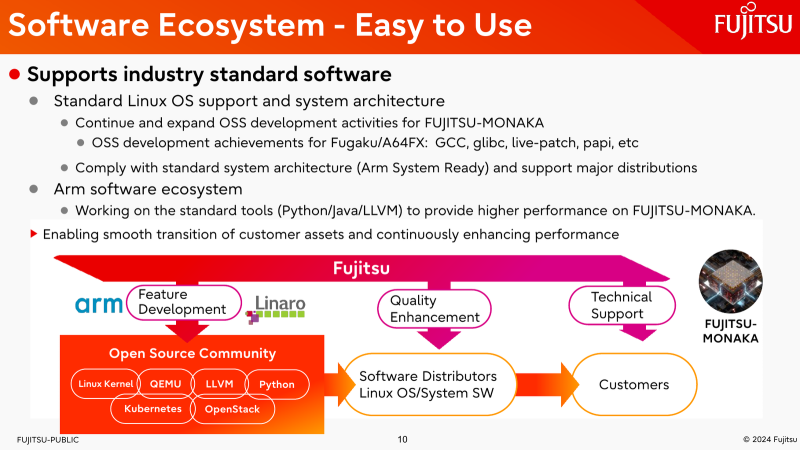

144 ядра, чиплеты, SRAM и 3D-упаковка: Fujitsu поделилась подробностями о грядущих Arm-процессорах MONAKAОпыт японской компании Fujitsu в разработке процессоров и суперкомпьютеров велик и многогранен. Долгое время основной архитектурой для решений Fujitsu была SPARC64, но времена меняются: в 2018 году компания анонсировала разработку собственного процессора на базе архитектуры Arm. Сегодня этот чип мы знаем под именем A64FX. В 2020 году японский кластер Fugaku на основе 48-ядерных A64FX с интегрированными HBM-памятью и интерконнектом занял первое место в рейтинге TOP500 с результатом 537,2 Пфлопс. Однако эти процессоры, которые всё ещё достойно трудятся не только в Fugaku, но и в других суперкомпьютерах, трудно назвать действительно универсальным и доступным. Важность архитектурных нововведений и смену IT-ландшафта в Fujitsu прекрасно осознают. Поэтому компания объявила о разработке нового серверного процессора под кодовым именем MONAKA, для которого она намеревается вдвое увеличить показатели производительности и энергоэффективности, а также учесть растущую популярность задач класса ИИ. А совсем недавно Fujitsu впервые более детально рассказала о технических особенностях будущих CPU. Во-первых, разработчики нового процессора хорошо осознают ограничения, накладываемые текущей транзисторной технологии. Похоже, из FinFET и её аналогов выжаты все или почти все соки и для прорывных решений нового поколения данная технология не подходит. В процессорах MONAKA будут использоваться транзисторы с затвором нового типа, так называемые GAA (Gate-all-Around). Похоже, речь идёт о технологии, которую разрабатывает и собирается внедрить в производство уже в следующем году Samsung в рамках 2-нм техпроцесса SF2. Внедрение 2-нм GAA-транзисторов позволит снизить паразитную ёмкость, а значит, добиться больших тактовых частот при меньшем напряжении питания. При этом новая технология будет применена не только в процессорных ядрах, но и в сборках кеш-памяти, также спроектированных с использованием собственного инструментария Fujitsu. Во-вторых, MONAKA изначально проектируется как модульный процессор. В центре разместится IO-кристалл, содержащий контроллеры DDR5 (12 каналов) и PCI Express 6.0/CXL 3.0. Окружать его будут сборки из 5-нм кристаллов кеш-памяти SRAM и расположенных поверх 2-нм кристаллах с процессорными ядрами. По вертикали соединение обеспечит технология TSV, а по горизонтали — кремниевая подложка-интерпозер. Фактически речь идёт о 3D-компоновке. 12-канальная подсистема памяти обеспечит отсутствие узких мест: у A64FX проблем с пропускной способностью благодаря использованию HBM2 не было, но объем самой памяти был ограничен 32 Гбайт. Зато у MONAKA проблем с расширением не будет — как с помощью классических модулей DIMM, так и посредством банков памяти CXL, благо, за основу сразу взята версия PCIe 6.0 с пропускной способностью 256 Гбайт/с в режиме x16. Сколько будет самих линий, пока не уточняется. Новая платформа изначально проектируется двухсокетной, при этом в количестве ядер Fujitsu также не скромничает: процессоры MONAKA получат 144 ядра, а благодаря новому 2-нм техпроцессу они будут не такими уж горячими. Им хватит воздушного охлаждения, говорят создатели. Процессоры получат набор инструкций Armv9-A с векторными расширениями SVE2 и технологией доверенных вычислений Confidential Computing. Скорее всего, без кастомных инструкций не обойдётся и в этот раз. Последнее особенно важно ввиду того, что MONAKA предназначены не только для рынка HPC, но и для использования в облачных средах. Подсистема конфиденциальных вычислений позволяет шифровать содержимое каждой виртуальной машины собственным ключом, так что доступа к внутренностям ВМ не будет даже у владельцев ЦОД. Впрочем, современные HPC-комплексы всё чаще используют именно облачный подход для доступа к ресурсам. Несмотря на популярность GPU и других специализированных ускорителей, Fujitsu считает, что гетерогенная архитектура имеет существенные недостатки — она заметно дороже, особенно с учётом ценовой политики производителей, склонна к неполной утилизации ресурсов, а также не слишком экономична и зачастую требует специфических систем охлаждения. Компания полагает, что гомогенная архитектура MONAKA этих недостатков лишена и в сочетании с ПО Fujitsu может успешно обрабатывать ИИ-нагрузки. В программной части Fujitsu активно полагается на решения с открытым кодом. Процессоры MONAKA будут отвечать стандартам Arm System Ready и получат полноценную поддержку Linux и сопутствующего инструментария, в частности, GCC, glibc, live-patch, papi и т.д. Разработка ведётся в тесном содружестве с Linaro, организацией, занимающейся консолидацией открытого ПО для Arm, а также с альянсом UXL. Для MONAKA компания подготовит, например, оптимизированную библиотеку OpenBLAS. Также Fujitsu уделяет внимание экологии: напомним, одной из главных черт нового процессора будет его экономичность, что отвечает целям японской национальной программы NEDO, ставящей своей целью достижение 40 % снижения энергопотребления ЦОД к 2030 году. Что касается начала поставок MONAKA, здесь всё идёт по плану: первые партии новых процессоров найдут своё место в серверах и вычислительных узлах уже в 2027 году. Это вполне согласуется с циклом разработки PCI Express, согласно которому появления решений PCIe 6.0 на рынке следует ожидать не ранее 2025 года.

28.06.2024 [12:35], Сергей Карасёв

Loongson представила 64-ядерные серверные процессоры с чиплетной компоновкойКитайская компания Loongson, по сообщению Tom's Hardware, начала пробный выпуск процессоров 3C6000, 3D6000 и 3E6000 для серверных систем. В настоящее время эти изделия проходят тестирование, а серийное производство запланировано на IV квартал 2024 года. Чип 3C6000 содержит 16 ядер LA664 (32 потока инструкций) с микроархитектурой LoongArch, разработанной Loongson. Утверждается, что новинка обеспечивает вдвое более высокую производительность по сравнению с процессором 3C5000, функционирующим на частоте 2,2 ГГц. Для 3C6000 реализована поддержка четырёх каналов оперативной памяти DDR4-3200.

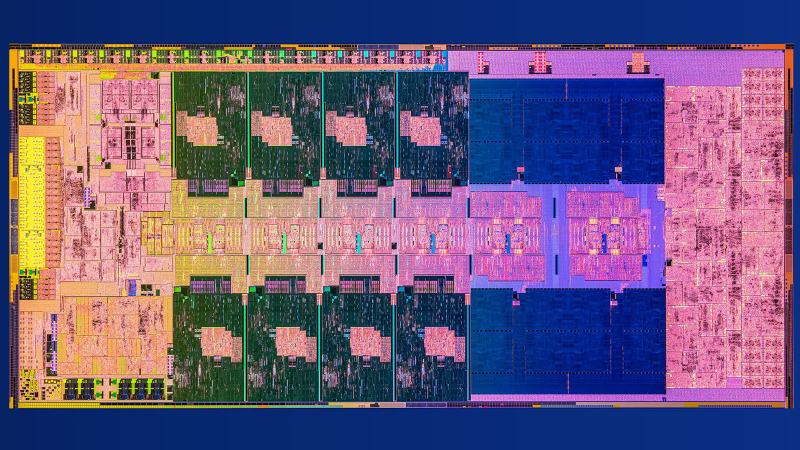

Источник изображения: Loongson Решения 3D6000 и 3E6000, в свою очередь, имеют чиплетную компоновку. Они объединяют соответственно два и четыре кристалла 3C6000, связанных посредством технологии Loongson Coherent Link. В результате, получаются CPU с 32 и 64 вычислительными ядрами с возможностью одновременной обработки 64 и 128 потоков инструкций. Архитектура чиплетов считается будущим микропроцессоров. Причём Китай делает особую ставку на чиплетную компоновку на фоне жёстких санкций со стороны США, которые ограничивают доступ китайских компаний к передовым технологиям производства полупроводниковой продукции. Объединяя несколько кристаллов в составе одного CPU, разработчики из КНР получают возможность наращивать производительность чипов без применения наиболее «тонких» техпроцессов. В Китае в условиях активного импортозамещения наложен запрет на использование процессоров Intel и AMD в компьютерах и серверах для государственного сектора. Благодаря этому спрос на отечественную продукцию растёт, а Loongson увеличивает рыночную долю. |

|