Материалы по тегу: шины

|

07.05.2026 [00:55], Владимир Мироненко

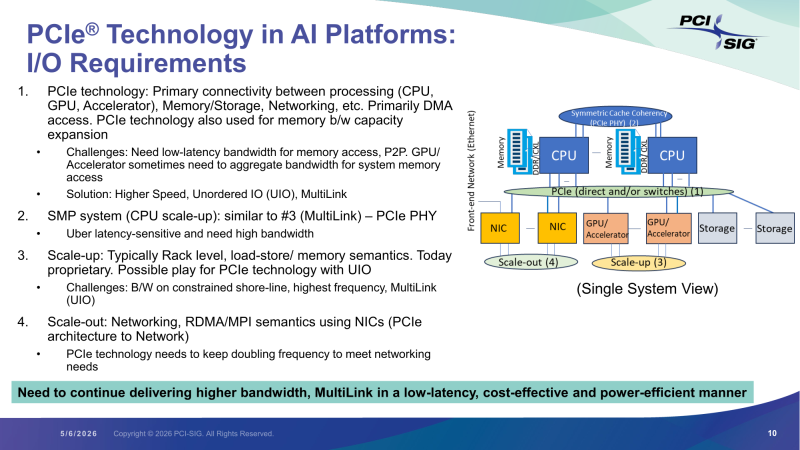

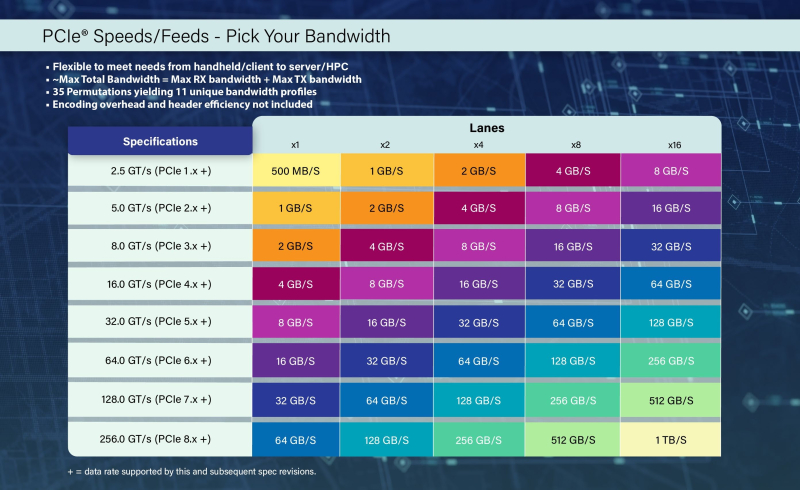

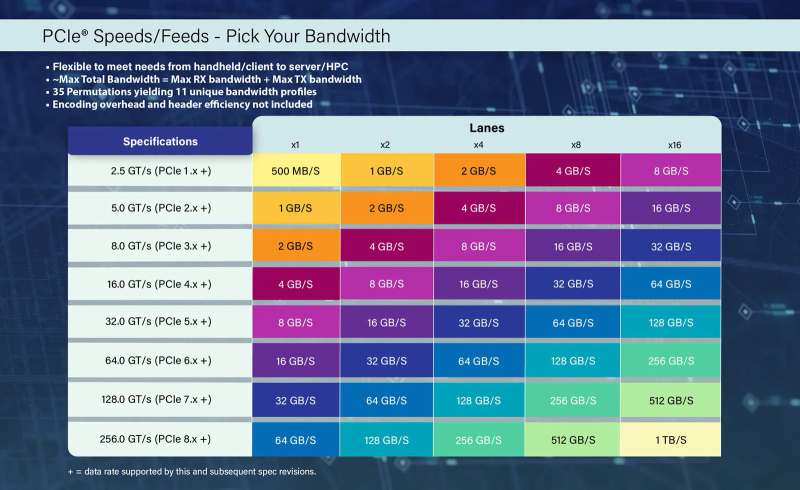

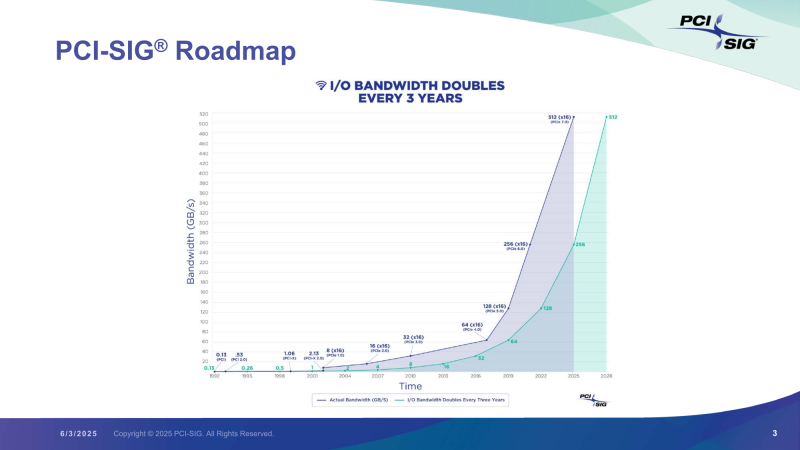

1 Тбайт/с на x16: PCI-SIG раньше срока предоставила спецификации PCI Express 8.0 версии 0.5Некоммерческая организация PCI-SIG объявила о выходе версии 0.5 стандарта PCIe 8.0, которую предоставили отраслевым партнёрам раньше запланированного срока. Это официальный первый вариант спецификации PCIe 8.0, включающий отзывы о прошлогоднем выпуске стандарта 0.3. Как ожидается, стандарт будет полностью готов к 2028 году, что значительно повысит производительность шины PCIe. PCIe 8.0 должен увеличить пропускную способность в два раза по сравнению с PCIe 7.0, который в свою очередь в два раза превосходит по скорости актуальную версию стандарта — PCIe 6.0. Серверные процессоры AMD и Intel получат поддержку PCIe 6.0, и в планы обеих компаний уже включена реализация в будущем стандарта PCIe 7.0. В свою очередь, PCI-SIG стремится выпустить PCIe 8.0 до того, как отрасли потребуется ещё более высокая пропускная способность, что позволит рынку строить дальнейшие планы развития с учётом требований PCIe. Цели спецификации PCIe 8.0:

19.09.2025 [11:45], Сергей Карасёв

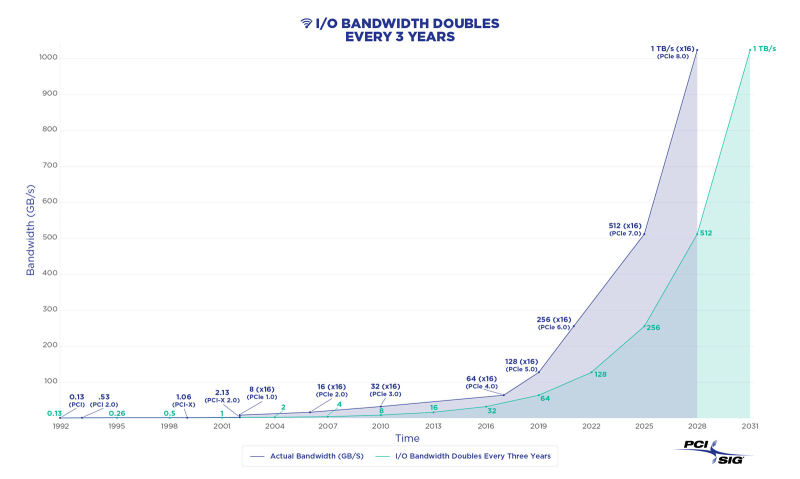

Обнародована предварительная спецификация PCIe 8.0Некоммерческая организация PCI Special Interest Group (PCI-SIG) сообщила о выходе спецификации PCI Express (PCIe) 8.0 версии 0.3. Документ, как отмечается, получил одобрение со стороны участников соответствующей рабочей группы и теперь доступен членам организации. Стандарт PCIe 8.0 предполагает, что «сырая» скорость передачи данных составит до 256 ГТ/с на линию. При этом пропускная способность в двустороннем режиме x16 будет достигать 1 Тбайт/с против 512 Гбайт/с у интерфейса предыдущего поколения. Для PCIe 8.0 предусмотрено обеспечение обратной совместимости с более ранними версиями PCIe. Организация PCI-SIG намерена выпустить полную версию спецификации PCIe 8.0 к 2028 году. Стандарт разрабатывается с прицелом на системы ИИ, высокоскоростные сети, периферийные вычисления, квантовые платформы и другие приложения, которым требуется высокая пропускная способность. Модель членства PCI-SIG подразумевает, что каждая компания-участник может внести свой вклад в процесс разработки спецификаций. В случае PCIe 8.0 внимание в числе прочего уделяется повышению энергетической эффективности и общим улучшениям на уровне протокола. Ещё одним направлением работ названо достижение целевых показателей надёжности. Эл Янес (Al Yanes), президент и председатель PCI-SIG, отмечает, что выход спецификации PCIe 8.0 в 2028 году отражает тенденцию удвоения пропускной способности данного интерфейса каждые три года. По его словам, новый стандарт обеспечит экономичный и скоростной интерконнект с низкими задержками для удовлетворения растущих потребностей отрасли.

09.08.2025 [13:22], Сергей Карасёв

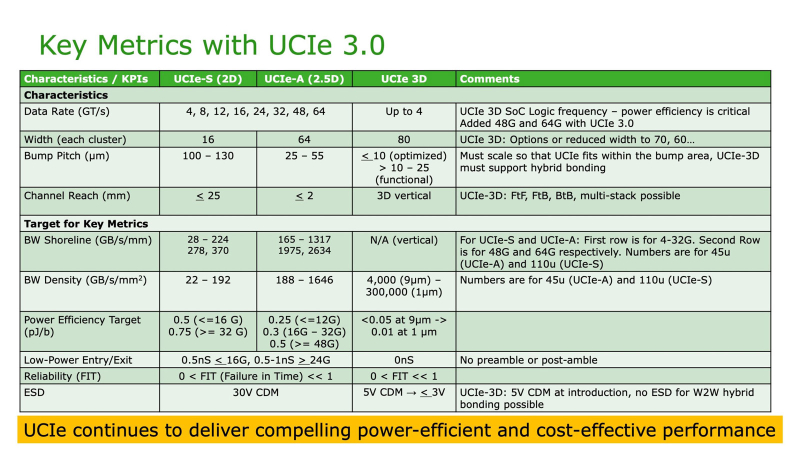

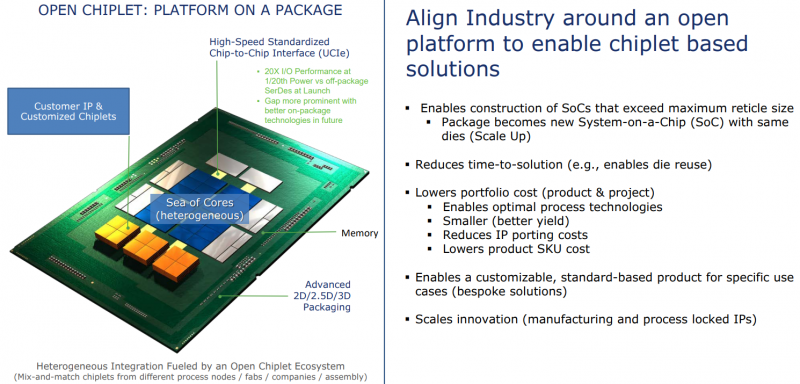

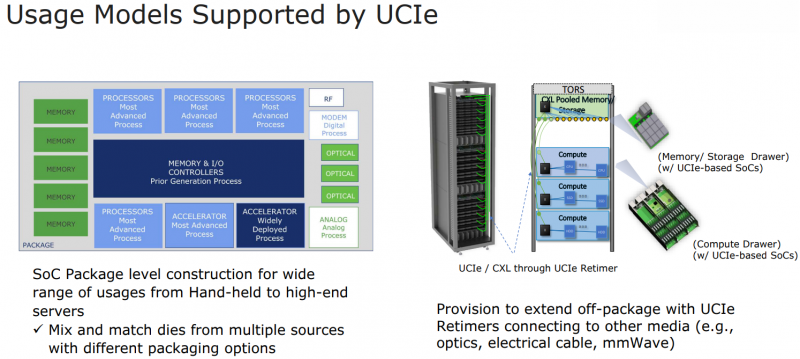

До 64 ГТ/с: обнародована спецификация UCIe 3.0 для объединения чиплетовКонсорциум Universal Chiplet Interconnect Express (UCIe) объявил о выпуске спецификации UCIe 3.0 для соединения чиплетов в составе высокопроизводительных систем, таких как платформы аналитики данных, HPC и ИИ. Напомним, консорциум UCIe был сформирован в 2022 году с целью создания стандартного интерконнекта, позволяющего объединять в одном корпусе чиплеты разных производителей, обладающие различными функциями и изготовленные на разных предприятиях. В состав консорциума вошли Intel, AMD, Qualcomm и TSMC, а также ведущие гиперскейлеры, включая Google Cloud, Meta✴ и Microsoft. Обнародованная спецификация UCIe 3.0 предусматривает удвоение скорости по сравнению со стандартом предыдущего поколения — до 48 и 64 ГТ/с для вариантов UCIe-S (стандартная упаковка 2D) и UCIe-A (передовая упаковка 2.5D). Таким образом, достигается более высокая пропускная способность в расчёте на соединение, что имеет большое значение, когда для обмена данными между кристаллами может быть задействовано строго ограниченное количество соединений. В случае UCIe 3D скорость ограничивается 4 ГТ/с.

Для UCIe 3.0 заявлена обратная совместимость со спецификациями предыдущих поколений. Упомянута улучшенная перекалибровка во время выполнения, обеспечивающая снижение энергопотребления каналов передачи данных и чиплетов. Предусмотрены и другие усовершенствования, ориентированные на повышение плотности полосы пропускания, энергоэффективности и управляемости на системном уровне. В целом, спецификация UCIe 3.0 обеспечивает более высокую масштабируемость, гибкость и совместимость, что, как считают участники консорциума, поможет ускорить инновации в области модульной полупроводниковой архитектуры. Вместе с тем некоммерческая организация Open Compute Project Foundation (OCP) выпустила новую спецификацию Universal D2D Transaction и Link-Layer, которая охватывает в том числе UCIe.

05.08.2025 [18:00], Сергей Карасёв

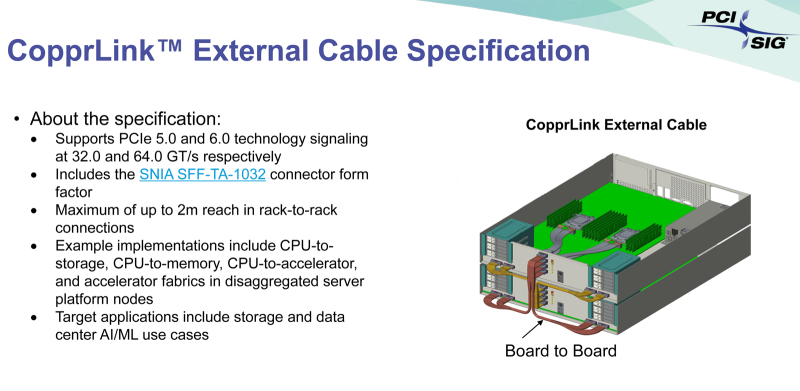

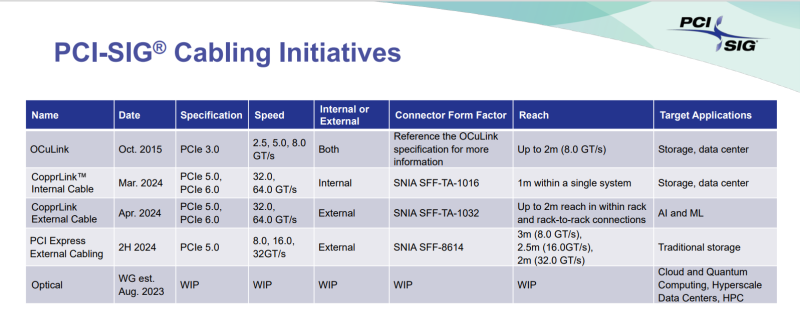

Спецификации PCIe 8.0 будут утверждены к 2028 году: до 1 Тбайт/с в двустороннем режиме x16Организация PCI Special Interest Group (PCI-SIG) объявила о том, что спецификация PCI Express (PCIe) 8.0 будет готова к 2028 году. Интерфейс нового поколения обеспечит удвоение пропускной способности по сравнению с предыдущей версией стандарта, а также привнесёт ряд других изменений. Напомним, финальная спецификация PCIe 7.0 была опубликована в июне нынешнего года. «Сырая» скорость достигает 128 ГТ/с на линию, а пропускная способность в двустороннем режиме в конфигурации x16 составляет 512 Гбайт/с. Реализованы кодирование PAM4, поддержка Flit-режима и обратная совместимость с предыдущими версиями PCIe. В случае PCIe 8.0 «сырая» скорость увеличится до 256 ГТ/с на линию, тогда как пропускная способность в двустороннем режиме x16 поднимется до 1 Тбайт/с. Как и прежде, планируется обеспечение обратной совместимости с более ранними поколениями PCIe. Для повышения скорости передачи данных подвергнется доработкам протокол. Кроме того, будет уделяться внимание дальнейшему улучшению энергетической эффективности, обеспечению целевых показателей надёжности и задержки. Упомянуто кодирование PAM4. Одновременно продолжится работа над совершенствованием кабелей CopprLink для PCIe. Весной 2024 года PCI-SIG обнародовала спецификации электрических кабелей и разъёмов CopprLink для внешних и внутренних подключений PCIe 5.0 и PCIe 6.0: скорость достигает 32 и 64 ГТ/с соответственно. Максимальная длина соединения в пределах одной системы составляет 1 м, между стойками — 2 м. Но, как отмечается, для высокопроизводительных систем требуются соединения большей протяжённости. В целом, спецификация PCIe 8.0 нацелена на создание высокоскоростного интерфейса для таких сфер применения, как ИИ и машинное обучение, периферийные и квантовые вычисления, а также приложения с интенсивным использованием данных, включая дата-центры гиперскейлеров, НРС-задачи, автомобильные и аэрокосмические платформы и пр.

11.06.2025 [23:59], Игорь Осколков

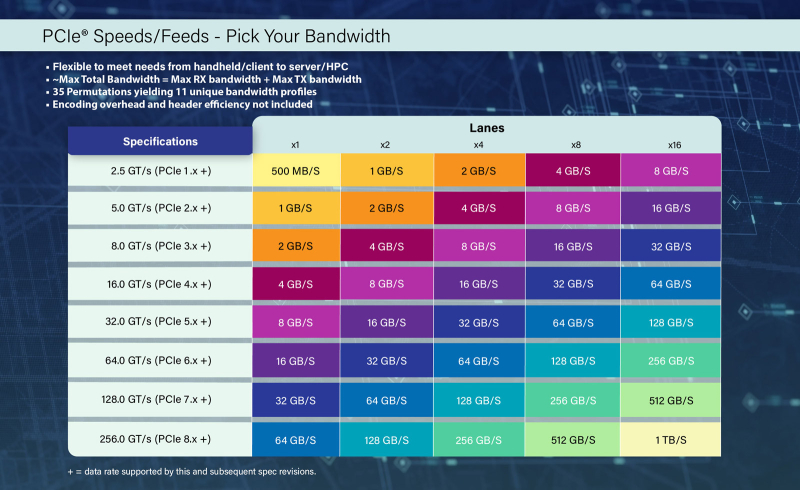

Представлена финальная спецификация PCI Express 7.0Консорциум PCI-SIG официально объявил о релизе спецификаций PCI Express 7.0 версии 1.0. Базовые характеристики интерфейса изменений не претерпели: «сырая» скорость 128 ГТ/с на линию, которая конвертируется в 512 Гбайт/с в двустороннем режиме в конфигурации x16; кодирование PAM4; поддержка Flit-режима; универсальность и обратная совместимость с предыдущими версиями PCIe; повышенная энергоэффективность; расширенная коррекция ошибок и т.д. Новый стандарт ориентирован на решения с интенсивным обменом данными, которым требуются низкая задержка, высокая скорость и повышенная надёжность: ИИ-платформы, 800G-сети, облака гиперскейлеров, квантовые системы и т.п. Впрочем, как и стандарты прошлого поколения, PCIe 7.0 сохранит гибкость, предоставляя 11 различных профилей, которые охватывают весь спектр возможных применений интерфейса, от мобильных платформ до HPC-систем. Консорциум придерживается выбранного темпа выпуска спецификаций — каждые три года появляется новый стандарт, который, по мнению PCI-SIG, всегда чуть опережает текущие потребности индустрии. Здесь есть два важных момента. Во-первых, PCI-SIG не пытается добиться максимально возможной скорости (за NVLink уже не угнаться), а старается дать максимум скорости по приемлемой цене. Во-вторых, уже сейчас разработчики IP говорят о возможных проблемах насыщения данными даже одной линии PCIe 7.0 в некоторых приложениях и сложностях физической и логической реализации нового интерфейса. Впрочем, до появления первых реальных продуктов с поддержкой PCIe 7.0 ещё долго. На 2027 год запланирован старт предварительного «тестирования на соответствие» (FYI, First Year Inventory Compliance Program), так что внедрение нового стандарта начнётся не раньше 2028 года. Внедрение PCIe 6.0, представленного ещё в январе 2022 года, тоже только-только начинается и займёт ещё год-два. Анонсированная почти два года назад оптическая версия PCIe продолжает разрабатываться. В PCIe 7.0 и PCIe 6.4 впервые были добавлены спецификации ретаймеров, которые позволят передавать сигнал PCIe по оптоволокну. Это позволит сделать интерконнект на базе PCIe значительно компактнее, чем при использовании традиционных медных соединений, а также позволит эффективно вывести PCIe за пределы узла. Впрочем, пока что речь идёт скорее о масштабах стойки или нескольких, а не целого ЦОД.

18.06.2024 [22:45], Алексей Степин

Обещанного три года ждут: разработка и внедрение новых стандартов PCI Express не ускорятся, но PCI-SIG не видит в этом проблемыНа недавно прошедшей конференции PCI-SIG Developers Conference 2024 вице-президент группы, Ричард Соломон (Richard Solomon) рассказал о разработке новых версий стандарта PCI Express. Создание новых стандартов вышло на устоявшийся трехлётний цикл, но в данном случае имплементация и выход на массовый рынок не равны собственно разработке очередной версии PCIe. Приблизительно за три года PCI-SIG успевает разработать, внести корректировки, согласовать все нюансы со всеми участниками консорциума и опубликовать спецификации нового стандарта. Но после этого необходимо получить первые образцы «кремния» с его поддержкой и провести все необходимые квалификационные процедуры. Одна только фаза «тестирования на соответствие» (FYI, First Year Inventory Compliance Program) занимает полгода. Главной причиной достаточно длительного цикла, отметил вице-президент PCI-SIG, является время от окончания работы над спецификациями до получения готовых ASIC, без которых невозможно начать полномасштабное тестирование. Таким образом, формально появившийся в начале 2022 года стандарт PCIe 6.0 лишь в июне 2024 года добрался до фазы FYI. При этом первый дизайн (только на бумаге, конечно) IP-блоков для PCIe 6.0 появился ещё даже до финализации стандарта. Более того, спецификации PCIe 6.0 в скором времени снова будут обновлены для поддержки нового стандарта оптических соединений, которые, впрочем, не заменят, а дополнят традиционные медные соединения. Финализация правок ожидается в декабре текущего года. Кроме того, появится поддержка и новых кабелей CopprLink. Так что на выход PCIe 6.0 на рынок стоит рассчитывать где-то в начале 2025 года. Конечно, хотелось бы привести цикл разработки PCI Express в соответствии с циклами других производителей, включая разработчиков Ethernet, Infiniband и CXL, но состав PCI-SIG, насчитывающий уже почти тысячу компаний-участников, продолжает расти, что, конечно, не способствует быстрому согласованию спецификаций и получению всех нужных образцов технологии. Более того, все устройства любого стандарта PCIe обязаны быть совместимы со старыми версиями, вплоть до 1.0. И весь этот процесс необходимо поддерживать и далее: на середину или конец 2025 года запланирован выпуск финальных спецификаций PCI Express 7.0. Так что FIY-фазы стоит ожидать не ранее 2028 года. При этом проверка устройств нового стандарта на взаимную совместимость, в том числе чисто электрическую, становится всё сложнее с учётом заявленных частот и скоростей и оттого всё более необходимой. Но даже с трёхлетним циклом разработки, говорит PCI-SIG, пока удаётся опережать требования индустрии. Пропускная способность I/O-систем тоже удваивается примерно каждые три года, но к этому моменту у разработчиков PCIe уже готов и протестирован новый стандарт, покрывающий все разумные потребности и массово реализуемый за разумные деньги. И сравнивать PCIe, например, с NVLink с этой точки зрения может быть не совсем корректно, поскольку целью PCI-SIG не является достижение предельно высокой производительности любой ценой. Вместо этого группа обеспечивает развитие разумной, совместимой экосистемы решений с наилучшим соотношением цены и возможностей. Это не означает, что в абсолютных значениях решения на базе новых стандартов будут дешевле, но, как отметил вице-президент, экосистема PCIe позволяет разработчикам выбрать приемлемое для каждого случая сочетание характеристик. В настоящее время спецификация PCIe 7.0 версии 0.5 стала доступна участникам PCI-SIG. Новый стандарт доводит скорость передачи данных до 128 ГТ/с на линию при повышении энергоэффективности. Напомним, начиная с PCIe 6.0 доступен режим кодирования Flit, позволяющий избежать накладных расходов при передаче данных, и сделан переход к модуляции PAM4. Оптический вариант PCIe 7.0 тоже появится, но всё ещё будет опциональным. По словам Соломона, разговоры о вынужденном переходе на «оптику» ведутся более десяти лет, но по факту возможностей «меди» всё ещё хватает и будет хватать.

01.05.2024 [17:00], Сергей Карасёв

Внутри и снаружи: PCI-SIG обнародовала спецификации кабелей CopprLink для PCIe 5.0/6.0Организация PCI Special Interest Group (PCI-SIG) обнародовала спецификации электрических кабелей и разъёмов CopprLink для внешних и внутренних подключений PCIe 5.0/6.0. Новые соединения на основе меди позволят заменить существующие кабели OCuLink в тех случаях, когда требуется более высокая пропускная способность. Стандарт CopprLink был анонсирован в конце 2023 года. Кабели данного типа обеспечат высокоскоростные подключения в пределах отдельных систем, а также между различными узлами в составе стойки. Кроме того, как отмечалось ранее, разрабатываются варианты для межстоечного соединения. Спецификация CopprLink для внутренних подключений:

Спецификация CopprLink для внешних подключений:

Отмечается, что в дальнейшем кабели CopprLink будут развиваться с учётом возможностей интерфейса PCIe следующих поколений. Технология CopprLink, как ожидается, будет востребована в сферах, где необходимы небольшие задержки, включая дата-центры, производительные СХД, сети и пр. В будущем ожидается появление оптических кабелей PCIe.

02.08.2023 [18:00], Сергей Карасёв

Светлое будущее: у PCIe появится версия с оптическими соединениями — создана рабочая группа для разработки технологииКонсорциум PCI-SIG объявил о формировании рабочей группы PCI-SIG Optical Workgroup, которая займётся реализацией интерфейса PCI Express (PCIe) по оптическим соединениям. Это, как ожидается, станет важным этапом развития соответствующей экосистемы. Внедрение оптических соединений для PCIe по сравнению с существующими решениями обеспечит более высокую пропускную способность, пониженное энергопотребление, увеличенную дальность действия и меньшие задержки.

Источник изображения: pixabay.com Новая технология, как ожидается, будет востребована в облачных дата-центрах, системах НРС и на площадках гиперскейлеров. Речь идёт о создании системы, поддерживающей широкий спектр оптических технологий. Консорциум PCI-SIG призывает всех своих участников присоединиться к Optical Workgroup, поделиться опытом и помочь определить конкретные цели рабочей группы и требования к аппаратным компонентам. Новая рабочая группа сосредоточит усилия над тем, чтобы сделать архитектуру PCIe более подходящей для оптических сетей. Между тем, как отмечается, продолжаются работы над спецификацией PCIe 7.0, которая предусматривает увеличение производительности до 128 ГТ/с по одной линии.

16.05.2022 [23:41], Алексей Степин

Intel: UCIe объединит разнородные чиплеты внутри одной упаковки и за её пределамиШина PCI Express давно стала стандартом де-факто: она не требует много контактов, её производительность в пересчёте на линию уже достигла ≈4 Гбайт/с (32 ГТ/с) в версии PCIe 5.0, а использование стека CXL сделает PCI Express поистине универсальной. Но для соединения чиплетов или межпроцессорной коммуникации эта шина в текущем её виде подходит не лучшим образом. Но использование проприетарных технологий существенно ограничивает потенциал чиплетных решений, и для преодоления этого ограничения в марте этого года 10-ю крупными компаниями-разработчиками, включая AMD, Qualcomm, TSMC, Arm и Samsung, был основан новый стандарт Universal Chiplet Interconnect Express (UCIe). Уже первая реализация UCIe должна превзойти PCI Express во многих аспектах: если линия PCIe 5.0 представляет собой четыре физических контакта с пропускной способностью 32 ГТ/с, то UCIe позволит передавать по единственному контакту до 12 Гбит/с, а затем планка будет повышена до 16 Гбит/с. При этом энергопотребление у UCIe ниже, а эффективность — выше. На равном с PCIe расстоянии новый стандарт может быть вчетверо производительнее при том же количестве проводников. В перспективе эта цифра может быть увеличена до 10–20 раз, то есть, узким местом между чиплетами UCIe явно не станет. Более того, новый интерконнект не только изначально совместим с CXL, но и гораздо лучше приспособлен к задачам дезагрегации. Иными словами, быстрая связь напрямую между чиплетами возможна не только в одной упаковке или внутри узла, но и за его пределами. Весьма заинтересована в новом стандарте Intel, которая планирует использовать UCIe таким образом, что в процессорах нового поколения ядра x86 смогут соседствовать с Arm или RISC-V. При этом планируется обеспечить совместимость UCIe с технологиями упаковки Intel EMIB и TSMC CoWoS, заодно добавив поддержку других шин, в том числе Arm AMBA, а также возможность легкой конвертации в проприетарные протоколы других разработчиков. В настоящее время Intel уже есть несколько примеров использования UCIe. Так, в одном из вариантов с помощью новой шины к процессорным ядрам подключаются ускорители и блок управления, а упаковка EMIB используется для подключения чипа к дезагрегированной памяти DDR5 и линиям PCI Express.

03.04.2020 [13:37], Геннадий Детинич

Консорциумы CXL и Gen-Z объединяют усилия: протоколы станут совместимыми, а возможности расширятсяКонсорциумы CXL и Gen-Z сообщили, что их руководящие органы подписали договор о взаимопонимании. Пописанный меморандум раскрывает планы сотрудничества между двумя организациями, обещая совместимые протоколы и расширенные возможности каждого из представленных интерфейсов. Первые версии спецификаций Gen-Z и CXL (Compute Express Link) вышли, соответственно, в феврале 2018 года и в марте 2019 года. Каждый из этих интерфейсов призван обойти ограничения по пропускной способности, накладываемые на многоядерные и многоузловые конфигурации процессоров и ускорителей.  Как один, так и другой интерфейс отвечают за согласованность кешей множества подключённых решений и обеспечивают минимальные задержки при доступе к вычислительным ресурсам и хранилищам данных на основе ОЗУ или долговременных накопителей. В то же время интерфейс CXL специализируется на согласованной работе внутри шасси, а интерфейс Gen-Z позволяет согласовывать работу на уровне блоков, стоек и массивов. В целом, участники консорциума Gen-Z поддержали идею Compute Express Link и признали её как дополняющую для развития интерфейса Gen-Z. В течение прошлого года в консорциум CXL, за организацией которого стоит компания Intel, вошли много компаний, включая AMD и ARM. Дело оставалось за малым ― объединить усилия и добиться совместимости протоколов и архитектур.  Сегодня такой день настал. Консорциумы CXL и Gen-Z договорились организовать совместные смешанные рабочие группы для разработки «мостов» между протоколами обеих спецификаций и сделать всё необходимое, чтобы расширить возможности каждого из стандартов за счёт возможностей другого. |

|