Материалы по тегу: dimm

|

15.10.2024 [19:43], Николай Хижняк

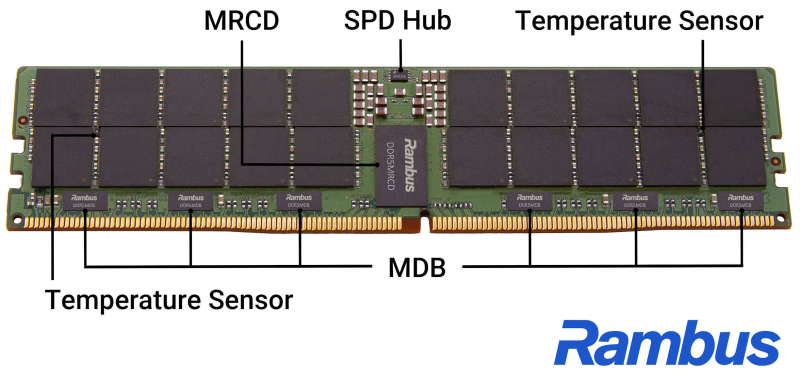

Rambus представила полный набор компонентов для выпуска DDR5-памяти MRDIMM-12800 и RDIMM-8000Компания Rambus объявила о выпуске наборов электронных SMD-компонентов, необходимых для производства модулей ОЗУ RDIMM и MRDIMM нового поколения для серверов. Наборы включают тактовые генераторы, драйверы для управления питанием и некоторые другие компоненты. В представленный Rambus набор вошли следующие базовый компоненты:

Компания поясняет, что DDR5 MRDIMM-12800 использует новую конструкцию модуля, которая повышает скорость передачи данных и производительность системы за счёт мультиплексирования двух рангов, эффективно чередуя два потока данных. Это позволяет шине памяти хоста удвоить скорость передачи данных в сравнении с традиционными модулями при использовании тех же физических соединений DDR5 RDIMM. Для этого требуется чип MRCD, который может адресовать два ранга DRAM в чередующихся тактовых циклах, а также чипы MDB для управления потоками данных к микросхемам DRAM и от них. Для каждого модуля DDR5 MRDIMM-12800 требуется один MRCD и десять чипов MDB. MRCD и MDB также будут поддерживать формфактор Tall MRDIMM с четырьмя рангами.

18.07.2024 [00:05], Владимир Мироненко

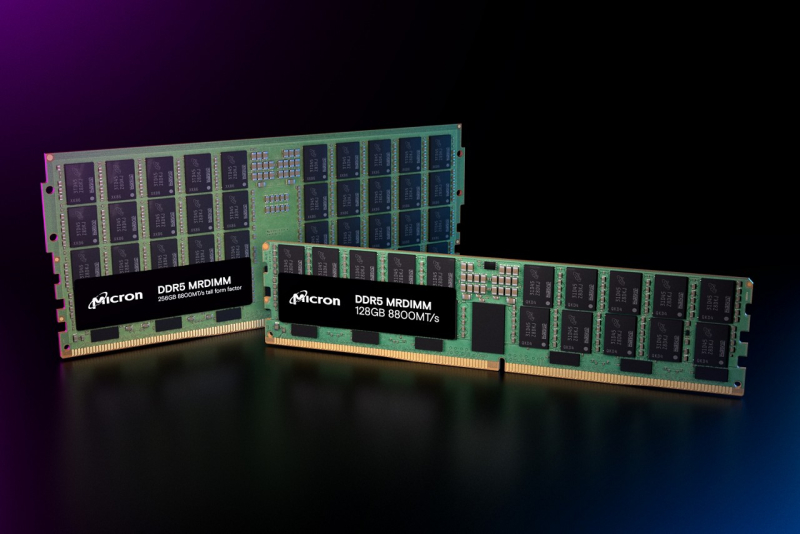

Micron начала рассылку образцов модулей памяти DDR5-8800 MRDIMMКомпания Micron Technology объявила о старте рассылки образцов модулей памяти DDR5 MRDIMM (Multiplexed Rank Dual Inline Memory Module), специально разработанной для приложений ИИ и HPC. По сравнению с обычными RDIMM у модулей MRDIMM до 39 % выше пропускная способность памяти, на 15 % выше эффективность работы шины и до 40 % ниже задержка. MRDIMM-модули будут иметь ёмкость 32, 64, 96, 128 и 256 Гбайт. Модули памяти обеспечивают скорость передачи данных 8800 МТ/с и выпускаются в двух форматах: стандартной и увеличенной (TFF, Tall Form Factor) высоты, которые подходят для серверов высотой 1U и 2U. Благодаря улучшенной конструкции модулей TFF температура DRAM снижается до 20 °С при той же мощности и потоке воздуха, обеспечивая более эффективное охлаждение в ЦОД и оптимизируя общее энергопотребление системы для рабочих нагрузок с интенсивным использованием памяти. Сообщается, что новое предложение представляет собой первое поколение семейства Micron MRDIMM и будет совместимо только с процессорами Intel Xeon 6, поскольку стандарт JEDEC для памяти MRDIMM официально ещё не выпущен. Массовые поставки Micron MRDIMM начнутся во II половине 2024 года. Компания сообщила, что последующие поколения MRDIMM будут по-прежнему обеспечивать до 45 % лучшую пропускную способность памяти на канал по сравнению с RDIMM аналогичного поколения. Ранее образцы MRDIMM (или MR-DIMM) показала ADATA. А SK hynix совместно с Intel и Renesas ещё в конце 2022 года объявила о создании похожего типа памяти — DDR5 MCR (Multiplexer Combined Ranks) DIMM. Весной этого года Micron также показала образцы DDR5-8800 MCR DIMM.

24.03.2024 [02:06], Сергей Карасёв

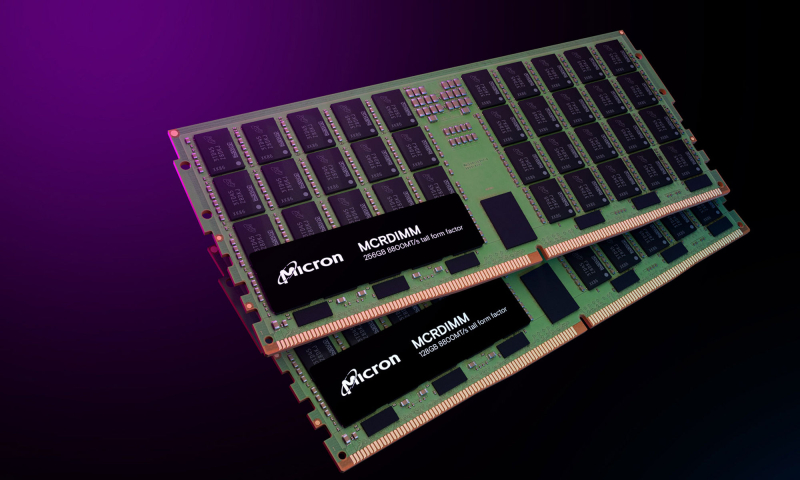

Micron показала модули памяти MCR DIMM DDR5-8800 ёмкостью 256 ГбайтКомпания Micron, по сообщению ресурса Tom's Hardware, продемонстрировала на конференции NVIDIA GTC 2024 модули оперативной памяти MCR DIMM ёмкостью 256 Гбайт для серверов следующего поколения, в том числе для систем, построенных на процессорах Intel Xeon Granite Rapids. Модули имеют увеличенную высоту, но Micron также намерена выпустить варианты стандартной высоты для серверов типоразмера 1U. Изделия соответствуют стандарту DDR5-8800. С каждой стороны модуля расположены по 40 чипов памяти. Заявленное энергопотребление изделия составляет 20 Вт, тогда как у RDIMM объёмом 128 Гбайт при использовании профиля DDR5-4800 оно равно 10 Вт. Новые изделия Micron позволяют оснащать серверы 3 Тбайт памяти при наличии 12 слотов ОЗУ и 6 Тбайт при наличии 24 слотов. MCR DIMM использует специальный буфер между DRAM и CPU, который позволяет двум физическим рангам функционировать так, как если бы они были двумя отдельными модулями памяти, работающими параллельно. Это позволяет извлекать из памяти вдвое больше данных за каждый такт, а также увеличить скорость обмена информацией с CPU. Таким образом, можно одновременно поднять и ёмкость, и производительность памяти. SK hynix также поддерживает MCR DIMM, а вот AMD и JEDEC готовят альтернативный стандарт MRDIMM, который тоже поддерживает создание высокоёмких модулей DDR5-8800. Впрочем, концептуально оба решения восходят к OMI/DDIMM от IBM и даже FB-DIMM.

03.06.2023 [14:10], Алексей Степин

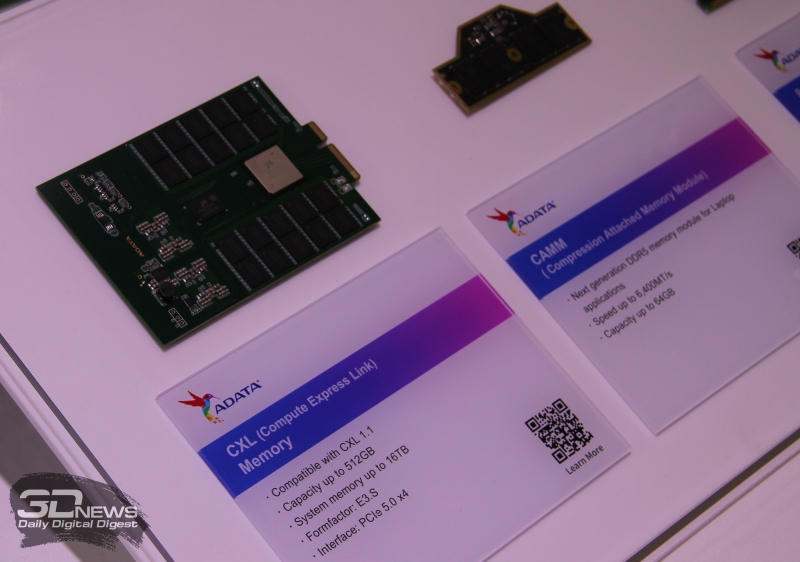

ADATA продемонстрировала память следующего поколения: CAMM, CXL и MR-DIMMНа ежегодной выставке Computex 2023 компания ADATA продемонстрировала свои первые модули памяти нового поколения, которые будут использоваться в современных вычислительных системах: CAMM, CXL и MR-DIMM. Для серверных систем компания продемонстрировала решение на базе стандарта CXL 1.1 с интерфейсом PCI Express 5.0 x4, выполненное в форм-факторе E3.S. Модуль несёт на борту контроллер Montage Technology и предназначен для расширения основного объёма оперативной памяти, подобно решениям DCPMM. При этом у Samsung, например, уже есть DRAM с поддержкой CXL 2.0. Интересно выглядит также другое серверное решение — MR-DIMM (multi-ranked buffered DIMM). Это новое поколение буферизированной памяти, поддержка которой появится в следующих поколениях процессоров AMD и Intel. По сути, такой модуль объединяет два RDIMM в одном, что позволяет поднять ёмкость и производительность «малой кровью». Скорость этих последних новинок стартует с отметки 8400 Мт/с, максимальное значение пока составляет 17600 Мт/с. Модули MR-DIMM Adata будут поставляться в объёмах 16, 32, 64, 128 и 192 Гбайт. Одним из инициаторов создания стандарта MR-DIMM (или MRDIMM) стала AMD. Intel, Renesas и SK hynix работают над похожим решением — MCR DIMM. Наконец, у компании уже есть готовый дизайн модуля CAMM в форм-факторе, который призван заменить SO-DIMM в компактных, сверхкомпактных и переносных системах. Интересно, что каждый модуль CAMM на базе LPDDR5 изначально будет поддерживать работу в двухканальном режиме. Правда, спецификации CAMM будут завершены только во второй половине этого года, так что некоторые характеристики могут измениться.

04.11.2019 [21:00], Алексей Степин

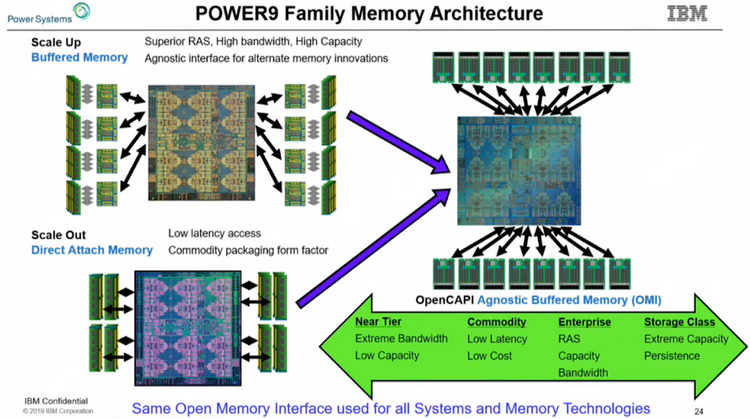

IBM продвигает открытый стандарт оперативной DDIMM-памяти OMI для серверовПрактически у всех современных процессоров контроллер памяти давно и прочно является частью самого ЦП, будь то монолитный кристалл или чиплетная сборка. Но не всегда подобная монолитность является плюсом — к примеру, она усложняет задачу увеличения количества каналов доступа к памяти. Таких каналов уже 8 и существуют проекты процессоров с 10 каналами памяти. Но это усложняет как сами ЦП, так и системные платы, ведь только на подсистему памяти, без учёта интерфейса PCI Express, может уйти 300 и более контактов, которые ещё требуется корректно развести и подключить.

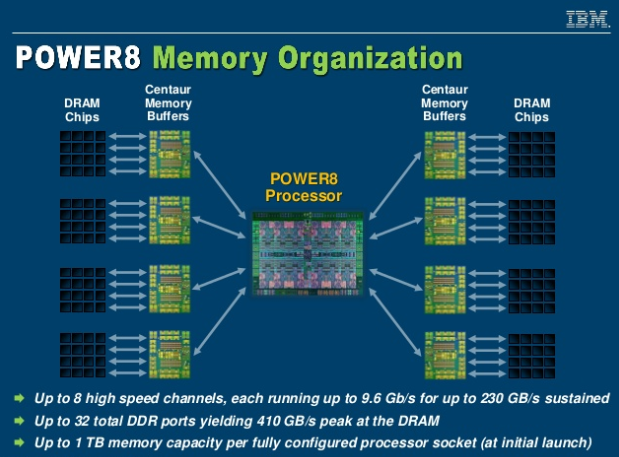

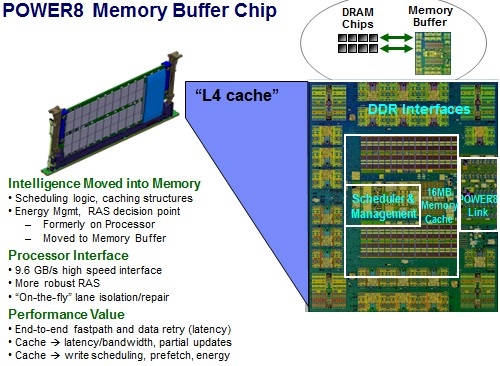

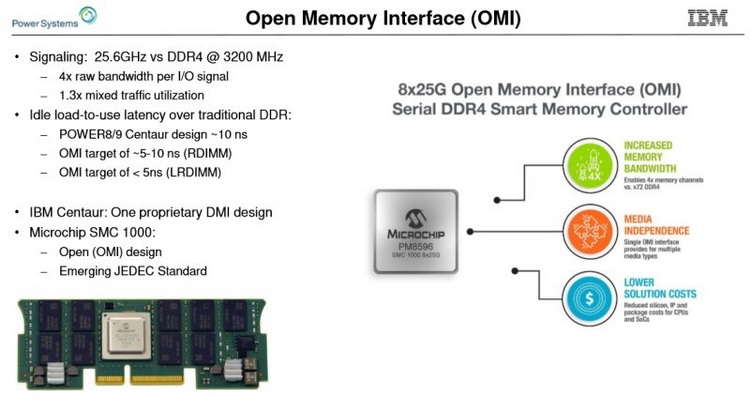

Организация подсистемы памяти у POWER8 У IBM есть ответ, и заключается он в переносе части функций контроллера памяти на сторону модулей DIMM. Сам интерфейс между ЦП и модулями памяти становится последовательным и предельно унифицированным. Похожая схема использовалась в стандарте FB-DIMM, аналогичную компоновку применила и сама IBM в процессорах POWER8 и POWER9 в варианте Scale-Up.

Роль и возможности буфера Centaur у POWER8 Контроллер памяти у этих процессоров упрощён, в нём отсутствует контроллер физического уровня (PHY). Его задачи возложены на чип-буфер Centaur, который посредством одноимённого последовательного интерфейса и связывается с процессором на скорости 28,8 Гбайт/с. Контроллеров интерфейса Centaur в процессорах IBM целых восемь, что дает ПСП в районе 230 Гбайт/с. За счёт выноса ряда функций в чипы-буфера удалось сократить площадь кристалла, и без того немалую (свыше 700 мм2), но за это пришлось заплатить увеличением задержек в среднем на 10 нс. Частично это сглажено за счёт наличия в составе Centaur кеша L4.

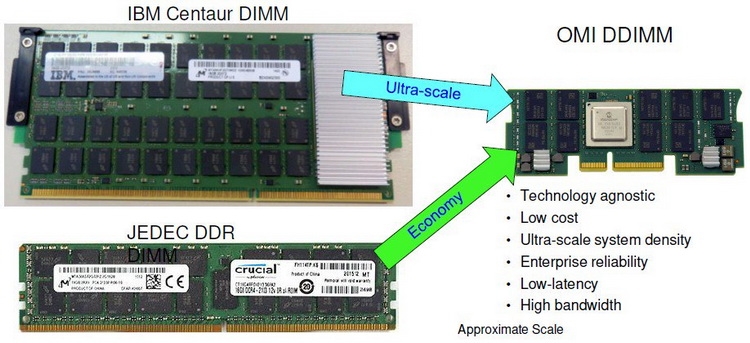

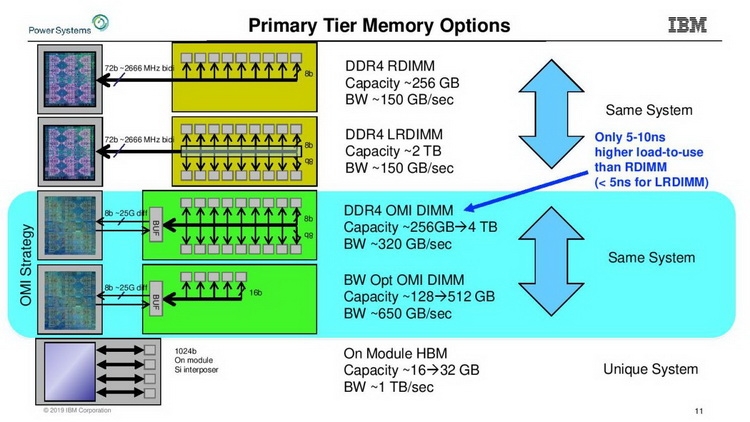

Сравнительные размеры модулей Centaur, RDIMM и OMI DDIMM Стандарт не является открытым, но IBM предлагает ему на смену полностью открытый вариант под названием Open Memory Interface (OMI). В его основу положена семантика и протоколы, описанные в стандарте OpenCAPI 3.1, а физический уровень представлен шиной BlueLink (25 Гбит/с на линию), которая уже используется для реализации NVLink и OpenCAPI. Реализация OMI проще Centaur, что позволяет сделать чип-буфер более компактным и выделяющим меньше тепла. Но все преимущества сохраняются: так, число контактов процессора, отвечающих за интерфейс памяти, можно снизить с примерно 300 до 75, поскольку посылаются только простые команды загрузки и сохранения данных. Вся реализация физического интерфейса осуществляется силами чипа-компаньона OMI, и в нём же может находиться дополнительный кеш.

Модули OMI DDIMM станут стандартом JEDEC Помимо экономии контактов есть и ещё одна выгода: можно реализовать любой тип памяти, будь то DDR, GDDR и даже NVDIMM — вся PHY-часть придётся на различные варианты чипов OMI, но со стороны стандартного разъёма любой модуль OMI будет выглядеть одинаково. Сейчас взят прицел на реализацию модулей с памятью DDR5. При использовании существующих чипов DDR4 система с интерфейсом OMI может достичь совокупной ПСП порядка 650 Гбайт/с. Дополнительные задержки составят 5 ‒ 10 нс для RDIMM и лишь 4 нс для LRDIMM. Из всех соперников технологии на такое способны только сборки HBM, которые в силу своей природы имеют ограниченную ёмкость, дороги в реализации и не могут быть вынесены с общей с ЦП подложки.

Новый стандарт упростит процессоры и позволит увеличить ёмкость подсистемы памяти Чипы-буферы OMI можно разместить как на модуле памяти, так и на системной плате. Разумеется, для стандартизации выбран первый вариант. В нём предусмотрено 84 контакта на модуль, сами же модули получили название Dual-Inline Memory Module (DDIMM). DDIMM вышли существенно компактнее своих традиционных собратьев: ширина модуля сократилась со 133 до 85 мм. Реализация буфера OMI ↔ DDR4 уже существует в кремнии: компания Microsemi продемонстрировала чип SMC 1000 (PM8596), поддерживающего 8 линий OMI со скоростью 25 Гбит/с каждая. Допустима также работа в режиме 4 × 1 с вдвое меньшей общей пропускной способностью.

DDIMM: меньше ширина, проще разъём Со стороны чипов памяти SMC 1000 имеет стандартный 72-битный интерфейс с ECC и поддержкой различных комбинаций DRAM и NAND-устройств. Тактовая частота DRAM — до 3,2 ГГц, высота модуля зависит от количества и типов устанавливаемых чипов. В случае одиночной высоты модули могут иметь ёмкость до 128 Гбайт, двойная высота позволит создать DDIMM объёмом свыше 256 Гбайт. Сам чип SMC 1000 невелик, всего 17 × 17 мм, а невысокое тепловыделение гарантирует отсутствие проблем с перегревом, свойственных FB-DIMM.

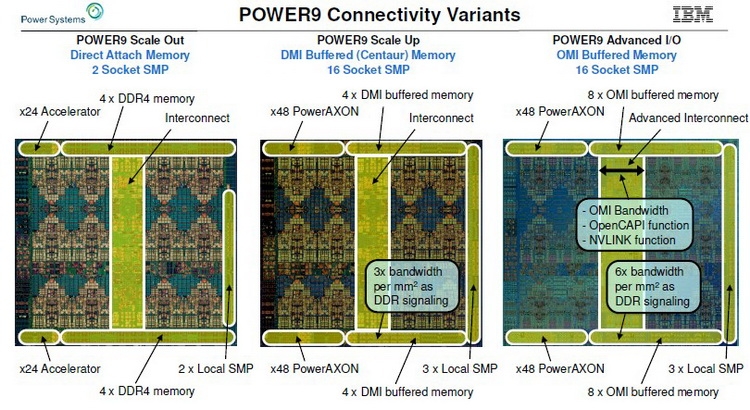

Процессоры IBM POWER9 AIO дополнили существующую серию Первыми процессорами с поддержкой OMI стали новые POWER9 версии Advanced I/O (AIO), дополнившие семейства Scale Up (SC) и Scale Out (SO). В них реализовано 16 каналов OMI по 8 линий каждый (до 650 Гбайт/с суммарно), а также новые версии интерфейсов NVLink (возможно, 3.0) и OpenCAPI 4.0. Количество линий PCI Express 4.0 по-прежнему составляет 48. Шина IBM BlueLink была переименована в PowerAXON. За счёт её использования в системах на базе процессоров POWER возможна реализация 16-сокетных систем без применения дополнительной логики. Максимальное количество ядер у POWER9 AIO равно 24, с учётом SMT4 это даёт 96 исполняемых потоков. Имеется также кеш L3 типа eDRAM объёмом 120 Мбайт. Техпроцесс остался прежним, это 14-нм FinFET.

Архитектура подсистем памяти у семейства IBM POWER9 Поставки POWER9 AIO начнутся в этом году, цены неизвестны, но с учётом 8 миллиардов транзисторов и кристалла площадью 728 мм2 они не могут быть низкими. Однако без OMI эти процессоры были бы ещё более дорогими. В комплект поставки входит и чип-буфер OMI, правда, не самая быстрая версия с пропускной способностью на уровне 410 Гбайт/с. Задел для модернизации есть, и для расширения ПСП достаточно будет заменить модули DDIMM на более быстрые варианты.

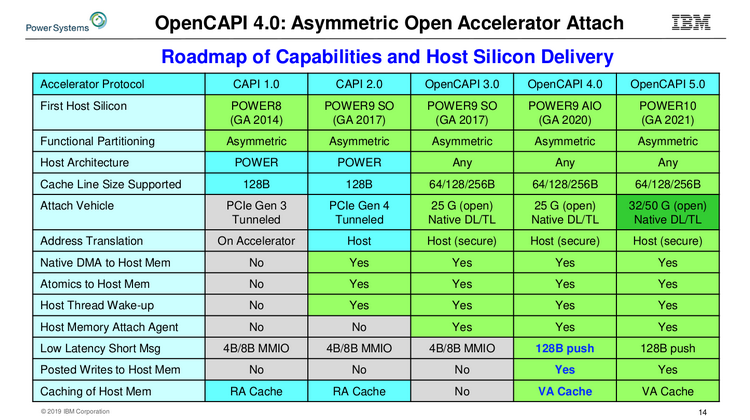

Сравнительная таблица существующих и будущих версий OpenCAPI Следующее поколение процессоров IBM, POWER10, появится только в 2021 году. К этому времени ожидается принятие стандарта OMI на рынке высокопроизводительных многопроцессорных систем. Попутно IBM готовит новые версии OpenCAPI, не привязанные к архитектуре POWER, а значит, путь к OMI будет открыт и другим вендорам. |

|