Intel Foundry опубликовала видео с демонстрацией своих передовых решений в области упаковки микросхем с использованием технологических процессов 18A/14A, технологий Foveros 3D и EMIB-T. В видео представлены концептуальные и масштабируемые конструкции с возможностью размещения до 16 вычислительных блоков, 24 стеков HBM и многое другое.

Как отметил ресурс WCCFTech, видеоролик демонстрирует, что ждёт клиентов Intel, стремящихся использовать её технологии при создании будущих чипов. Эти технологии будут устанавливать стандарты для чипов следующего поколения для HPC, ИИ, ЦОД и многого другого. Передовые решения в области упаковки также усилят позиции Intel в конкуренции с TSMC, которая представили решение CoWoS, обеспечивающее 9,5-кратное превышение размеров стандартного фотошаблона (830 мм²), использующее технологический процесс A16 и более 12 стеков HBM4E (CoWoS-L).

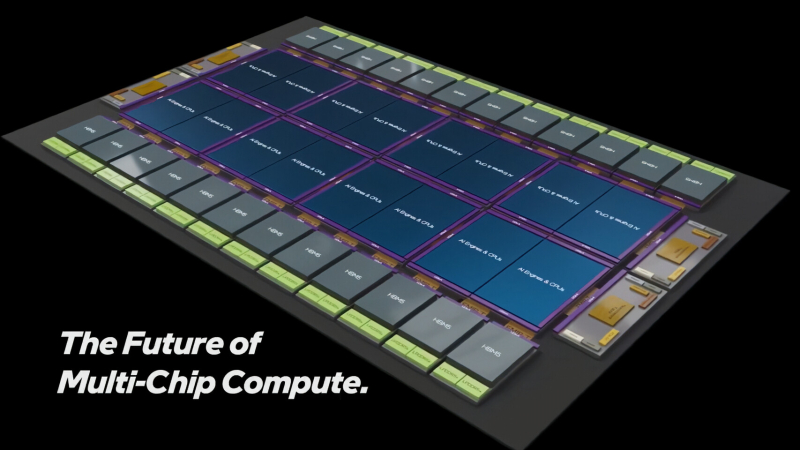

Согласно видео, технологии Intel Foveros 3D и межкристального соединения EMIB-T позволяют объединить до 16 вычислительных кристаллов в паре с 24 стеками HBM5 в одном корпусе. При этом используются 18A-процессы Intel, включая 18A-P и 18A-PT, и 14A-процессы, которые компания готовит к массовому производству, в том числе для внешних заказчиков.

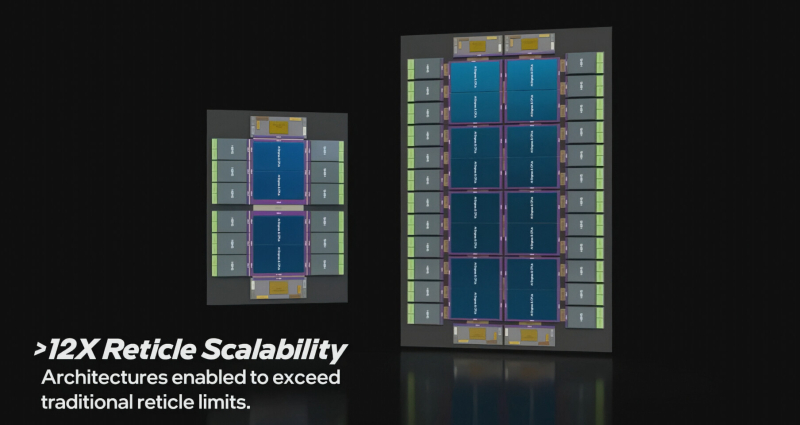

В опубликованном видеоролике Intel демонстрирует два передовых решения для корпусирования микросхем. Одна микросхема включает четыре вычислительных блока и 12 модулей HBM, а вторая — 16 вычислительных блоков и 24 модуля HBM. Также у более крупной размещено в одном корпусе вдвое больше контроллеров LPDDR5X, до 48, что значительно увеличивает плотность памяти для ИИ-нагрузок и ЦОД.

Для создания микросхем используется технология послойного объединения кристаллов, при которой базовые кристаллы, изготовленные с использованием процесса 18A-PT, используют подачу питания с обратной стороны (PowerVia) и включают SRAM-банки. На базовый тайл затем устанавливается основной вычислительный тайл, который может включать в себя ИИ-движки, CPU или другие IP-блоки. Они изготавливаются по технологическим процессам Intel 14A или 14A-E, используют транзисторы RibbonFET второго поколения и технологию PowerDirect, и соединяются с базовым тайлом с помощью технологии Foveros Direct 3D, обеспечивающей вертикальное размещение компонентов, образуя 3D-стек.

Затем несколько чиплетов соединяются и дополнительно взаимодействуют с памятью с помощью технологии упаковки EMIB-T. Верхний тайл использует 24 модуля HBM, которые могут поддерживать как существующие стандарты HBM, такие как HBM3/HBM3E, так и будущие, такие как HBM4/HBM4E или HBM5. При этом активно используется UCIe.

Теперь дело за практической реализацией замыслов. Компания возвращается на рынок с ИИ-ускорителем Jaguar Shores и GPU Crescent Island для ИИ-инференса, но всё зависит от сделок со сторонними поставщиками.

Источник: