Материалы по тегу: soc

|

21.10.2024 [13:21], Сергей Карасёв

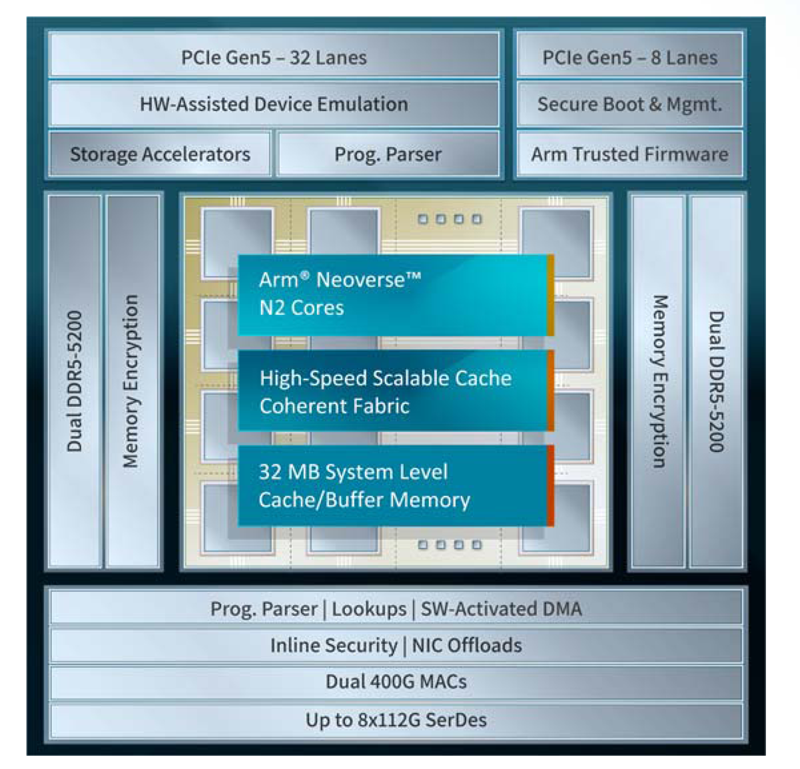

Xsight Labs представила 400GbE DPU серии E1Компания Xsight Labs анонсировала, как утверждается, самую производительную на рынке программно-определяемую «систему на чипе» (SoC), предназначенную для создания DPU с поддержкой RoCEv2 и UET (Ultra Ethernet Transport). Изделие под названием E1 станет доступно заказчикам для тестирования во II квартале 2025 года. Чип будет предлагаться в модификациях E1-32 и E1-64. Первая содержит 32 ядра Arm Neoverse N2 v9.0-A, имеет 16 Мбайт кеша и использует конфигурацию памяти 2 × DDR5-5200. Показатель TDP равен 65 Вт. У второго варианта количество ядер составляет 64, размер конфигурируемого кеша/буфера — 32 Мбайт. Конфигурация памяти — 4 × DDR5-5200, величина TDP — 90 Вт. В обоих случаях используется полное шифрование памяти на лету (AES-XTS). Новинка использует до восьми блоков SerDes, обеспечивая сетевую пропускную способность до 800 Гбит/с. Возможны следующие конфигурации портов: 2 × 400GbE, 4 × 200GbE и 8 × 100/50/25/10GbE. Заявлена производительность на уровне 200 Mpps и 20 млн подключений в секунду. Также есть пара 1GbE-портов для внешнего управления. Доступны программируемые DMA-движки (до 3 Тбит/с) и разгрузка типовых операций, включая шифрование AES-GCM (для IPSec) и AES-XTS (для СХД) на лету.

Источник изображения: Xsight Labs Есть восемь двухрежимных контроллеров и 40 (32+8) линий PCIe 5.0, а также поддержка P2P-коммутации PCIe. Упомянуты поддержка до четырёх хостов/устройств, SR-IOV (64K PF/VF), а также программная эмуляция и пространства MMIO. Реализована поддержка интерфейсов I2C/I3C/SMBus, SPI/QSPI, SMI, UART, GPIO, 1588 RTC, JTAG. Говорится о высоком уровне обеспечения безопасности: возможно создание изолированных и защищённых сред, которые аутентифицируют каждого клиента. Поддерживается функция безопасной загрузки UEFI Secure Boot with Arm Trusted Firmware (TF-A). Заявлена возможность работы «из коробки» в Debian, Ubuntu, SONiC и Lightbits Labs LightOS, а также совместимость с Netdev, VirtIO, XNA/XDP и DPDK/SPDK. В частности, возможна эмуляция NVMe-, RDMA- и сетевых устройств. Изделие E1 производится по 5-нм технологии TSMC. Оно, как утверждает Xsight Labs, обеспечивает беспрецедентную энергоэффективность и вычислительные возможности, устанавливая новый стандарт производительности для DPU SoC. Новинка ориентирована на облачные платформы и периферийные дата-центры, поддерживающие интенсивные ИИ-нагрузки. DPU позволяет создавать SDN/SDS-решения, брандмауэры, NVMe-oF СХД, вычислительные хранилища, CDN-платформы, балансировщики и т.п.

10.10.2024 [21:18], Алексей Степин

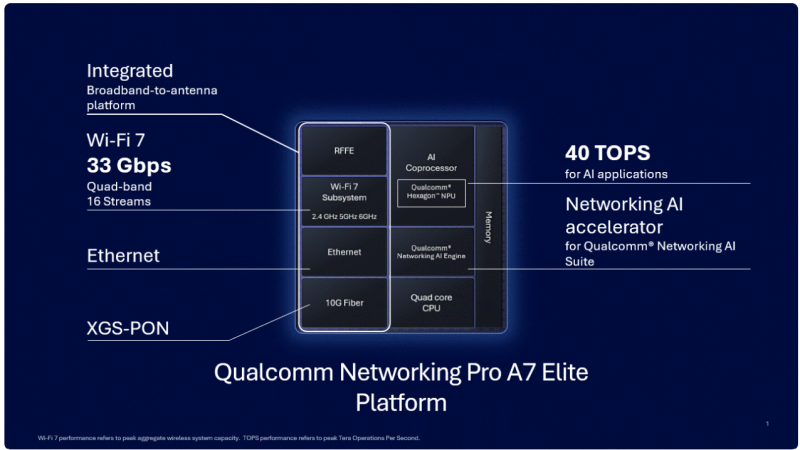

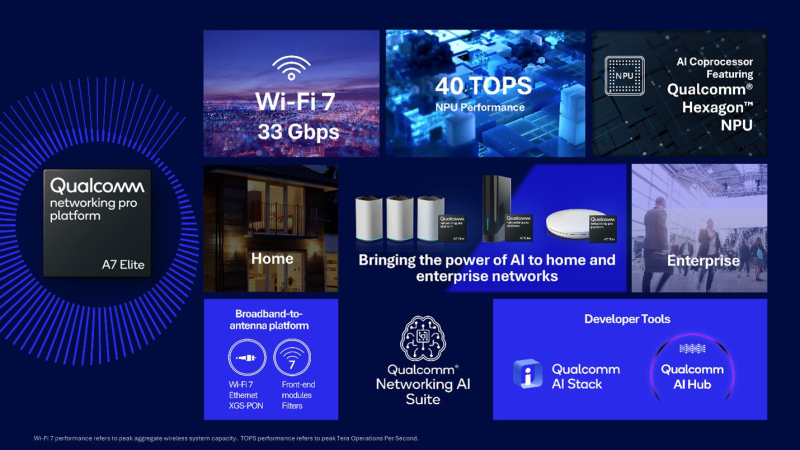

«Элитный» Wi-Fi 7 с ИИ-поддержкой: Qualcomm представила сетевую платформу Pro A7 EliteКомпания Qualcomm объявила о выпуске новой беспроводной сетевой платформы Pro A7 Elite класса «всё-в-одном» с поддержкой беспроводного стандарта Wi-Fi 7 (802.11be) и XGS-PON. Платформа предназначена для размещения на периферии и оснащена широким спектром самых современных сетевых возможностей, дополненных ИИ-функциями. Сердцем новинки является четырёхъядерный процессор, тип и модель которого Qualcomm не разглашает, известно лишь, что в основе лежит 14-нм техпроцесс, а ядра работают на частоте 1,8 ГГц. Процессор работает в паре с памятью DDR3L/DDR4, в качестве накопителя возможно использование флеш-памяти NOR, NAND или eMMC. Зато часть, ответственная за ИИ, хорошо известна — это один из вариантов Qualcomm Hexagon NPU с заявленной производительностью 40 Топс (INT8). Его целью является улучшение работы Wi-Fi, в том числе реализация функций умного классификатора трафика, интеллектуальное управление усилением беспроводного сигнала, детектирование ошибок и др. Платформа может похвастаться развитой сетевой подсистемой: во-первых, в ней реализована поддержка подключений XGS-PON, допускающая работу в качестве шлюза/терминала HGS/ONT или SFU/SFU+ ONU. При этом поддерживается скорость 10 Гбит/с как в восходящем, так и в нисходящем потоках. Проводная Ethernet-часть представлена двумя портами 2.5GbE и одним 10GbE (USXGMII/SGMII+). Wi-Fi-часть Pro A7 Elite предлагает пиковую агрегированную канальную скорость до 33 Гбит/с. Есть поддержка Wi-Fi 7 (802.11be) и Wi-Fi 6/6E (802.11ax), а также совместимость с Wi-Fi 5/4. Радиочасть может обслуживать четыре диапазона одновременно (6/5/2,4 ГГц) и 16 пространственных потоков. Максимальная ширина канала составляет 320 МГц. Для улучшения качества и скорости подключений реализованы технологии Qualcomm Automatic Frequency Coordination (AFC) Service, Simultaneous & Alternating Multi Link и Adaptive Interference Puncturing. Поддерживается WPA3 Personal/Enterprise/Easy Connect. Опционально доступна поддержка 4G/5G FWA, 802.15.4 (Zigbee/Thread) и Bluetooth, реализуемая посредством отдельных модулей. Дополнительно предусмотрено четыре порта PCIe 3.0, порты USB 2.0/3.0, а также интерфейсы I²C, I²S, PTA Coex, SPI и UART. SoC совместима с популярным открытым ПО: OpenWRT, RDK, TiP OpenWiFi, prplOS и OpenSync. Qualcomm уже поставляет образцы Pro A7 Elite.

03.06.2024 [13:54], Сергей Карасёв

Смарт-модуль Quectel SG368Z с поддержкой Wi-Fi 5 и Bluetooth 4.2 выполнен на процессоре Rockchip RK3568Компания Quectel, по сообщению ресурса CNX Software, подготовила к выпуску смарт-модуль SG368Z в LGA-упаковке, предназначенный для устройств для умного дома, IoT-оборудования, систем промышленной автоматизации и пр. В основу изделия положена платформа Rockchip. Новинка выполнена в корпусе с размерами 46,0 × 42,0 × 3,15 мм. Задействован чип RK3568 с четырьмя ядрами Arm Cortex-A55 с тактовой частотой до 2,0 ГГц. Обработкой графики занят ускоритель Arm Mali-G52 с поддержкой OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1. Есть нейропроцессорный блок с производительностью до 0,8 TOPS. Возможна работа с видеоматериалами 4Kp60 H.264, H.265, VP9, 1080p60 MPEG-4/-2/-1, VP8, VC1. Смарт-модуль Quectel SG368Z может нести на борту 2 или 4 Гбайт оперативной памяти, а также 16 или 32 Гбайт флеш-памяти. В оснащение входят контроллеры Wi-Fi 5 и Bluetooth 4.2, два сетевых интерфейса 1GbE. Изделие может функционировать в тандеме с функциональными модулями Quectel, обеспечивающими поддержку 4G Cat 1/4, 5G, Wi-Fi 6 и GNSS. Это позволяет проектировать широкий спектр устройств для различных целей. Среди прочего упомянута поддержка интерфейсов HDMI, eDP, LVDS, MIPI и USB 2.0/3.0 (×4). Решение будет предлагаться в коммерческом и индустриальном вариантах исполнения: в первом случае диапазон рабочих температур простирается от -10 до +75 °C, во втором — от -40 до +85 °C. Говорится о совместимости с Linux, Android и OpenWrt. Новинка является основой платы для разработчиков Quectel SG368Z Smart Module Development Board, оснащённой набором различных разъёмов.

18.10.2022 [19:00], Сергей Карасёв

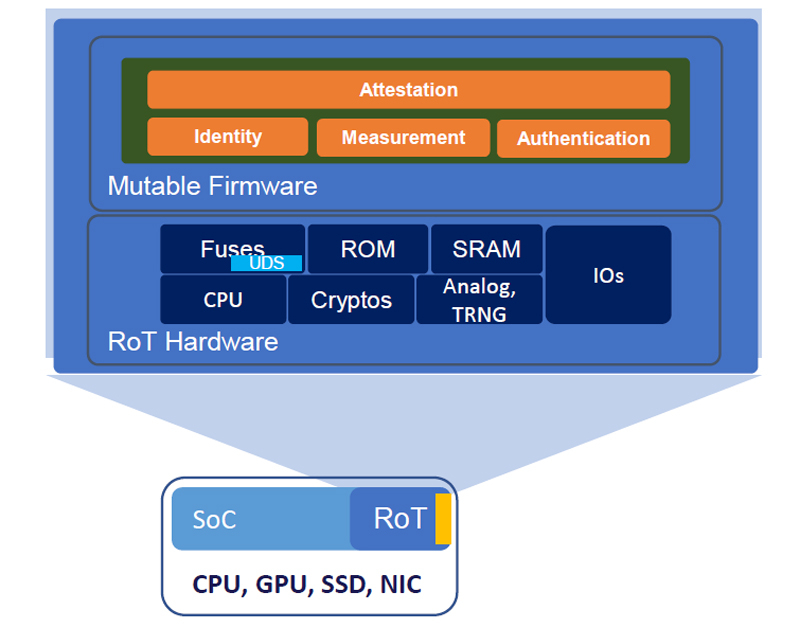

AMD, Google, Microsoft и NVIDIA представили Caliptra — проект по повышению безопасности каждого чипаВ ходе саммита OCP (Open Compute Project) анонсирована открытая спецификация Caliptra 0.5, призванная повысить безопасность процессоров, ускорителей, накопителей и практически любых систем-на-чипе (SoC). Речь идёт об аппаратной реализации технологии Root of Trust (RoT). Она предназначена для проверки целостности и подлинности прошивок и другого встроенного, а также системного программного обеспечения.  RoT гарантирует, что только доверенное ПО может исполняться на чипе. Отмечается, что традиционно средства RoT отделены от SoC и обычно обеспечиваются материнской платой. Однако новые бизнес-модели, предполагающие периферийные и облачные вычисления, предъявляют повышенные требования к обеспечению безопасности. Спецификация Caliptra 0.5 как раз и решает данную проблему.

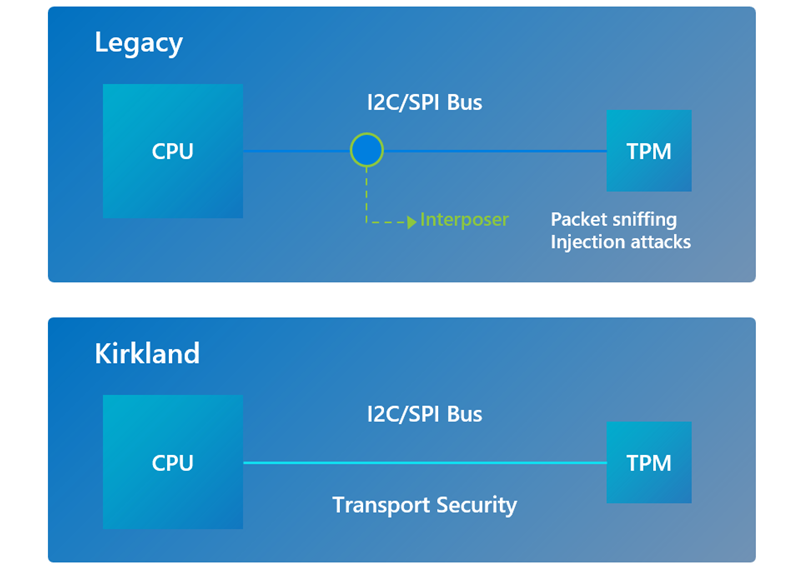

Источник изображений: Caliptra В разработке решения приняли участие AMD, Google, Microsoft и NVIDIA. Спецификация будет поддерживаться различными аппаратными изделиями следующего поколения — CPU, GPU, SSD, NIC и иные ASIC. Отмечается, что Caliptra 0.5 RTL (IP-блоки на базе RISC-V с необходимой обвязкой) распространяется через CHIPS Alliance (Common Hardware for Interfaces, Processors and Systems) — консорциум, который работает над созданием целого спектра открытых решений для SoC и высокоплотных упаковок чипов.  «Существует потребность в улучшенной прозрачности и согласованности низкоуровневой аппаратной безопасности. Мы открываем исходный код Caliptra вместе с нашими партнёрами для удовлетворения этих потребностей», — отмечает Microsoft. Также компания совместно с Google, Infineon и Intel представила Project Kirkland, направленный на создание защищённого канала связи между CPU и TPM с использованием программных средств.

Источник: Microsoft Спецификация Caliptra 0.5 доступна здесь для оценки. На основе отзывов будет выработан окончательный стандарт, отвечающий различным потребностям в зависимости от варианта использования. Кроме того, доступен исходный код, что поможет членам сообщества интегрировать решение в свои микросхемы. Говорится также, что выход спецификации знаменует собой важный шаг вперёд в сторону общеотраслевого сотрудничества в области информационной безопасности. |

|