Финансовые организации, системы бронирования и прочие операторы бизнес-критичных задач любят «большие машины» IBM за надёжность. Недаром литера z в названии систем означает Zero Downtime — нулевое время простоя. На конференции Hot Chips 33 компания представила новое поколение z-процессоров, впервые в истории получившее собственное имя Telum (дротик в переводе с латыни). «Оружейное» название выбрано неспроста: в новой архитектуре IBM внедрила и новые, ранее не использовавшиеся в System z решения, предназначенные, в частности, для борьбы с фродом.

Одни из ключевых заказчиков IBM — крупные финансовые корпорации и банки — давно ждали встроенных ИИ-средств, поскольку их системы должны обрабатывать тысячи и тысячи транзакций в секунду, и делать это максимально надёжно. Одной из целей при разработке Telum было внедрение инференс-вычислений, происходящих в реальном времени прямо в процессе обработки транзакции и без отсылки каких-либо данных за пределы системы.

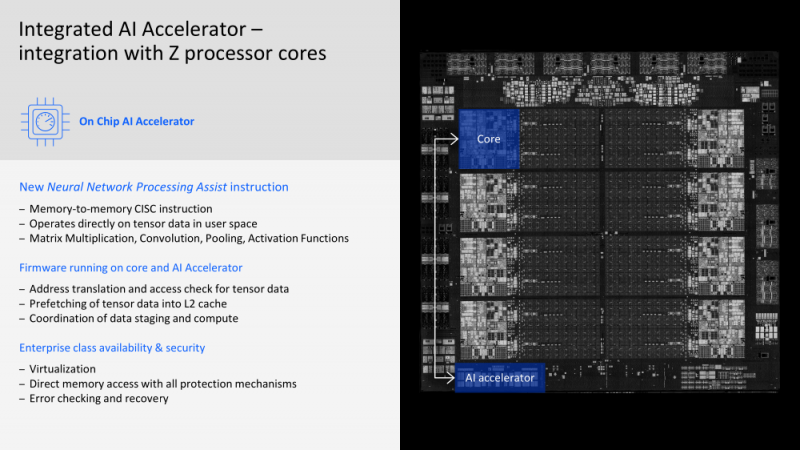

Поэтому инференс-ускоритель в Telum соединён напрямую с подсистемой кешей и использует все механизмы защиты процессора и памяти z/Architecture. И сам он тоже несёт ряд характерных для z подходов. Так, управляет работой акселератора отдельная «прошивка» (firmware), которую можно менять для оптимизации задач конкретного клиента. Она выполняется на одном из ядер и собственно ускорителе, который общается с данным ядром, и отвечает за обращения к памяти и кешу, безопасность и целостность данных и управление собственно вычислениями.

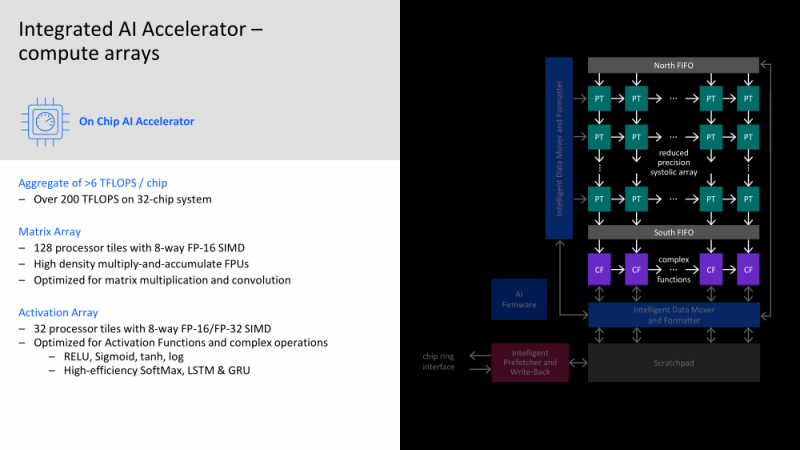

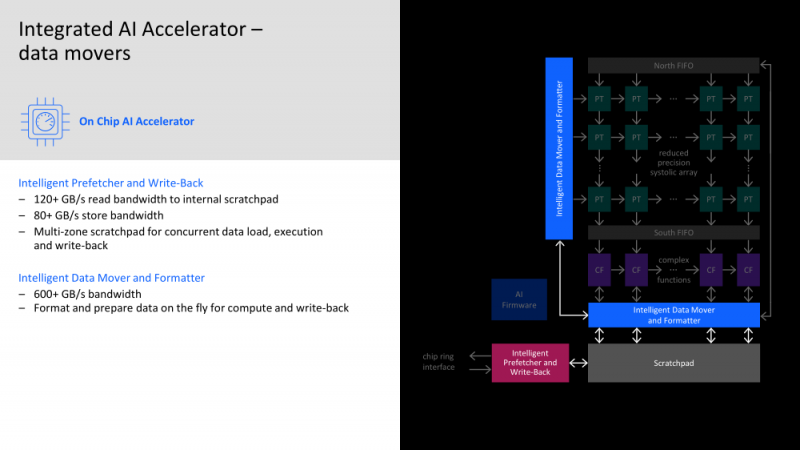

Акселератор включает два вида движков. Первый имеет 128 SIMD-блоков для MAC-операций с FP16-данными и нужен для перемножения и свёртки матриц. У второго всего 32 SIMD-блока, но он может работать с FP16/FP32-данными и оптимизирован для функций активации сети и других, более комплексных задач. Дополняет их блок сверхбыстрой памяти (scratchpad) и «умный» IO-движок, ответственный за перемещение и подготовку данных, который умеет переформатировать их на лету.

Scratchpad подключён к блоку, который подкачивает данные из L2-кеша и отправляет обратно результаты вычислений. IBM отдельно подчёркивает, что наличие выделенного ИИ-ускорителя позволяет параллельно использовать и обычные SIMD-блоки в ядрах, явно намекая на AVX-512 VNNI. Впрочем, в Sapphire Rapids теперь тоже есть отдельный AMX-блок в ядре, который однако скромнее по функциональности.

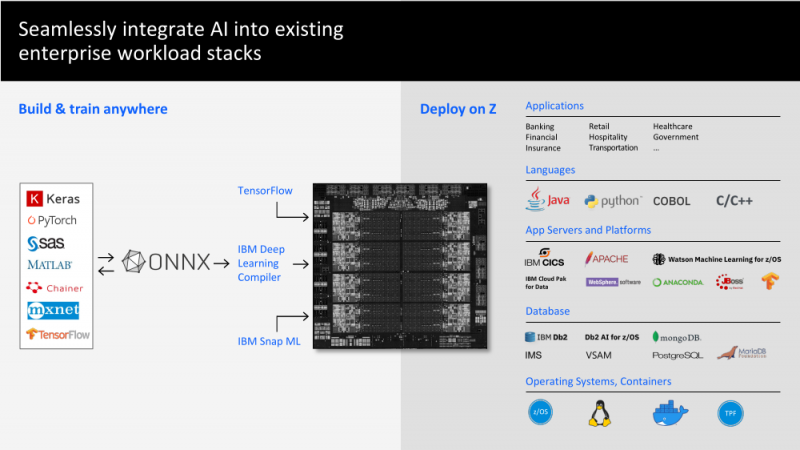

Доступ к ускорителю возможен из пространства пользователя, в том числе в виртуализированном окружении. Для работы с новым ускорителем компания предлагает IBM Deep Learning Compiler, который поможет оптимизировать импортируемые ONNX-модели. Также есть готовая поддержка TensorFlow, IBM Snap ML и целого ряда популярных средств разработки. На процессор приходится один ИИ-ускоритель производительностью более 6 Тфлопс FP16.

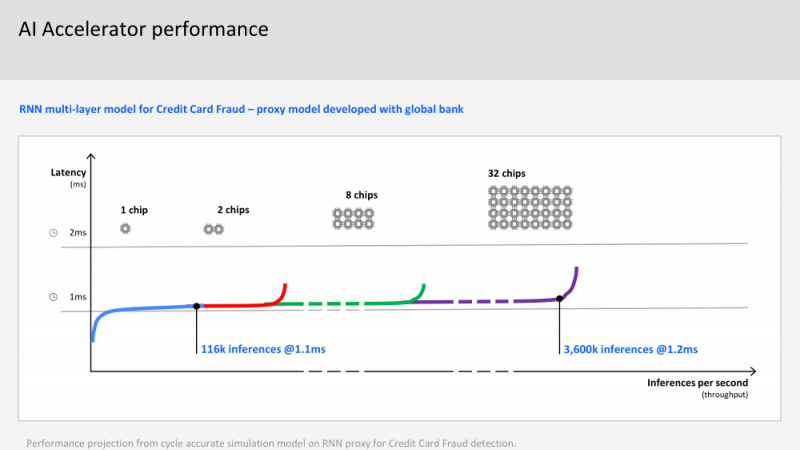

На тестовой RNN-модели для защиты от фрода чип может выполнять 116 тыс. инференс-операций с задержкой в пределах 1,1 мс, а для системы из 32 процессоров этот показатель составляет уже 3,6 млн инференс-операций, а латентность при этом возрастает всего лишь до 1,2 мс. Помимо ИИ-акселератора также имеется общий для всех ядер ускоритель (де-)компрессии (gzip) + у каждого ядра есть ещё и движок для CSMP. Ну и ускорители для сортировки и шифрования тоже никуда не делись.

За надёжность отвечают сотни различных механизмов проверки и перепроверки работоспособности. Так, например, регистры и кеш дублируются, позволяя в случае сбоя ядра сделать его полную перезагрузку и продолжить выполнение задач ровно с того места, где оно прервалось. А для оперативной памяти, которая в обязательном порядке шифруется, используется режим Redundant Array of Memory (RAIM), своего рода RAID-массив, где одна кеш-линия «размазывается» сразу между восемью модулями.

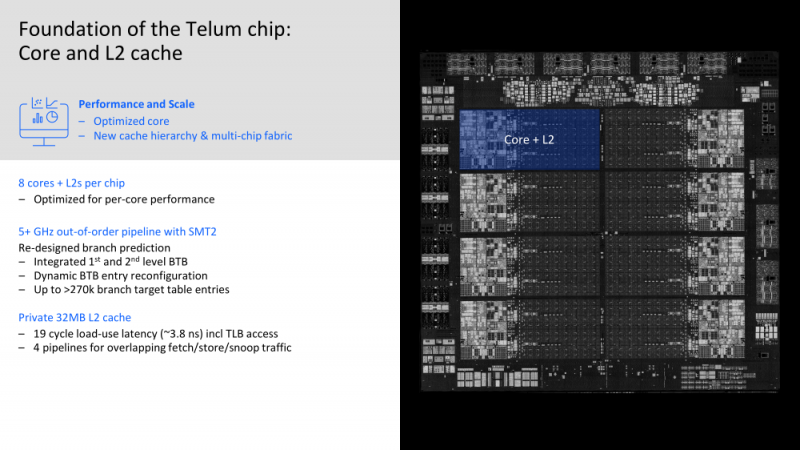

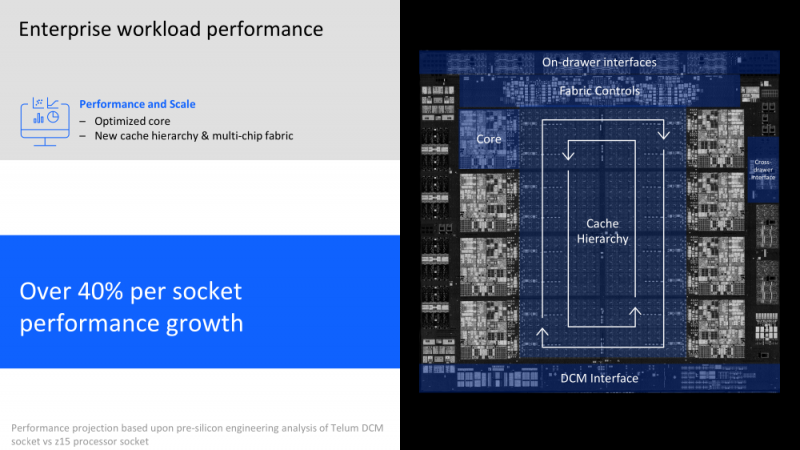

Telum, унаследовав многое от своего предшественника z15, всё же кардинально отличается от него. Процессор содержит восемь ядер с поддержкой «умного» глубокого внеочередного исполнения и SMT2, работающих на частоте более 5 ГГц. Каждому ядру полагается 32 Мбайт L2-кеша, так что на его фоне другие современные CPU выглядят блекло. Но не всё так просто.

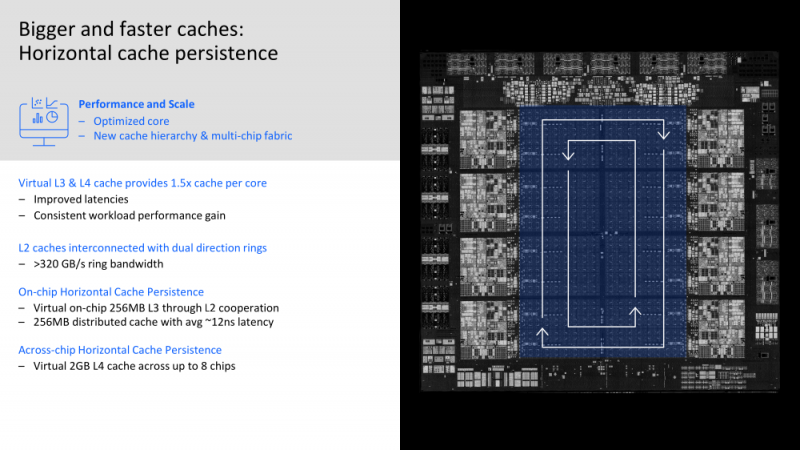

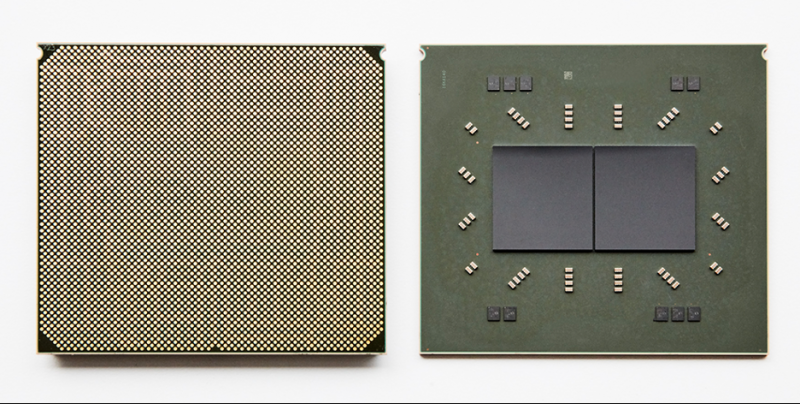

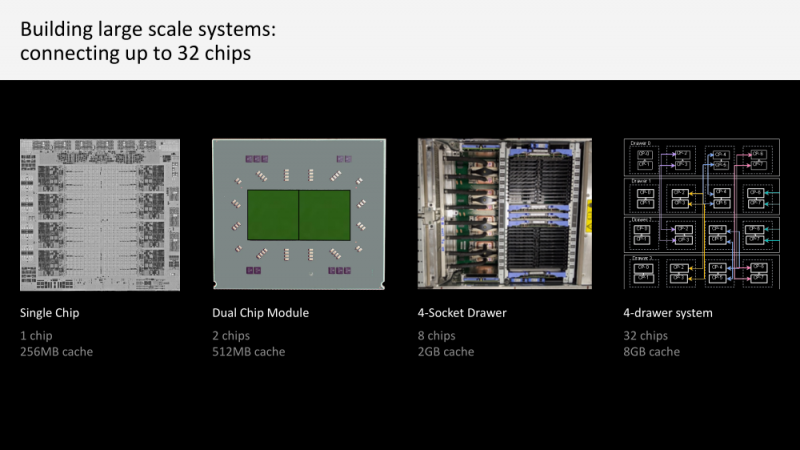

Между собой кеши общаются посредством двунаправленной кольцевой шины с пропускной способностью более 320 Гбайт/с, формируя таким образом виртуальный L3-кеш объёмом 256 Мбайт и со средней задержкой в 12 нс. Каждый чип Telum может содержать один (SCM) или два (DCM) процессора. А в одном узле может быть до четырёх чипов, то есть до восьми CPU, объединённых по схеме каждый-с-каждым с той же скоростью 320 Гбайт/с.

Таким образом, в рамках узла формируется виртуальный L4-кеш объёмом уже 2 Гбайт. Плоская топология кешей, по данным IBM, обеспечивает новым процессорам меньшую латентность в сравнении с z15. Масштабирование возможно до 32 процессоров, но отдельные узлы связаны несколькими подключениями со скоростью «всего» 45 Гбайт/с в каждую сторону.

В целом, IBM говорит о 40% прироста производительности в сравнении с z15 в пересчёте на сокет. Telum содержит 22 млрд транзисторов и имеет TDP на уровне 400 Вт в нормальном режиме работы. Процессор будет производиться на мощностях Samsung с использованием 7-нм техпроцесса EUV. Он станет основной для мейнфреймов IBM z16 и LinuxNOW. Программной платформой всё так же будут как традиционная z/OS, так и Linux.

Источник: