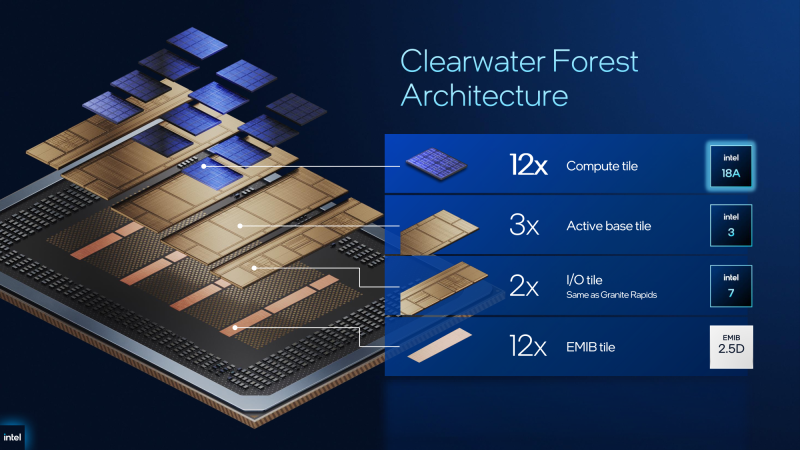

На прошлой неделе Intel представила первые процессоры семейства Xeon 6+, изготовленные по передовому техпроцессу 18A — Clearwater Forest (CWF), выпуск которых был отложен практически на год. Ожидание того стоило, поскольку компания вывела свою тайловую архитектуру и возможности упаковки на новый уровень. Clearwater Forest включает 12 EMIB-чиплетов (2.5D-упаковка), объединяющих 3 базовых тайла (Active Base, Intel 3) с 2 IO-чиплетами I/O (Intel 7) и 12 вычислительными тайламм с E-ядрами Core (Intel 18A с RibbonFET и PowerVia).

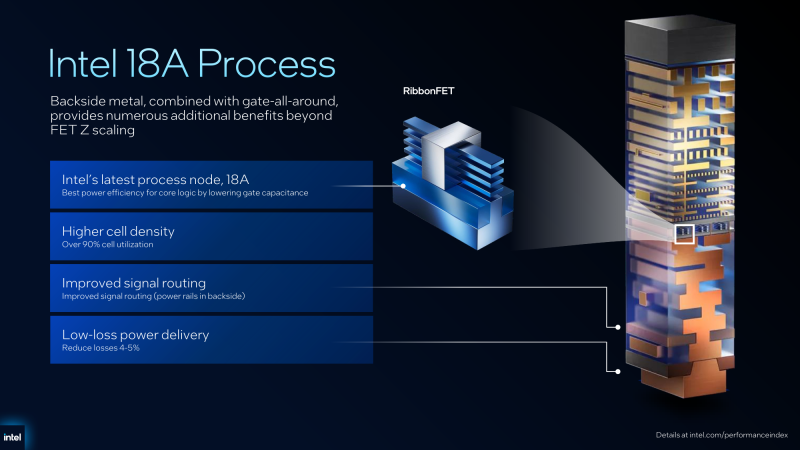

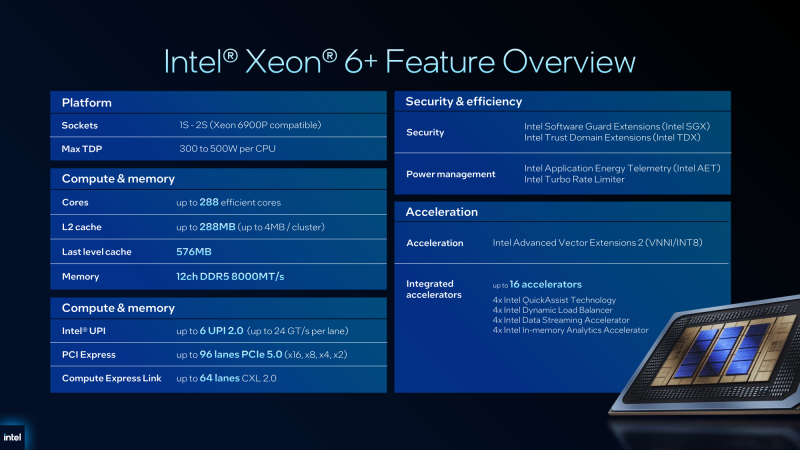

Это один из первых чипов, который производится по техпроцессу 18A, обеспечивающему, по словам компании, наилучшую энергоэффективность для основной логики благодаря меньшей ёмкости затвора, а также более высокую плотность ячеек, улучшенную маршрутизацию сигналов и шины питания на задней стороне. Технология 18A также снижает потери питания на 4–5 %. При общем повышении производительности компании удалось остаться в рамках прежнего диапазона TDP от 300 до 500 Вт.

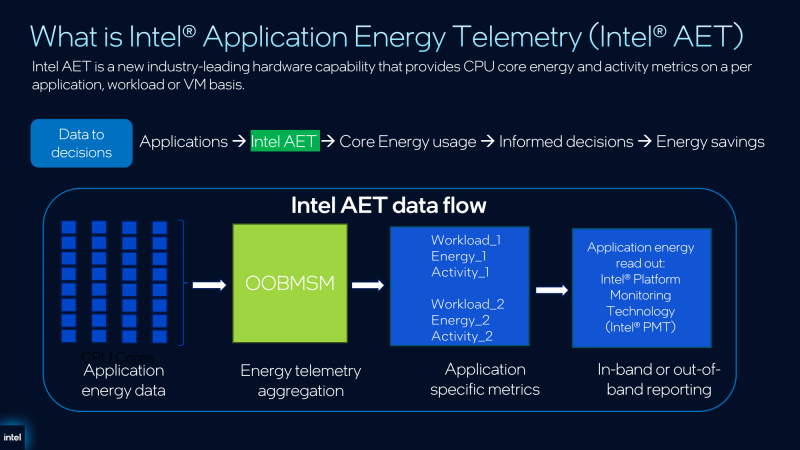

Ещё одна особенность Clearwater Forest — Intel AET (Application Energy Telemetry) — новая технология телеметрии энергопотребления приложений, нагрузок и ВМ. В отличие от интерфейса Intel Running Average Power Limit (RAPL), обеспечивающего мониторинг энергопотребления CPU, а также в некоторых сценариях DRAM и интегрированных GPU, с отражением расхода энергии в целом, новая функция позволяет контролировать энергопотребления по каждому приложению. Эта функция помогает разработчикам/администраторам профилировать и масштабировать рабочие нагрузки на процессорах с большим количеством ядер. Также реализована поддержка технологии Intel Turbo Rate Limiter.

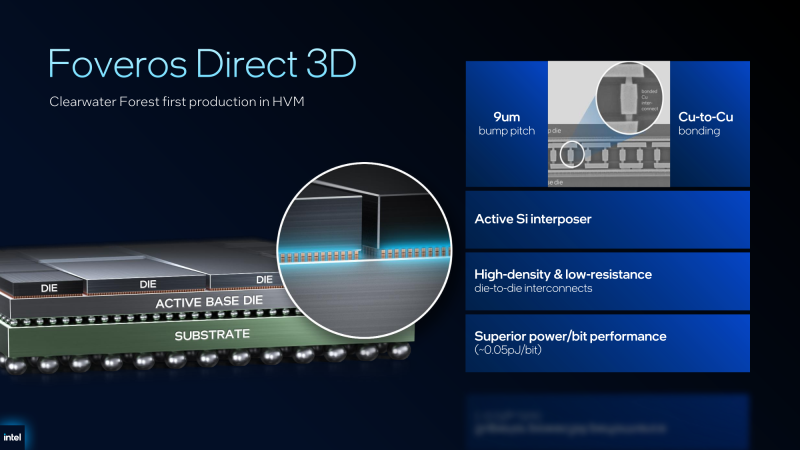

Clearlwater Forest-AP также является первым процессором массового производства, использующим технологию Foveros Direct3D — это передовое решение для корпусирования, которое объединяет вычислительные и IO-тайлы на базовых тайлах. Foveros Direct 3D имеет расстояние между контактами 9 мкм и использует вертикальное соединение Cu–Cu. Технология реализована в виде активного кремниевого интерпозера с высокой плотностью и низким сопротивлением, обеспечивая производительность ~0,05 пДж/бит. Проще говоря, на передачу данных между тайлами расходуется минимум энергии.

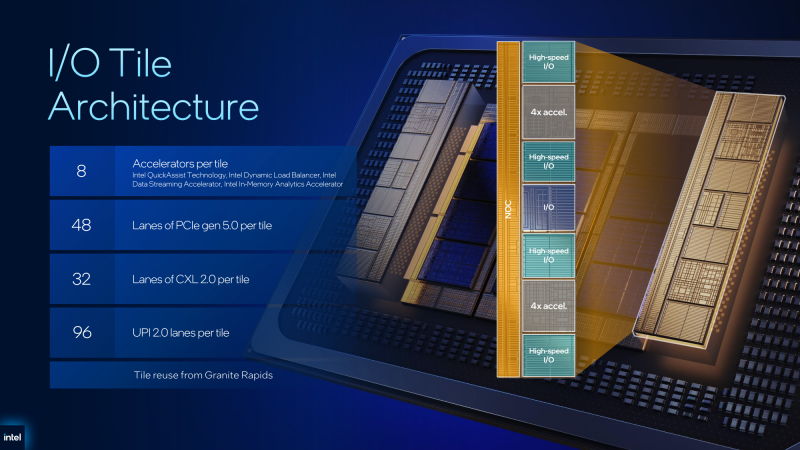

I/O-тайл позаимствован у Granite Rapids-AP (6900P). Он содержит восемь блоков ускорителей Intel Quick Assist (QAT), Intel Dynamic Load Balancer (DLB), Intel Data Streaming Accelerator (DSA) и Intel In-Memory Analytics Accelerator (IAA) — суммарно до четырёх ускорителей каждого типа на CPU. I/O-тайл также имеет 48 линий PCIe 5.0 (всего 96 на процессор), 32 линии CXL 2.0 (всего 64) и 96 линий UPI 2.0 (всего 192). Всего доступно шесть UPI-подключений (по 24 ГТ/с), который в 2S-конфигурации дают 576 Гбайт/с между CPU.

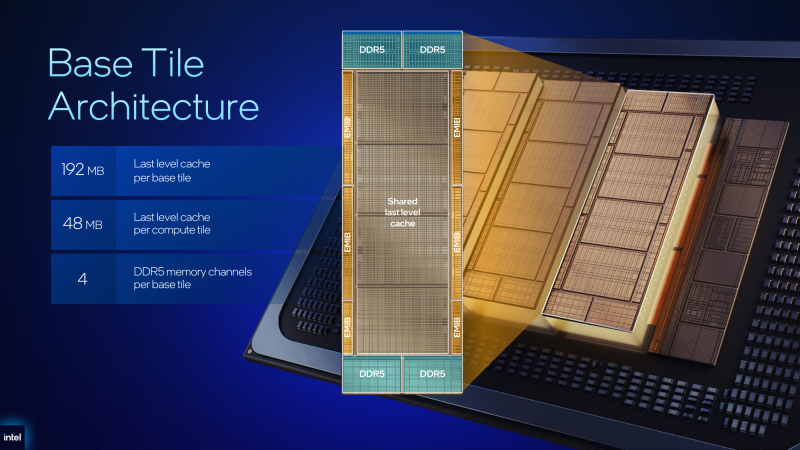

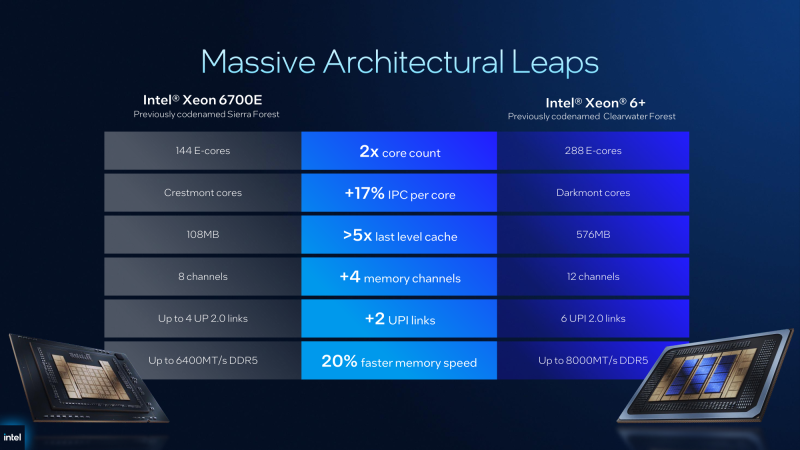

Базовый тайл оснащён четырьмя контроллерами памяти DDR5-8000 (без поддержки MRDIMM), что в сумме обеспечивает 12 каналов памяти на процессор. Тайл также подключён к общему L3-кешу с 48 Мбайт на вычислительный блок или 192 Мбайт на базовый тайл. Суммарно это даёт 576 Мбайт общего L3-кеша на чип. Формально это существенный прогресс в сравнении с Sierra Forest-AP (6900E), но эти чипы массовыми так и не стали.

Вычислительный тайл состоит из шести модулей, по четыре E-ядра Darkmont в каждом (по-прежнему без SMT/HT) — 24 ядра на тайл или 288 ядер на 12 тайлов в составе процессора. Один модуль содержит 4 Мбайт общего L2-кеша, т.е. 24 Мбайт L2-кеша на тайл и 288 Мбайт L2-кеша на процессор. Clearwater Forest используют тот же сокет LGA 7529, что и Xeon 6900P (Granite Rapids-AP) и Xeon 6900E (Sierra Forest-AP). Ожидается и появление более компактных 144-ядерных Clearwater Forest-SP.

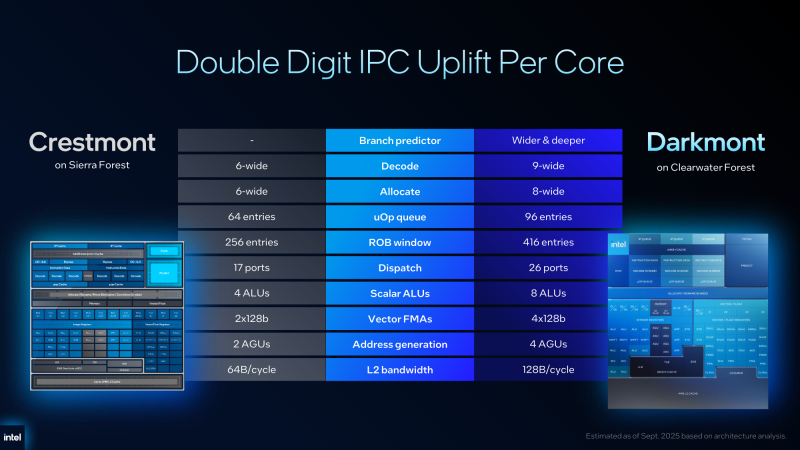

E-ядра Darkmont — это более «широкая» и быстрая версия предыдущей архитектуры Skymont, использовавшейся в десктопных CPU. По сравнению с Crestmont в Sierra Forest она представляет собой значительное обновление. В Darkmont реализовано девятипоточное декодирование — вместо шестипоточного в Crestmont — с помощью трёх трёхпоточных декодеров и возможность аллокации до 8 инструкций за раз. Ёмкость очереди микроопераций выросла с 64 до 96 записей, а буфера переупорядочивания с 256 до 416 записей.

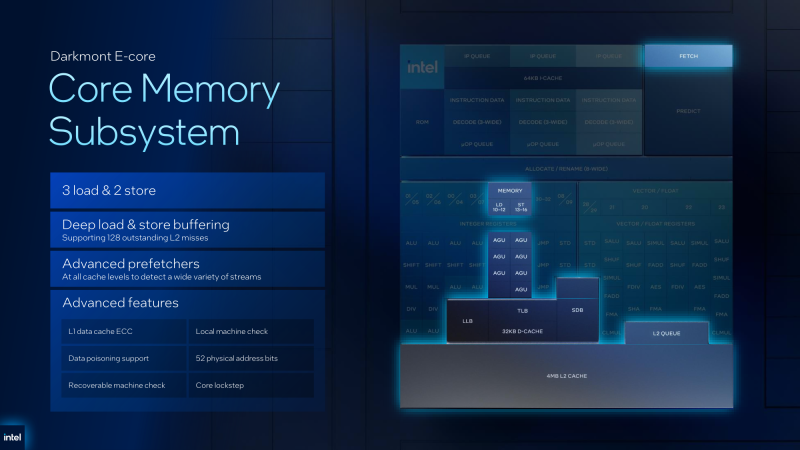

Также имеется увеличенный кеш инструкций объёмом 64 Кбайт, и более точный улучшенный механизм предсказаний ветвлений. При этом работа с L2-кешем ускорена вдвое, до 128 байт/такт, а передача данных между L1-кешами теперь происходит быстрее и более предсказуемо (через L2). Кроме того, усовершенствована предвыборка на всех уровнях кеша.

В планировщик можно отдавать 8 инструкций за такт (+60 % по сравнению с предыдущим поколением) и завершать исполнение до 16 операций за такт (вдвое больше). Количество портов исполнения увеличено с 17 до 26. Скалярный движок (Scalar Engine) получил 8 целочисленных вычислительных блока (было 4), 3 блока генерации адресов загрузки и 4 блока генерации адресов сохранения (было 2), а также поддержку подсистемой памяти трёх загрузок и двух сохранений за раз. Векторный движок (Vector Engine) получил 4 блока vector/float store, 2 vector/float и 4 стека vector/float — можно работать с четырьмя 128-байт FMA-операциями, а не двумя. Заявлена поддержка AVX2 с VNNI и INT8.

В целом, Darkmont E-Core в платформе Clearwater Forest обеспечивают производительность до 90 % выше, чем 144-ядерный процессор Xeon 6780E (Sierra Forest-SP), а также повышение эффективности на 23 % по всем вариантам нагрузок. Сравнение не вполне корректное, учитывая разницу в количестве ядер. По сравнению с Cascade Lake-SP новая архитектура обеспечивает консолидацию серверов до 8:1 с более низкой совокупной стоимостью владения. Функции безопасности будут включать Intel Software Guard Extensions (SGX) и Intel Trust Domain Extensions (TDX).

Источник: