Европейский Союз продолжает активно развивать собственное видение суперкомпьютеров ближайшего будущего, в основу которых ляжет архитектура RISC-V. За три с половиной года работы проекта Marenostrum Experimental Exascale Platform (MEEP) создана новая платформа, детально описывающая различные блоки и свойства таких HPC-систем.

Выбор микроархитектуры RISC-V в качестве основы MEEP вполне оправдан — она является открытой и позволяет разработчикам не зависеть от проприетарных наборов инструкций и аппаратных решений. Таким образом ЕС планирует достигнуть автономии в сфере супервычислений, обзаведясь собственной платформой.

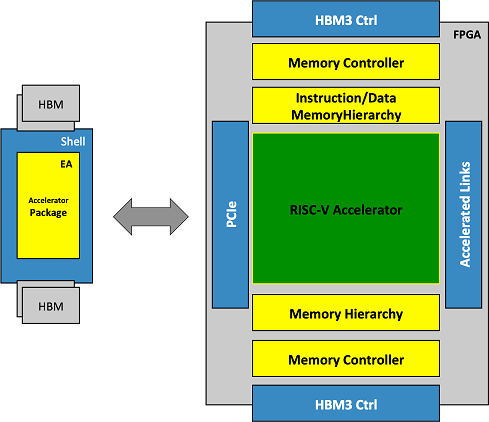

Высокоуровневое описание эмулируемого ускорителя

В основе проекта MEEP лежит ядро Accelerated Memory and Compute Engine (ACME), изначально спроектированное с прицелом на применение высокоскоростной памяти HBM3 и состоящее из тайлов памяти (Memory Tile) и вычислительных тайлов VAS, объединённых меш-интерконнектом. Воплощение дизайна ACME в реальный кремний пока ещё дело будущего, но уже очевидно, что процессоры, разработанные в рамках проекта MEEP, будут иметь чиплетную компоновку.

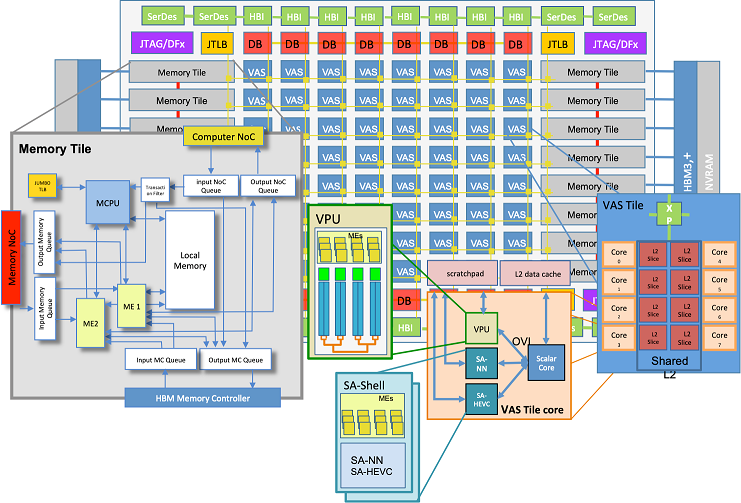

Архитектура ACME и её строительные блоки

В конструкции ACME на долю Memory Tile выпадают все операции с подсистемами памяти, включая построение иерархических массивов, использующих разные типы памяти, в том числе MRAM и HBM3. Модули VAS включают себя по 8 процессорных ядер со своими разделами L2-кеша. Каждое такое ядро состоит из нескольких отдельных блоков: скалярного RISC-V, блока векторных операций, а также блоков ускорителей двух типов — SA-HEVC для обработки видео и SA-NN для нейросетевых задач, в частности, инференса.

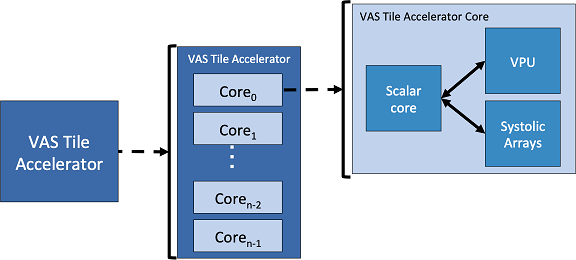

Схема работы ускорителей в составе блоков VAS

По сути, каждый модуль VAS представляет собой вполне законченный многоядерный процессор RISC-V, способный работать со всеми современными форматами данных, автоматически распознающий расширенные инструкции и выполняющий их с помощью соответствующих ускорителей в своём составе.

Платформа, созданная в рамках проекта MEEP, уже функционирует как эмулируемый с помощью FPGA Xilinx полноценный прототип. Он позволяет не только вести разработку и отладку ПО для новой европейской суперкомпьютерной экосистемы, но и производить валидацию аппаратных компонентов для будущих ускорителей/процессоров с архитектурой ACME.

Источник: