На саммите OCP 2022 компанией Astera Labs озвучены любопытные цифры: уже к 2025 году 49% данных и 59% всех серверов в мире будут располагаться в публичных облаках. Серьёзную лепту в этот рост привносит рынок ИИ — размеры моделей удваиваются каждые 3,5 месяца, а в денежном выражении объём этого сектора рынка к тому же 2025 году должен превысить $60 млрд. А помочь в развитии подходящих аппаратных инфраструктур, по мнению Astera Labs, может CXL.

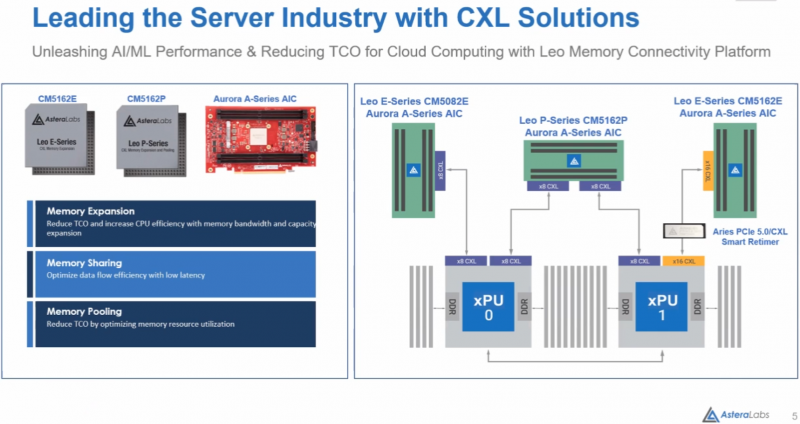

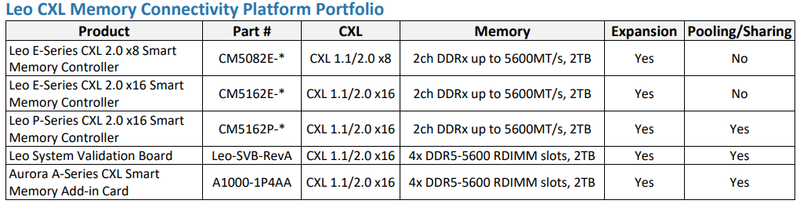

Первым достаточно масштабным применением CXL станут системы расширения памяти, которые полезны уже в системах с поддержкой лишь CXL 1.1, тогда как создание пулов DRAM потребует CXK 2.0. Однако у Astera Labs уже есть полноценные ASIC для этих задач — решения серий Leo E и Leo P.

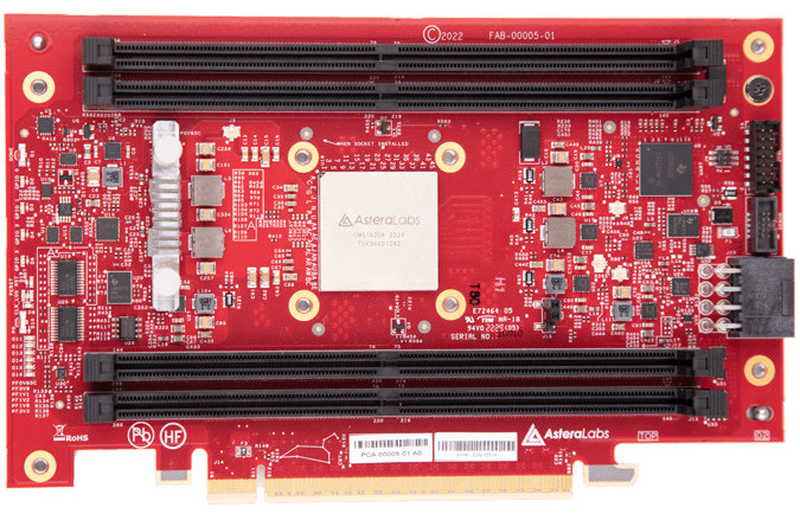

Leo E представляет собой экспандер, связующее звено между PCI Express и DDR. На основе этого чипа компания разработала платы расширения Aurora c 8 и 16 линиями CXL на базе чипов CM5082E и CM5162E, соответственно. В отличие от решений некоторых других разработчиков, осваивающих CXL, Astera Labs предлагает не FPGA-реализацию, а полноценную платформу, которую можно использовать в практических целях уже сейчас.

В серии Leo наибольший интерес представляет чип CM5162P — это уже не просто мост между процессором, PCIe и банками DRAM на плате расширения, а полноценное решение для пулинга памяти с поддержкой CXL 2.0. Оно включает в себя контроллеры физических уровней CXL 2.0 и JEDEC DDRx, блоки обеспечения функций безопасности и кастомизации. Контроллеры совместимы с любой стандартной памятью со скоростями до 5600 МТ/с.

Плата Aurora на базе CM5162P может использовать физический интерфейс PCIe x16 как два интерфейса CXL x8 и, таким образом, общаться одновременно с обоими процессорами в классическом двухпроцессорном сервере. Максимальный объём пула DRAM составляет 2 Тбайт в четырёх модулях DDR5 RDIMM — солидная прибавка к возможностям контроллеров памяти в CPU.

Кроме того, в арсенале компании есть и подходящие ретаймеры серии Aries, совместимые с PCIe 4.0/5.0 и CXL. Эти чипы поддерживают гибкую бифуркацию шины и соответствуют спецификациям Intel PCIe Standard Retimer Footprint. А возможности интегрированных приёмопередатчиков заведомо превышают минимальные требования PCIe Base Specification, что позволяет создавать на базе Aries действительно разветвлённые системы расширения и пулинга DRAM.

Таким образом, Astera Labs уже можно назвать одним из пионеров практического освоения рынка CXL-решений: у компании есть законченное портфолио, включающее в себя всё необходимое, от ASIC и ретаймеров до плат расширения, готовых к использованию в ИИ-платформах и облачных системах.

Источник: